#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 17                                                                           |

| Program Memory Size        | 4KB (1.375K x 24)                                                            |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 20-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04kl101-e-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-5:** PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS

|          | Pin Number                       |               |    |     |        |                                                   |  |  |

|----------|----------------------------------|---------------|----|-----|--------|---------------------------------------------------|--|--|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN |    |     | Buffer | Description                                       |  |  |

| AN0      | 2                                | 19            | 2  | I   | ANA    | A/D Analog Inputs. Not available on PIC24F16KL10X |  |  |

| AN1      | 3                                | 20            | 3  | Ι   | ANA    | family devices.                                   |  |  |

| AN2      | 4                                | 1             | —  | Ι   | ANA    |                                                   |  |  |

| AN3      | 5                                | 2             | _  | I   | ANA    |                                                   |  |  |

| AN4      | 6                                | 3             | _  | I   | ANA    |                                                   |  |  |

| AN9      | 18                               | 15            | 12 | I   | ANA    |                                                   |  |  |

| AN10     | 17                               | 14            | 11 | I   | ANA    |                                                   |  |  |

| AN11     | 16                               | 13            | _  | I   | ANA    |                                                   |  |  |

| AN12     | 15                               | 12            | _  | I   | ANA    |                                                   |  |  |

| AN13     | 7                                | 4             | 4  | I   | ANA    | 7                                                 |  |  |

| AN14     | 8                                | 5             | 5  | I   | ANA    | 1                                                 |  |  |

| AN15     | 9                                | 6             | 6  | I   | ANA    | 1                                                 |  |  |

| AVdd     | 20                               | 17            | 14 | I   | ANA    | Positive Supply for Analog modules                |  |  |

| AVss     | 19                               | 16            | 13 | I   | ANA    | Ground Reference for Analog modules               |  |  |

| CCP1     | 14                               | 11            | 10 | I/O | ST     | CCP1 Capture Input/Compare and PWM Output         |  |  |

| CCP2     | 15                               | 12            | 9  | I/O | ST     | CCP2 Capture Input/Compare and PWM Output         |  |  |

| C1INA    | 8                                | 5             | 5  | I   | ANA    | Comparator 1 Input A (+)                          |  |  |

| C1INB    | 7                                | 4             | 4  | I   | ANA    | Comparator 1 Input B (-)                          |  |  |

| C1INC    | 5                                | 2             | _  | I   | ANA    | Comparator 1 Input C (+)                          |  |  |

| C1IND    | 4                                | 1             | _  | I   | ANA    | Comparator 1 Input D (-)                          |  |  |

| C1OUT    | 17                               | 14            | 11 | 0   | _      | Comparator 1 Output                               |  |  |

| CLK I    | 7                                | 4             | 9  | I   | ANA    | Main Clock Input                                  |  |  |

| CLKO     | 8                                | 5             | 10 | 0   | _      | System Clock Output                               |  |  |

| CN0      | 10                               | 7             | 7  | I   | ST     | Interrupt-on-Change Inputs                        |  |  |

| CN1      | 9                                | 6             | 6  | I   | ST     |                                                   |  |  |

| CN2      | 2                                | 19            | 2  | I   | ST     |                                                   |  |  |

| CN3      | 3                                | 20            | 3  | I   | ST     | 7                                                 |  |  |

| CN4      | 4                                | 1             | _  | I   | ST     | 7                                                 |  |  |

| CN5      | 5                                | 2             | _  | Ι   | ST     | ]                                                 |  |  |

| CN6      | 6                                | 3             | _  | I   | ST     | 7                                                 |  |  |

| CN8      | 14                               | 11            | 10 | I   | ST     | 1                                                 |  |  |

| CN9      | _                                | _             | —  | I   | ST     | 1                                                 |  |  |

| CN11     | 18                               | 15            | 12 | I   | ST     | 7                                                 |  |  |

| CN12     | 17                               | 14            | 11 | I   | ST     | 1                                                 |  |  |

| CN13     | 16                               | 13            | —  | I   | ST     | 1                                                 |  |  |

| CN14     | 15                               | 12            | _  | I   | ST     | 7                                                 |  |  |

| CN21     | 13                               | 10            | 9  | I   | ST     | 1                                                 |  |  |

| CN22     | 12                               | 9             | 8  | I   | ST     | 1                                                 |  |  |

| CN23     | 11                               | 8             | —  | I   | ST     | 1                                                 |  |  |

| CN29     | 8                                | 5             | 5  | I   | ST     | 1                                                 |  |  |

| CN30     | 7                                | 4             | 4  | 1   | ST     | 1                                                 |  |  |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

# 3.0 CPU

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the CPU, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"CPU"** (DS39703).

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16<sup>th</sup> Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K word boundary of either program memory or data EEPROM memory, defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (i.e., A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by a 16-bit integer signed and unsigned division. All divide operations require 19 cycles to complete, but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme, with up to eight sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is illustrated in Figure 3-1.

## 3.1 Programmer's Model

Figure 3-2 displays the programmer's model for the PIC24F. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions.

Table 3-1 provides a description of each register. All registers associated with the programmer's model are memory mapped.

# 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                    | U-0                  | U-0                                        | U-0            | U-0                            | U-0                          | U-0               | R/W-0          |

|------------------------|----------------------|--------------------------------------------|----------------|--------------------------------|------------------------------|-------------------|----------------|

|                        | _                    | _                                          | _              | _                              | _                            | _                 | DC             |

| bit 15                 |                      | I I                                        |                |                                |                              |                   | bit            |

| R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                       | R-0            | R/W-0                          | R/W-0                        | R/W-0             | R/W-0          |

| IPL2 <sup>(2)</sup>    | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>                        | RA             | N                              | OV                           | Z                 | C              |

| bit 7                  |                      | 20                                         |                |                                | 0.                           | _                 | bit            |

|                        |                      |                                            |                |                                |                              |                   |                |

| Legend:<br>R = Readabl | e hit                | W = Writable b                             | it             | II = I Inimplem                | nented bit, read             | d as 'O'          |                |

| -n = Value at          |                      | '1' = Bit is set                           | iii iii        | '0' = Bit is clea              |                              | x = Bit is unkr   | NOWD           |

|                        |                      |                                            |                |                                |                              |                   |                |

| bit 15-9               | Unimplemen           | ted: Read as '0                            | ,              |                                |                              |                   |                |

| bit 8                  | -                    | f Carry/Borrow b                           |                |                                |                              |                   |                |

|                        |                      | -                                          |                | (for byte-sized da             | ata) or 8 <sup>th</sup> Iow- | order bit (for wo | ord-sized dat  |

|                        | of the res           | sult occurred                              |                |                                |                              |                   |                |

|                        | •                    |                                            |                | rder bit of the res            |                              | ed                |                |

| bit 7-5                | IPL<2:0>: CF         | PU Interrupt Prio                          | rity Level (IP | L) Status bits <sup>(1,2</sup> | 2)                           |                   |                |

|                        |                      |                                            |                | 5); user interrupt             | s disabled                   |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I<br>nterrupt Priority I | •              | ,                              |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

| bit 4                  | <b>RA:</b> REPEAT    | Loop Active bit                            |                |                                |                              |                   |                |

|                        |                      | oop in progress                            |                |                                |                              |                   |                |

|                        |                      | oop not in progr                           | ess            |                                |                              |                   |                |

| bit 3                  | N: ALU Nega          |                                            |                |                                |                              |                   |                |

|                        | 1 = Result wa        | 0                                          | (              | 4:                             |                              |                   |                |

|                        |                      | as non-negative                            | (zero or posi  | tive)                          |                              |                   |                |

| bit 2                  | OV: ALU Ove          |                                            |                |                                |                              |                   |                |

|                        |                      | occurred for sig                           |                | plement) arithm                | etic in this arith           | imetic operation  | n              |

| bit 1                  | <b>Z:</b> ALU Zero   |                                            |                |                                |                              |                   |                |

|                        |                      |                                            | te the 7 hit 4 | nas set it at some             | e time in the n              | aet               |                |

|                        |                      |                                            |                | cts the Z bit, has             |                              |                   | sult)          |

| bit 0                  | C: ALU Carry         |                                            | ,              | ,,                             |                              | ,                 | -7             |

| ~                      |                      |                                            | Significant b  | oit (MSb) of the r             | esult occurred               |                   |                |

|                        |                      |                                            |                | bit (MSb) of the               |                              |                   |                |

| Note 1: Th             | ne IPI. Status hi    | ts are read-only                           | when NSTD      | IS (INTCON1<1                  | 5>) = 1                      |                   |                |

|                        |                      |                                            |                | IPL3 bit (CORC                 |                              | m the CPU I Into  | rrunt Priority |

| <b>2</b> .             |                      |                                            |                |                                |                              |                   | in april nonty |

2: The IPL Status bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

#### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is as follows:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to <sup>(011000)</sup> to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '000100' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-5.

| ; Set up  | NVMCON for re | ow erase operation               |                                     |

|-----------|---------------|----------------------------------|-------------------------------------|

| M         | OV #0x405     | 8, WO ;                          |                                     |

| M         | OV WO, NVI    | MCON ;                           | Initialize NVMCON                   |

| ; Init po | inter to row  | to be ERASED                     |                                     |

| M         | OV #tblpag    | ge(PROG_ADDR), W0 ;              |                                     |

| M         | OV WO, TB     | LPAG ;                           | Initialize PM Page Boundary SFR     |

| M         | OV #tblof:    | <pre>fset(PROG_ADDR), W0 ;</pre> | Initialize in-page EA[15:0] pointer |

| TI        | BLWTL WO, [W  | 0] ;                             | Set base address of erase block     |

| D         | ISI #5        | ;                                | Block all interrupts                |

|           |               |                                  | for next 5 instructions             |

| MO        | OV #0x55,     | WO                               |                                     |

| M         | OV WO, NVI    | MKEY ;                           | Write the 55 key                    |

| MO        | OV #0xAA,     | W1 ;                             |                                     |

| MO        | OV W1, NVI    | MKEY ;                           | Write the AA key                    |

| B         | SET NVMCON    | , #WR ;                          | Start the erase sequence            |

| NO        | ЭР            | ;                                | Insert two NOPs after the erase     |

| N         | OP            | ;                                | command is asserted                 |

|           |               |                                  |                                     |

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE

### 6.3 NVM Address Register

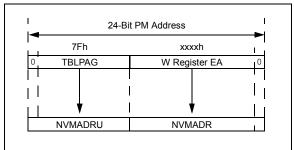

As with Flash program memory, the NVM Address Registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space; instead, they directly capture the EA<23:0> of the last Table Write instruction that has been executed and selects the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", is unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

#### FIGURE 6-1: DATA EEPROM ADDRESSING WITH TBLPAG AND NVM ADDRESS REGISTERS

### 6.4 Data EEPROM Operations

The EEPROM block is accessed using Table Read and Table Write operations, similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- Bulk erase the entire data EEPROM

- Write one word

- Read one word

| Note: | Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | The C30 C compiler includes library<br>procedures to automatically perform the<br>Table Read and Table Write operations,<br>manage the Table Pointer and write<br>buffers, and unlock and initiate memory<br>write sequences. This eliminates the need<br>to create assembler macros or time<br>critical routines in C for each application. |

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the C30 compiler libraries.

#### 6.4.3 READING THE DATA EEPROM

To read a word from data EEPROM, the Table Read instruction is used. Since the EEPROM array is only 16 bits wide, only the TBLRDL instruction is needed. The read operation is performed by loading TBLPAG and WREG with the address of the EEPROM location followed by a TBLRDL instruction.

A typical read sequence using the Table Pointer management (builtin\_tblpage and builtin\_tbloffset) and Table Read (builtin\_tblrdl) procedures from the C30 compiler library is provided in Example 6-5.

Program Space Visibility (PSV) can also be used to read locations in the data EEPROM.

#### EXAMPLE 6-5: READING THE DATA EEPROM USING THE TBLRD COMMAND

| <pre>intattribute ((space(eedata))) eeData = 0x1234;</pre>                                                                                                                             | // Global variable located in EEPROM                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| int data;                                                                                                                                                                              | // Data read from EEPROM                                                                                                  |

| unsigned int offset;                                                                                                                                                                   |                                                                                                                           |

| <pre>// Set up a pointer to the EEPROM location to be en<br/>TBLPAG =builtin_tblpage(&amp;eeData);<br/>offset =builtin_tbloffset(&amp;eeData);<br/>data =builtin_tblrdl(offset);</pre> | rased<br>// Initialize EE Data page pointer<br>// Initizlize lower word of address<br>// Write EEPROM data to write latch |

### 7.4.2 DETECTING BOR

When BOR is enabled, the BOR bit (RCON<1>) is always reset to '1' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR and BOR bits are reset to '0' in the software, immediately after any POR event. If the BOR bit is '1' while POR is '0', it can be reliably assumed that a BOR event has occurred.

**Note:** Even when the device exits from Deep Sleep mode, both the POR and BOR are set.

#### 7.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, BOR remains under hardware control and operates as previously described. However, whenever the device enters Sleep mode, BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

#### 8.3 Interrupt Control and Status Registers

Depending on the particular device, the PIC24F16KL402 family of devices implements up to 28 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS5

- IEC0 through IEC5

- IPC0 through IPC7, ICP9, IPC12, ICP16, ICP18 and IPC20

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIV table.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence listed in Table 8-2. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. The INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits are in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user may change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit, which together with the IPL<2:0> bits, also indicates the current CPU priority level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All interrupt registers are described in Register 8-3 through Register 8-30, in the following sections.

#### 8.4 Interrupt Setup Procedures

#### 8.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS Control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and the type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits, for all enabled interrupt sources, may be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized, such that all user interrupt sources are assigned to Priority Level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 8.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (i.e., C or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 8.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 8.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, OEh, with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period. Level 7 interrupt sources are not disabled by the DISI instruction.

# 16.0 CAPTURE/COMPARE/PWM (CCP) AND ENHANCED CCP MODULES

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Capture/Compare/PWM module, refer to the "dsPIC33/PIC24 Family Reference Manual".

Depending on the particular device, PIC24F16KL402 family devices include up to three CCP and/or ECCP modules. Key features of all CCP modules include:

- 16-bit input capture for a range of edge events

- 16-bit output compare with multiple output options

- Single-output Pulse-Width Modulation (PWM) with up to 10 bits of resolution

- User-selectable time base from any available timer

- Special Event Trigger on capture and compare events to automatically trigger a range of peripherals

ECCP modules also include these features:

- Operation in Half-Bridge and Full-Bridge (Forward and Reverse) modes

- Pulse steering control across any or all Enhanced PWM pins with user-configurable steering synchronization

- User-configurable external Fault detect with auto-shutdown and auto-restart

PIC24FXXKL40X/30X devices instantiate three CCP modules, one Enhanced (ECCP1) and two standard (CCP2 and CCP3). All other devices instantiate two standard CCP modules (CCP1 and CCP2).

#### 16.1 Timer Selection

On all PIC24F16KL402 family devices, the CCP and ECCP modules use Timer3 as the time base for capture and compare operations. PWM and Enhanced PWM operations may use either Timer2 or Timer4. PWM time base selection is done through the CCPTMRS0 register (Register 16-6).

#### 16.2 CCP I/O Pins

To configure I/O pins with a CCP function, the proper mode must be selected by setting the CCPxM<3:0> bits.

Where the Enhanced CCP module is available, it may have up to four PWM outputs depending on the selected operating mode. These outputs are designated, P1A through P1D. The outputs that are active depend on the ECCP operating mode selected. To configure I/O pins for Enhanced PWM operation, the proper PWM mode must be selected by setting the PM<1:0> and CCPxM<3:0> bits.

## 18.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UART:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write data byte to lower byte of UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0 and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately, because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

### 18.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UART (as described in **Section 18.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

# 18.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UART for the desired mode.

- 2. Set UTXEN and UTXBRK sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

#### 18.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UART (as described in Section 18.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UART.

- 3. A receive interrupt will be generated when one or more data characters have been received as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

# 18.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-to-Send (UxCTS) and Request-to-Send (UxRTS) are the two hardware-controlled pins that are associated with the UART module. These two pins allow the UART to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

# 18.7 Infrared Support

The UART module provides two types of infrared UART support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 18.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UART module is enabled; it can be used to support the IrDA codec chip.

# 18.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UART has full implementation of the IrDA encoder and decoder as part of the UART module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

#### REGISTER 20-1: CMxCON: COMPARATOR x CONTROL REGISTER

| R/W-0      | R/W-0                                | R/W-0                                  | R/W-0             | U-0              | U-0              | R/W-0                               | R-0            |

|------------|--------------------------------------|----------------------------------------|-------------------|------------------|------------------|-------------------------------------|----------------|

| CON        | COE                                  | CPOL                                   | CLPWR             |                  | _                | CEVT                                | COUT           |

| bit 15     |                                      |                                        | •                 |                  | •                |                                     | bit            |

|            |                                      |                                        |                   |                  |                  |                                     |                |

| R/W-0      | R/W-0                                | U-0                                    | R/W-0             | U-0              | U-0              | R/W-0                               | R/W-0          |

| EVPOL1     | <sup>(1)</sup> EVPOL0 <sup>(1)</sup> |                                        | CREF              |                  |                  | CCH1                                | CCH0           |

| bit 7      |                                      |                                        |                   |                  |                  |                                     | bit            |

| Legend:    |                                      |                                        |                   |                  |                  |                                     |                |

| R = Reada  | abla bit                             | W = Writable                           | hit               |                  | montod bit roo   | d aa '0'                            |                |

|            |                                      |                                        |                   |                  | nented bit, rea  |                                     |                |

| -n = Value | atPOR                                | '1' = Bit is se                        | [                 | '0' = Bit is cle | ared             | x = Bit is unkn                     | iown           |

| bit 15     | CON: Compa                           | arator Enable b                        | it                |                  |                  |                                     |                |

|            | •                                    | ator is enabled                        |                   |                  |                  |                                     |                |

|            |                                      | ator is disabled                       |                   |                  |                  |                                     |                |

| bit 14     | COE: Compa                           | arator Output E                        | nable bit         |                  |                  |                                     |                |

|            |                                      |                                        | resent on the C   | KOUT pin         |                  |                                     |                |

|            | -                                    | ator output is in                      | -                 |                  |                  |                                     |                |

| bit 13     |                                      | •                                      | Polarity Select b | bit              |                  |                                     |                |

|            |                                      | ator output is in<br>ator output is ne |                   |                  |                  |                                     |                |

| bit 12     | -                                    | -                                      | Power Mode Se     | loct hit         |                  |                                     |                |

|            |                                      | •                                      | Low-Power mo      |                  |                  |                                     |                |

|            |                                      |                                        | perate in Low-Po  |                  |                  |                                     |                |

| bit 11-10  | Unimplemer                           | ted: Read as                           | 0'                |                  |                  |                                     |                |

| bit 9      | CEVT: Comp                           | arator Event bi                        | t                 |                  |                  |                                     |                |

|            | 1 = Compara                          | ator event defir                       | ned by EVPOL<     | 1:0> has occu    | ırred; subsequ   | ent triggers and                    | interrupts a   |

|            |                                      | until the bit is o                     |                   |                  |                  |                                     |                |

|            | -                                    | ator event has                         |                   |                  |                  |                                     |                |

| bit 8      |                                      | parator Output                         | bit               |                  |                  |                                     |                |

|            | <u>When CPOL</u><br>1 = VIN+ > V     |                                        |                   |                  |                  |                                     |                |

|            | 0 = VIN + < V                        |                                        |                   |                  |                  |                                     |                |

|            | When CPOL                            |                                        |                   |                  |                  |                                     |                |

|            | 1 = VIN+ < V                         |                                        |                   |                  |                  |                                     |                |

|            | 0 = VIN + > V                        |                                        |                   |                  |                  |                                     |                |

| bit 7-6    |                                      |                                        | t/Interrupt Polar |                  |                  |                                     |                |

|            |                                      |                                        |                   |                  |                  | ator output (whil                   |                |

|            |                                      |                                        |                   |                  |                  | f the comparato<br>of the comparato |                |

|            |                                      |                                        | t generation is o |                  | Ign transition o |                                     | output         |

| bit 5      |                                      | nted: Read as                          | •                 |                  |                  |                                     |                |

| bit 4      | -                                    |                                        | ice Select bits ( | non-invertina ii | nput)            |                                     |                |

|            |                                      |                                        | nects to the inte | -                |                  |                                     |                |

|            |                                      |                                        | nects to the CxI  |                  | J                |                                     |                |

| Note 1:    | If EVPOL<1:0> is                     | s set to a value                       | other than '00',  | the first interr | upt generated    | will occur on an                    | y transition c |

|            | COUT, regardles                      |                                        |                   |                  |                  |                                     |                |

|            | bits setting.                        |                                        |                   |                  |                  |                                     |                |

2: Unimplemented on 14-pin (PIC24FXXKL100/200) devices.

### 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

NOTES:

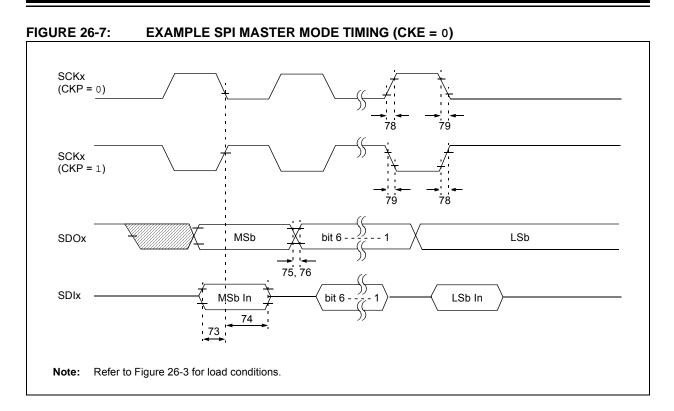

## TABLE 26-27: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

| Param<br>No. | Symbol                | Characteristic                             | Min | Max | Units | Conditions |

|--------------|-----------------------|--------------------------------------------|-----|-----|-------|------------|

| 73           | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 20  |     | ns    |            |

| 74           | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge  | 40  | —   | ns    |            |

| 75           | TDOR                  | SDOx Data Output Rise Time                 | _   | 25  | ns    |            |

| 76           | TDOF                  | SDOx Data Output Fall Time                 | _   | 25  | ns    |            |

| 78           | TscR                  | SCKx Output Rise Time (Master mode)        | _   | 25  | ns    |            |

| 79           | TscF                  | SCKx Output Fall Time (Master mode)        | _   | 25  | ns    |            |

|              | FSCK                  | SCKx Frequency                             | —   | 10  | MHz   |            |

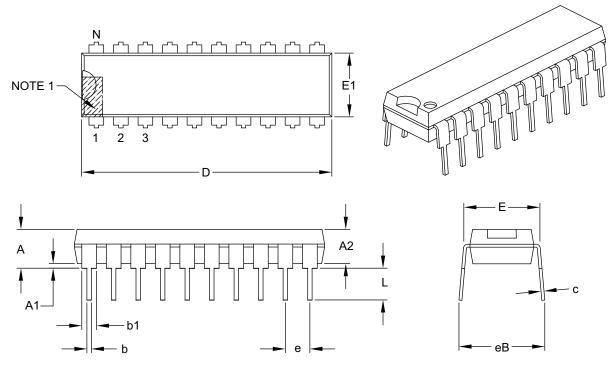

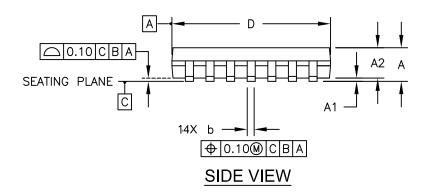

### 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |      | INCHES   |       |

|----------------------------|----------|------|----------|-------|

| Dimension                  | n Limits | MIN  | NOM      | MAX   |

| Number of Pins             | Ν        |      | 20       |       |

| Pitch                      | е        |      | .100 BSC |       |

| Top to Seating Plane       | Α        | -    | -        | .210  |

| Molded Package Thickness   | A2       | .115 | .130     | .195  |

| Base to Seating Plane      | A1       | .015 | -        | -     |

| Shoulder to Shoulder Width | Е        | .300 | .310     | .325  |

| Molded Package Width       | E1       | .240 | .250     | .280  |

| Overall Length             | D        | .980 | 1.030    | 1.060 |

| Tip to Seating Plane       | L        | .115 | .130     | .150  |

| Lead Thickness             | С        | .008 | .010     | .015  |

| Upper Lead Width           | b1       | .045 | .060     | .070  |

| Lower Lead Width           | b        | .014 | .018     | .022  |

| Overall Row Spacing §      | eВ       | _    | _        | .430  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

# 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-087C Sheet 1 of 2

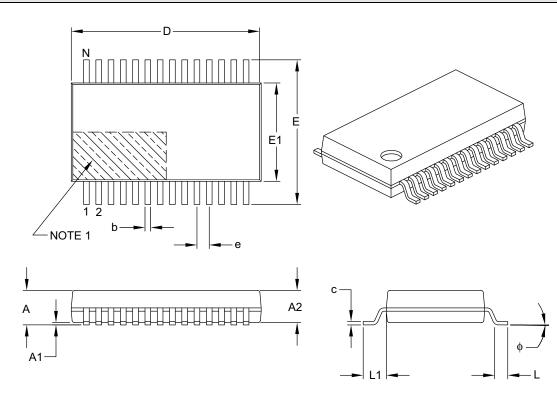

### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units           |      | MILLIMETERS | 3     |

|--------------------------|-----------------|------|-------------|-------|

| D                        | imension Limits | MIN  | NOM         | MAX   |

| Number of Pins           | N               |      | 28          |       |

| Pitch                    | е               |      | 0.65 BSC    |       |

| Overall Height           | A               | -    | -           | 2.00  |

| Molded Package Thickness | A2              | 1.65 | 1.75        | 1.85  |

| Standoff                 | A1              | 0.05 | -           | -     |

| Overall Width            | E               | 7.40 | 7.80        | 8.20  |

| Molded Package Width     | E1              | 5.00 | 5.30        | 5.60  |

| Overall Length           | D               | 9.90 | 10.20       | 10.50 |

| Foot Length              | L               | 0.55 | 0.75        | 0.95  |

| Footprint                | L1              |      | 1.25 REF    |       |

| Lead Thickness           | С               | 0.09 | -           | 0.25  |

| Foot Angle               | ф               | 0°   | 4°          | 8°    |

| Lead Width               | b               | 0.22 | -           | 0.38  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

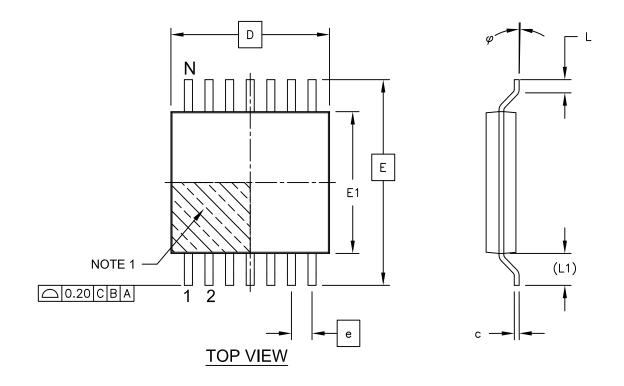

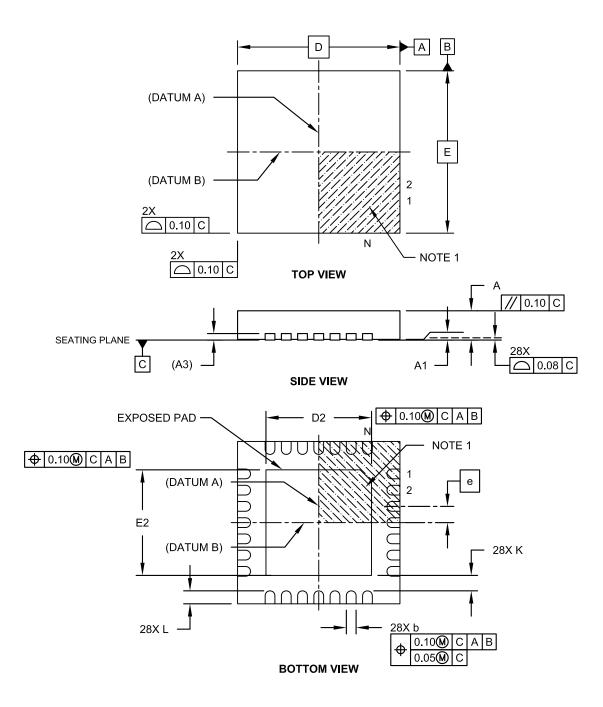

### 28-Lead Plastic Quad Flat, No Lead Package (MQ) – 5x5x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-140B Sheet 1 of 2

# INDEX

| 1 | • |

|---|---|

| • | ١ |

| A/D                                    |     |

|----------------------------------------|-----|

| 10-Bit High-Speed A/D Converter        | 157 |

| Conversion Timing Requirements         | 224 |

| Module Specifications                  | 223 |

| A/D Converter                          |     |

| Analog Input Model                     | 164 |

| Transfer Function                      | 165 |

| AC Characteristics                     |     |

| A/D Module                             | 223 |

| Capacitive Loading Requirements on     |     |

| Output Pins                            | 209 |

| Internal RC Oscillator Accuracy        | 211 |

| Internal RC Oscillator Specifications  | 211 |

| Load Conditions and Requirements       | 209 |

| Temperature and Voltage Specifications |     |

| Assembler                              |     |

| MPASM Assembler                        |     |

# В

| Block Diagrams                              |     |

|---------------------------------------------|-----|

| 10-Bit High-Speed A/D Converter             | 158 |

| 16-Bit Timer1                               | 115 |

| Accessing Program Memory with               |     |

| Table Instructions                          |     |

| CALL Stack Frame                            | 43  |

| Capture Mode Operation                      | 126 |

| Comparator Module                           |     |

| Comparator Voltage Reference Module         | 171 |

| Compare Mode Operation                      |     |

| CPU Programmer's Model                      |     |

| Data Access From Program Space              |     |

| Address Generation                          |     |

| Data EEPROM Addressing with TBLPAG and      |     |

| NVM Registers                               | 55  |

| Enhanced PWM Mode                           | 127 |

| High/Low-Voltage Detect (HLVD) Module       | 173 |

| Individual Comparator Configurations        | 168 |

| MCLR Pin Connections Example                |     |

| MSSPx Module (I <sup>2</sup> C Master Mode) | 137 |

| MSSPx Module (I <sup>2</sup> C Mode)        |     |

| MSSPx Module (SPI Mode)                     |     |

| PIC24F CPU Core                             |     |

| PIC24F16KL402 Family (General)              |     |

| PSV Operation                               | 46  |

| PWM Operation (Simplified)                  | 126 |

| Recommended Minimum Connections             |     |

| Reset System                                |     |

| Serial Resistor                             | 107 |

| Shared I/O Port Structure                   | 111 |

| Simplified UARTx                            | 149 |

| SPI Master/Slave Connection                 | 136 |

| Suggested Placement of Oscillator Circuit   |     |

| System Clock                                |     |

| Table Register Addressing                   |     |

| Timer2                                      | 117 |

| Timer3                                      | 119 |

| Timer4                                      |     |

| Watchdog Timer (WDT)                        | 184 |

|                                             |     |

# С

| C Compilers                                      |

|--------------------------------------------------|

| MPLAB XC Compilers 188                           |

| Capture/Compare/PWM (CCP) 125                    |

| CCP/ECCP                                         |

| CCP I/O Pins 125                                 |

| Timer Selection 125                              |

| Code Examples                                    |

| Data EEPROM Bulk Erase 57                        |

| Data EEPROM Unlock Sequence 53                   |

| Erasing a Program Memory Row,                    |

| Assembly Language 50                             |

| Erasing a Program Memory Row, C Language 51      |

| I/O Port Write/Read (Assembly Language) 114      |

| I/O Port Write/Read (C Language) 114             |

| Initiating a Programming Sequence,               |

| Assembly Language 52                             |

| Initiating a Programming Sequence, C Language 52 |

| Loading the Write Buffers, Assembly Language 51  |

| Loading the Write Buffers, C Language 52         |

| PWRSAV Instruction Syntax 105                    |

| Reading Data EEPROM Using the                    |

| TBLRD Command58                                  |

| Sequence for Clock Switching                     |

| Single-Word Erase                                |

| Single-Word Write to Data EEPROM 57              |

| Ultra Low-Power Wake-up Initialization 107       |

| Code Protection                                  |

| Comparator                                       |

| Comparator Voltage Reference                     |

| Configuring                                      |

| Configuration Bits                               |

| Core Features                                    |

| CPU                                              |

| ALU                                              |

| Control Registers                                |

| Core Registers                                   |

| Programmer's Model                               |

| Customer Notification Service                    |

| Customer Support                                 |

|                                                  |

| D                                                |

| Data EEPROM Memory           | 53 |

|------------------------------|----|

| Erasing                      | 56 |

| Nonvolatile Memory Registers |    |

| NVMCON                       | 53 |

| NVMKEY                       | 53 |

| NVMADR(U)                    | 55 |

| Operations                   | 55 |

| Programming                  |    |

| Bulk Erase                   | 57 |

| Reading Data EEPROM          | 58 |

| Single-Word Write            | 57 |

| Data Memory                  |    |

| Address Space                | 33 |

| Memory Map                   | 33 |

| Near Data Space              | 34 |

| Organization                 | 34 |

| SFR Space                    | 34 |

| Software Stack               | 43 |

| Space Width                  | 33 |

|                              |    |