# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 17                                                                           |

| Program Memory Size        | 4KB (1.375K x 24)                                                            |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04kl101-e-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-6               | : Т  | IMER   | REGIS  | TER N  | IAP    |        |        |        |        |             |                        |          |              |                  |        |         |         |               |

|-------------------------|------|--------|--------|--------|--------|--------|--------|--------|--------|-------------|------------------------|----------|--------------|------------------|--------|---------|---------|---------------|

| File Name               | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7       | Bit 6                  | Bit 5    | Bit 4        | Bit 3            | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

| TMR1                    | 0100 |        |        |        |        |        |        |        |        | Timer1 Reg  | gister                 |          |              |                  |        |         |         | 0000          |

| PR1                     | 0102 |        |        |        |        |        |        |        | Tir    | mer1 Period | Register               |          |              |                  |        |         |         | FFFF          |

| T1CON                   | 0104 | TON    | _      | TSIDL  | _      | _      | _      | T1ECS1 | T1ECS0 | _           | TGATE                  | TCKPS1   | TCKPS0       | _                | TSYNC  | TCS     | _       | 0000          |

| TMR2                    | 0106 | _      | _      | _      | _      | _      | _      | _      | _      |             |                        |          | Timer2 R     | egister          |        |         |         | 0000          |

| PR2                     | 0108 | _      | _      | _      | _      | _      | _      | _      | _      |             |                        |          | Timer2 Perio | d Register       |        |         |         | OOFF          |

| T2CON                   | 010A | _      | _      | _      | _      | _      | _      | _      | _      | _           | T2OUTPS3               | T2OUTPS2 | T2OUTPS1     | T2OUTPS0         | TMR2ON | T2CKPS1 | T2CKPS0 | 0000          |

| TMR3                    | 010C |        |        |        |        |        |        |        |        | Timer3 Reg  | gister                 |          |              |                  |        |         |         | 0000          |

| T3GCON                  | 010E | -      | —      | —      | —      | —      | —      | —      | —      | TMR3GE      | T3GPOL                 | T3GTM    | T3GSPM       | T3GGO/<br>T3DONE | T3GVAL | T3GSS1  | T3GSS0  | 0000          |

| T3CON                   | 0110 | _      | _      | _      | _      | _      | _      | _      | _      | TMR3CS1     | TMR3CS0                | T3CKPS1  | T3CKPS0      | T3OSCEN          | T3SYNC | _       | TMR3ON  | 0000          |

| TMR4 <sup>(1)</sup>     | 0112 | _      | _      | _      | _      | _      | —      | _      | _      |             | •                      | •        | Timer4 R     | egister          |        |         |         | 0000          |

| PR4 <sup>(1)</sup>      | 0114 | _      | _      | _      | _      | _      | —      | —      | _      |             |                        |          | Timer4 Perio | d Register       |        |         |         | 00FF          |

| T4CON <sup>(1)</sup>    | 0116 | _      | _      | _      | _      | _      | —      | —      | _      | _           | T4OUTPS3               | T4OUTPS2 | T4OUTPS1     | T4OUTPS0         | TMR40N | T4CKPS1 | T4CKPS0 | 0000          |

| CCPTMRS0 <sup>(1)</sup> | 013C | -      | _      | _      | _      | —      | _      | —      | _      | —           | C3TSEL0 <sup>(1)</sup> | _        | -            | C2TSEL0          | -      | _       | C1TSEL0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

#### TABLE 4-7: CCP/ECCP REGISTER MAP

|                         |      |        | -      |        |        |        |        |       |       | 1                  |                    |            |            | 1            |           |        |        |               |

|-------------------------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------------------|--------------------|------------|------------|--------------|-----------|--------|--------|---------------|

| File Name               | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7              | Bit 6              | Bit 5      | Bit 4      | Bit 3        | Bit 2     | Bit 1  | Bit 0  | All<br>Resets |

| CCP1CON                 | 0190 | _      | _      | —      | _      | _      | —      | —     | _     | PM1 <sup>(1)</sup> | PM0 <sup>(1)</sup> | DC1B1      | DC1B0      | CCP1M3       | CCP1M2    | CCP1M1 | CCP1M0 | 0000          |

| CCPR1L                  | 0192 | -      | _      | _      | _      | _      | _      | _     | _     |                    |                    | Capture/Co | ompare/PWN | M1 Register  | Low Byte  |        |        | 0000          |

| CCPR1H                  | 0194 | -      | _      | _      | _      | _      | _      | _     | _     |                    |                    | Capture/Co | mpare/PWN  | /11 Register | High Byte |        |        | 0000          |

| ECCP1DEL <sup>(1)</sup> | 0196 | -      | _      | _      | _      | _      | _      | _     | _     | PRSEN              | PDC6               | PDC5       | PDC4       | PDC3         | PDC2      | PDC1   | PDC0   | 0000          |

| ECCP1AS <sup>(1)</sup>  | 0198 | -      | _      | _      | _      | _      | _      | _     | _     | ECCPASE            | ECCPAS2            | ECCPAS1    | ECCPAS0    | PSSAC1       | PSSAC0    | PSSBD1 | PSSBD0 | 0000          |

| PSTR1CON(1)             | 019A | _      | _      | _      | _      | _      | _      | _     | _     | CMPL1              | CMPL0              | _          | STRSYNC    | STRD         | STRC      | STRB   | STRA   | 0001          |

| CCP2CON                 | 019C | _      | _      | _      | _      | _      | _      | _     | _     | _                  | _                  | DC2B1      | DC2B0      | CCP2M3       | CCP2M2    | CCP2M1 | CCP2M0 | 0000          |

| CCPR2L                  | 019E | _      | _      | _      | _      | _      | _      | _     | _     |                    |                    | Capture/Co | ompare/PWN | M2 Register  | Low Byte  |        |        | 0000          |

| CCPR2H                  | 01A0 | _      | _      | _      | _      | _      | _      | _     | _     |                    |                    | Capture/Co | ompare/PWN | /12 Register | High Byte |        |        | 0000          |

| CCP3CON <sup>(1)</sup>  | 01A8 | _      | _      | _      | _      | _      | _      | _     | _     | —                  | _                  | DC3B1      | DC3B0      | CCP3M3       | CCP3M2    | CCP3M1 | CCP3M0 | 0000          |

| CCPR3L <sup>(1)</sup>   | 01AA | _      | _      | _      | _      | _      | _      | _     | _     |                    |                    | Capture/Co | ompare/PWN | VI3 Register | Low Byte  |        |        | 0000          |

| CCPR3H <sup>(1)</sup>   | 01AC | _      |        | _      | _      | _      | —      | —     | _     |                    |                    | Capture/Co | ompare/PWN | /13 Register | High Byte |        |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

### TABLE 4-8: MSSP REGISTER MAP

| File Name               | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6   | Bit 5      | Bit 4        | Bit 3                                                    | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|---------|------------|--------------|----------------------------------------------------------|------------|-------|-------|---------------|

| SSP1BUF                 | 0200 | _      | —      | _      | _      |        | —      | —     | —     |        |         | MSSP1 F    | Receive Buff | er/Transmit                                              | Register   |       |       | 00xx          |

| SSP1CON1                | 0202 | _      | _      | _      | _      | _      | _      | _     | _     | WCOL   | SSPOV   | SSPEN      | CKP          | SSPM3                                                    | SSPM2      | SSPM1 | SSPM0 | 0000          |

| SSP1CON2                | 0204 | _      | _      | _      | _      | _      | _      | _     | _     | GCEN   | ACKSTAT | ACKDT      | ACKEN        | RCEN                                                     | PEN        | RSEN  | SEN   | 0000          |

| SSP1CON3                | 0206 | _      | _      | _      | _      | _      | _      | _     | _     | ACKTIM | PCIE    | SCIE       | BOEN         | SDAHT                                                    | SBCDE      | AHEN  | DHEN  | 0000          |

| SSP1STAT                | 0208 | _      | _      | _      | _      | _      | _      | _     | _     | SMP    | CKE     | D/Ā        | Р            | S                                                        | R/W        | UA    | BF    | 0000          |

| SSP1ADD                 | 020A | —      | _      | _      | _      | _      | —      | —     | _     |        |         |            |              | ter (I <sup>2</sup> C™ S<br>Register (I <sup>2</sup> 0   |            | ode)  |       | 0000          |

| SSP1MSK                 | 020C | _      |        | _      | _      |        | _      | _     |       |        | М       | SSP1 Addre | ess Mask R   | egister (I <sup>2</sup> C                                | Slave Mode | e)    |       | 00FF          |

| SSP2BUF <sup>(1)</sup>  | 0210 | _      |        | _      | _      |        | _      | _     |       |        |         | MSSP2 F    | Receive Buff | er/Transmit                                              | Register   |       |       | 00xx          |

| SSP2CON1(1)             | 0212 | _      |        | _      | _      |        | _      | _     |       | WCOL   | SSPOV   | SSPEN      | CKP          | SSPM3                                                    | SSPM2      | SSPM1 | SSPM0 | 0000          |

| SSP2CON2(1)             | 0214 | _      | _      | _      | _      |        | _      | _     |       | GCEN   | ACKSTAT | ACKDT      | ACKEN        | RCEN                                                     | PEN        | RSEN  | SEN   | 0000          |

| SSP2CON3(1)             | 0216 | _      | _      | _      | —      | _      | _      | _     | _     | ACKTIM | PCIE    | SCIE       | BOEN         | SDAHT                                                    | SBCDE      | AHEN  | DHEN  | 0000          |

| SSP2STAT <sup>(1)</sup> | 0218 | _      | _      | _      | _      | _      | _      | _     | _     | SMP    | CKE     | D/Ā        | Р            | S                                                        | R/W        | UA    | BF    | 0000          |

| SSP2ADD <sup>(1)</sup>  | 021A | _      | _      | _      | _      | _      | —      | _     | —     |        | MSS     |            |              | ster (I <sup>2</sup> C Sla<br>Register (I <sup>2</sup> C |            | ode)  |       | 0000          |

| SSP2MSK <sup>(1)</sup>  | 021C | _      | -      | _      | _      | _      | _      | _     |       |        | М       | SSP2 Addre | ess Mask R   | egister (I <sup>2</sup> C                                | Slave Mode | e)    |       | 00FF          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

#### TABLE 4-9: UART REGISTER MAP

| IADLL 4      | <b>J</b> . | UANT     |        |          |        |        |        |         |            |               |          |       |            |         |        |        |       |               |

|--------------|------------|----------|--------|----------|--------|--------|--------|---------|------------|---------------|----------|-------|------------|---------|--------|--------|-------|---------------|

| File<br>Name | Addr       | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8      | Bit 7         | Bit 6    | Bit 5 | Bit 4      | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE       | 0220       | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1    | UEN0       | WAKE          | LPBACK   | ABAUD | RXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222       | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF   | TRMT       | URXISEL1      | URXISEL0 | ADDEN | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224       | _        | _      | _        | _      | _      |        | _       |            |               |          | UART1 | Transmit R | egister |        |        |       | xxxx          |

| U1RXREG      | 0226       | _        | _      | _        | _      | _      |        | _       |            |               |          | UART1 | Receive Re | egister |        |        |       | 0000          |

| U1BRG        | 0228       |          |        |          |        |        |        | Baud Ra | ate Genera | tor Prescaler | Register |       |            |         |        |        |       | 0000          |

| U2MODE       | 0230       | UARTEN   | _      | USIDL    | IREN   | RTSMD  |        | UEN1    | UEN0       | WAKE          | LPBACK   | ABAUD | RXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232       | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF   | TRMT       | URXISEL1      | URXISEL0 | ADDEN | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234       | _        | _      | _        | _      | _      |        | _       |            |               |          | UART2 | Transmit R | egister |        |        |       | xxxx          |

| U2RXREG      | 0236       | _        | _      | _        | _      | _      |        | _       |            |               |          | UART2 | Receive Re | egister |        |        |       | 0000          |

| U2BRG        | 0238       |          |        |          |        |        |        | Baud Ra | ate Genera | tor Prescaler | Register |       |            |         |        |        |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 7.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 7-3. Note that the System Reset Signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| Reset Type         | Clock Source | SYSRST Delay | System Clock<br>Delay | Notes      |

|--------------------|--------------|--------------|-----------------------|------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT | —                     | 1, 2       |

|                    | FRC, FRCDIV  | TPOR + TPWRT | TFRC                  | 1, 2, 3    |

|                    | LPRC         | TPOR + TPWRT | TLPRC                 | 1, 2, 3    |

|                    | ECPLL        | TPOR + TPWRT | Тьоск                 | 1, 2, 4    |

|                    | FRCPLL       | TPOR + TPWRT | TFRC + TLOCK          | 1, 2, 3, 4 |

|                    | XT, HS, SOSC | TPOR+ TPWRT  | Тоѕт                  | 1, 2, 5    |

|                    | XTPLL, HSPLL | TPOR + TPWRT | TOST + TLOCK          | 1, 2, 4, 5 |

| BOR                | EC           | TPWRT        | —                     | 2          |

|                    | FRC, FRCDIV  | TPWRT        | TFRC                  | 2, 3       |

|                    | LPRC         | TPWRT        | TLPRC                 | 2, 3       |

|                    | ECPLL        | TPWRT        | Тьоск                 | 2, 4       |

|                    | FRCPLL       | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

|                    | XT, HS, SOSC | TPWRT        | Тоѕт                  | 2, 5       |

|                    | XTPLL, HSPLL | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

| All Others         | Any Clock    | _            | —                     | None       |

### TABLE 7-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

Note 1: TPOR = Power-on Reset delay.

2: TPWRT = 64 ms nominal if the Power-up Timer is enabled; otherwise, it is zero.

3: TFRC and TLPRC = RC oscillator start-up times.

**4:** TLOCK = PLL lock time.

**5:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

**6:** If Two-Speed Start-up is enabled, regardless of the primary oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

Note: For detailed operating frequency and timing specifications, see Section 26.0 "Electrical Characteristics".

#### 8.3 Interrupt Control and Status Registers

Depending on the particular device, the PIC24F16KL402 family of devices implements up to 28 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS5

- IEC0 through IEC5

- IPC0 through IPC7, ICP9, IPC12, ICP16, ICP18 and IPC20

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIV table.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence listed in Table 8-2. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. The INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits are in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user may change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit, which together with the IPL<2:0> bits, also indicates the current CPU priority level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All interrupt registers are described in Register 8-3 through Register 8-30, in the following sections.

#### REGISTER 8-1: SR: ALU STATUS REGISTER

| U-0                   | U-0                   | U-0                   | U-0               | U-0                      | U-0               | U-0              | R/W-0             |

|-----------------------|-----------------------|-----------------------|-------------------|--------------------------|-------------------|------------------|-------------------|

| —                     |                       | _                     | —                 | —                        | —                 |                  | DC <sup>(1)</sup> |

| bit 15                |                       |                       |                   |                          |                   |                  | bit 8             |

|                       |                       |                       |                   |                          |                   |                  |                   |

| R/W-0                 | R/W-0                 | R/W-0                 | R-0               | R/W-0                    | R/W-0             | R/W-0            | R/W-0             |

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup>         | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup>  |

| bit 7                 |                       |                       |                   | •                        |                   |                  | bit 0             |

|                       |                       |                       |                   |                          |                   |                  |                   |

| Legend:               |                       |                       |                   |                          |                   |                  |                   |

| R = Readab            | le bit                | W = Writable          | bit               | U = Unimplem             | nented bit, read  | d as '0'         |                   |

| -n = Value a          | t POR                 | '1' = Bit is set      |                   | '0' = Bit is clea        | ared              | x = Bit is unkr  | nown              |

|                       |                       |                       |                   |                          |                   |                  |                   |

| bit 15-9              | Unimplemen            | ted: Read as 'o       | )'                |                          |                   |                  |                   |

| bit 7-5               | IPL<2:0>: CF          | PU Interrupt Price    | ority Level Stat  | us bits <sup>(2,3)</sup> |                   |                  |                   |

|                       | 111 = CPU lr          | nterrupt Priority     | Level is 7 (15)   | user interrupts          | s disabled        |                  |                   |

|                       |                       | nterrupt Priority     | • • •             |                          |                   |                  |                   |

|                       |                       | nterrupt Priority     | ( )               |                          |                   |                  |                   |

|                       |                       | nterrupt Priority     |                   |                          |                   |                  |                   |

|                       |                       | nterrupt Priority     | • • •             |                          |                   |                  |                   |

|                       |                       | nterrupt Priority     |                   |                          |                   |                  |                   |

|                       |                       | nterrupt Priority     | • • •             |                          |                   |                  |                   |

|                       |                       | nterrunt Priority     | ( )               |                          |                   |                  |                   |

- 000 = CPU Interrupt Priority Level is 0 (8)

- **Note 1:** See Register 3-1 for the description of these bits, which are not dedicated to interrupt control functions.

- **2:** The IPL bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

- 3: The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

Note: Bit 8 and bits 4 through 0 are described in Section 3.0 "CPU".

### REGISTER 8-19: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0          | R/W-1                   | R/W-0                                                   | R/W-0            | U-0              | U-0             | U-0             | U-0   |

|--------------|-------------------------|---------------------------------------------------------|------------------|------------------|-----------------|-----------------|-------|

| _            | U1RXIP2                 | U1RXIP1                                                 | U1RXIP0          |                  | _               | _               |       |

| bit 15       |                         |                                                         | L                |                  | l               |                 | bit 8 |

|              |                         |                                                         |                  |                  |                 |                 |       |

| U-0          | U-0                     | U-0                                                     | U-0              | U-0              | R/W-1           | R/W-0           | R/W-0 |

| _            | —                       | —                                                       | —                | _                | T3IP2           | T3IP1           | T3IP0 |

| bit 7        |                         |                                                         | •                |                  |                 |                 | bit 0 |

|              |                         |                                                         |                  |                  |                 |                 |       |

| Legend:      |                         |                                                         |                  |                  |                 |                 |       |

| R = Readab   | le bit                  | W = Writable                                            | bit              | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value a | t POR                   | '1' = Bit is set                                        |                  | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| bit 14-12    |                         | >: UART1 Rece<br>pt is Priority 7 (<br>pt is Priority 1 | •                |                  |                 |                 |       |

|              | 000 = Interru           | pt source is dis                                        |                  |                  |                 |                 |       |

| bit 11-3     | •                       | ted: Read as '                                          |                  |                  |                 |                 |       |

| bit 2-0      | T3IP<2:0>: ⊺            | imer3 Interrupt                                         | Priority bits    |                  |                 |                 |       |

|              | 111 = Interru<br>•<br>• | pt is Priority 7(                                       | highest priority | interrupt)       |                 |                 |       |

|              | •                       |                                                         |                  |                  |                 |                 |       |

| U-0              | R/W-1                                                                                               | R/W-0                                                                                              | R/W-0                                                           | U-0                            | R/W-1                  | R/W-0                  | R/W-0                  |

|------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------|------------------------|------------------------|------------------------|

| _                | U2TXIP2 <sup>(1)</sup>                                                                              | U2TXIP1 <sup>(1)</sup>                                                                             | U2TXIP0 <sup>(1)</sup>                                          | —                              | U2RXIP2 <sup>(1)</sup> | U2RXIP1 <sup>(1)</sup> | U2RXIP0 <sup>(1)</sup> |

| bit 15           |                                                                                                     |                                                                                                    |                                                                 |                                |                        |                        | bit                    |

|                  |                                                                                                     |                                                                                                    |                                                                 |                                |                        |                        |                        |

| U-0              | R/W-1                                                                                               | R/W-0                                                                                              | R/W-0                                                           | U-0                            | U-0                    | U-0                    | U-0                    |

|                  | INT2IP2                                                                                             | INT2IP1                                                                                            | INT2IP0                                                         | _                              | —                      | _                      |                        |

| bit 7            |                                                                                                     |                                                                                                    |                                                                 |                                |                        |                        | bit (                  |

| Legend:          |                                                                                                     |                                                                                                    |                                                                 |                                |                        |                        |                        |

| R = Readat       | ole bit                                                                                             | W = Writable I                                                                                     | oit                                                             | U = Unimpler                   | nented bit, read       | as '0'                 |                        |

| -n = Value a     |                                                                                                     | '1' = Bit is set                                                                                   |                                                                 | '0' = Bit is clea              |                        | x = Bit is unkn        | own                    |

|                  |                                                                                                     |                                                                                                    |                                                                 |                                |                        |                        | -                      |

| bit 15           | Unimplemen                                                                                          | ted: Read as 'o                                                                                    | )'                                                              |                                |                        |                        |                        |

| bit 14-12        | U2TXIP<2:0>                                                                                         | : UART2 Trans                                                                                      | mitter Interrup                                                 | t Priority bits <sup>(1)</sup> |                        |                        |                        |

|                  | 111 = Interrup                                                                                      | ot is Priority 7 (I                                                                                | nighest priority                                                | interrupt)                     |                        |                        |                        |

|                  | •                                                                                                   |                                                                                                    |                                                                 |                                |                        |                        |                        |

|                  | •                                                                                                   |                                                                                                    |                                                                 |                                |                        |                        |                        |

|                  | 001 = Interrup                                                                                      | ot is Priority 1                                                                                   |                                                                 |                                |                        |                        |                        |

|                  |                                                                                                     | ot source is disa                                                                                  | abled                                                           |                                |                        |                        |                        |

| bit 11           | Unimplemen                                                                                          | ted: Read as 'o                                                                                    | )'                                                              |                                |                        |                        |                        |

| bit 10-8         | U2RXIP<2:0>                                                                                         | : UART2 Rece                                                                                       | iver Interrupt F                                                | Priority bits <sup>(1)</sup>   |                        |                        |                        |

|                  | 111 = Interrup                                                                                      | ot is Priority 7 (I                                                                                | nighest priority                                                | interrupt)                     |                        |                        |                        |

|                  | •                                                                                                   |                                                                                                    |                                                                 |                                |                        |                        |                        |

|                  | •                                                                                                   |                                                                                                    |                                                                 |                                |                        |                        |                        |

|                  | •                                                                                                   |                                                                                                    |                                                                 |                                |                        |                        |                        |

|                  | •<br>001 = Interrup                                                                                 |                                                                                                    |                                                                 |                                |                        |                        |                        |

|                  | 000 = Interru                                                                                       | ot source is disa                                                                                  |                                                                 |                                |                        |                        |                        |

| bit 7            | 000 = Interru<br>Unimplemen                                                                         | ot source is disa<br>ted: Read as 'o                                                               | )'                                                              |                                |                        |                        |                        |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>:                                                         | ot source is disa<br>ted: Read as 'o<br>External Intern                                            | <sup>)'</sup><br>upt 2 Priority b                               |                                |                        |                        |                        |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>:                                                         | ot source is disa<br>ted: Read as 'o                                                               | <sup>)'</sup><br>upt 2 Priority b                               |                                |                        |                        |                        |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>:                                                         | ot source is disa<br>ted: Read as 'o<br>External Intern                                            | <sup>)'</sup><br>upt 2 Priority b                               |                                |                        |                        |                        |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>:                                                         | ot source is disa<br>ted: Read as 'o<br>External Intern                                            | <sup>)'</sup><br>upt 2 Priority b                               |                                |                        |                        |                        |

|                  | 000 = Interrup<br>Unimplement<br>INT2IP<2:0>:<br>111 = Interrup<br>•<br>•<br>001 = Interrup         | ot source is disa<br>ted: Read as 'o<br>External Intern<br>ot is Priority 7 (I<br>ot is Priority 1 | <sub>)</sub> '<br>upt 2 Priority b<br>nighest priority          |                                |                        |                        |                        |

|                  | 000 = Interrup<br>Unimplement<br>INT2IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup | ot source is disa<br>ted: Read as 'c<br>External Intern<br>ot is Priority 7 (I                     | <sub>)</sub> '<br>upt 2 Priority b<br>nighest priority<br>abled |                                |                        |                        |                        |

#### REGISTER 8-24: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

#### REGISTER 8-30: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| R-0           | r-0                                     | R/W-0                                                                         | U-0                           | R-0                              | R-0                                                                           | R-0                                    | R-0            |

|---------------|-----------------------------------------|-------------------------------------------------------------------------------|-------------------------------|----------------------------------|-------------------------------------------------------------------------------|----------------------------------------|----------------|

| CPUIRQ        | r                                       | VHOLD                                                                         | —                             | ILR3                             | ILR2                                                                          | ILR1                                   | ILR0           |

| bit 15        |                                         |                                                                               |                               | •                                |                                                                               | ·                                      | bit 8          |

|               |                                         |                                                                               |                               |                                  |                                                                               |                                        |                |

| U-0           |                                         | R-0                                                                           |                               |                                  |                                                                               |                                        |                |

|               | VECNUM6                                 | VECNUM5                                                                       | VECNUM4                       | VECNUM3                          | VECNUM2                                                                       | VECNUM1                                | VECNUM0        |

| bit 7         |                                         |                                                                               |                               |                                  |                                                                               |                                        | bit (          |

| Legend:       |                                         | r = Reserved                                                                  | bit                           |                                  |                                                                               |                                        |                |

| R = Readable  | e bit                                   | W = Writable                                                                  | bit                           | U = Unimpler                     | nented bit, read                                                              | as '0'                                 |                |

| -n = Value at | POR                                     | '1' = Bit is set                                                              |                               | '0' = Bit is cle                 |                                                                               | x = Bit is unkr                        | nown           |

| bit 14        | 0 = No interr                           | vhen the CPU p<br>upt request is le<br>aintain as '0'                         |                               |                                  | errupt priority)                                                              |                                        |                |

| bit 14        | Reserved: M                             |                                                                               |                               | 0                                |                                                                               |                                        |                |

| bit 13        | VHOLD: Vect                             | tor Hold bit                                                                  |                               |                                  |                                                                               |                                        |                |

|               | 1 = VECNUN<br>current in<br>0 = VECNUN  | //<6:0> will cor<br>nterrupt<br>//<6:0> will con                              | tain the value                | e of the highe<br>of the last Ac | rupt is Stored in<br>st priority pend<br>knowledged inte<br>ther interrupts a | ling interrupt, i<br>errupt (last inte | instead of the |

| bit 12        | Unimplemen                              | ted: Read as '                                                                | )'                            |                                  |                                                                               |                                        |                |

| bit 11-8      | 1111 = CPU<br>•<br>•<br>•<br>0001 = CPU | w CPU Interrup<br>Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit | y Level is 15<br>y Level is 1 | el bits                          |                                                                               |                                        |                |

| bit 7         | Unimplemen                              | ted: Read as '                                                                | )'                            |                                  |                                                                               |                                        |                |

| bit 6-0       | VECNUM<6:                               | 0>: Vector Num                                                                | ber of Pendin                 | g Interrupt bits                 | 5                                                                             |                                        |                |

|               | 0111111 = Ir<br>•<br>•                  | nterrupt vector p                                                             | pending is Nu                 | mber 135                         |                                                                               |                                        |                |

|               |                                         | nterrupt vector p<br>nterrupt vector p                                        |                               |                                  |                                                                               |                                        |                |

### 8.4 Interrupt Setup Procedures

#### 8.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS Control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and the type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits, for all enabled interrupt sources, may be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized, such that all user interrupt sources are assigned to Priority Level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 8.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (i.e., C or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

### 8.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 8.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, OEh, with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period. Level 7 interrupt sources are not disabled by the DISI instruction.

# 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

PIC24F16KL402 family devices consist of two types of secondary oscillators:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

- Fast Internal RC (FRC) Oscillator

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

- Low-Power Internal RC (LPRC) Oscillator with two modes:

- High-Power/High-Accuracy mode

- Low-Power/Low-Accuracy mode

The primary oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, Fcy. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clock, Fosc/2, can be provided on the OSCO I/O pin for some operating modes of the primary oscillator.

# 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (for more information, see Section 23.2 "Configuration Bits"). The Primary Configuration bits, Oscillator POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The secondary oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC mode Frequency Range Configuration bits. POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is "frequency range is greater than 8 MHz".

The Configuration bits allow users to choose between the various clock modes, shown in Table 9-1.

### 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSMx Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                      | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|------------------------------------------------------|-------------------|-------------|------------|-------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| 500 kHz FRC Oscillator with Postscaler<br>(LPFRCDIV) | Internal          | 11          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                       | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator (SOSC)                 | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (HS) with PLL Module (HSPLL)      | Primary           | 10          | 011        |       |

| Primary Oscillator (EC) with PLL Module (ECPLL)      | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                              | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                              | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                              | Primary           | 00          | 010        |       |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| 8 MHz FRC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC oscillator. OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step-size is an approximation and is neither characterized nor tested.

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <b><sup>(2)</sup></b> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|--------------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                           | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                                |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit |                            |                    |  |  |  |

|----------------------------|---------------------------------------|----------------------------|--------------------|--|--|--|

| HS = Hardware Settable bit | CO = Clearable Only bit               | SO = Settable Only bit     |                    |  |  |  |

| R = Readable bit           | W = Writable bit                      | U = Unimplemented bit, rea | d as '0'           |  |  |  |

| -n = Value at POR          | '1' = Bit is set                      | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

#### bit 15 Unimplemented: Read as '0'

#### bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = 8 MHz FRC Oscillator (FRC)

- bit 11 Unimplemented: Read as '0'

#### bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(1)</sup>

- 111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = 8 MHz FRC Oscillator (FRC)

#### **Note 1:** Reset values for these bits are determined by the FNOSC<2:0> Configuration bits.

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- **3:** When SOSC is selected to run from a digital clock input rather than an external crystal (SOSCSRC = 0), this bit has no effect.

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                          | U-0                                                                                     | U-0                                                | U-0                                       |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------|--|

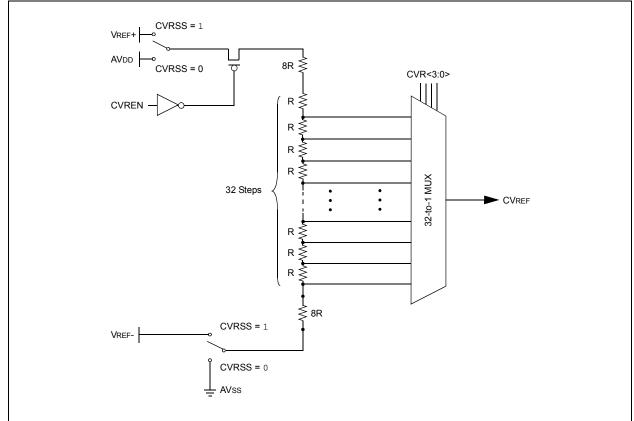

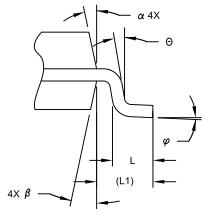

| _            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                              | <u> </u>                                                                                |                                                    | —                                         |  |