Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Detans                     |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 17                                                                           |

| Program Memory Size        | 4KB (1.375K x 24)                                                            |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 20-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04kl101-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                             | 9   |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers |     |

| 3.0   | СРИ                                                         |     |

| 4.0   | Memory Organization                                         | 31  |

| 5.0   | Flash Program Memory                                        | 47  |

| 6.0   | Data EEPROM Memory                                          | 53  |

| 7.0   | Resets                                                      | 59  |

| 8.0   | Interrupt Controller                                        | 65  |

| 9.0   | Oscillator Configuration                                    |     |

| 10.0  | Power-Saving Features                                       | 105 |

| 11.0  | I/O Ports                                                   | 111 |

| 12.0  | Timer1                                                      | 115 |

| 13.0  | Timer2 Module                                               | 117 |

| 14.0  | Timer3 Module                                               | 119 |

| 15.0  |                                                             |     |

| 16.0  | Capture/Compare/PWM (CCP) and Enhanced CCP Modules          | 125 |

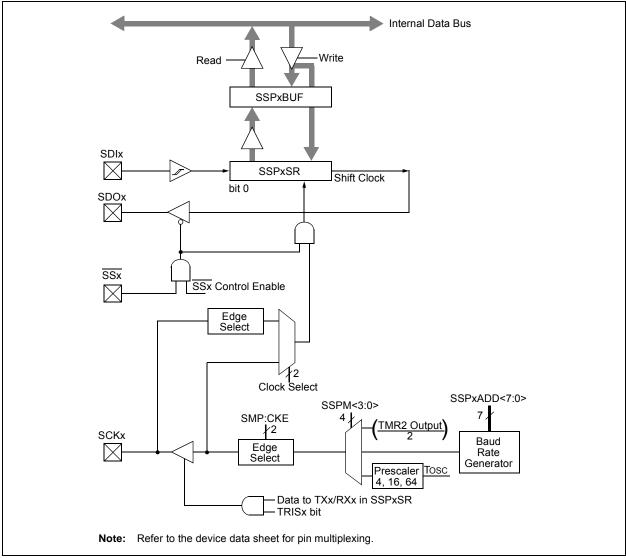

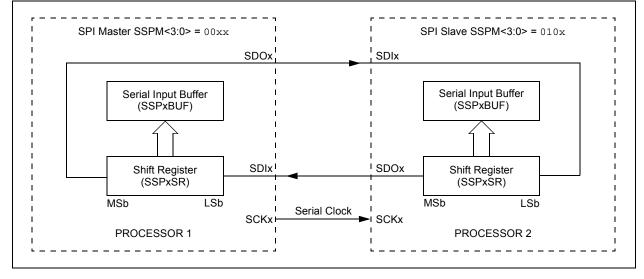

| 17.0  | Master Synchronous Serial Port (MSSP)                       | 135 |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)          | 149 |

| 19.0  | 10-Bit High-Speed A/D Converter                             | 157 |

| 20.0  |                                                             |     |

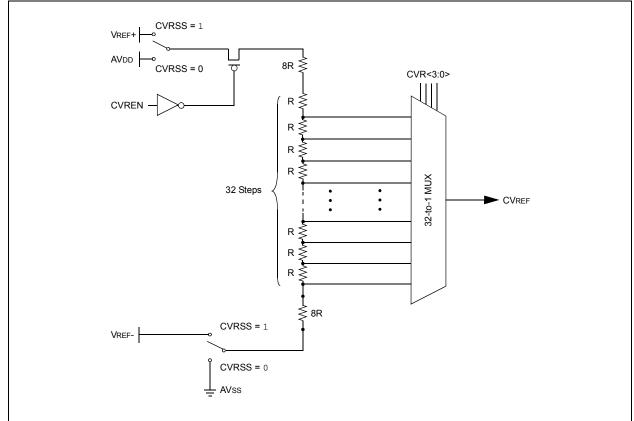

| 21.0  | Comparator Voltage Reference                                | 171 |

| 22.0  | High/Low-Voltage Detect (HLVD)                              | 173 |

| 23.0  | Special Features                                            | 175 |

| 24.0  | Development Support                                         | 187 |

| 25.0  | Instruction Set Summary                                     | 191 |

| 26.0  |                                                             |     |

| 27.0  | Packaging Information                                       | 225 |

| Appe  | endix A: Revision History                                   | 251 |

| Appe  | endix B: Migrating from PIC18/PIC24 to PIC24F16KL402        | 251 |

| Index | x                                                           | 253 |

| The I | Microchip Web Site                                          | 257 |

| Cust  | omer Change Notification Service                            |     |

| Cust  | omer Support                                                | 257 |

| Prod  | uct Identification System                                   | 259 |

|          |                                  | Pin N         | umber                             |               |     |                   |                                                     |  |  |

|----------|----------------------------------|---------------|-----------------------------------|---------------|-----|-------------------|-----------------------------------------------------|--|--|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | I/O | Buffer            | Description                                         |  |  |

| AN0      | 2                                | 19            | 2                                 | 27            | I   | ANA               | A/D Analog Inputs. Not available on PIC24F16KL30X   |  |  |

| AN1      | 3                                | 20            | 3                                 | 28            | I   | ANA               | family devices.                                     |  |  |

| AN2      | 4                                | 1             | 4                                 | 1             | I   | ANA               |                                                     |  |  |

| AN3      | 5                                | 2             | 5                                 | 2             | I   | ANA               |                                                     |  |  |

| AN4      | 6                                | 3             | 6                                 | 3             | Ι   | ANA               |                                                     |  |  |

| AN5      | _                                | _             | 7                                 | 4             | Ι   | ANA               |                                                     |  |  |

| AN9      | 18                               | 15            | 26                                | 23            | I   | ANA               |                                                     |  |  |

| AN10     | 17                               | 14            | 25                                | 22            | Ι   | ANA               |                                                     |  |  |

| AN11     | 16                               | 13            | 24                                | 21            | Ι   | ANA               |                                                     |  |  |

| AN12     | 15                               | 12            | 23                                | 20            | Ι   | ANA               |                                                     |  |  |

| AN13     | 7                                | 4             | 9                                 | 6             | Ι   | ANA               |                                                     |  |  |

| AN14     | 8                                | 5             | 10                                | 7             | I   | ANA               |                                                     |  |  |

| AN15     | 9                                | 6             | 11                                | 8             | I   | ANA               |                                                     |  |  |

| ASCL1    | _                                | _             | 15                                | 12            | I/O | I <sup>2</sup> C™ | Alternate MSSP1 I <sup>2</sup> C Clock Input/Output |  |  |

| ASDA1    | _                                | _             | 14                                | 11            | I/O | l <sup>2</sup> C  | Alternate MSSP1 I <sup>2</sup> C Data Input/Output  |  |  |

| AVdd     | 20                               | 17            | 28                                | 25            | Ι   | ANA               | Positive Supply for Analog modules                  |  |  |

| AVss     | 19                               | 16            | 27                                | 24            | Ι   | ANA               | Ground Reference for Analog modules                 |  |  |

| CCP1     | 14                               | 11            | 20                                | 17            | I/O | ST                | CCP1/ECCP1 Capture Input/Compare and PWM<br>Output  |  |  |

| CCP2     | 15                               | 12            | 23                                | 20            | I/O | ST                | CCP2 Capture Input/Compare and PWM Output           |  |  |

| CCP3     | 13                               | 10            | 19                                | 16            | I/O | ST                | CCP3 Capture Input/Compare and PWM Output           |  |  |

| C1INA    | 8                                | 5             | 7                                 | 4             | I   | ANA               | Comparator 1 Input A (+)                            |  |  |

| C1INB    | 7                                | 4             | 6                                 | 3             | I   | ANA               | Comparator 1 Input B (-)                            |  |  |

| C1INC    | 5                                | 2             | 5                                 | 2             | I   | ANA               | Comparator 1 Input C (+)                            |  |  |

| C1IND    | 4                                | 1             | 4                                 | 1             | I   | ANA               | Comparator 1 Input D (-)                            |  |  |

| C1OUT    | 17                               | 14            | 25                                | 22            | 0   | _                 | Comparator 1 Output                                 |  |  |

| C2INA    | 5                                | 2             | 5                                 | 2             | I   | ANA               | Comparator 2 Input A (+)                            |  |  |

| C2INB    | 4                                | 1             | 4                                 | 1             | I   | ANA               | Comparator 2 Input B (-)                            |  |  |

| C2INC    | 8                                | 5             | 7                                 | 4             | Ι   | ANA               | Comparator 2 Input C (+)                            |  |  |

| C2IND    | 7                                | 4             | 6                                 | 3             | Ι   | ANA               | Comparator 2 Input D (-)                            |  |  |

| C2OUT    | 14                               | 11            | 20                                | 17            | 0   |                   | Comparator 2 Output                                 |  |  |

| CLK I    | 7                                | 4             | 9                                 | 6             | Ι   | ANA               | Main Clock Input                                    |  |  |

| CLKO     | 8                                | 5             | 10                                | 7             | 0   | _                 | System Clock Output                                 |  |  |

#### TABLE 1-4: PIC24F16KL40X/30X FAMILY PINOUT DESCRIPTIONS

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

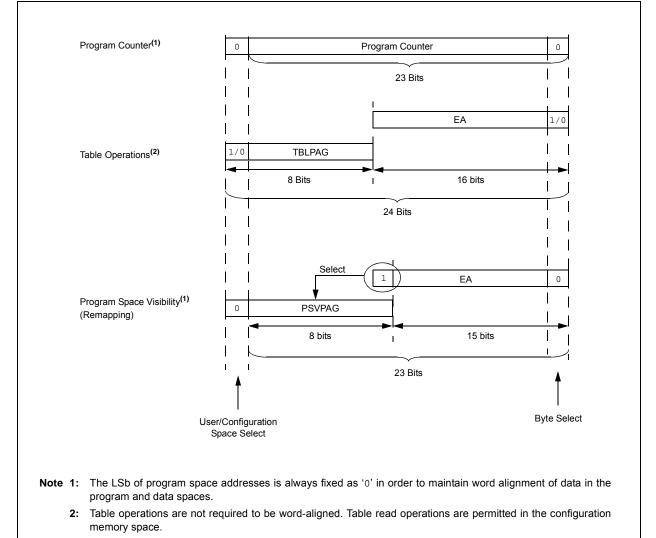

| A                        | Access        | Program Space Address        |           |                          |                    |                |  |

|--------------------------|---------------|------------------------------|-----------|--------------------------|--------------------|----------------|--|

| Access Type              | Space         | <23>                         | <22:16>   | <15>                     | <14:1>             | <0>            |  |

| Instruction Access       | User          | 0                            |           | PC<22:1>                 |                    | 0              |  |

| (Code Execution)         |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |                          |                    |                |  |

| TBLRD/TBLWT              | User          | TBLPAG<7:0>                  |           | Data EA<15:0>            |                    |                |  |

| (Byte/Word Read/Write)   |               | د0                           | xxx xxxx  | XXXX XXXX XXXX XXXX      |                    |                |  |

|                          | Configuration | TBLPAG<7:0>                  |           | Data EA<15:0>            |                    |                |  |

|                          |               | 12                           | xxx xxxx  | XXXX XXXX XXXX XXXX      |                    |                |  |

| Program Space Visibility | User          | 0 PSVPAG<7:                  |           | 7:0>(2) Data EA<14:0>(1) |                    | :0> <b>(1)</b> |  |

| (Block Remap/Read)       |               | 0                            | xxxx xxxx |                          | xxx xxxx xxxx xxxx |                |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) on PIC24F16KL402 family devices.

### 6.0 DATA EEPROM MEMORY

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information on Data       |

|       | EEPROM, refer to the "dsPIC33/PIC24        |

|       | Family Reference Manual", "Data            |

|       | EEPROM" (DS39720).                         |

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFFFh. For PIC24FXXKL4XX devices, the size of the data EEPROM is 256 words (7FFE00h to 7FFFFh). For PIC24FXXKL3XX devices, the size of the data EEPROM is 128 words (7FFF0h to 7FFFFh). The data EEPROM is not implemented in PIC24F08KL20X or PIC24F04KL10X devices.

The data EEPROM is organized as 16-bit wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

### 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle, and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

### 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

| //Disable Interrupts For 5 instructions |       |  |  |  |  |  |

|-----------------------------------------|-------|--|--|--|--|--|

| asm volatile("disi #5");                |       |  |  |  |  |  |

| //Issue Unlock Sequence                 |       |  |  |  |  |  |

| asm volatile ("mov #0x55, W0            | \n"   |  |  |  |  |  |

| "mov W0, NVMKEY                         | \n"   |  |  |  |  |  |

| "mov #0xAA, W1                          | \n"   |  |  |  |  |  |

| "mov W1, NVMKEY                         | \n"); |  |  |  |  |  |

| // Perform Write/Erase operation        | S     |  |  |  |  |  |

| asm volatile ("bset NVMCON, #WR         | \n"   |  |  |  |  |  |

| "nop                                    | \n"   |  |  |  |  |  |

| "nop                                    | \n"); |  |  |  |  |  |

### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

### 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC oscillator. OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step-size is an approximation and is neither characterized nor tested.

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <b><sup>(2)</sup></b> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|--------------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                           | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                                |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit |                            |                    |  |  |  |

|----------------------------|---------------------------------------|----------------------------|--------------------|--|--|--|

| HS = Hardware Settable bit | CO = Clearable Only bit               | SO = Settable Only bit     |                    |  |  |  |

| R = Readable bit           | W = Writable bit                      | U = Unimplemented bit, rea | d as '0'           |  |  |  |

| -n = Value at POR          | '1' = Bit is set                      | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

#### bit 15 Unimplemented: Read as '0'

#### bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = 8 MHz FRC Oscillator (FRC)

- bit 11 Unimplemented: Read as '0'

#### bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(1)</sup>

- 111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = 8 MHz FRC Oscillator (FRC)

#### **Note 1:** Reset values for these bits are determined by the FNOSC<2:0> Configuration bits.

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- **3:** When SOSC is selected to run from a digital clock input rather than an external crystal (SOSCSRC = 0), this bit has no effect.

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7   | CLKLOCK: Clock Selection Lock Enable bit                                                 |

|---------|------------------------------------------------------------------------------------------|

|         | <u>If FSCM is Enabled (FCKSM1 = 1):</u>                                                  |

|         | 1 = Clock and PLL selections are locked                                                  |

|         | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit |

|         | If FSCM is Disabled (FCKSM1 = 0):                                                        |

|         | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.  |

| bit 6   | Unimplemented: Read as '0'                                                               |

| bit 5   | LOCK: PLL Lock Status bit <sup>(2)</sup>                                                 |

|         | 1 = PLL module is in lock or the PLL module start-up timer is satisfied                  |

|         | 0 = PLL module is out of lock, the PLL start-up timer is running or PLL is disabled      |

| bit 4   | Unimplemented: Read as '0'                                                               |

| bit 3   | CF: Clock Fail Detect bit                                                                |

|         | 1 = FSCM has detected a clock failure                                                    |

|         | 0 = No clock failure has been detected                                                   |

| bit 2   | SOSCDRV: Secondary Oscillator Drive Strength bit <sup>(3)</sup>                          |

|         | 1 = High-power SOSC circuit is selected                                                  |

|         | 0 = Low/high-power select is done via the SOSCSRC Configuration bit                      |

| bit 1   | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                    |

|         | 1 = Enables secondary oscillator                                                         |

|         | 0 = Disables secondary oscillator                                                        |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                      |

|         | 1 = Initiates an oscillator switch to the clock source specified by the NOSC<2:0> bits   |

|         | 0 = Oscillator switch is complete                                                        |

| Note 1: | Reset values for these bits are determined by the FNOSC<2:0> Configuration bits.         |

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- **3:** When SOSC is selected to run from a digital clock input rather than an external crystal (SOSCSRC = 0), this bit has no effect.

#### REGISTER 11-1: ANSA: PORTA ANALOG SELECTION REGISTER

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —      | —   |     |     |     |     |     | —     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | ANSA3 | ANSA2 | ANSA1 | ANSA0 |

| bit 7 |     |     |     |       |       |       | bit 0 |

## Legend:

bit 3-0

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

ANSA<3:0>: Analog Select Control bits

1 = Digital input buffer is not active (use for analog input)

0 = Digital input buffer is active

#### REGISTER 11-2: ANSB: PORTB ANALOG SELECTION REGISTER

| R/W-1  | R/W-1  | R/W-1                 | R/W-1                 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|-----------------------|-----------------------|-----|-----|-----|-------|

| ANSB15 | ANSB14 | ANSB13 <sup>(1)</sup> | ANSB12 <sup>(1)</sup> | —   | —   | —   | —     |

| bit 15 |        | •                     |                       |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1                | R/W-1                | R/W-1                | R/W-1                |

|-------|-----|-----|-------|----------------------|----------------------|----------------------|----------------------|

| _     | —   | —   | ANSB4 | ANSB3 <sup>(2)</sup> | ANSB2 <sup>(1)</sup> | ANSB1 <sup>(1)</sup> | ANSB0 <sup>(1)</sup> |

| bit 7 |     |     |       |                      |                      |                      | bit 0                |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-12 | ANSB<15:12>: Analog Select Control bits <sup>(1)</sup><br>1 = Digital input buffer is not active (use for analog input)<br>0 = Digital input buffer is active |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-5  | Unimplemented: Read as '0'                                                                                                                                    |

| bit 4-0   | ANSB<4:0>: Analog Select Control bits <sup>(2)</sup>                                                                                                          |

|           | <ul><li>1 = Digital input buffer is not active (use for analog input)</li><li>0 = Digital input buffer is active</li></ul>                                    |

|           |                                                                                                                                                               |

**Note 1:** ANSB<13:12,2:0> are unimplemented on 14-pin devices.

2: ANSB<3> is unimplemented on 14-pin and 20-pin devices.

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                     | U-0                                                                                     | U-0                                                | U-0                                       |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------|--|

| _            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                         | <u> </u>                                                                                |                                                    | —                                         |  |

| bit 15       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                                         |                                                    | bit 8                                     |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                                         |                                                    |                                           |  |

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                   | R/W-0                                                                                   | R/W-0                                              | R/W-0                                     |  |

|              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DCxB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DCxB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CCPxM3 <sup>(1)</sup>                                                                                                                   | CCPxM2 <sup>(1)</sup>                                                                   | CCPxM1 <sup>(1)</sup>                              | CCPxM0 <sup>(1)</sup>                     |  |

| bit 7        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                                         |                                                    | bit (                                     |  |

| Legend:      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                                         |                                                    |                                           |  |