Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 17                                                                           |

| Program Memory Size        | 4KB (1.375K x 24)                                                            |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04kl101-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ .

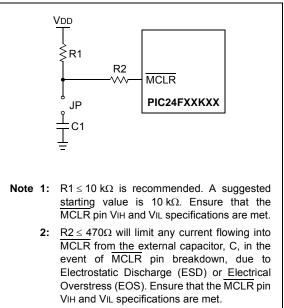

### 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

| Start<br>Addr | Bit 15                                                                                                                                                                                                                                                                                                                                                    | Bit 14                     | Bit 13                                | Bit 12                                           | Bit 11                                                      | Bit 10                                                                 | Bit 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit 8                                                                                       | Bit 7                                                                                                 | Bit 6                                                                                                           | Bit 5                                                                                                                                | Bit 4                                                                                                                    | Bit 3                                                                                                                                         | Bit 2                                                                                                                                        | Bit 1                                                                                                                                       | Bit 0                                                                                                                 | All<br>Resets                                                                                                                               |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------|--------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0000          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 0                                                                                            |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 0002          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 1                                                                                            |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 0004          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 2                                                                                            |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 0006          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 3                                                                                            |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 8000          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 4                                                                                            |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 000A          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 5                                                                                            |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 000C          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 6                                                                                            |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 000E          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 7                                                                                            |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 0010          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 8                                                                                            |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 0012          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 9                                                                                            |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 0014          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 10                                                                                           |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 0016          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 11                                                                                           |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 0018          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 12                                                                                           |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 001A          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 13                                                                                           |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 001C          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Working                                                                                     | Register 14                                                                                           |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 001E          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Vorking Regis                                                                               | ter 15                                                                                                |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             | _                                                                                                                     | 0800                                                                                                                                        |

| 0020          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        | Sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ack Pointer Li                                                                              | mit Value Reg                                                                                         | gister                                                                                                          |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | xxxx                                                                                                                                        |

| 002E          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        | Prog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | gram Counter                                                                                | Low Word Re                                                                                           | egister                                                                                                         |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 0030          | _                                                                                                                                                                                                                                                                                                                                                         | _                          | _                                     | _                                                | _                                                           | _                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                           | _                                                                                                     |                                                                                                                 |                                                                                                                                      | Program C                                                                                                                | ounter Reg                                                                                                                                    | ister High By                                                                                                                                | /te                                                                                                                                         |                                                                                                                       | 0000                                                                                                                                        |

| 0032          | _                                                                                                                                                                                                                                                                                                                                                         | _                          | _                                     | _                                                | _                                                           | _                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                           |                                                                                                       |                                                                                                                 | Table N                                                                                                                              | lemory Pag                                                                                                               | ge Address                                                                                                                                    | Register                                                                                                                                     |                                                                                                                                             |                                                                                                                       | 0000                                                                                                                                        |

| 0034          | _                                                                                                                                                                                                                                                                                                                                                         | _                          | _                                     | _                                                | _                                                           | _                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                           |                                                                                                       | Pr                                                                                                              | ogram Spa                                                                                                                            | ace Visibilit                                                                                                            | y Page Add                                                                                                                                    | dress Registe                                                                                                                                | er                                                                                                                                          |                                                                                                                       | 0000                                                                                                                                        |

| 0036          |                                                                                                                                                                                                                                                                                                                                                           |                            |                                       |                                                  |                                                             |                                                                        | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REPEAT LOOP                                                                                 | Counter Regi                                                                                          |                                                                                                                 |                                                                                                                                      |                                                                                                                          |                                                                                                                                               |                                                                                                                                              |                                                                                                                                             |                                                                                                                       | xxxxx                                                                                                                                       |

| 0042          | _                                                                                                                                                                                                                                                                                                                                                         | _                          | _                                     | _                                                | _                                                           | _                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DC                                                                                          | IPL2                                                                                                  | IPL1                                                                                                            | IPL0                                                                                                                                 | RA                                                                                                                       | N                                                                                                                                             | OV                                                                                                                                           | Z                                                                                                                                           | С                                                                                                                     | 0000                                                                                                                                        |

| 0044          | _                                                                                                                                                                                                                                                                                                                                                         | _                          | _                                     | _                                                | _                                                           | _                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                           | _                                                                                                     | _                                                                                                               | _                                                                                                                                    | _                                                                                                                        | IPL3                                                                                                                                          | PSV                                                                                                                                          | _                                                                                                                                           | _                                                                                                                     | 0000                                                                                                                                        |