### Microchip Technology - PIC24F08KL200-E/P Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 8KB (2.75K x 24)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 7x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 14-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl200-e-p |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

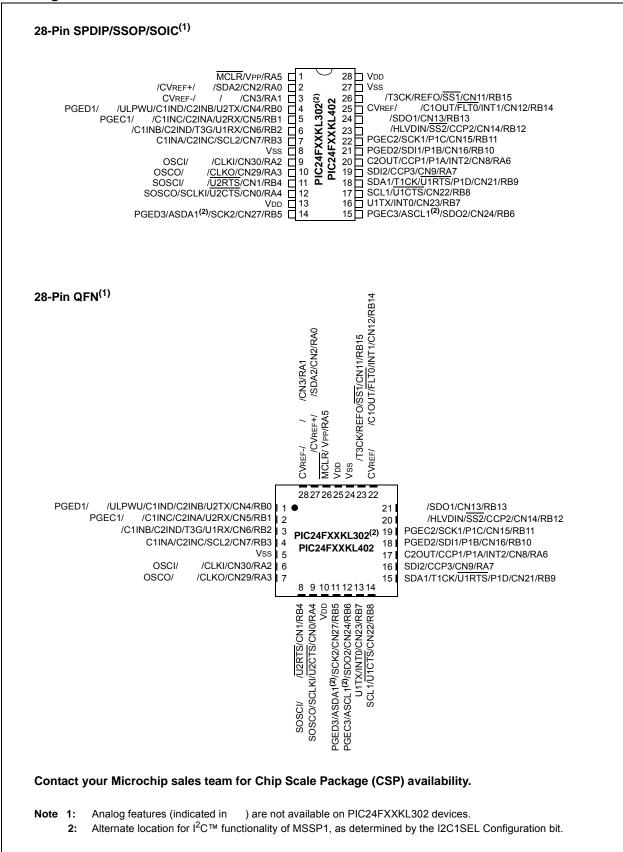

#### Pin Diagrams: PIC24FXXKL302/402

|          |                                  | Pin Number    | r                        |     |                                         |                                                           |

|----------|----------------------------------|---------------|--------------------------|-----|-----------------------------------------|-----------------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 14-Pin<br>PDIP/<br>TSSOP | I/O | Buffer                                  | Description                                               |

| SCK1     | 15                               | 12            | 8                        | I/O | ST                                      | MSSP1 SPI Serial Input/Output Clock                       |

| SCL1     | 12                               | 9             | 8                        | I/O | l <sup>2</sup> C                        | MSSP1 I <sup>2</sup> C Clock Input/Output                 |

| SCLKI    | 10                               | 7             | 12                       | I   | ST                                      | Digital Secondary Clock Input                             |

| SDA1     | 13                               | 10            | 9                        | I/O | l <sup>2</sup> C                        | MSSP1 I <sup>2</sup> C Data Input/Output                  |

| SDI1     | 17                               | 14            | 11                       | Ι   | ST                                      | MSSP1 SPI Serial Data Input                               |

| SDO1     | 16                               | 13            | 9                        | 0   | _                                       | MSSP1 SPI Serial Data Output                              |

| SOSCI    | 9                                | 6             | 11                       | I   | ANA                                     | Secondary Oscillator Input                                |

| SOSCO    | 10                               | 7             | 12                       | 0   | ANA                                     | Secondary Oscillator Output                               |

| SS1      | 12                               | 9             | 12                       | 0   | _                                       | SPI1 Slave Select                                         |

| T1CK     | 13                               | 10            | 9                        | I   | ST                                      | Timer1 Clock                                              |

| ТЗСК     | 18                               | 15            | 12                       | I   | ST                                      | Timer3 Clock                                              |

| T3G      | 6                                | 3             | 11                       | Ι   | ST                                      | Timer3 External Gate Input                                |

| U1CTS    | 12                               | 9             | 8                        | Ι   | ST                                      | UART1 Clear-to-Send Input                                 |

| U1RTS    | 13                               | 10            | 9                        | 0   | _                                       | UART1 Request-to-Send Output                              |

| U1RX     | 6                                | 3             | 12                       | I   | ST                                      | UART1 Receive                                             |

| U1TX     | 11                               | 8             | 11                       | 0   | _                                       | UART1 Transmit                                            |

| ULPWU    | 3                                | 1             | 3                        | I   | ANA                                     | Ultra Low-Power Wake-up Input                             |

| VDD      | 20                               | 17            | 14                       | Р   |                                         | Positive Supply for Peripheral Digital Logic and I/O Pins |

| VREF+    | 2                                | 19            | 2                        | I   | ANA                                     | A/D Reference Voltage Input (+)                           |

| VREF-    | 3                                | 20            | 3                        | I   | ANA                                     | A/D Reference Voltage Input (-)                           |

| Vss      | 19                               | 16            | 13                       | Р   | Ground Reference for Logic and I/O Pins |                                                           |

#### **TABLE 1-5:** PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

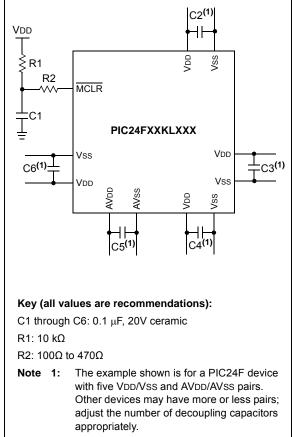

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC24F16KL402 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.4 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

Note: The AVDD and AVSS pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

### 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing it is not recommended.

All of the Table Write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

#### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. For more information, refer to **Section 5.5 "Programming Operations"**.

#### 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

**REGISTER 7-1:**

RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0     | 0 R/W-0                                | R/W-0 <sup>(3)</sup>                                                                         | U-0             | U-0                   | U-0                        | R/W-0            | R/W-0           |  |

|-----------|----------------------------------------|----------------------------------------------------------------------------------------------|-----------------|-----------------------|----------------------------|------------------|-----------------|--|

| TRAP      | R IOPUWR                               | SBOREN                                                                                       | _               | —                     | _                          | CM               | PMSLP           |  |

| bit 15    |                                        |                                                                                              |                 |                       |                            |                  | bit 8           |  |

|           |                                        |                                                                                              |                 |                       |                            |                  |                 |  |

| R/W-0     | 0 R/W-0                                | R/W-0                                                                                        | R/W-0           | R/W-0                 | R/W-0                      | R/W-1            | R/W-1           |  |

| EXTR      | R SWR                                  | SWDTEN <sup>(2)</sup>                                                                        | WDTO            | SLEEP                 | IDLE                       | BOR              | POR             |  |

| bit 7     |                                        |                                                                                              |                 |                       |                            |                  | bit 0           |  |

|           |                                        |                                                                                              |                 |                       |                            |                  |                 |  |

| Legend:   |                                        |                                                                                              | :4              |                       | a a material in the second |                  |                 |  |

| R = Read  |                                        | W = Writable b                                                                               | IT              | •                     | nented bit, read           |                  |                 |  |

| -n = Valu | e at POR                               | '1' = Bit is set                                                                             |                 | '0' = Bit is cle      | ared                       | x = Bit is unkr  | nown            |  |

| bit 15    | TRAPR. Tra                             | p Reset Flag bit                                                                             |                 |                       |                            |                  |                 |  |

| bit io    |                                        | Conflict Reset has                                                                           | occurred        |                       |                            |                  |                 |  |

|           |                                        | Conflict Reset has                                                                           |                 | b                     |                            |                  |                 |  |

| bit 14    | IOPUWR: III                            | egal Opcode or L                                                                             | Jninitialized V | V Access Reset        | Flag bit                   |                  |                 |  |

|           | 1 = An illega                          | al opcode detecti                                                                            | on, an illegal  | address mode          | or an Uninitial            | ized W register  | r is used as an |  |

|           |                                        | Pointer and cau                                                                              |                 |                       |                            |                  |                 |  |

|           | -                                      | al opcode or Unin                                                                            |                 | -                     | is not occurred            |                  |                 |  |

| bit 13    |                                        | oftware Enable/D                                                                             |                 | R bit <sup>(3)</sup>  |                            |                  |                 |  |

|           |                                        | urned on in softw<br>urned off in softw                                                      |                 |                       |                            |                  |                 |  |

| bit 12-10 | Unimpleme                              | nted: Read as '0                                                                             |                 |                       |                            |                  |                 |  |

| bit 9     | CM: Configu                            | ration Word Misn                                                                             | natch Reset I   | Flag bit              |                            |                  |                 |  |

|           |                                        | uration Word Mis                                                                             |                 |                       |                            |                  |                 |  |

|           | •                                      | uration Word Mis                                                                             |                 |                       | ed                         |                  |                 |  |

| bit 8     |                                        | gram Memory Po                                                                               | •               | •                     |                            |                  |                 |  |

|           |                                        | memory bias vo<br>memory bias vo                                                             |                 |                       |                            |                  |                 |  |

| h:+ 7     |                                        | mal Reset (MCLF                                                                              |                 |                       | y Sleep                    |                  |                 |  |

| bit 7     |                                        | r Clear (pin) Rese                                                                           | ,               | ed                    |                            |                  |                 |  |

|           |                                        | r Clear (pin) Rese                                                                           |                 |                       |                            |                  |                 |  |

| bit 6     | SWR: Softwa                            | are Reset (Instru                                                                            | ction) Flag bi  | t                     |                            |                  |                 |  |

|           |                                        | instruction has t                                                                            |                 |                       |                            |                  |                 |  |

|           |                                        | r instruction has r                                                                          |                 |                       |                            |                  |                 |  |

| bit 5     | SWDTEN: S                              | oftware Enable/D                                                                             | Disable of WE   | )T bit <sup>(2)</sup> |                            |                  |                 |  |

|           | 1 = WDT is e                           |                                                                                              |                 |                       |                            |                  |                 |  |

| 1.11.4    | 0 = WDT is 0                           |                                                                                              |                 |                       |                            |                  |                 |  |

| bit 4     |                                        | chdog Timer Time                                                                             | -               |                       |                            |                  |                 |  |

|           |                                        | e-out has occurre                                                                            |                 |                       |                            |                  |                 |  |

| Note 1.   | All of the Depart                      | tatua hita may ha                                                                            | act or closer   | d in coffword C       | atting one of th           | ana hita in aaft | wara daga nat   |  |

| Note 1:   | All of the Reset s<br>cause a device F | •                                                                                            | set of cleare   | eu în soitware. S     | beaung one of th           | IESE DIIS IN SOT | ware upes not   |  |

| 2:        | If the FWDTEN (                        |                                                                                              | is '1' (unprog  | rammed), the V        | VDT is always o            | enabled, regard  | dless of the    |  |

|           | SWDTEN bit set                         | -                                                                                            |                 | ,-                    |                            |                  |                 |  |

| 3.        | The SBOREN hi                          | SBOREN bit is forced to '0' when disabled by the Configuration bits. BOREN<1:0> (EPOR<1:0>). |                 |                       |                            |                  |                 |  |

**3:** The SBOREN bit is forced to '0' when disabled by the Configuration bits, BOREN<1:0> (FPOR<1:0>). When the Configuration bits are set to enable SBOREN, the default Reset state will be '1'.

| R/W-0              | R-0, HSC                                                                                                                                                                                                                                                                       | U-0                                                                                                                    | U-0                        | U-0               | U-0              | U-0             | U-0    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|------------------|-----------------|--------|

| ALTIVT             | DISI                                                                                                                                                                                                                                                                           | —                                                                                                                      | —                          | —                 | —                | —               | —      |

| bit 15             |                                                                                                                                                                                                                                                                                |                                                                                                                        |                            |                   |                  |                 | bit 8  |

|                    |                                                                                                                                                                                                                                                                                |                                                                                                                        |                            |                   |                  |                 |        |

| U-0                | U-0                                                                                                                                                                                                                                                                            | U-0                                                                                                                    | U-0                        | U-0               | R/W-0            | R/W-0           | R/W-0  |

| —                  | —                                                                                                                                                                                                                                                                              | —                                                                                                                      |                            | —                 | INT2EP           | INT1EP          | INT0EP |

| bit 7              |                                                                                                                                                                                                                                                                                |                                                                                                                        |                            |                   |                  |                 | bit 0  |

|                    |                                                                                                                                                                                                                                                                                |                                                                                                                        |                            |                   |                  |                 |        |

| Legend:            |                                                                                                                                                                                                                                                                                | HSC = Hardwa                                                                                                           | are Settable/C             | learable bit      |                  |                 |        |

| R = Readable       | e bit                                                                                                                                                                                                                                                                          | W = Writable b                                                                                                         | bit                        | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value at      | POR                                                                                                                                                                                                                                                                            | '1' = Bit is set                                                                                                       |                            | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

| bit 14<br>bit 13-3 | 0 = Uses stan<br>DISI: DISI In:<br>1 = DISI instr<br>0 = DISI instr<br>Unimplement                                                                                                                                                                                             | rnate Interrupt V<br>dard (default) v<br>struction Status<br>ruction is active<br>ruction is not ac<br>ted: Read as '0 | ector table<br>bit<br>tive |                   |                  |                 |        |

| bit 2<br>bit 1     | <ul> <li>INT2EP: External Interrupt 2 Edge Detect Polarity Select bit</li> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> <li>INT1EP: External Interrupt 1 Edge Detect Polarity Select bit</li> <li>1 = Interrupt on negative edge</li> </ul> |                                                                                                                        |                            |                   |                  |                 |        |

| bit 0              | INTOEP: Exte<br>1 = Interrupt c                                                                                                                                                                                                                                                | on positive edge<br>rnal Interrupt 0<br>on negative edg<br>on positive edge                                            | Edge Detect F<br>e         | Polarity Select b | bit              |                 |        |

#### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER2

| R/W-0        | U-0           | R/W-0                                  | R/W-0          | R/W-0             | U-0              | U-0            | R/W-0  |

|--------------|---------------|----------------------------------------|----------------|-------------------|------------------|----------------|--------|

| NVMIE        |               | AD1IE                                  | U1TXIE         | U1RXIE            | —                | _              | T3IE   |

| bit 15       |               |                                        |                |                   |                  |                | bit 8  |

|              |               |                                        |                |                   |                  |                |        |

| R/W-0        | R/W-0         | U-0                                    | U-0            | R/W-0             | R/W-0            | U-0            | R/W-0  |

| T2IE         | CCP2IE        | _                                      |                | T1IE              | CCP1IE           | —              | INTOIE |

| bit 7        |               |                                        |                |                   |                  |                | bit C  |

| Legend:      |               |                                        |                |                   |                  |                |        |

| R = Readab   | le bit        | W = Writable t                         | bit            | U = Unimplen      | nented bit, read | l as '0'       |        |

| -n = Value a | t POR         | '1' = Bit is set                       |                | '0' = Bit is clea | ared             | x = Bit is unk | nown   |

| L:4 / C      |               |                                        | - 1-14         |                   |                  |                |        |

| bit 15       |               | /I Interrupt Enabl<br>request is enabl |                |                   |                  |                |        |

|              |               | request is not er                      |                |                   |                  |                |        |

| bit 14       | Unimpleme     | nted: Read as '0                       | ,              |                   |                  |                |        |

| bit 13       | AD1IE: A/D    | Conversion Com                         | plete Interrup | t Enable bit      |                  |                |        |

|              |               | request is enabl                       |                |                   |                  |                |        |

| L:1 40       | -             | request is not er                      |                | <b>bla b</b> :4   |                  |                |        |

| bit 12       |               | RT1 Transmitter<br>request is enabl    | •              | DIE DIT           |                  |                |        |

|              |               | request is not er                      |                |                   |                  |                |        |

| bit 11       | U1RXIE: UA    | RT1 Receiver In                        | terrupt Enable | e bit             |                  |                |        |

|              |               | request is enabl                       |                |                   |                  |                |        |

|              | -             | request is not er                      |                |                   |                  |                |        |

| bit 10-9     | -             | nted: Read as '0                       |                |                   |                  |                |        |

| bit 8        |               | 3 Interrupt Enable                     |                |                   |                  |                |        |

|              |               | request is enabl<br>request is not er  |                |                   |                  |                |        |

| bit 7        |               | 2 Interrupt Enable                     |                |                   |                  |                |        |

|              |               | request is enabl                       |                |                   |                  |                |        |

|              | 0 = Interrupt | request is not er                      | nabled         |                   |                  |                |        |

| bit 6        |               | pture/Compare/F                        | -              | ot Enable bit     |                  |                |        |

|              |               | request is enabl<br>request is not er  |                |                   |                  |                |        |

| bit 5-4      |               | nted: Read as '0                       |                |                   |                  |                |        |

| bit 3        | -             | Interrupt Enable                       |                |                   |                  |                |        |

| bit 5        |               | request is enabl                       |                |                   |                  |                |        |

|              |               | request is not er                      |                |                   |                  |                |        |

| bit 2        | CCP1IE: Ca    | pture/Compare/F                        | WM1 Interru    | ot Enable bit     |                  |                |        |

|              |               | request is enabl                       |                |                   |                  |                |        |

| L:1 4        |               | request is not er                      |                |                   |                  |                |        |

| bit 1        | -             | nted: Read as '0                       |                |                   |                  |                |        |

| bit 0        |               | rnal Interrupt 0 E<br>request is enabl |                |                   |                  |                |        |

|              |               | TEQUEST IS ETIDDI                      | 6U             |                   |                  |                |        |

#### REGISTER 8-13: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0   | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-------|-----|-----|-----|-----|-------|

|        | —   | _     | _   |     | _   | _   | _     |

| bit 15 | •   |       |     |     |     |     | bit 8 |

|        |     |       |     |     |     |     |       |

| U-0    | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| —      | —   | T3GIE | —   | —   | —   | —   | —     |

| bit 7  |     |       |     |     |     |     | bit 0 |

| DIT | 1 |

|-----|---|

|     |   |

bit 1

| Legend:           |                  |                                        |                    |  |  |

|-------------------|------------------|----------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                   | x = Bit is unknown |  |  |

| bit 15-6 | Unimplemented: Read as '0'                       |

|----------|--------------------------------------------------|

| bit 5    | T3GIF: Timer3 External Gate Interrupt Enable bit |

|          | 1 = Interrupt request is enabled                 |

|          | 0 = Interrupt request is not enabled             |

|          |                                                  |

Unimplemented: Read as '0' bit 4-0

#### **REGISTER 8-14: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                 | U-0   |

|-------|-----|-----|-----|-----|-----------------------|-----------------------|-------|

| _     | —   | —   | —   | —   | BCL2IE <sup>(1)</sup> | SSP2IE <sup>(1)</sup> | —     |

| bit 7 |     |     |     |     |                       |                       | bit 0 |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-3 Unimplemented: Read as '0'

BCL2IE: MSSP2 I<sup>2</sup>C<sup>™</sup> Bus Collision Interrupt Enable bit<sup>(1)</sup> bit 2

- 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

- SSP2IF: MSSP2 SPI/I<sup>2</sup>C Event Interrupt Enable bit<sup>(1)</sup>

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 0 Unimplemented: Read as '0'

- Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

|                    | R/W-1                                                                                              | R/W-0                                                                                                     | R/W-0                                                      | U-0              | R/W-1            | R/W-0           | R/W-0   |

|--------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|------------------|-----------------|---------|

| _                  | T2IP2                                                                                              | T2IP1                                                                                                     | T2IP0                                                      | _                | CCP2IP2          | CCP2IP1         | CCP2IP0 |

| bit 15             |                                                                                                    |                                                                                                           |                                                            |                  |                  | L               | bit 8   |

|                    |                                                                                                    |                                                                                                           |                                                            |                  |                  |                 |         |

| U-0                | U-0                                                                                                | U-0                                                                                                       | U-0                                                        | U-0              | U-0              | U-0             | U-0     |

| —                  | _                                                                                                  | _                                                                                                         | _                                                          | —                | _                | _               | _       |

| bit 7              |                                                                                                    |                                                                                                           |                                                            |                  |                  |                 | bit C   |

|                    |                                                                                                    |                                                                                                           |                                                            |                  |                  |                 |         |

| Legend:            |                                                                                                    |                                                                                                           |                                                            |                  |                  |                 |         |

| R = Readab         | ole bit                                                                                            | W = Writable                                                                                              | bit                                                        | U = Unimple      | mented bit, read | l as '0'        |         |

| -n = Value a       | at POR                                                                                             | '1' = Bit is set                                                                                          |                                                            | '0' = Bit is cle | eared            | x = Bit is unkr | iown    |

|                    |                                                                                                    |                                                                                                           |                                                            |                  |                  |                 |         |

| bit 15             | Unimplemen                                                                                         | ted: Read as 'd                                                                                           | )'                                                         |                  |                  |                 |         |

| bit 14-12          | T2IP<2:0>: ⊺                                                                                       | ïmer2 Interrupt                                                                                           | Priority bits                                              |                  |                  |                 |         |

|                    | 111 = Interru                                                                                      | pt is Priority 7 (I                                                                                       | highest priorit                                            | y interrupt)     |                  |                 |         |

|                    | •                                                                                                  |                                                                                                           |                                                            |                  |                  |                 |         |

|                    | •                                                                                                  |                                                                                                           |                                                            |                  |                  |                 |         |

|                    | •                                                                                                  |                                                                                                           |                                                            |                  |                  |                 |         |

|                    |                                                                                                    | pt is Priority 1                                                                                          |                                                            |                  |                  |                 |         |

|                    | 000 = Interru                                                                                      | pt source is disa                                                                                         |                                                            |                  |                  |                 |         |

| bit 11             | 000 = Interru<br>Unimplemen                                                                        | pt source is disanted: Read as 'o                                                                         | )'                                                         |                  |                  |                 |         |

| bit 11<br>bit 10-8 | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:                                                         | pt source is disa<br><b>ited:</b> Read as '(<br>>: Capture/Com                                            | )'<br>Ipare/PWM2 I                                         | • •              | / bits           |                 |         |

|                    | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:                                                         | pt source is disanted: Read as 'o                                                                         | )'<br>Ipare/PWM2 I                                         | • •              | / bits           |                 |         |

|                    | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:                                                         | pt source is disa<br><b>ited:</b> Read as '(<br>>: Capture/Com                                            | )'<br>Ipare/PWM2 I                                         | • •              | ∕ bits           |                 |         |

|                    | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:                                                         | pt source is disa<br><b>ited:</b> Read as '(<br>>: Capture/Com                                            | )'<br>Ipare/PWM2 I                                         | • •              | / bits           |                 |         |

|                    | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:<br>111 = Interru<br>•<br>•<br>001 = Interru             | pt source is disa<br><b>ited:</b> Read as '(<br>>: Capture/Com<br>pt is Priority 7 (I<br>pt is Priority 1 | <sub>)</sub> ,<br>Ipare/PWM2 I<br>highest priorit          | • •              | / bits           |                 |         |

|                    | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:<br>111 = Interru<br>•<br>001 = Interru<br>000 = Interru | pt source is disa<br><b>ited:</b> Read as '(<br>>: Capture/Com<br>pt is Priority 7 (l                     | <sub>)</sub> ,<br>ipare/PWM2 I<br>highest priorit<br>abled | • •              | / bits           |                 |         |

#### REGISTER 8-18: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

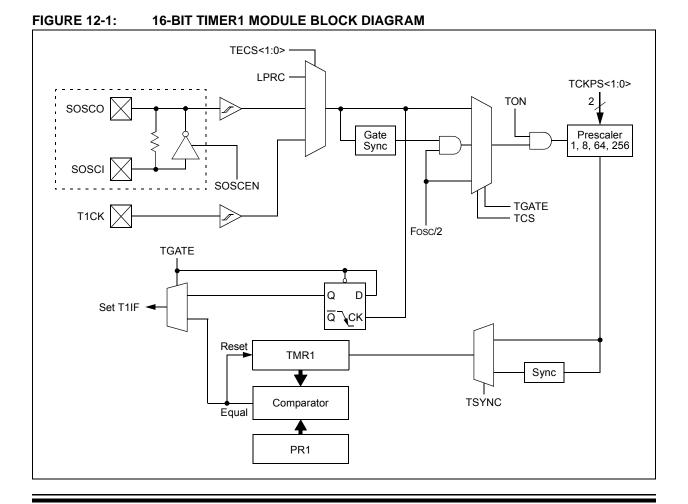

### 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can operate as a free-running, interval timer/counter, or serve as the time counter for a software-based Real-Time Clock (RTC). Timer1 is only reset on initial VDD power-on events. This allows the timer to continue operating as an RTC clock source through other types of device Reset.

Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 illustrates a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

### 18.1 UART Baud Rate Generator (BRG)

The UART module includes a dedicated 16-bit Baud Rate Generator (BRG). The UxBRG register controls the period of a free-running, 16-bit timer. Equation 18-1 provides the formula for computation of the baud rate with BRGH = 0.

## EQUATION 18-1: UARTx BAUD RATE WITH BRGH = $0^{(1)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$ UxBRG =  $\frac{FCY}{16 \cdot Baud Rate} - 1$

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

Example 18-1 provides the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 18-2 shows the formula for computation of the baud rate with BRGH = 1.

## EQUATION 18-2: UARTx BAUD RATE WITH BRGH = $1^{(1)}$

Baud Rate =

$$\frac{FCY}{4 \cdot (UxBRG + 1)}$$

$UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$

Note 1: Based on FCY = FOSC/2; Doze mode

and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FCY/4 (for UxBRG = 0) and the minimum baud rate possible is FCY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

#### EXAMPLE 18-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

```

Desired Baud Rate

= FCY/(16 (UxBRG + 1))

Solving for UxBRG Value:

UxBRG

= ((FCY/Desired Baud Rate)/16) - 1

UxBRG

= ((400000/9600)/16) - 1

= 25

UxBRG

Calculated Baud Rate = 400000/(16(25+1))

= 9615

Error

= (Calculated Baud Rate – Desired Baud Rate)

Desired Baud Rate

= (9615 - 9600)/9600

= 0.16\%

Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

```

### 19.0 10-BIT HIGH-SPEED A/D CONVERTER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 10-Bit High-Speed A/D Converter, refer to the "dsPIC33/PIC24 Family Reference Manual", "10-Bit A/D Converter" (DS39705).

The 10-bit A/D Converter has the following key features:

- · Successive Approximation (SAR) conversion

- Conversion speeds of up to 500 ksps

- · Up to 12 analog input pins

- External voltage reference input pins

- · Internal band gap reference input

- · Automatic Channel Scan mode

- · Selectable conversion trigger source

- · Two-word conversion result buffer

- · Selectable Buffer Fill modes

- · Four result alignment options

- · Operation during CPU Sleep and Idle modes

Depending on the particular device, PIC24F16KL402 family devices implement up to 12 analog input pins, designated AN0 through AN4 and AN9 through AN15. In addition, there are two analog input pins for external voltage reference connections (VREF+ and VREF-). These voltage reference inputs may be shared with other analog input pins. A block diagram of the A/D Converter is displayed in Figure 19-1.

To perform an A/D conversion:

- 1. Configure the A/D module:

- a) Configure port pins as analog inputs and/ or select band gap reference inputs (ANSA<3:0>, ANSB<15:12,4:0> and ANCFG<0>).

- b) Select the voltage reference source to match the expected range on analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- e) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select interrupt rate (AD1CON2<5:2>).

- g) Turn on A/D module (AD1CON1<15>).

- Configure A/D interrupt (if required):

- a) Clear the AD1IF bit.

2.

b) Select A/D interrupt priority.

| R/W-0         | U-0                            | R/W-0                           | U-0             | U-0                                   | U-0               | U-0              | U-0            |

|---------------|--------------------------------|---------------------------------|-----------------|---------------------------------------|-------------------|------------------|----------------|

| HLVDEN        |                                | HLSIDL                          | —               | _                                     |                   |                  | —              |

| bit 15        |                                |                                 |                 | -                                     |                   |                  | bit 8          |

|               |                                |                                 |                 |                                       |                   |                  |                |

| R/W-0         | R/W-0                          | R/W-0                           | U-0             | R/W-0                                 | R/W-0             | R/W-0            | R/W-0          |

| VDIR          | BGVST                          | IRVST                           | —               | HLVDL3                                | HLVDL2            | HLVDL1           | HLVDL0         |

| bit 7         |                                |                                 |                 |                                       |                   |                  | bit (          |

| Legend:       |                                |                                 |                 |                                       |                   |                  |                |

| R = Readabl   | le bit                         | W = Writable                    | bit             | U = Unimplem                          | nented bit, read  | l as '0'         |                |

| -n = Value at | POR                            | '1' = Bit is set                |                 | '0' = Bit is clea                     | ared              | x = Bit is unkn  | iown           |

|               |                                |                                 |                 |                                       |                   |                  |                |

| bit 15        | HLVDEN: Hig                    | gh/Low-Voltage                  | Detect Power    | Enable bit                            |                   |                  |                |

|               | 1 = HLVD is                    |                                 |                 |                                       |                   |                  |                |

|               | 0 = HLVD is                    |                                 |                 |                                       |                   |                  |                |

| bit 14        | -                              | ted: Read as '(                 |                 |                                       |                   |                  |                |

| bit 13        |                                | /D Stop in Idle N               |                 | the device enter                      | rs Idlo modo      |                  |                |

|               |                                | es module opera                 |                 |                                       |                   |                  |                |

| bit 12-8      |                                | ted: Read as 'd                 |                 |                                       |                   |                  |                |

| bit 7         | VDIR: Voltage                  | e Change Direc                  | tion Select bit |                                       |                   |                  |                |

|               |                                |                                 | • •             | or exceeds the                        | • • •             | ,                |                |

|               |                                |                                 | •               | or falls below th                     | ne trip point (HL | VDL<3:0>)        |                |

| bit 6         |                                | d Gap Voltage S                 | -               |                                       |                   |                  |                |

|               |                                | that the band g that the band g |                 |                                       |                   |                  |                |

| bit 5         |                                | al Reference V                  |                 |                                       |                   |                  |                |

|               |                                |                                 | -               | oltage is stable a                    | and the High-Ve   | oltage Detect lo | ogic generates |

|               | the interr                     | upt flag at the s               | pecified volta  | ge range                              |                   |                  |                |

|               |                                |                                 |                 | oltage is unstab<br>cified voltage ra |                   |                  |                |

|               | enabled                        |                                 | ay at the spe   | uneu voltage la                       | inge, and the f   |                  | SHOULD HOL DE  |

| bit 4         | Unimplemen                     | ted: Read as '0                 | )'              |                                       |                   |                  |                |

| bit 3-0       | -                              | : High/Low-Volt                 |                 | Limit bits                            |                   |                  |                |

|               | 1111 = Exter                   | nal analog inpu                 | -               | it comes from th                      | e HLVDIN pin)     |                  |                |

|               | 1110 = Trip F                  | Point 14 <sup>(1)</sup>         |                 |                                       |                   |                  |                |

|               | 1101 = Trip F<br>1100 = Trip F |                                 |                 |                                       |                   |                  |                |

|               | •<br>•                         |                                 |                 |                                       |                   |                  |                |

|               |                                |                                 |                 |                                       |                   |                  |                |

|               | 0000 = Trip F                  | oint ∩(1)                       |                 |                                       |                   |                  |                |

|               | 0000 – mpi                     | Sint O                          |                 |                                       |                   |                  |                |

#### REGISTER 22-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

#### TABLE 26-19: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS                             |       |                                  |     |                    |     |       |                                                     |

|------------------------------------------------|-------|----------------------------------|-----|--------------------|-----|-------|-----------------------------------------------------|

| Param<br>No. Sym Characteristic <sup>(1)</sup> |       |                                  | Min | Тур <sup>(2)</sup> | Max | Units | Conditions                                          |

| OS50                                           | Fplli | PLL Input Frequency<br>Range     | 4   | _                  | 8   | MHz   | ECPLL, HSPLL modes,<br>-40°C $\leq$ TA $\leq$ +85°C |

| OS51                                           | Fsys  | PLL Output Frequency<br>Range    | 16  | —                  | 32  | MHz   | $-40^{\circ}C \le TA \le +85^{\circ}C$              |

| OS52                                           | TLOCK | PLL Start-up Time<br>(Lock Time) | —   | 1                  | 2   | ms    |                                                     |

| OS53                                           | DCLK  | CLKO Stability (Jitter)          | -2  | 1                  | 2   | %     | Measured over 100 ms period                         |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 26-20: INTERNAL RC OSCILLATOR ACCURACY

| AC CHA       | RACTERISTICS                 |     |     |     |       |                                                                      |                                  |  |

|--------------|------------------------------|-----|-----|-----|-------|----------------------------------------------------------------------|----------------------------------|--|

| Param<br>No. | Characteristic               | Min | Тур | Max | Units | Conditions                                                           |                                  |  |

| F20          | FRC @ 8 MHz <sup>(1)</sup>   | -2  |     | +2  | %     | +25°C                                                                | $3.0V \leq V\text{DD} \leq 3.6V$ |  |

|              |                              | -5  | _   | +5  | %     | $-40^\circ C \le T \texttt{A} \le +85^\circ C$                       | $1.8V \leq V\text{DD} \leq 3.6V$ |  |

|              |                              | -10 |     | +10 | %     | $-40^{\circ}C \le TA \le +125^{\circ}C \qquad 1.8V \le VDD \le 3.6V$ |                                  |  |

| F21          | LPRC @ 31 kHz <sup>(2)</sup> | -15 |     | +15 | %     | $-40^{\circ}C \le TA \le +85^{\circ}C \qquad 1.8V \le VDD \le 3.6V$  |                                  |  |

|              |                              | -25 |     | +25 | %     | $-40^\circ C \leq TA \leq +125^\circ C$                              | $1.8V \leq V\text{DD} \leq 3.6V$ |  |

**Note 1:** The frequency is calibrated at +25°C and 3.3V. The OSCTUN bits can be used to compensate for temperature drift.

2: The change of LPRC frequency as VDD changes.

#### TABLE 26-21: INTERNAL RC OSCILLATOR SPECIFICATIONS

|                                 |       |                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |           |       |            |  |  |

|---------------------------------|-------|--------------------|------------------------------------------------------|-----------|-------|------------|--|--|

| Param<br>No. Sym Characteristic |       | Min                | Тур                                                  | Max       | Units | Conditions |  |  |

|                                 | TFRC  | FRC Start-up Time  | —                                                    | 5         | _     | μS         |  |  |

|                                 | TLPRC | LPRC Start-up Time | —                                                    | — 70 — μs |       |            |  |  |

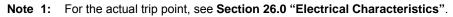

#### TABLE 26-29: EXAMPLE SPI MODE REQUIREMENTS (SLAVE MODE TIMING, CKE = 0)

| Param<br>No. | Symbol                | Characteristic                                                            | Min          | Max           | Units | Conditions |          |

|--------------|-----------------------|---------------------------------------------------------------------------|--------------|---------------|-------|------------|----------|

| 70           | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input |              | 3 Тсү         |       | ns         |          |

| 70A          | TssL2WB               | SSx to Write to SSPxBUF                                                   |              | 3 Tcy         | _     | ns         |          |

| 71           | TscH                  | SCKx Input High Time                                                      | Continuous   | 1.25 Tcy + 30 |       | ns         |          |

| 71A          |                       | (Slave mode)                                                              | Single Byte  | 40            |       | ns         | (Note 1) |

| 72           | TscL                  | SCKx Input Low Time                                                       | Continuous   | 1.25 Tcy + 30 | _     | ns         |          |

| 72A          |                       | (Slave mode)                                                              | Single Byte  | 40            |       | ns         | (Note 1) |

| 73           | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx                                     | 20           | _             | ns    |            |          |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the First Cloc                               | 1.5 Tcy + 40 |               | ns    | (Note 2)   |          |

| 74           | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx I                                    | Edge         | 40            | _     | ns         |          |

| 75           | TDOR                  | SDOx Data Output Rise Time                                                |              | —             | 25    | ns         |          |

| 76           | TDOF                  | SDOx Data Output Fall Time                                                |              | —             | 25    | ns         |          |

| 77           | TssH2doZ              | SSx ↑ to SDOx Output High-Impedance                                       | 9            | 10            | 50    | ns         |          |

| 80           | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Ed                                      | —            | 50            | ns    |            |          |

| 83           | TscH2ssH,<br>TscL2ssH | SSx ↑ after SCKx Edge                                                     | 1.5 Tcy + 40 | _             | ns    |            |          |

|              | FSCK                  | SCKx Frequency                                                            |              | —             | 10    | MHz        |          |

**Note 1:** Requires the use of Parameter 73A.

2: Only if Parameters 71A and 72A are used.

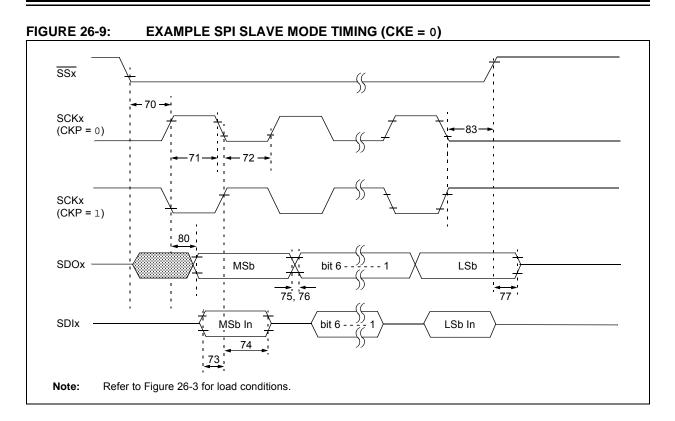

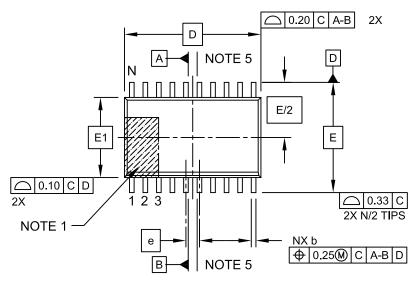

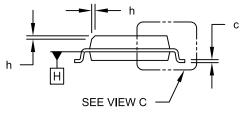

### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

TOP VIEW

VIEW A-A

Microchip Technology Drawing C04-094C Sheet 1 of 2

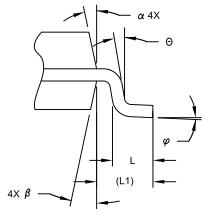

### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

|                          | MILLIMETERS |             |           |      |  |  |

|--------------------------|-------------|-------------|-----------|------|--|--|

| Dimension Lir            | nits        | MIN         | NOM       | MAX  |  |  |

| Number of Pins           | N           | 20          |           |      |  |  |

| Pitch                    | е           |             | 1.27 BSC  |      |  |  |

| Overall Height           | Α           | -           | -         | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05        | -         | -    |  |  |

| Standoff §               | A1          | 0.10        | -         | 0.30 |  |  |

| Overall Width            | E           |             | 10.30 BSC |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC    |           |      |  |  |

| Overall Length           | D           | D 12.80 BSC |           |      |  |  |

| Chamfer (Optional)       | h           | 0.25        | -         | 0.75 |  |  |

| Foot Length              | L           | 0.40        | -         | 1.27 |  |  |

| Footprint                | L1          | 1.40 REF    |           |      |  |  |

| Lead Angle               | Θ           | 0°          | -         | -    |  |  |

| Foot Angle               | φ           | 0°          | -         | 8°   |  |  |

| Lead Thickness           | С           | 0.20        | -         | 0.33 |  |  |

| Lead Width               | b           | 0.31        | -         | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°          | -         | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°          | -         | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2

#### 28-Lead Plastic Quad Flat, No Lead Package (MQ) – 5x5x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |          |      |  |

|------------------------|------------------|-------------|----------|------|--|

| Dimension              | Dimension Limits |             |          |      |  |

| Number of Pins         | N                |             | 28       |      |  |

| Pitch                  | е                |             | 0.50 BSC |      |  |

| Overall Height         | A                | 0.80        | 0.90     | 1.00 |  |

| Standoff               | A1               | 0.00        | 0.02     | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF    |          |      |  |

| Overall Width          | E                |             | 5.00 BSC |      |  |

| Exposed Pad Width      | E2               | 3.15        | 3.25     | 3.35 |  |

| Overall Length         | D                | 5.00 BSC    |          |      |  |

| Exposed Pad Length     | D2               | 3.15        | 3.25     | 3.35 |  |

| Contact Width          | b                | 0.18        | 0.25     | 0.30 |  |

| Contact Length         | L                | 0.35        | 0.40     | 0.45 |  |

| Contact-to-Exposed Pad | K                | 0.20        | -        | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-140B Sheet 2 of 2

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."