# Microchip Technology - PIC24F08KL200-I/P Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 8KB (2.75K x 24)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 7x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

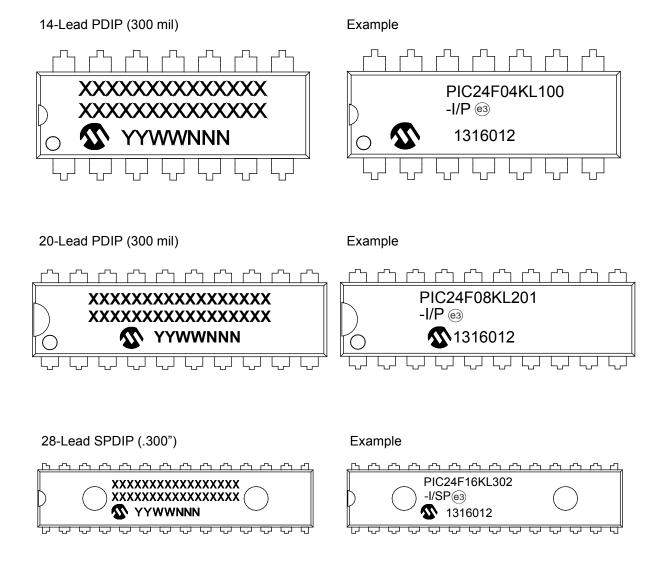

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 14-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl200-i-p |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.2 Other Special Features

- Communications: The PIC24F16KL402 family incorporates multiple serial communication peripherals to handle a range of application requirements. The MSSP module implements both SPI and I<sup>2</sup>C™ protocols, and supports both Master and Slave modes of operation for each. Devices also include one of two UARTs with built-in IrDA<sup>®</sup> encoders/decoders.

- Analog Features: Select members of the PIC24F16KL402 family include a 10-bit A/D Converter module. The A/D module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, as well as faster sampling speeds.

The comparator modules are configurable for a wide range of operations and can be used as either a single or double comparator module.

# 1.3 Details on Individual Family Members

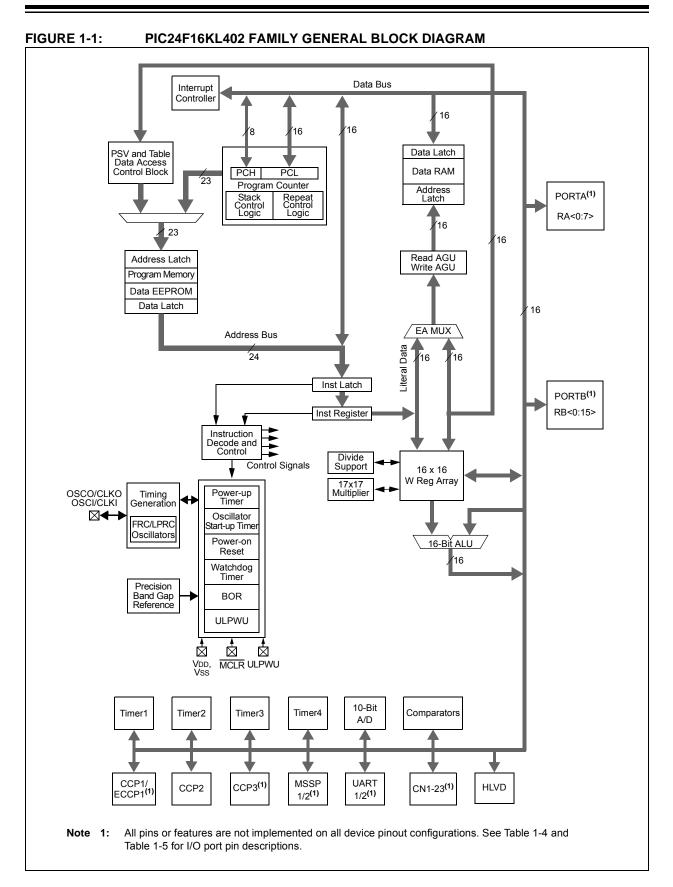

Devices in the PIC24F16KL402 family are available in 14-pin, 20-pin and 28-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The PIC24F16KL402 family may be thought of as four different device groups, each offering a slightly different set of features. These differ from each other in multiple ways:

- · The size of the Flash program memory

- The presence and size of data EEPROM

- The presence of an A/D Converter and the number of external analog channels available

- · The number of analog comparators

- The number of general purpose timers

- The number and type of CCP modules (i.e., CCP vs. ECCP)

- The number of serial communications modules (both MSSPs and UARTs)

The general differences between the different sub-families are shown in Table 1-1. The feature sets for specific devices are summarized in Table 1-2 and Table 1-3.

A list of the individual pin features available on the PIC24F16KL402 family devices, sorted by function, is provided in Table 1-4 (for PIC24FXXKL40X/30X devices) and Table 1-5 (for PIC24FXXKL20X/10X devices). Note that these tables show the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

| Device Group  | Program<br>Memory<br>(bytes) | Data<br>EEPROM<br>(bytes) | Timers<br>(8/16-bit) | CCP and<br>ECCP | Serial<br>(MSSP/<br>UART) | A/D<br>(channels) | Comparators |

|---------------|------------------------------|---------------------------|----------------------|-----------------|---------------------------|-------------------|-------------|

| PIC24FXXKL10X | 4K                           | _                         | 1/2                  | 2/0             | 1/1                       | _                 | 1           |

| PIC24FXXKL20X | 8K                           | —                         | 1/2                  | 2/0             | 1/1                       | 7 or 12           | 1           |

| PIC24FXXKL30X | 8K                           | 256                       | 2/2                  | 2/1             | 2/2                       | —                 | 2           |

| PIC24FXXKL40X | 8K or 16K                    | 512                       | 2/2                  | 2/1             | 2/2                       | 12                | 2           |

### TABLE 1-1:FEATURE COMPARISON FOR PIC24F16KL402 FAMILY GROUPS

|          |                                  | Pin N         | umber                             |               |     |        |                                                              |

|----------|----------------------------------|---------------|-----------------------------------|---------------|-----|--------|--------------------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | I/O | Buffer | Description                                                  |

| SOSCI    | 9                                | 6             | 11                                | 8             | I   | ANA    | Secondary Oscillator Input                                   |

| SOSCO    | 10                               | 7             | 12                                | 9             | 0   | ANA    | Secondary Oscillator Output                                  |

| SS1      | 12                               | 9             | 26                                | 23            | 0   | _      | SPI1 Slave Select                                            |

| SS2      | 15                               | 12            | 23                                | 20            | 0   | _      | SPI2 Slave Select                                            |

| T1CK     | 13                               | 10            | 18                                | 15            | I   | ST     | Timer1 Clock                                                 |

| T3CK     | 18                               | 15            | 26                                | 23            | I   | ST     | Timer3 Clock                                                 |

| T3G      | 6                                | 3             | 6                                 | 3             | I   | ST     | Timer3 External Gate Input                                   |

| U1CTS    | 12                               | 9             | 17                                | 14            | I   | ST     | UART1 Clear-to-Send Input                                    |

| U1RTS    | 13                               | 10            | 18                                | 15            | 0   |        | UART1 Request-to-Send Output                                 |

| U1RX     | 6                                | 3             | 6                                 | 3             | I   | ST     | UART1 Receive                                                |

| U1TX     | 11                               | 8             | 16                                | 13            | 0   |        | UART1 Transmit                                               |

| U2CTS    | 10                               | 7             | 12                                | 9             | I   | ST     | UART2 Clear-to-Send Input                                    |

| U2RTS    | 9                                | 6             | 11                                | 8             | 0   |        | UART2 Request-to-Send Output                                 |

| U2RX     | 5                                | 2             | 5                                 | 2             | I   | ST     | UART2 Receive                                                |

| U2TX     | 4                                | 1             | 4                                 | 1             | 0   | _      | UART2 Transmit                                               |

| ULPWU    | 4                                | 1             | 4                                 | 1             | I   | ANA    | Ultra Low-Power Wake-up Input                                |

| Vdd      | 20                               | 17            | 13, 28                            | 10, 25        | Р   | —      | Positive Supply for Peripheral Digital Logic and<br>I/O Pins |

| VREF+    | 2                                | 19            | 2                                 | 27            | I   | ANA    | A/D Reference Voltage Input (+)                              |

| VREF-    | 3                                | 20            | 3                                 | 28            | I   | ANA    | A/D Reference Voltage Input (-)                              |

| Vss      | 19                               | 16            | 8, 27                             | 5, 24         | Р   | _      | Ground Reference for Logic and I/O Pins                      |

#### PIC24F16KL40X/30X FAMILY PINOUT DESCRIPTIONS (CONTINUED) **TABLE 1-4:**

TTL = TTL input buffer Legend:

ANA = Analog level input/output

ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

|          |                                  | Pin Number    | r                        |     |                  |                                                           |

|----------|----------------------------------|---------------|--------------------------|-----|------------------|-----------------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 14-Pin<br>PDIP/<br>TSSOP | I/O | Buffer           | Description                                               |

| SCK1     | 15                               | 12            | 8                        | I/O | ST               | MSSP1 SPI Serial Input/Output Clock                       |

| SCL1     | 12                               | 9             | 8                        | I/O | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C Clock Input/Output                 |

| SCLKI    | 10                               | 7             | 12                       | I   | ST               | Digital Secondary Clock Input                             |

| SDA1     | 13                               | 10            | 9                        | I/O | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C Data Input/Output                  |

| SDI1     | 17                               | 14            | 11                       | Ι   | ST               | MSSP1 SPI Serial Data Input                               |

| SDO1     | 16                               | 13            | 9                        | 0   | _                | MSSP1 SPI Serial Data Output                              |

| SOSCI    | 9                                | 6             | 11                       | I   | ANA              | Secondary Oscillator Input                                |

| SOSCO    | 10                               | 7             | 12                       | 0   | ANA              | Secondary Oscillator Output                               |

| SS1      | 12                               | 9             | 12                       | 0   | _                | SPI1 Slave Select                                         |

| T1CK     | 13                               | 10            | 9                        | I   | ST               | Timer1 Clock                                              |

| ТЗСК     | 18                               | 15            | 12                       | I   | ST               | Timer3 Clock                                              |

| T3G      | 6                                | 3             | 11                       | Ι   | ST               | Timer3 External Gate Input                                |

| U1CTS    | 12                               | 9             | 8                        | Ι   | ST               | UART1 Clear-to-Send Input                                 |

| U1RTS    | 13                               | 10            | 9                        | 0   | _                | UART1 Request-to-Send Output                              |

| U1RX     | 6                                | 3             | 12                       | I   | ST               | UART1 Receive                                             |

| U1TX     | 11                               | 8             | 11                       | 0   | _                | UART1 Transmit                                            |

| ULPWU    | 3                                | 1             | 3                        | I   | ANA              | Ultra Low-Power Wake-up Input                             |

| VDD      | 20                               | 17            | 14                       | Р   |                  | Positive Supply for Peripheral Digital Logic and I/O Pins |

| VREF+    | 2                                | 19            | 2                        | I   | ANA              | A/D Reference Voltage Input (+)                           |

| VREF-    | 3                                | 20            | 3                        | I   | ANA              | A/D Reference Voltage Input (-)                           |

| Vss      | 19                               | 16            | 13                       | Р   | _                | Ground Reference for Logic and I/O Pins                   |

#### **TABLE 1-5:** PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

## TABLE 4-8: MSSP REGISTER MAP

| File Name               | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit 6   | Bit 5      | Bit 4        | Bit 3                                                    | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--------------|----------------------------------------------------------|------------|-------|-------|---------------|

| SSP1BUF                 | 0200 | _      | —      | _      | _      |        | —      | —     | —     | Image: Second Secon |         |            |              |                                                          |            | 00xx  |       |               |

| SSP1CON1                | 0202 | _      | _      | _      | _      | _      | _      | _     | _     | WCOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SSPOV   | SSPEN      | CKP          | SSPM3                                                    | SSPM2      | SSPM1 | SSPM0 | 0000          |

| SSP1CON2                | 0204 | _      | _      | _      | _      | _      | _      | _     | _     | GCEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ACKSTAT | ACKDT      | ACKEN        | RCEN                                                     | PEN        | RSEN  | SEN   | 0000          |

| SSP1CON3                | 0206 | _      | _      | _      | _      | _      | _      | _     | _     | ACKTIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PCIE    | SCIE       | BOEN         | SDAHT                                                    | SBCDE      | AHEN  | DHEN  | 0000          |

| SSP1STAT                | 0208 | _      | _      | _      | _      | _      | _      | _     | _     | SMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CKE     | D/Ā        | Р            | S                                                        | R/W        | UA    | BF    | 0000          |

| SSP1ADD                 | 020A | _      | _      | _      | _      | _      | —      | —     | _     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |              |                                                          |            | ode)  |       | 0000          |

| SSP1MSK                 | 020C | _      |        | _      | _      |        | _      | _     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | М       | SSP1 Addre | ess Mask R   | egister (I <sup>2</sup> C                                | Slave Mode | e)    |       | 00FF          |

| SSP2BUF <sup>(1)</sup>  | 0210 | _      |        | _      | _      |        | _      | _     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | MSSP2 F    | Receive Buff | er/Transmit                                              | Register   |       |       | 00xx          |

| SSP2CON1(1)             | 0212 | _      |        | _      | _      |        | _      | _     |       | WCOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SSPOV   | SSPEN      | CKP          | SSPM3                                                    | SSPM2      | SSPM1 | SSPM0 | 0000          |

| SSP2CON2(1)             | 0214 | _      | _      | _      | _      |        | _      | _     |       | GCEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ACKSTAT | ACKDT      | ACKEN        | RCEN                                                     | PEN        | RSEN  | SEN   | 0000          |

| SSP2CON3(1)             | 0216 | _      | _      | _      | —      | _      | _      | _     | _     | ACKTIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PCIE    | SCIE       | BOEN         | SDAHT                                                    | SBCDE      | AHEN  | DHEN  | 0000          |

| SSP2STAT <sup>(1)</sup> | 0218 | _      | _      | _      | _      | _      | _      | _     | _     | SMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CKE     | D/Ā        | Р            | S                                                        | R/W        | UA    | BF    | 0000          |

| SSP2ADD <sup>(1)</sup>  | 021A | _      | _      | _      | _      | _      | —      | _     | —     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MSS     |            |              | ster (I <sup>2</sup> C Sla<br>Register (I <sup>2</sup> C |            | ode)  |       | 0000          |

| SSP2MSK <sup>(1)</sup>  | 021C | _      | -      | _      | _      | _      | _      | _     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | М       | SSP2 Addre | ess Mask R   | egister (I <sup>2</sup> C                                | Slave Mode | e)    |       | 00FF          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

#### TABLE 4-9: UART REGISTER MAP

| IADLL 4      | <b>J</b> . | UANT     |                            |          |        |                                        |        |         |            |               |          |       |            |         |        |        |       |               |

|--------------|------------|----------|----------------------------|----------|--------|----------------------------------------|--------|---------|------------|---------------|----------|-------|------------|---------|--------|--------|-------|---------------|

| File<br>Name | Addr       | Bit 15   | Bit 14                     | Bit 13   | Bit 12 | Bit 11                                 | Bit 10 | Bit 9   | Bit 8      | Bit 7         | Bit 6    | Bit 5 | Bit 4      | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE       | 0220       | UARTEN   | —                          | USIDL    | IREN   | RTSMD                                  | _      | UEN1    | UEN0       | WAKE          | LPBACK   | ABAUD | RXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222       | UTXISEL1 | UTXINV                     | UTXISEL0 | _      | UTXBRK                                 | UTXEN  | UTXBF   | TRMT       | URXISEL1      | URXISEL0 | ADDEN | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224       | _        | _                          | _        | _      | _                                      |        | _       |            |               |          | UART1 | Transmit R | egister |        |        |       | xxxx          |

| U1RXREG      | 0226       | _        | _                          | _        | _      | _                                      |        | _       |            |               |          | UART1 | Receive Re | egister |        |        |       | 0000          |

| U1BRG        | 0228       |          |                            |          |        | Baud Rate Generator Prescaler Register |        |         |            |               |          |       |            | 0000    |        |        |       |               |

| U2MODE       | 0230       | UARTEN   | _                          | USIDL    | IREN   | RTSMD                                  |        | UEN1    | UEN0       | WAKE          | LPBACK   | ABAUD | RXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232       | UTXISEL1 | UTXINV                     | UTXISEL0 | _      | UTXBRK                                 | UTXEN  | UTXBF   | TRMT       | URXISEL1      | URXISEL0 | ADDEN | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234       | _        | UART2 Transmit Register xx |          |        |                                        |        |         |            |               |          | xxxx  |            |         |        |        |       |               |

| U2RXREG      | 0236       | _        | _                          | _        | _      | _                                      |        | _       |            |               |          | UART2 | Receive Re | egister |        |        |       | 0000          |

| U2BRG        | 0238       |          |                            |          |        |                                        |        | Baud Ra | ate Genera | tor Prescaler | Register |       |            |         |        |        |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12    | Bit 11                | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5 | Bit 4                | Bit 3                | Bit 2                | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|-----------|-----------------------|--------|--------|--------|---------|-------|-------|----------------------|----------------------|----------------------|--------|--------|---------------|

| ADC1BUF0     | 0300 |        |        |        |           |                       |        |        | A/D Bu | uffer 0 |       |       |                      |                      |                      |        |        | xxxx          |

| ADC1BUF1     | 0302 |        |        |        |           |                       |        |        | A/D Bu | uffer 1 |       |       |                      |                      |                      |        |        | xxxx          |

| AD1CON1      | 0320 | ADON   | —      | ADSIDL | —         | _                     | _      | FORM1  | FORM0  | SSRC2   | SSRC1 | SSRC0 | _                    |                      | ASAM                 | SAMP   | DONE   | 0000          |

| AD1CON2      | 0322 | VCFG2  | VCFG1  | VCFG0  | OFFCAL    | —                     | CSCNA  |        | _      | r       |       | SMPI3 | SMPI2                | SMPI1                | SMPI0                | r      | ALTS   | 0000          |

| AD1CON3      | 0324 | ADRC   | EXTSAM | PUMPEN | SAMC4     | SAMC3                 | SAMC2  | SAMC1  | SAMC0  |         |       | ADCS5 | ADCS4                | ADCS3                | ADCS2                | ADCS1  | ADCS0  | 0000          |

| AD1CHS       | 0328 | CH0NB  | —      |        | —         | CH0SB3                | CH0SB2 | CH0SB1 | CH0SB0 | CH0NA   |       | _     | _                    | CH0SA3               | CH0SA2               | CH0SA1 | CH0SA0 | 0000          |

| AD1CSSL      | 0330 | CSSL15 | CSSL14 | CSSL13 | CSSL12(1) | CSSL11 <sup>(1)</sup> | CSSL10 | CSSL9  | CSSL8  | CSSL7   | CSSL6 | _     | CSSL4 <sup>(1)</sup> | CSSL3 <sup>(1)</sup> | CSSL2 <sup>(1)</sup> | CSSL1  | CSSL0  | 0000          |

Legend: — = unimplemented, read as '0', r = reserved bit. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 14-pin devices; read as '0'.

#### TABLE 4-14: ANALOG SELECT REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12                | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2                | Bit 1                | Bit 0                | All<br>Resets       |

|-----------|------|--------|--------|--------|-----------------------|--------|--------|-------|-------|-------|-------|-------|-------|----------|----------------------|----------------------|----------------------|---------------------|

| ANCFG     | 04DE | _      | —      | —      | —                     | _      | _      |       | _     | _     | _     |       |       | _        | —                    |                      | VBGEN                | 0000                |

| ANSA      | 04E0 | -      | _      | -      | —                     | _      | -      | _     | _     | _     | _     | _     | _     | ANSA3    | ANSA2                | ANSA1                | ANSA0                | 000F                |

| ANSB      | 04E2 | ANSB15 | ANSB14 | ANSB13 | ANSB12 <sup>(1)</sup> | —      | _      | _     | _     | —     | —     | _     | ANSB4 | ANSB3(2) | ANSB2 <sup>(1)</sup> | ANSB1 <sup>(1)</sup> | ANSB0 <sup>(1)</sup> | F01F <sup>(3)</sup> |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 14-pin devices; read as '0'.

2: These bits are unimplemented in 14-pin and 20-pin devices; read as '0'

3: Reset value for 28-pin devices is shown.

### TABLE 4-15: COMPARATOR REGISTER MAP

| File<br>Name          | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------------------|------|--------|--------|--------|--------|--------|--------|----------------------|-------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT                | 0630 | CMIDL  | —      | _      |        | _      | _      | C2EVT <sup>(1)</sup> | C1EVT | —      | —      | _     |       | _     | _     | C2OUT | C1OUT | xxxx          |

| CVRCON                | 0632 | _      | _      | _      | _      | _      | _      | _                    | _     | CVREN  | CVROE  | CVRSS | CVR4  | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON                | 0634 | CON    | COE    | CPOL   | CLPWR  | —      | _      | CEVT                 | COUT  | EVPOL1 | EVPOL0 | —     | CREF  | —     | _     | CCH1  | CCH0  | xxxx          |

| CM2CON <sup>(1)</sup> | 0636 | CON    | COE    | CPOL   | CLPWR  | _      | _      | CEVT                 | COUT  | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented in PIC24FXXKL10X/20X devices; read as '0'.

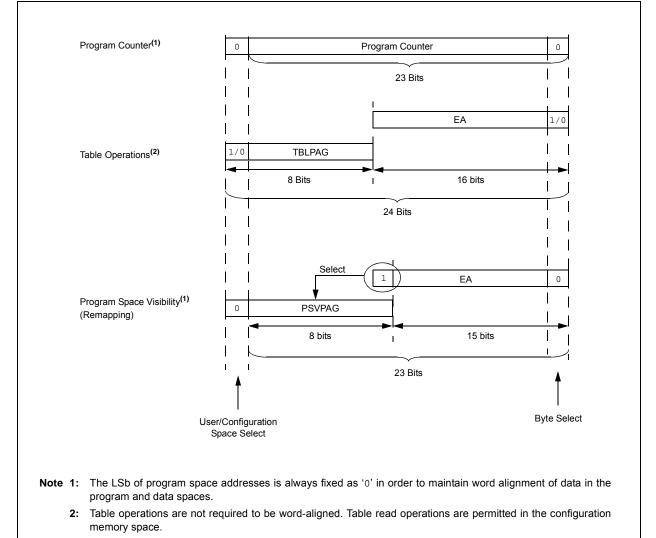

| A                        | Access        |      | Progra     | m Space A            | Address       |                |

|--------------------------|---------------|------|------------|----------------------|---------------|----------------|

| Access Type              | Space         | <23> | <22:16>    | <15>                 | <14:1>        | <0>            |

| Instruction Access       | User          | 0    |            | PC<22:1>             |               | 0              |

| (Code Execution)         |               |      | 0xx xxxx x | xxx xxxx             | x xxxx xxx0   |                |

| TBLRD/TBLWT              | User          | TBI  | _PAG<7:0>  |                      | Data EA<15:0> |                |

| (Byte/Word Read/Write)   |               | د0   | xxx xxxx   | XXX                  | ***           | xxx            |

|                          | Configuration | TBI  | _PAG<7:0>  |                      | Data EA<15:0> |                |

|                          |               | 12   | xxx xxxx   | XXX                  | ***           | xxx            |

| Program Space Visibility | User          | 0    | PSVPAG<7:  | <sub>0&gt;</sub> (2) | Data EA<14    | :0> <b>(1)</b> |

| (Block Remap/Read)       |               | 0    | XXXX XXX   | xx                   | XXX XXXX XXX  | x xxxx         |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) on PIC24F16KL402 family devices.

# 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing it is not recommended.

All of the Table Write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

# 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. For more information, refer to **Section 5.5 "Programming Operations"**.

# 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

## REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| R/W-0         | U-0                 | R/W-0                              | R/W-0           | R/W-0             | U-0              | U-0             | R/W-0       |

|---------------|---------------------|------------------------------------|-----------------|-------------------|------------------|-----------------|-------------|

| NVMIF         | _                   | AD1IF                              | U1TXIF          | U1RXIF            |                  |                 | T3IF        |

| bit 15        |                     |                                    |                 |                   |                  |                 | bit 8       |

|               | 5444.6              |                                    |                 | <b>-</b>          |                  |                 | 5444.6      |

| R/W-0         | R/W-0               | U-0                                | U-0             | R/W-0             | R/W-0            | U-0             | R/W-0       |

| T2IF          | CCP2IF              | —                                  | —               | T1IF              | CCP1IF           | —               | INTOIF      |

| bit 7         |                     |                                    |                 |                   |                  |                 | bit (       |

| Legend:       |                     |                                    |                 |                   |                  |                 |             |

| R = Readable  | e bit               | W = Writable                       | bit             | U = Unimplen      | nented bit, read | d as '0'        |             |

| -n = Value at | POR                 | '1' = Bit is set                   |                 | '0' = Bit is clea | ared             | x = Bit is unkı | nown        |

|               |                     |                                    |                 |                   |                  |                 |             |

| bit 15        | NVMIF: NVM          | I Interrupt Flag                   | Status bit      |                   |                  |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 14        | -                   | ted: Read as '                     |                 |                   |                  |                 |             |

| bit 13        | <b>AD1IF:</b> A/D ( | Conversion Cor                     | nplete Interrup | t Flag Status bit | t                |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

| h:1 40        | -                   | request has no                     |                 | Otatus hit        |                  |                 |             |

| bit 12        |                     | RT1 Transmitter                    |                 | Status bit        |                  |                 |             |

|               |                     | request has no                     |                 |                   |                  |                 |             |

| bit 11        | -                   | RT1 Receiver In                    |                 | tatus bit         |                  |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 10-9      | Unimplemer          | ted: Read as '                     | 0'              |                   |                  |                 |             |

| bit 8         | T3IF: Timer3        | Interrupt Flag                     | Status bit      |                   |                  |                 |             |

|               | •                   | request has oc                     |                 |                   |                  |                 |             |

|               |                     | request has no                     |                 |                   |                  |                 |             |

| bit 7         |                     | Interrupt Flag                     |                 |                   |                  |                 |             |

|               |                     | request has oc<br>request has no   |                 |                   |                  |                 |             |

| bit 6         |                     | -                                  |                 | ot Flag Status b  | it               |                 |             |

|               | •                   | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 5-4       | Unimplemer          | ted: Read as '                     | 0'              |                   |                  |                 |             |

| bit 3         | T1IF: Timer1        | Interrupt Flag                     | Status bit      |                   |                  |                 |             |

|               | •                   | request has oc<br>request has no   |                 |                   |                  |                 |             |

| bit 2         | -                   | -                                  |                 | ot Flag Status b  | it (ECCP1 on F   | PIC24FXXKL40    | )X devices) |

|               | 1 = Interrupt       | request has oc                     | curred          | 0                 | Υ.               |                 | ,           |

| L:1 4         | -                   | request has no                     |                 |                   |                  |                 |             |

| bit 1         | -                   | ted: Read as '                     |                 |                   |                  |                 |             |

|               |                     |                                    |                 |                   |                  |                 |             |

| bit 0         |                     | rnal Interrupt 0<br>request has oc | -               |                   |                  |                 |             |

| U-0          | U-0                    | U-0                    | U-0                    | U-0                | R/W-1                  | R/W-0                  | R/W-0                  |

|--------------|------------------------|------------------------|------------------------|--------------------|------------------------|------------------------|------------------------|

|              | —                      |                        |                        | _                  | BCL2IP2 <sup>(1)</sup> | BCL2IP1 <sup>(1)</sup> | BCL2IP0 <sup>(1)</sup> |

| bit 15       |                        |                        |                        |                    |                        |                        | bit 8                  |

|              |                        |                        |                        |                    |                        |                        |                        |

| U-0          | R/W-1                  | R/W-0                  | R/W-0                  | U-0                | U-0                    | U-0                    | U-0                    |

| —            | SSP2IP2 <sup>(1)</sup> | SSP2IP1 <sup>(1)</sup> | SSP2IP0 <sup>(1)</sup> | —                  | —                      | —                      | —                      |

| bit 7        |                        |                        |                        |                    |                        |                        | bit 0                  |

|              |                        |                        |                        |                    |                        |                        |                        |

| Legend:      |                        |                        |                        |                    |                        |                        |                        |

| R = Readab   | le bit                 | W = Writable           | bit                    | U = Unimplem       | nented bit, read       | l as '0'               |                        |

| -n = Value a | t POR                  | '1' = Bit is set       |                        | '0' = Bit is clea  | ared                   | x = Bit is unkn        | own                    |

|              |                        |                        |                        |                    |                        |                        |                        |

| bit 15-11    | •                      | ted: Read as '         |                        |                    |                        |                        |                        |

| bit 10-8     |                        |                        |                        | Interrupt Priori   | ty bits <sup>(1)</sup> |                        |                        |

|              | 111 = Interru          | pt is Priority 7(      | highest priority       | interrupt)         |                        |                        |                        |

|              | •                      |                        |                        |                    |                        |                        |                        |

|              | •                      |                        |                        |                    |                        |                        |                        |

|              | 001 = Interru          |                        |                        |                    |                        |                        |                        |

|              | •                      | pt source is dis       |                        |                    |                        |                        |                        |

| bit 7        | •                      | ted: Read as '         |                        |                    |                        |                        |                        |

| bit 6-4      |                        |                        |                        | rupt Priority bits | <sub>S</sub> (1)       |                        |                        |

|              | 111 = Interru          | ot is Priority 7 (     | highest priority       | interrupt)         |                        |                        |                        |

|              | •                      |                        |                        |                    |                        |                        |                        |

|              | •                      |                        |                        |                    |                        |                        |                        |

|              | 001 = Interru          | •                      |                        |                    |                        |                        |                        |

|              |                        | ot source is dis       |                        |                    |                        |                        |                        |

| bit 3-0      | Unimplemen             | ted: Read as 'o        | )'                     |                    |                        |                        |                        |

|              |                        |                        |                        |                    |                        |                        |                        |

### REGISTER 8-26: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

### REGISTER 8-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1                  | R/W-0                  | R/W-0                  |

|--------|-----|-----|-----|-----|------------------------|------------------------|------------------------|

| —      | —   | —   | —   | —   | U2ERIP2 <sup>(1)</sup> | U2ERIP1 <sup>(1)</sup> | U2ERIP0 <sup>(1)</sup> |

| bit 15 |     |     |     |     |                        |                        | bit 8                  |

| U-0   | R/W-1                  | R/W-0                  | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|-------|------------------------|------------------------|------------------------|-----|-----|-----|-------|

| _     | U1ERIP2 <sup>(1)</sup> | U1ERIP1 <sup>(1)</sup> | U1ERIP0 <sup>(1)</sup> |     |     | —   | —     |

| bit 7 |                        |                        |                        |     |     |     | bit 0 |

| Legend:      |            |                                 |                                            |                    |  |  |  |

|--------------|------------|---------------------------------|--------------------------------------------|--------------------|--|--|--|

| R = Readat   | ole bit    | W = Writable bit                | ble bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value a | at POR     | '1' = Bit is set                | '0' = Bit is cleared                       | x = Bit is unknown |  |  |  |

|              |            |                                 |                                            |                    |  |  |  |

| bit 15-11    | -          | nented: Read as '0'             |                                            |                    |  |  |  |

| bit 10-8     | U2ERIP<2   | 2:0>: UART2 Error Interrupt     | t Priority bits <sup>(1)</sup>             |                    |  |  |  |

|              | 111 = Inte | errupt is Priority 7 (highest p | priority interrupt)                        |                    |  |  |  |