Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 7x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | 14-TSSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl200-i-st |

#### **Table of Contents**

| 1.0   | Device Overview                                             | 9   |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 21  |

| 3.0   | CPU                                                         | 25  |

| 4.0   | Memory Organization                                         | 31  |

| 5.0   | Flash Program Memory                                        | 47  |

| 6.0   | Data EEPROM Memory                                          | 53  |

| 7.0   | Resets                                                      | 59  |

| 8.0   | Interrupt Controller                                        | 65  |

| 9.0   | Oscillator Configuration                                    | 95  |

| 10.0  | Power-Saving Features                                       | 105 |

| 11.0  | I/O Ports                                                   | 111 |

| 12.0  | Timer1                                                      | 115 |

| 13.0  | Timer2 Module                                               | 117 |

| 14.0  | Timer3 Module                                               | 119 |

| 15.0  | Timer4 Module                                               | 123 |

| 16.0  | Capture/Compare/PWM (CCP) and Enhanced CCP Modules          | 125 |

| 17.0  | Master Synchronous Serial Port (MSSP)                       | 135 |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)          | 149 |

| 19.0  | 10-Bit High-Speed A/D Converter                             | 157 |

| 20.0  | Comparator Module                                           | 167 |

| 21.0  |                                                             |     |

| 22.0  | High/Low-Voltage Detect (HLVD)                              | 173 |

| 23.0  | Special Features                                            | 175 |

| 24.0  | Development Support                                         | 187 |

| 25.0  | Instruction Set Summary                                     | 191 |

| 26.0  |                                                             |     |

| 27.0  | Packaging Information                                       | 225 |

| Appe  | endix A: Revision History                                   | 251 |

| Appe  | endix B: Migrating from PIC18/PIC24 to PIC24F16KL402        | 251 |

| Index | x                                                           | 253 |

| The I | Microchip Web Site                                          | 257 |

| Custo | omer Change Notification Service                            | 257 |

| Custo | omer Support                                                | 257 |

| Prod  | uct Identification System                                   | 250 |

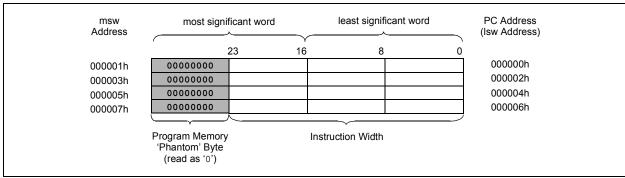

# 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address, as shown in Figure 4-2.

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

#### 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 00000h and 000200h for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h, with the actual address for the start of code at 000002h.

PIC24F devices also have two Interrupt Vector Tables (IVT), located from 000004h to 0000FFh and 000104h to 0001FFh. These vector tables allow each of the many device interrupt sources to be handled by separate ISRs. A more detailed discussion of the Interrupt Vector Tables is provided in **Section 8.1** "Interrupt Vector Table (IVT)".

#### 4.1.3 DATA EEPROM

In the PIC24F16KL402 family, the data EEPROM is mapped to the top of the user program memory space, starting at address, 7FFE00, and expanding up to address, 7FFFFF.

The data EEPROM is organized as 16-bit wide memory and 256 words deep. This memory is accessed using Table Read and Table Write operations, similar to the user code memory.

#### 4.1.4 DEVICE CONFIGURATION WORDS

Table 4-1 provides the addresses of the device Configuration Words for the PIC24F16KL402 family. Their location in the memory map is shown in Figure 4-1.

For more information on device Configuration Words, see Section 23.0 "Special Features".

TABLE 4-1: DEVICE CONFIGURATION

WORDS FOR PIC24F16KL402

FAMILY DEVICES

| Configuration Words | Configuration Word<br>Addresses |

|---------------------|---------------------------------|

| FBS                 | F80000                          |

| FGS                 | F80004                          |

| FOSCSEL             | F80006                          |

| FOSC                | F80008                          |

| FWDT                | F8000A                          |

| FPOR                | F8000C                          |

| FICD                | F8000E                          |

TABLE 4-4: ICN REGISTER MAP

| File<br>Name | Addr | Bit 15                 | Bit 14                 | Bit 13                 | Bit 12  | Bit 11                 | Bit 10 | Bit 9                 | Bit 8                  | Bit 7                  | Bit 6                 | Bit 5                 | Bit 4                 | Bit 3  | Bit 2  | Bit 1  | Bit 0                  | All<br>Resets |

|--------------|------|------------------------|------------------------|------------------------|---------|------------------------|--------|-----------------------|------------------------|------------------------|-----------------------|-----------------------|-----------------------|--------|--------|--------|------------------------|---------------|

| CNPD1        | 0056 | CN15PDE <sup>(1)</sup> | CN14PDE <sup>(1)</sup> | CN13PDE <sup>(1)</sup> | CN12PDE | CN11PDE                | _      | CN9PDE <sup>(2)</sup> | CN8PDE                 | CN7PDE <sup>(2)</sup>  | CN6PDE <sup>(1)</sup> | CN5PDE <sup>(1)</sup> | CN4PDE <sup>(1)</sup> | CN3PDE | CN2PDE | CN1PDE | CN0PDE                 | 0000          |

| CNPD2        | 0058 | -                      | CN30PDE                | CN29PDE                | _       | CN27PDE <sup>(2)</sup> | _      | _                     | CN24PDE <sup>(2)</sup> | CN23PDE <sup>(1)</sup> | CN22PDE               | CN21PDE               | -                     | ı      | 1      | -      | CN16PDE <sup>(2)</sup> | 0000          |

| CNEN1        | 0062 | CN15IE <sup>(1)</sup>  | CN14IE <sup>(1)</sup>  | CN13IE <sup>(1)</sup>  | CN12IE  | CN11IE                 | _      | CN9IE <sup>(1)</sup>  | CN8IE                  | CN7IE <sup>(1)</sup>   | CN6IE <sup>(2)</sup>  | CN5PIE <sup>(2)</sup> | CN4IE <sup>(2)</sup>  | CN3IE  | CNIE   | CN1IE  | CN0IE                  | 0000          |

| CNEN2        | 0064 | _                      | CN30IE                 | CN29IE                 | _       | CN27IE <sup>(2)</sup>  | _      | _                     | CN24IE <sup>(2)</sup>  | CN23IE <sup>(1)</sup>  | CN22IE                | CN21IE                | ı                     | 1      | 1      |        | CN16IE <sup>(2)</sup>  | 0000          |

| CNPU1        | 006E | CN15PUE <sup>(1)</sup> | CN14PUE <sup>(1)</sup> | CN13PUE <sup>(1)</sup> | CN12PUE | CN11PUE                | _      | CN9PUE <sup>(1)</sup> | CN8PUE                 | CN7PUE <sup>(1)</sup>  | CN6PUE <sup>(2)</sup> | CN5PUE <sup>(2)</sup> | CN4PUE <sup>(2)</sup> | CN3PUE | CN2PUE | CN1PUE | CN0PUE                 | 0000          |

| CNPU2        | 0070 | _                      | CN30PUE                | CN29PUE                | _       | CN27PUE <sup>(2)</sup> | _      | _                     | CN24PUE <sup>(2)</sup> | CN23PUE <sup>(1)</sup> | CN22PUE               | CN21PUE               | I                     |        | -      |        | CN16PUE <sup>(2)</sup> | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 14-pin devices; read as '0'.

2: These bits are unimplemented in 14-pin and 20-pin devices; read as '0'.

#### TABLE 4-16: SYSTEM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | SBOREN | _      | _      | -      | CM     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 3100          |

| OSCTUN    | 0748 | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 074E | ROEN   | _      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN | _      | HLSIDL | _      | _      | ı      | ı      | -      | VDIR    | BGVST | IRVST  | -     | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on configuration fuses and by type of Reset.

#### **TABLE 4-17: NVM REGISTER MAP**

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5  | Bit 4   | Bit 3      | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|---------|--------|--------|-------|-------|-------|-------|--------|---------|------------|--------|--------|--------|---------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | PGMONLY | _      | _      | _     | _     | _     | ERASE | NVMOP5 | NVMOP4  | NVMOP3     | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMKEY    | 0766 | _      | _      | _      | _       | 1      | _      | _     | _     |       |       |        | NVM Key | / Register |        |        |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-18: ULTRA LOW-POWER WAKE-UP REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|---------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ULPWCON   | 0768 | ULPEN  | _      | ULPSIDL | _      | _      | _      | _     | ULPSINK | _     | _     | _     | _     | _     | _     | _     | _     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-19: PMD REGISTER MAP

| .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      |        | <b></b> |        |        |        |        |       |       |         |       |       |       |        |        |        |        |            |

|-----------------------------------------|------|--------|---------|--------|--------|--------|--------|-------|-------|---------|-------|-------|-------|--------|--------|--------|--------|------------|

| File Name                               | Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

| PMD1                                    | 0770 | _      | T4MD    | T3MD   | T2MD   | T1MD   | _      | -     | _     | SSP1MD  | U2MD  | U1MD  | -     | _      | _      | 1      | ADC1MD | 0000       |

| PMD2                                    | 0772 | _      | _       | _      | _      | _      | _      | ı     | _     | _       | ı     | _     | -     | _      | CCP3MD | CCP2MD | CCP1MD | 0000       |

| PMD3                                    | 0774 | _      | _       | _      | _      | _      | CMPMD  | ı     | _     | _       | ı     | _     | -     | _      | _      | SSP2MD | ı      | 0000       |

| PMD4                                    | 0776 | _      | _       | _      | _      | _      | _      | _     | _     | ULPWUMD | _     | _     | EEMD  | REFOMD |        | HLVDMD | _      | 0000       |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0  | R/W-0 <sup>(3)</sup> | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|--------|----------------------|-----|-----|-----|-------|-------|

| TRAPR  | IOPUWR | SBOREN               | _   | _   | _   | CM    | PMSLP |

| bit 15 |        |                      |     |     |     |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0                 | R/W-0 | R/W-0 | R/W-0 | R/W-1 | R/W-1 |

|-------|-------|-----------------------|-------|-------|-------|-------|-------|

| EXTR  | SWR   | SWDTEN <sup>(2)</sup> | WDTO  | SLEEP | IDLE  | BOR   | POR   |

| bit 7 |       |                       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 TRAPR: Trap Reset Flag bit

1 = A Trap Conflict Reset has occurred0 = A Trap Conflict Reset has not occurred

bit 14 IOPUWR: Illegal Opcode or Uninitialized W Access Reset Flag bit

1 = An illegal opcode detection, an illegal address mode or an Uninitialized W register is used as an

Address Pointer and caused a Reset

0 = An illegal opcode or Uninitialized W register Reset has not occurred

bit 13 SBOREN: Software Enable/Disable of BOR bit<sup>(3)</sup>

1 = BOR is turned on in software0 = BOR is turned off in software

bit 12-10 **Unimplemented:** Read as '0'

bit 9 CM: Configuration Word Mismatch Reset Flag bit

1 = A Configuration Word Mismatch Reset has occurred0 = A Configuration Word Mismatch Reset has not occurred

bit 8 **PMSLP:** Program Memory Power During Sleep bit

1 = Program memory bias voltage remains powered during Sleep0 = Program memory bias voltage is powered down during Sleep

bit 7 **EXTR:** External Reset (MCLR) Pin bit

1 = A Master Clear (pin) Reset has occurred 0 = A Master Clear (pin) Reset has not occurred

0 - 7 Master Olear (pin) reset has not occurre

bit 6 SWR: Software Reset (Instruction) Flag bit

1 = A RESET instruction has been executed 0 = A RESET instruction has not been executed

0 - A RESET INSTRUCTION HAS NOT DEEN executed

**SWDTEN:** Software Enable/Disable of WDT bit<sup>(2)</sup>

1 = WDT is enabled 0 = WDT is disabled

bit 4 WDTO: Watchdog Timer Time-out Flag bit

1 = WDT time-out has occurred

0 = WDT time-out has not occurred

**Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** The SBOREN bit is forced to '0' when disabled by the Configuration bits, BOREN<1:0> (FPOR<1:0>). When the Configuration bits are set to enable SBOREN, the default Reset state will be '1'.

bit 5

#### REGISTER 8-1: SR: ALU STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0             |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

| _      | _   | _   | _   | _   | _   | _   | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0                 | R/W-0                 | R/W-0                 | R-0               | R/W-0            | R/W-0             | R/W-0            | R/W-0            |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 **Unimplemented:** Read as '0'

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup>

111 = CPU Interrupt Priority Level is 7 (15); user interrupts disabled

110 = CPU Interrupt Priority Level is 6 (14)

101 = CPU Interrupt Priority Level is 5 (13)

100 = CPU Interrupt Priority Level is 4 (12)

011 = CPU Interrupt Priority Level is 3 (11)

010 = CPU Interrupt Priority Level is 2 (10)

001 = CPU Interrupt Priority Level is 1 (9)

000 = CPU Interrupt Priority Level is 0 (8)

Note 1: See Register 3-1 for the description of these bits, which are not dedicated to interrupt control functions.

2: The IPL bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

3: The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

Note: Bit 8 and bits 4 through 0 are described in Section 3.0 "CPU".

#### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER2

| R/W-0  | R-0, HSC | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|----------|-----|-----|-----|-----|-----|-------|

| ALTIVT | DISI     | _   | _   | _   | _   | _   | _     |

| bit 15 | •        | •   |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| _     | _   | _   | _   | _   | INT2EP | INT1EP | INT0EP |

| bit 7 |     |     |     |     |        |        | bit 0  |

**Legend:** HSC = Hardware Settable/Clearable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 ALTIVT: Enable Alternate Interrupt Vector Table bit

1 = Uses Alternate Interrupt Vector Table0 = Uses standard (default) vector table

bit 14 DISI: DISI Instruction Status bit

1 = DISI instruction is active 0 = DISI instruction is not active

bit 13-3 **Unimplemented:** Read as '0'

bit 2 INT2EP: External Interrupt 2 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 1 INT1EP: External Interrupt 1 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 0 INT0EP: External Interrupt 0 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

#### REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-------|-----|-----|-----|-----|-------|

| _     | _   | T3GIF | _   | _   | _   | _   | _     |

| bit 7 |     |       |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 Unimplemented: Read as '0'

bit 5 T3GIF: Timer3 External Gate Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 4-0 **Unimplemented:** Read as '0'

#### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                 | U-0   |

|-------|-----|-----|-----|-----|-----------------------|-----------------------|-------|

| _     | _   | _   | _   | _   | BCL2IF <sup>(1)</sup> | SSP2IF <sup>(1)</sup> | _     |

| bit 7 |     |     |     |     |                       |                       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **Unimplemented:** Read as '0'

bit 2 BCL2IF: MSSP2 I<sup>2</sup>C™ Bus Collision Interrupt Flag Status bit<sup>(1)</sup>

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 1 SSP2IF: MSSP2 SPI/I<sup>2</sup>C Event Interrupt Flag Status bit<sup>(1)</sup>

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 **Unimplemented:** Read as '0'

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

#### REGISTER 8-25: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0   |

|-------|--------|--------|--------|-----|-----|-----|-------|

| _     | T3GIP2 | T3GIP1 | T3GIP0 | _   | _   | _   | _     |

| bit 7 |        |        |        |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 Unimplemented: Read as '0'

bit 6-4 T3GIP<2:0>: Timer3 External Gate Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3-0 **Unimplemented:** Read as '0'

#### 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

PIC24F16KL402 family devices consist of two types of secondary oscillators:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

- · Fast Internal RC (FRC) Oscillator

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

- Low-Power Internal RC (LPRC) Oscillator with two modes:

- High-Power/High-Accuracy mode

- Low-Power/Low-Accuracy mode

The primary oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, Fcy. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clock, Fosc/2, can be provided on the OSCO I/O pin for some operating modes of the primary oscillator.

#### 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (for more information, see Section 23.2 "Configuration Bits"). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The secondary oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC Frequency Range Configuration POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is "frequency range is greater than 8 MHz".

The Configuration bits allow users to choose between the various clock modes, shown in Table 9-1.

# 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSMx Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                   | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|---------------------------------------------------|-------------------|-------------|------------|-------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)     | Internal          | 11          | 111        | 1, 2  |

| 500 kHz FRC Oscillator with Postscaler (LPFRCDIV) | Internal          | 11          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                    | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator (SOSC)              | Secondary         | 0.0         | 100        | 1     |

| Primary Oscillator (HS) with PLL Module (HSPLL)   | Primary           | 10          | 011        |       |

| Primary Oscillator (EC) with PLL Module (ECPLL)   | Primary           | 0.0         | 011        |       |

| Primary Oscillator (HS)                           | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                           | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                           | Primary           | 0.0         | 010        |       |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)     | Internal          | 11          | 001        | 1     |

| 8 MHz FRC Oscillator (FRC)                        | Internal          | 11          | 000        | 1     |

Note 1: OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 11.3 Input Change Notification

The Input Change Notification (ICN) function of the I/O ports allows the PIC24F16KL402 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 23 external signals that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the Change Notification (CN) module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to Vss, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately, using the CNPD1 and CNPD2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to Vss by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

Note:

Pull-ups and pull-downs on Change Notification pins should always be disabled whenever the port pin is configured as a digital output.

#### **EXAMPLE 11-1: PORT WRITE/READ EXAMPLE (ASSEMBLY LANGUAGE)**

```

MOV #0xFF00, W0 ; Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs

MOV W0, TRISB

MOV #0x00FF, W0 ; Enable PORTB<15:8> digital input buffers

MOV W0, ANSB

NOP ; Delay 1 cycle

BTSS PORTB, #13 ; Next Instruction

```

#### **EXAMPLE 11-2: PORT WRITE/READ EXAMPLE (C LANGUAGE)**

```

TRISB = 0xFF00; // Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs

ANSB = 0x00FF; // Enable PORTB<15:8> digital input buffers

NOP(); // Delay 1 cycle

if(PORTBbits.RB13 == 1) // execute following code if PORTB pin 13 is set.

{

}

```

#### REGISTER 16-1: CCPxCON: CCPx CONTROL REGISTER (STANDARD CCP MODULES)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|

| _     | _   | DCxB1 | DCxB0 | CCPxM3 <sup>(1)</sup> | CCPxM2 <sup>(1)</sup> | CCPxM1 <sup>(1)</sup> | CCPxM0 <sup>(1)</sup> |

| bit 7 |     |       |       |                       |                       |                       | bit 0                 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-4 DCxB<1:0>: PWM Duty Cycle Bit 1 and Bit 0 for CCPx Module bits

Capture and Compare modes:

Unused.

PWM mode:

These bits are the two Least Significant bits (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight Most Significant bits (DCxB<9:2>) of the duty cycle are found in CCPRxL.

bit 3-0 CCPxM<3:0>: CCPx Module Mode Select bits<sup>(1)</sup>

1111 = Reserved

1110 = Reserved

1101 = Reserved

1100 = PWM mode

1011 = Compare mode: Special Event Trigger; resets timer on CCPx match (CCPxIF bit is set)

1010 = Compare mode: Generates software interrupt on compare match (CCPxIF bit is set, CCPx pin reflects I/O state)

1001 = Compare mode: Initializes CCPx pin high; on compare match, forces CCPx pin low (CCPxIF bit is set)

1000 = Compare mode: Initializes CCPx pin low; on compare match, forces CCPx pin high (CCPxIF bit is set)

0111 = Capture mode: Every 16th rising edge

0110 = Capture mode: Every 4th rising edge

0101 = Capture mode: Every rising edge

0100 = Capture mode: Every falling edge

0011 = Reserved

0010 = Compare mode: Toggles output on match (CCPxIF bit is set)

0001 = Reserved

0000 = Capture/Compare/PWM is disabled (resets CCPx module)

Note 1: CCPxM<3:0> = 1011 will only reset the timer and not start the A/D conversion on a CCPx match.

#### REGISTER 16-3: ECCP1AS: ECCP1 AUTO-SHUTDOWN CONTROL REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|---------|---------|---------|--------|--------|--------|--------|

| ECCPASE | ECCPAS2 | ECCPAS1 | ECCPAS0 | PSSAC1 | PSSAC0 | PSSBD1 | PSSBD0 |

| bit 7   |         |         |         |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7 ECCPASE: ECCP1 Auto-Shutdown Event Status bit

1 = A shutdown event has occurred; ECCP outputs are in a shutdown state

0 = ECCP outputs are operating

bit 6-4 ECCPAS<2:0>: ECCP1 Auto-Shutdown Source Select bits

111 = VIL on  $\overline{FLTO}$  pin, or either C1OUT or C2OUT is high

110 = VIL on FLT0 pin or C2OUT comparator output is high

101 = VIL on FLT0 pin or C1OUT comparator output is high

100 = VIL on  $\overline{FLTO}$  pin

011 = Either C1OUT or C2OUT is high

010 = C2OUT comparator output is high

001 = C1OUT comparator output is high

000 = Auto-shutdown is disabled

bit 3-2 PSSAC<1:0>: P1A and P1C Pins Shutdown State Control bits

1x = P1A and P1C pins tri-state

01 = Drive pins, P1A and P1C, to '1'

00 = Drive pins, P1A and P1C, to '0'

bit 1-0 PSSBD<1:0>: P1B and P1D Pins Shutdown State Control bits

1x = P1B and P1D pins tri-state

01 = Drive pins, P1B and P1D, to '1'

00 = Drive pins, P1B and P1D, to '0'

Note 1: This register is implemented only on PIC24FXXKL40X/30X devices.

**Note 1:** The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.

2: Writing to the ECCPASE bit is disabled while an auto-shutdown condition persists.

**3:** Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

#### REGISTER 19-3: AD1CON3: A/D CONTROL REGISTER 3

| R/W-0  | R-0    | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|-------|-------|-------|-------|-------|

| ADRC   | EXTSAM | PUMPEN | SAMC4 | SAMC3 | SAMC2 | SAMC1 | SAMC0 |

| bit 15 |        |        |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | ADCS5 | ADCS4 | ADCS3 | ADCS2 | ADCS1 | ADCS0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 ADRC: A/D Conversion Clock Source bit 1 = A/D internal RC clock 0 = Clock derived from system clock bit 14 **EXTSAM:** Extended Sampling Time bit 1 = A/D is still sampling after SAMP = 0 0 = A/D is finished sampling bit 13 **PUMPEN:** Charge Pump Enable bit 1 = Charge pump for switches is enabled 0 = Charge pump for switches is disabled bit 12-8 SAMC<4:0>: Auto-Sample Time bits 11111 = 31 TAD 00001 = 1 TAD00000 = 0 TAD (not recommended) bit 7-6 Unimplemented: Maintain as '0' bit 5-0 ADCS<5:0>: A/D Conversion Clock Select bits 11111 = 64 • Tcy 11110 = 63 • Tcy 00001 = 2 • Tcy 00000 = Tcy

#### REGISTER 23-3: FOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER

| R/P-1 | R/P-1   | R/P-1   | U-0 | U-0 | R/P-0  | R/P-0  | R/P-1  |

|-------|---------|---------|-----|-----|--------|--------|--------|

| IESO  | LPRCSEL | SOSCSRC | _   | _   | FNOSC2 | FNOSC1 | FNOSC0 |

| bit 7 |         |         |     |     |        |        | bit 0  |

R = Readable bit P = Programmable bit

Legend:

U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **IESO:** Internal External Switchover bit

1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

bit 6 LPRCSEL: Internal LPRC Oscillator Power Select bit

1 = High-Power/High-Accuracy mode0 = Low-Power/Low-Accuracy mode

bit 5 SOSCSRC: Secondary Oscillator Clock Source Configuration bit

1 = SOSC analog crystal function is available on the SOSCI/SOSCO pins

0 = SOSC crystal is disabled; digital SCLKI function is selected on the SOSCO pin

bit 4-3 Unimplemented: Read as '0'

bit 2-0 FNOSC<2:0>: Oscillator Selection bits

111 = 8 MHz FRC Oscillator with Divide-by-N (FRCDIV)

110 = 500 kHz Low-Power FRC Oscillator with Divide-by-N (LPFRCDIV)

101 = Low-Power RC Oscillator (LPRC)

100 = Secondary Oscillator (SOSC)

011 = Primary Oscillator with PLL module (HS+PLL, EC+PLL)

010 = Primary Oscillator (XT, HS, EC)

001 = 8 MHz FRC Oscillator with Divide-by-N with PLL module (FRCDIV+PLL)

000 = 8 MHz FRC Oscillator (FRC)

#### 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

#### 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### TABLE 26-13: DC CHARACTERISTICS: DATA EEPROM MEMORY

| DC CHARACTERISTICS |        |                                                         |                                             | d Operating temperat | ure -40 | $0^{\circ}C \leq TA$ | <b>8V to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +125°C for Extended |

|--------------------|--------|---------------------------------------------------------|---------------------------------------------|----------------------|---------|----------------------|----------------------------------------------------------------------|

| Param<br>No.       | Sym    | Characteristic                                          | Min Typ <sup>(1)</sup> Max Units Conditions |                      |         |                      |                                                                      |

|                    |        | Data EEPROM Memory                                      |                                             |                      |         |                      |                                                                      |

| D140               | EPD    | Cell Endurance                                          | 100,000                                     | _                    | _       | E/W                  |                                                                      |

| D141               | VPRD   | VDD for Read                                            | VMIN                                        | _                    | 3.6     | V                    | Vмін = Minimum operating voltage                                     |

| D143A              | TIWD   | Self-Timed Write Cycle<br>Time                          | _                                           | 4                    | _       | ms                   |                                                                      |

| D143B              | TREF   | Number of Total<br>Write/Erase Cycles Before<br>Refresh | _                                           | 10M                  | _       | E/W                  |                                                                      |

| D144               | TRETDD | Characteristic Retention                                | 40                                          | _                    | _       | Year                 | Provided no other specifications are violated                        |

| D145               | IDDPD  | Supply Current during<br>Programming                    | _                                           | 7                    |         | mA                   |                                                                      |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

#### TABLE 26-14: DC CHARACTERISTICS: COMPARATOR

Standard Operating Conditions: 2.0V < VDD < 3.6V

Operating temperature  $-40^{\circ}\text{C} < \text{Ta} \le +85^{\circ}\text{C}$  (unless otherwise stated)

$-40^{\circ}C \le TA \le +125^{\circ}C$  for Extended

| Param<br>No. | Symbol | Characteristic              | Min | Тур | Max | Units | Comments |

|--------------|--------|-----------------------------|-----|-----|-----|-------|----------|

| D300         | VIOFF  | Input Offset Voltage        | _   | 20  | 40  | mV    |          |

| D301         | VICM   | Input Common-Mode Voltage   | 0   | _   | VDD | V     |          |

| D302         | CMRR   | Common-Mode Rejection Ratio | 55  |     |     | dB    |          |

#### TABLE 26-15: DC CHARACTERISTICS: COMPARATOR VOLTAGE REFERENCE

Standard Operating Conditions: 2.0V < VDD < 3.6V

Operating temperature  $-40^{\circ}\text{C} < \text{Ta} \le +85^{\circ}\text{C}$  (unless otherwise stated)

-40°C  $\leq$  TA  $\leq$  +125°C for Extended

| Param<br>No. | Symbol | Characteristic          | Min | Тур | Max        | Units | Comments |

|--------------|--------|-------------------------|-----|-----|------------|-------|----------|

| VRD310       | CVRES  | Resolution              | _   | _   | VDD/32     | LSb   |          |

| VRD311       | CVRAA  | Absolute Accuracy       | _   | _   | AVDD - 1.5 | LSb   |          |

| VRD312       | CVRur  | Unit Resistor Value (R) | _   | 2k  | _          | Ω     |          |

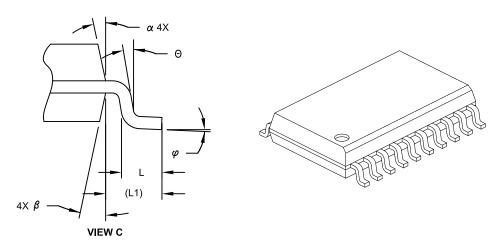

#### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                              | Units         |           |           | MILLIMETERS |  |  |  |

|------------------------------|---------------|-----------|-----------|-------------|--|--|--|

| Dimension Lim                | nits          | MIN       | NOM       | MAX         |  |  |  |

| Number of Pins               | N             |           | 20        |             |  |  |  |

| Pitch                        | е             |           | 1.27 BSC  |             |  |  |  |

| Overall Height               | Α             | -         | -         | 2.65        |  |  |  |

| Molded Package Thickness     | A2            | 2.05      | -         | -           |  |  |  |

| Standoff §                   | A1            | 0.10      | -         | 0.30        |  |  |  |

| Overall Width                | E             | •         | 10.30 BSC |             |  |  |  |

| Molded Package Width E1 7.50 |               |           | 7.50 BSC  |             |  |  |  |

| Overall Length               | D             | 12.80 BSC |           |             |  |  |  |

| Chamfer (Optional)           | h             | 0.25      | -         | 0.75        |  |  |  |

| Foot Length                  | L             | 0.40      | ı         | 1.27        |  |  |  |

| Footprint                    | L1            |           | 1.40 REF  |             |  |  |  |

| Lead Angle                   | Θ             | 0°        | -         | -           |  |  |  |

| Foot Angle                   | φ             | 0°        | -         | 8°          |  |  |  |

| Lead Thickness               | С             | 0.20      | -         | 0.33        |  |  |  |

| Lead Width                   | b             | 0.31      | -         | 0.51        |  |  |  |

| Mold Draft Angle Top         | t Angle Top α |           |           | 15°         |  |  |  |

| Mold Draft Angle Bottom      | β             | 5°        | =         | 15°         |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2

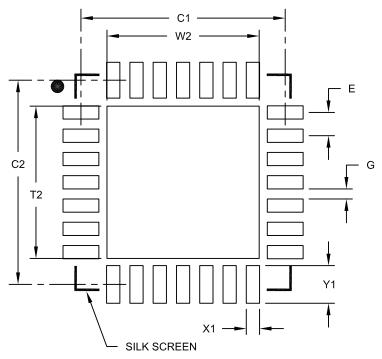

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                             |     | MILLIM | ETERS    |      |

|-----------------------------|-----|--------|----------|------|

| Dimension                   | MIN | NOM    | MAX      |      |

| Contact Pitch               | Е   |        | 0.65 BSC |      |

| Optional Center Pad Width   | W2  |        |          | 4.25 |

| Optional Center Pad Length  | T2  |        |          | 4.25 |

| Contact Pad Spacing         | C1  |        | 5.70     |      |

| Contact Pad Spacing         | C2  |        | 5.70     |      |

| Contact Pad Width (X28)     | X1  |        |          | 0.37 |

| Contact Pad Length (X28) Y1 |     |        |          | 1.00 |

| Distance Between Pads       | G   | 0.20   |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

| Program Memory                                   | IEC4 (Interrupt Enable Control 4)                 | 80  |

|--------------------------------------------------|---------------------------------------------------|-----|

| Address Space31                                  | IEC5 (Interrupt Enable Control 5)                 | 80  |

| Data EEPROM32                                    | IFS0 (Interrupt Flag Status 0)                    | 73  |

| Device Configuration Words32                     | IFS1 (Interrupt Flag Status 1)                    | 74  |

| Hard Memory Vectors32                            | IFS2 (Interrupt Flag Status 2)                    | 75  |

| Organization32                                   | IFS3 (Interrupt Flag Status 3)                    | 75  |

| Program Space                                    | IFS4 (Interrupt Flag Status 4)                    | 76  |

| Memory Map31                                     | IFS5 (Interrupt Flag Status 5)                    | 76  |

| Program Verification                             | INTCON 2 (Interrupt Control 2)                    |     |

| PWM (CCP Module)                                 | INTCON1 (Interrupt Control 1)                     |     |

| TMR4 to PR4 Match123                             | INTTREG (Interrupt Control and Status)            |     |

|                                                  | IPC0 (Interrupt Priority Control 0)               |     |

| R                                                | IPC1 (Interrupt Priority Control 1)               |     |

| Register Maps                                    | IPC12 (Interrupt Priority Control 12)             |     |

| A/D Converter41                                  | IPC16 (Interrupt Priority Control 16)             |     |

| Analog Select41                                  | IPC18 (Interrupt Priority Control 18)             |     |

| CCP/ECCP                                         | IPC2 (Interrupt Priority Control 2)               |     |

| Comparator                                       | IPC20 (Interrupt Priority Control 20)             |     |

| CPU Core                                         | ` ' '                                             |     |

| ICN                                              | IPC3 (Interrupt Priority Control 3)               |     |

| Interrupt Controller                             | IPC4 (Interrupt Priority Control 4)               |     |

|                                                  | IPC5 (Interrupt Priority Control 5)               |     |

| MSSP                                             | IPC6 (Interrupt Priority Control 6)               |     |

| NVM                                              | IPC7 (Interrupt Priority Control 7)               |     |

| Pad Configuration                                | IPC9 (Interrupt Priority Control 9)               |     |

| PMD42                                            | NVMCON (Flash Memory Control)                     |     |

| PORTA40                                          | NVMCON (Nonvolatile Memory Control)               |     |

| PORTB40                                          | OSCCON (Oscillator Control)                       |     |

| System, Clock Control42                          | OSCTUN (FRC Oscillator Tune)                      | 100 |

| Timer38                                          | PADCFG1 (Pad Configuration Control)               | 147 |

| UART39                                           | PSTR1CON (ECCP1 Pulse Steering Control)           |     |

| Ultra Low-Power Wake-up42                        | RCON (Reset Control)                              | 60  |

| Registers                                        | REFOCON (Reference Oscillator Control)            | 103 |

| AD1CHS (A/D Input Select)162                     | SR (ALU STATUS)                                   |     |

| AD1CON1 (A/D Control 1) 159                      | SSPxADD (MSSPx Slave Address/Baud                 | •   |

| AD1CON2 (A/D Control 2) 160                      | Rate Generator)                                   | 146 |

| AD1CON3 (A/D Control 3) 161                      | SSPxCON1 (MSSPx Control 1, I <sup>2</sup> C Mode) |     |

| AD1CSSL (A/D Input Scan Select)163               | SSPxCON1 (MSSPx Control 1, SPI Mode)              |     |

| ANCFG (Analog Input Configuration)               | SSPxCON2 (MSSPx Control 2, I <sup>2</sup> C Mode) |     |

| ANSA (PORTA Analog Selection)                    | SSPxCON3 (MSSPx Control 3, I <sup>2</sup> C Mode) |     |

| ANSB (PORTB Analog Selection)113                 | SSPxCON3 (MSSPx Control 3, SPI Mode)              |     |

| CCP1CON (ECCP1 Control, Enhanced CCP)129         | SSPxMSK (I <sup>2</sup> C Slave Address Mask)     |     |

| CCPTMRS0 (CCP Timer Select Control 0)            | SSPxSTAT (MSSPx Status, I <sup>2</sup> C Mode)    |     |

| CCPxCON (CCPx Control, Standard CCP)128          | SSPxSTAT (MSSPx Status, SPI Mode)                 |     |

| CLKDIV (Clock Divider)99                         | T1CON (Timer1 Control)                            |     |

| CMSTAT (Comparator Status)170                    | · · · · · · · · · · · · · · · · · · ·             |     |

| CMxCON (Comparator x Control)                    | T2CON (Timer2 Control)                            |     |

|                                                  | T3CON (Timer3 Control)                            |     |

| CORCON (CPU Control)                             | T3GCON (Timer3 Gate Control)                      |     |

| CVRCON (Comparator Voltage                       | T4CON (Timer4 Control)                            |     |

| Reference Control)                               | ULPWCON (ULPWU Control)                           |     |

| DEVID (Device ID)                                | UxMODE (UARTx Mode)                               |     |

| DEVREV (Device Revision)183                      | UxSTA (UARTx Status and Control)                  | 154 |

| ECCP1AS (ECCP1 Auto-Shutdown Control)130         | Resets                                            |     |

| ECCP1DEL (ECCP1 Enhanced PWM Control) 131        | Brown-out Reset (BOR)                             | 63  |

| FBS (Boot Segment Configuration) 176             | Clock Source Selection                            | 61  |

| FGS (General Segment Configuration) 176          | Delay Times                                       | 62  |

| FICD (In-Circuit Debugger Configuration)181      | Device Times                                      | 62  |

| FOSC (Oscillator Configuration)                  | RCON Flag Operation                               |     |

| FOSCSEL (Oscillator Selection Configuration) 177 | SFR States                                        |     |

| FPOR (Reset Configuration)180                    | Revision History                                  |     |

| FWDT (Watchdog Timer Configuration) 179          | •                                                 |     |

| HLVDCON (High/Low-Voltage Detect Control) 174    | S                                                 |     |

| IEC0 (Interrupt Enable Control 0)                | Serial Peripheral Interface. See SPI Mode.        |     |

| IEC1 (Interrupt Enable Control 1)                | SFR Space                                         | 34  |

| IEC2 (Interrupt Enable Control 2)                | Software Stack                                    |     |

| IEC3 (Interrupt Enable Control 3) 79             | 55510 Oldon                                       |     |