Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 12                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 512 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 7x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                               |

| Supplier Device Package    | 14-TSSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl200t-i-st |

TABLE 1-5: PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  | Pin Number    | •                        |     |        |                                                                               |

|----------|----------------------------------|---------------|--------------------------|-----|--------|-------------------------------------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 14-Pin<br>PDIP/<br>TSSOP | I/O | Buffer | Description                                                                   |

| CVREF    | 17                               | 14            | 11                       | I   | ANA    | Comparator Voltage Reference Output                                           |

| CVREF+   | 2                                | 19            | 2                        | 1   | ANA    | Comparator Reference Positive Input Voltage                                   |

| CVREF-   | 3                                | 20            | 3                        | I   | ANA    | Comparator Reference Negative Input Voltage                                   |

| HLVDIN   | 15                               | 12            | 6                        | I   | ST     | High/Low-Voltage Detect Input                                                 |

| INT0     | 11                               | 8             | 12                       | - 1 | ST     | Interrupt 0 Input                                                             |

| INT1     | 17                               | 14            | 11                       | - 1 | ST     | Interrupt 1 Input                                                             |

| INT2     | 14                               | 11            | 10                       | I   | ST     | Interrupt 2 Input                                                             |

| MCLR     | 1                                | 18            | 1                        | _   | ST     | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |

| OSCI     | 7                                | 4             | 4                        | ı   | ANA    | Main Oscillator Input                                                         |

| OSCO     | 8                                | 5             | 5                        | 0   | ANA    | Main Oscillator Output                                                        |

| PGEC1    | 5                                | 2             | _                        | I/O | ST     | ICSP™ Clock 1                                                                 |

| PCED1    | 4                                | 1             | _                        | I/O | ST     | ICSP Data 1                                                                   |

| PGEC2    | 2                                | 19            | 2                        | I/O | ST     | ICSP Clock 2                                                                  |

| PGED2    | 3                                | 20            | 3                        | I/O | ST     | ICSP Data 2                                                                   |

| PGEC3    | 10                               | 7             | 7                        | I/O | ST     | ICSP Clock 3                                                                  |

| PGED3    | 9                                | 6             | 6                        | I/O | ST     | ICSP Data 3                                                                   |

| RA0      | 2                                | 19            | 2                        | I/O | ST     | PORTA Pins                                                                    |

| RA1      | 3                                | 20            | 3                        | I/O | ST     |                                                                               |

| RA2      | 7                                | 4             | 4                        | I/O | ST     |                                                                               |

| RA3      | 8                                | 5             | 5                        | I/O | ST     |                                                                               |

| RA4      | 10                               | 7             | 7                        | I/O | ST     |                                                                               |

| RA5      | 1                                | 18            | 1                        | I   | ST     |                                                                               |

| RA6      | 14                               | 11            | 10                       | I/O | ST     |                                                                               |

| RB0      | 4                                | 1             | _                        | I/O | ST     | PORTB Pins                                                                    |

| RB1      | 5                                | 2             | _                        | I/O | ST     |                                                                               |

| RB2      | 6                                | 3             | _                        | I/O | ST     |                                                                               |

| RB4      | 9                                | 6             | 6                        | I/O | ST     |                                                                               |

| RB7      | 11                               | 8             | _                        | I/O | ST     |                                                                               |

| RB8      | 12                               | 9             | 8                        | I/O | ST     |                                                                               |

| RB9      | 13                               | 10            | 9                        | I/O | ST     |                                                                               |

| RB12     | 15                               | 12            | _                        | I/O | ST     |                                                                               |

| RB13     | 16                               | 13            | _                        | I/O | ST     |                                                                               |

| RB14     | 17                               | 14            | 11                       | I/O | ST     |                                                                               |

| RB15     | 18                               | 15            | 12                       | I/O | ST     |                                                                               |

| REFO     | 18                               | 15            | 12                       | 0   |        | Reference Clock Output                                                        |

**Legend:** TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

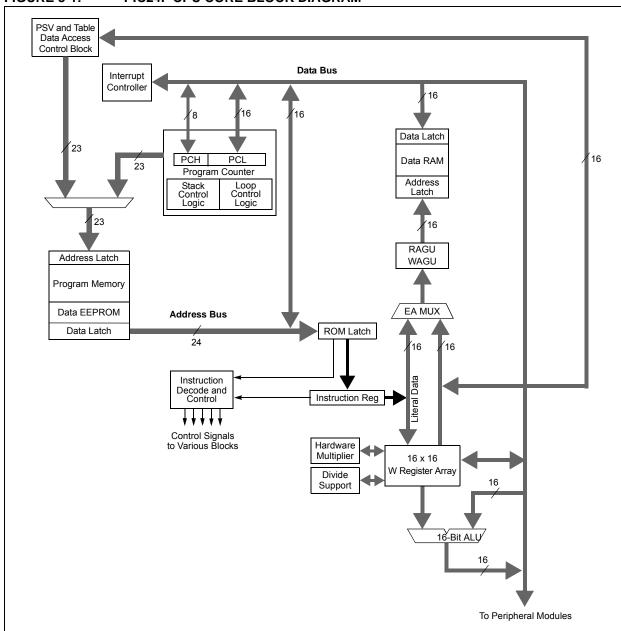

FIGURE 3-1: PIC24F CPU CORE BLOCK DIAGRAM

TABLE 3-1: CPU CORE REGISTERS

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | REPEAT Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

#### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|---------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY | _   | _   | _   | _     |

| bit 15     |       |       |         |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _     | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:           | HC = Hardware Clearable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit            | SO = Settable Only bit             |                    |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15 **WR:** Write Control bit (program or erase)

1 = Initiates a data EEPROM erase or write cycle (can be set but not cleared in software)

0 = Write cycle is complete (cleared automatically by hardware)

bit 14 WREN: Write Enable bit (erase or program)

1 = Enables an erase or program operation

0 = No operation allowed (device clears this bit on completion of the write/erase operation)

bit 13 WRERR: Flash Error Flag bit

1 = A write operation is prematurely terminated (any  $\overline{MCLR}$  or WDT Reset during programming operation)

0 = The write operation completed successfully

bit 12 **PGMONLY:** Program Only Enable bit

1 = Write operation is executed without erasing target address(es) first

0 = Automatic erase-before-write; write operations are preceded automatically by an erase of target address(es)

bit 11-7 **Unimplemented:** Read as '0'

bit 6 **ERASE**: Erase Operation Select bit

1 = Performs an erase operation when WR is set

0 = Performs a write operation when WR is set

bit 5-0 **NVMOP<5:0>:** Programming Operation Command Byte bits<sup>(1)</sup>

Erase Operations (when ERASE bit is '1'):

011010 = Erases 8 words

011001 = Erases 4 words

011000 = Erases 1 word

0100xx = Erases entire data EEPROM

Programming Operations (when ERASE bit is '0'):

001xxx = Writes 1 word

Note 1: These NVMOP configurations are unimplemented on PIC24F04KL10X and PIC24F08KL20X devices.

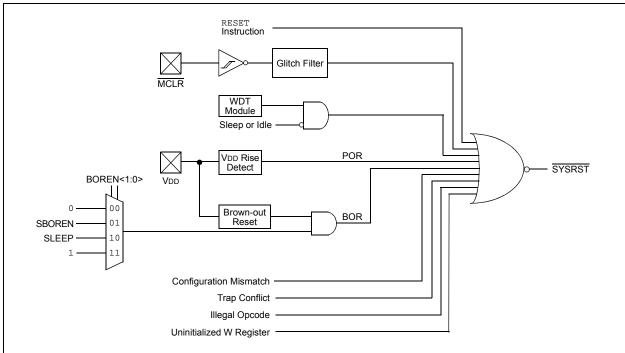

### 7.0 RESETS

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Resets, refer to the "dsPIC33/PIC24 Family Reference Manual", "Reset with Programmable Brown-out Reset" (DS39728).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

POR: Power-on Reset

MCLR: Pin Reset

SWR: RESET Instruction

WDTR: Watchdog Timer Reset

BOR: Brown-out ResetTRAPR: Trap Conflict ResetIOPUWR: Illegal Opcode Reset

UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on a Power-on Reset (POR) and unchanged by all other Resets.

Note:

Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A POR will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer (WDT) and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note:

The status bits in the RCON register should be cleared after they are read so that the next RCON register value, after a device Reset, will be meaningful.

FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

#### REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| R/W-0  | U-0 | R/W-0 | R/W-0  | R/W-0  | U-0 | U-0 | R/W-0 |

|--------|-----|-------|--------|--------|-----|-----|-------|

| NVMIF  |     | AD1IF | U1TXIF | U1RXIF |     |     | T3IF  |

| bit 15 |     |       |        |        |     |     | bit 8 |

| R/W-0 | R/W-0  | U-0 | U-0 | R/W-0 | R/W-0  | U-0 | R/W-0  |

|-------|--------|-----|-----|-------|--------|-----|--------|

| T2IF  | CCP2IF | _   | _   | T1IF  | CCP1IF | _   | INT0IF |

| bit 7 |        |     |     |       |        |     | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **NVMIF:** NVM Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 14 Unimplemented: Read as '0'

bit 13 AD1IF: A/D Conversion Complete Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 12 **U1TXIF:** UART1 Transmitter Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 11 **U1RXIF:** UART1 Receiver Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 10-9 **Unimplemented:** Read as '0'

bit 8 T3IF: Timer3 Interrupt Flag Status bit

1 = Interrupt request has occurred 0 = Interrupt request has not occurred

bit 7 T2IF: Timer2 Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 6 CCP2IF: Capture/Compare/PWM2 Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 5-4 **Unimplemented:** Read as '0'

bit 3 T1IF: Timer1 Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 2 CCP1IF: Capture/Compare/PWM1 Interrupt Flag Status bit (ECCP1 on PIC24FXXKL40X devices)

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 1 **Unimplemented:** Read as '0'

bit 0 INT0IF: External Interrupt 0 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

### REGISTER 8-17: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

|--------|-------|-------|-------|-----|---------|---------|---------|

| _      | T1IP2 | T1IP1 | T1IP0 |     | CCP1IP2 | CCP1IP1 | CCP1IP0 |

| bit 15 |       |       |       |     |         |         | bit 8   |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|-----|-----|-----|-----|---------|---------|---------|

| _     | _   | _   | _   | _   | INT0IP2 | INT0IP1 | INT0IP0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 T1IP<2:0>: Timer1 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 CCP1IP<2:0>: Capture/Compare/PWM1 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

-

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 **INT0IP<2:0>:** External Interrupt 0 Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

### 8.4 Interrupt Setup Procedures

#### 8.4.1 INITIALIZATION

To configure an interrupt source:

- Set the NSTDIS Control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and the type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits, for all enabled interrupt sources, may be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized, such that all user interrupt sources are assigned to Priority Level 4.

- Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

### 8.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (i.e., C or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 8.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

### 8.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, OEh, with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period. Level 7 interrupt sources are not disabled by the DISI instruction.

### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

|-------|-----|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| _     | _   | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup> | TUN3 <sup>(1)</sup> | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |

| bit 7 |     |                     |                     |                     |                     |                     | bit 0               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits<sup>(1)</sup>

011111 = Maximum frequency deviation

011110

•

•

000001

000000 = Center frequency, oscillator is running at factory calibrated frequency

111111

•

•

• 100001

100000 = Minimum frequency deviation

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

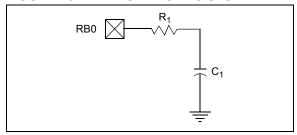

### 10.3 Ultra Low-Power Wake-up

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption. This feature provides a low-power technique for periodically waking up the device from Sleep mode.

To use this feature:

- Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- Stop charging the capacitor by configuring RB0 as an input.

- Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0. When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 10-2 for initializing the ULPWU module.

A series resistor, between RB0 and the external capacitor, provides overcurrent protection for the RB0/AN2/ULPWU pin and enables software calibration of the time-out (see Figure 10-1).

#### FIGURE 10-1: SERIES RESISTOR

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

#### **EXAMPLE 10-2: ULTRA LOW-POWER WAKE-UP INITIALIZATION**

```

// 1. Charge the capacitor on RBO

TRISBbits.TRISB0 = 0;

LATBbits.LATB0 = 1;

for(i = 0; i < 10000; i++) Nop();

//2. Stop Charging the capacitor on RBO

TRISBbits.TRISB0 = 1;

//**********************************

//3. Enable ULPWU Interrupt

IFS5bits.ULPWUIF = 0;

IEC5bits.ULPWUIE = 1;

TPC20bits.UIJPWUITP = 0x7;

//4. Enable the Ultra Low Power Wakeup module and allow capacitor discharge

ULPWCONbits.ULPEN = 1;

ULPWCONbits.ULPSINK = 1;

/****************************

//5. Enter Sleep Mode

*******************

//********

Sleep();

//for Sleep, execution will resume here

```

### REGISTER 14-2: T3GCON: TIMER3 GATE CONTROL REGISTER(1)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0            | R-x    | R/W-0  | R/W-0  |

|--------|--------|-------|--------|------------------|--------|--------|--------|

| TMR3GE | T3GPOL | T3GTM | T3GSPM | T3GGO/<br>T3DONE | T3GVAL | T3GSS1 | T3GSS0 |

| bit 7  |        |       |        |                  |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7 TMR3GE: Timer3 Gate Enable bit

$\frac{\text{If TMR3ON} = 0:}{\text{This bit is ignored.}}$   $\frac{\text{If TMR3ON} = 1:}{\text{If TMR3ON} = 1:}$

1 = Timer counting is controlled by the Timer3 gate function0 = Timer counts regardless of the Timer3 gate function

bit 6 T3GPOL: Timer3 Gate Polarity bit

1 = Timer gate is active-high (Timer3 counts when the gate is high) 0 = Timer gate is active-low (Timer3 counts when the gate is low)

bit 5 T3GTM: Timer3 Gate Toggle Mode bit

1 = Timer Gate Toggle mode is enabled.

0 = Timer Gate Toggle mode is disabled and toggle flip-flop is cleared

Timer3 gate flip-flop toggles on every rising edge.

bit 4 T3GSPM: Timer3 Gate Single Pulse Mode bit

1 = Timer Gate Single Pulse mode is enabled and is controlling the Timer3 gate

0 = Timer Gate Single Pulse mode is disabled

bit 3 T3GGO/T3DONE: Timer3 Gate Single Pulse Acquisition Status bit

1 = Timer gate single pulse acquisition is ready, waiting for an edge

0 = Timer gate single pulse acquisition has completed or has not been started

This bit is automatically cleared when T3GSPM is cleared.

bit 2 T3GVAL: Timer3 Gate Current State bit

Indicates the current state of the timer gate that could be provided to the TMR3 register; unaffected by

the state of TMR3GE.

bit 1-0 T3GSS<1:0>: Timer3 Gate Source Select bits

11 = Comparator 2 output

10 = Comparator 1 output

01 = TMR2 to match PR2 output

00 = T3G input pin

Note 1: Initializing T3GCON prior to T3CON is recommended.

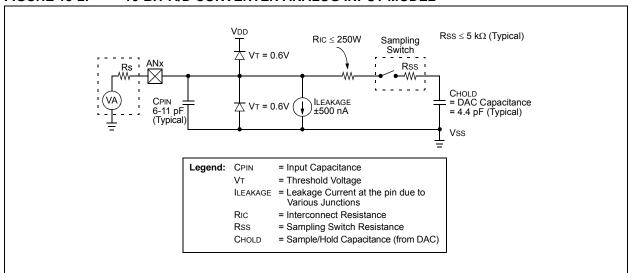

# 19.0 10-BIT HIGH-SPEED A/D CONVERTER

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 10-Bit High-Speed A/D Converter, refer to the "dsPIC33/PIC24 Family Reference Manual", "10-Bit A/D Converter" (DS39705).

The 10-bit A/D Converter has the following key features:

- · Successive Approximation (SAR) conversion

- · Conversion speeds of up to 500 ksps

- · Up to 12 analog input pins

- · External voltage reference input pins

- · Internal band gap reference input

- · Automatic Channel Scan mode

- · Selectable conversion trigger source

- · Two-word conversion result buffer

- · Selectable Buffer Fill modes

- · Four result alignment options

- · Operation during CPU Sleep and Idle modes

Depending on the particular device, PIC24F16KL402 family devices implement up to 12 analog input pins, designated AN0 through AN4 and AN9 through AN15. In addition, there are two analog input pins for external voltage reference connections (VREF+ and VREF-). These voltage reference inputs may be shared with other analog input pins.

A block diagram of the A/D Converter is displayed in Figure 19-1.

To perform an A/D conversion:

- 1. Configure the A/D module:

- a) Configure port pins as analog inputs and/ or select band gap reference inputs (ANSA<3:0>, ANSB<15:12,4:0> and ANCFG<0>).

- Select the voltage reference source to match the expected range on analog inputs (AD1CON2<15:13>).

- Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- e) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select interrupt rate (AD1CON2<5:2>).

- g) Turn on A/D module (AD1CON1<15>).

- 2. Configure A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select A/D interrupt priority.

#### REGISTER 19-1: AD1CON1: A/D CONTROL REGISTER 1

| R/W-0               | U-0 | R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|---------------------|-----|--------|-----|-----|-----|-------|-------|

| ADON <sup>(1)</sup> | _   | ADSIDL | _   | _   | _   | FORM1 | FORM0 |

| bit 15              |     |        |     |     |     |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0, HSC | R-0, HSC |

|-------|-------|-------|-----|-----|-------|------------|----------|

| SSRC2 | SSRC1 | SSRC0 | _   | _   | ASAM  | SAMP       | DONE     |

| bit 7 |       |       |     |     |       |            | bit 0    |

| Legend:           | HSC = Hardware Settable/Clearable bit |                            |                    |  |  |

|-------------------|---------------------------------------|----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, rea | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared       | x = Bit is unknown |  |  |

bit 15 **ADON:** A/D Operating Mode bit<sup>(1)</sup>

1 = A/D Converter module is operating

0 = A/D Converter is off

bit 14 Unimplemented: Read as '0'

bit 13 ADSIDL: A/D Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-10 Unimplemented: Read as '0'

bit 9-8 **FORM<1:0>:** Data Output Format bits

11 = Signed fractional (sddd dddd dd00 0000)

10 = Fractional (dddd dddd dd00 0000)

01 = Signed integer (ssss sssd dddd dddd)

00 = Integer (0000 00dd dddd dddd)

bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

111 = Internal counter ends sampling and starts conversion (auto-convert)

110 = Reserved

101 = Reserved

100 = Reserved

011 = Reserved

010 = Timer1 compare ends sampling and starts conversion

001 = Active transition on INT0 pin ends sampling and starts conversion

000 = Clearing the SAMP bit ends sampling and starts conversion

bit 4-3 **Unimplemented:** Read as '0'

bit 2 ASAM: A/D Sample Auto-Start bit

1 = Sampling begins immediately after the last conversion completes; SAMP bit is auto-set

0 = Sampling begins when the SAMP bit is set

bit 1 SAMP: A/D Sample Enable bit

1 = A/D Sample-and-Hold amplifier is sampling input

0 = A/D Sample-and-Hold amplifier is holding

bit 0 **DONE:** A/D Conversion Status bit

1 = A/D conversion is done

0 = A/D conversion is not done

**Note 1:** Values of ADC1BUFx registers will not retain their values once the ADON bit is cleared. Read out the conversion values from the buffer before disabling the module.

### **EQUATION 19-1:** A/D CONVERSION CLOCK PERIOD<sup>(1)</sup>

$$ADCS = \frac{TAD}{TCY} - 1$$

$$TAD = TCY \cdot (ADCS + 1)$$

Note 1: Based on Tcy = 2 \* Tosc; Doze mode and PLL are disabled.

### FIGURE 19-2: 10-BIT A/D CONVERTER ANALOG INPUT MODEL

**Note:** CPIN value depends on device package and is not tested. Effect of CPIN is negligible if Rs  $\leq$  5 k $\Omega$ .

### TABLE 25-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|-----------------------------------------|---------------|----------------|--------------------------|

| PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode              | 1             | 1              | WDTO, Sleep              |

| RCALL                | RCALL  | Expr            | Relative Call                           | 1             | 2              | None                     |

|                      | RCALL  | Wn              | Computed Call                           | 1             | 2              | None                     |

| REPEAT               | REPEAT | #lit14          | Repeat Next Instruction lit14 + 1 times | 1             | 1              | None                     |

|                      | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 times  | 1             | 1              | None                     |

| RESET                | RESET  |                 | Software Device Reset                   | 1             | 1              | None                     |

| RETFIE               | RETFIE |                 | Return from Interrupt                   | 1             | 3 (2)          | None                     |

| RETLW                | RETLW  | #lit10,Wn       | Return with Literal in Wn               | 1             | 3 (2)          | None                     |

| RETURN               | RETURN |                 | Return from Subroutine                  | 1             | 3 (2)          | None                     |

| RLC                  | RLC    | f               | f = Rotate Left through Carry f         | 1             | 1              | C, N, Z                  |

|                      | RLC    | f,WREG          | WREG = Rotate Left through Carry f      | 1             | 1              | C, N, Z                  |

|                      | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws       | 1             | 1              | C, N, Z                  |

| RLNC                 | RLNC   | f               | f = Rotate Left (No Carry) f            | 1             | 1              | N, Z                     |

|                      | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f         | 1             | 1              | N, Z                     |

|                      | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws          | 1             | 1              | N, Z                     |

| RRC                  | RRC    | f               | f = Rotate Right through Carry f        | 1             | 1              | C, N, Z                  |

|                      | RRC    | f,WREG          | WREG = Rotate Right through Carry f     | 1             | 1              | C, N, Z                  |

|                      | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws      | 1             | 1              | C, N, Z                  |

| RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f           | 1             | 1              | N, Z                     |

|                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f        | 1             | 1              | N, Z                     |

|                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws         | 1             | 1              | N, Z                     |

| SE                   | SE     | Ws, Wnd         | Wnd = Sign-Extended Ws                  | 1             | 1              | C, N, Z                  |

| SETM                 | SETM   | f               | f = FFFFh                               | 1             | 1              | None                     |

|                      | SETM   | WREG            | WREG = FFFFh                            | 1             | 1              | None                     |

|                      | SETM   | Ws              | Ws = FFFFh                              | 1             | 1              | None                     |

| SL                   | SL     | f               | f = Left Shift f                        | 1             | 1              | C, N, OV, Z              |

|                      | SL     | f,WREG          | WREG = Left Shift f                     | 1             | 1              | C, N, OV, Z              |

|                      | SL     | Ws,Wd           | Wd = Left Shift Ws                      | 1             | 1              | C, N, OV, Z              |

|                      | SL     | Wb, Wns, Wnd    | Wnd = Left Shift Wb by Wns              | 1             | 1              | N, Z                     |

|                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5             | 1             | 1              | N, Z                     |

| SUB                  | SUB    | f               | f = f – WREG                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | f,WREG          | WREG = f – WREG                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | #lit10,Wn       | Wn = Wn – lit10                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,#lit5,Wd     | Wd = Wb – lit5                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBB                 | SUBB   | f               | $f = f - WREG - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | f,WREG          | WREG = $f - WREG - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      |        |                 | $Wn = Wn - lit10 - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | #lit10,Wn       |                                         |               |                |                          |

|                      | SUBB   | Wb,Ws,Wd        | Wd = Wb - Ws - (C)                      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,#lit5,Wd     | Wd = Wb – lit5 – (C)                    | 1             | 1              | C, DC, N, OV, Z          |

| SUBR                 | SUBR   | f               | f = WREG – f                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | f,WREG          | WREG = WREG – f                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,Ws,Wd        | Wd = Ws – Wb                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | f,WREG          | WREG = WREG – f – $(\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | Wb,Ws,Wd        | $Wd = Ws - Wb - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$       | 1             | 1              | C, DC, N, OV, Z          |

| SWAP                 | SWAP.b | Wn              | Wn = Nibble Swap Wn                     | 1             | 1              | None                     |

|                      | SWAP   | Wn              | Wn = Byte Swap Wn                       | 1             | 1              | None                     |

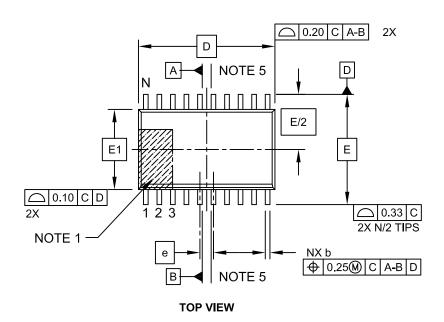

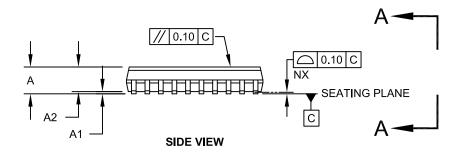

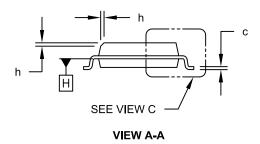

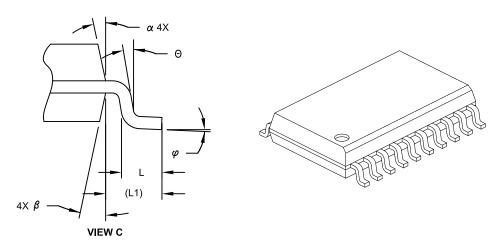

### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2

### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |          |           | MILLIMETERS |  |  |  |

|--------------------------|-------|----------|-----------|-------------|--|--|--|

| Dimension Limits         |       | MIN      | NOM       | MAX         |  |  |  |

| Number of Pins           | N     |          | 20        |             |  |  |  |

| Pitch                    | е     |          | 1.27 BSC  |             |  |  |  |

| Overall Height           | Α     | -        | -         | 2.65        |  |  |  |

| Molded Package Thickness | A2    | 2.05     | -         | -           |  |  |  |

| Standoff §               | A1    | 0.10     | -         | 0.30        |  |  |  |

| Overall Width            | E     | •        | 10.30 BSC |             |  |  |  |

| Molded Package Width     | E1    | 7.50 BSC |           |             |  |  |  |

| Overall Length           | D     |          | 12.80 BSC |             |  |  |  |

| Chamfer (Optional)       | h     | 0.25     | -         | 0.75        |  |  |  |

| Foot Length              | L     | 0.40     | ı         | 1.27        |  |  |  |

| Footprint                | L1    |          | 1.40 REF  |             |  |  |  |

| Lead Angle               | Θ     | 0°       | -         | -           |  |  |  |

| Foot Angle               | φ     | 0°       | -         | 8°          |  |  |  |

| Lead Thickness           | С     | 0.20     | =         | 0.33        |  |  |  |

| Lead Width               | b     | 0.31     | -         | 0.51        |  |  |  |

| Mold Draft Angle Top     | α     | 5°       | -         | 15°         |  |  |  |

| Mold Draft Angle Bottom  | β     | 5°       | =         | 15°         |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2

NOTES:

### **INDEX**

| A                                                          |     | C                                              |     |

|------------------------------------------------------------|-----|------------------------------------------------|-----|

| A/D                                                        |     | C Compilers                                    |     |

| 10-Bit High-Speed A/D Converter                            | 157 | MPLAB XC Compilers                             | 188 |

| Conversion Timing Requirements                             |     | Capture/Compare/PWM (CCP)                      |     |

| Module Specifications                                      |     | CCP/ECCP \ \ \ \ /                             |     |

| A/D Converter                                              |     | CCP I/O Pins                                   | 125 |

| Analog Input Model                                         | 164 | Timer Selection                                | 125 |

| Transfer Function                                          |     | Code Examples                                  |     |

| AC Characteristics                                         |     | Data EEPROM Bulk Erase                         | 57  |

| A/D Module                                                 | 223 | Data EEPROM Unlock Sequence                    | 53  |

| Capacitive Loading Requirements on                         |     | Erasing a Program Memory Row,                  |     |

| Output Pins                                                | 209 | Assembly Language                              | 50  |

| Internal RC Oscillator Accuracy                            |     | Erasing a Program Memory Row, C Language       |     |

| Internal RC Oscillator Specifications                      | 211 | I/O Port Write/Read (Assembly Language)        | 114 |

| Load Conditions and Requirements                           | 209 | I/O Port Write/Read (C Language)               |     |

| Temperature and Voltage Specifications                     |     | Initiating a Programming Sequence,             |     |

| Assembler                                                  |     | Assembly Language                              | 52  |

| MPASM Assembler                                            | 188 | Initiating a Programming Sequence, C Language. | 52  |

| B                                                          |     | Loading the Write Buffers, Assembly Language   | 51  |

| В                                                          |     | Loading the Write Buffers, C Language          | 52  |

| Block Diagrams                                             |     | PWRSAV Instruction Syntax                      | 105 |

| 10-Bit High-Speed A/D Converter                            | 158 | Reading Data EEPROM Using the                  |     |

| 16-Bit Timer1                                              | 115 | TBLRD Command                                  | 58  |

| Accessing Program Memory with                              |     | Sequence for Clock Switching                   | 102 |

| Table Instructions                                         |     | Single-Word Erase                              | 56  |

| CALL Stack Frame                                           |     | Single-Word Write to Data EEPROM               | 57  |

| Capture Mode Operation                                     |     | Ultra Low-Power Wake-up Initialization         | 107 |

| Comparator Module                                          |     | Code Protection                                | 185 |

| Comparator Voltage Reference Module                        |     | Comparator                                     | 167 |

| Compare Mode Operation                                     |     | Comparator Voltage Reference                   | 171 |

| CPU Programmer's Model                                     | 27  | Configuring                                    |     |

| Data Access From Program Space                             |     | Configuration Bits                             |     |

| Address Generation                                         |     | Core Features                                  | 9   |

| Data EEPROM Addressing with TBLPAG and                     |     | CPU                                            |     |

| NVM Registers                                              |     | ALU                                            |     |

| Enhanced PWM Mode                                          |     | Control Registers                              |     |

| High/Low-Voltage Detect (HLVD) Module                      |     | Core Registers                                 |     |

| Individual Comparator Configurations                       |     | Programmer's Model                             |     |

| MCLR Pin Connections Example                               |     | Customer Change Notification Service           | 257 |

| MSSPx Module (I <sup>2</sup> C Master Mode)                |     | Customer Notification Service                  |     |

| MSSPx Module (I <sup>2</sup> C Mode)                       |     | Customer Support                               | 257 |

| MSSPx Module (SPI Mode)                                    |     | D                                              |     |

| PIC24F CPU Core                                            |     | _                                              | EO  |

| PIC24F16KL402 Family (General)                             |     | Data EEPROM Memory                             |     |

| PSV Operation (Simplified)                                 |     | Erasing                                        | 50  |

| PWM Operation (Simplified) Recommended Minimum Connections |     | Nonvolatile Memory Registers  NVMCON           | 52  |

|                                                            |     | NVMKEY                                         |     |

| Reset SystemSerial Resistor                                |     | NVMADR(U)                                      |     |

| Shared I/O Port Structure                                  |     | Operations                                     |     |

| Simplified UARTx                                           |     | Programming                                    | 55  |

| SPI Master/Slave Connection                                |     | Bulk Erase                                     | 57  |

| Suggested Placement of Oscillator Circuit                  |     | Reading Data EEPROM                            |     |

|                                                            |     | Single-Word Write                              |     |

| System ClockTable Register Addressing                      |     | Data Memory                                    | 57  |

| Timer2                                                     |     | Address Space                                  | 33  |

| Timer3                                                     |     | Memory Map                                     |     |

| Timer4                                                     |     | Near Data Space                                |     |

| Watchdog Timer (WDT)                                       |     | Organization                                   |     |

| **************************************                     | 107 | SFR Space                                      |     |

|                                                            |     | Software Stack                                 |     |

|                                                            |     | Space Width                                    |     |

|                                                            |     | · · · · · · · · · · · · · · · · ·              | 55  |

| Program Memory                                   | IEC4 (Interrupt Enable Control 4)                 | 80  |

|--------------------------------------------------|---------------------------------------------------|-----|

| Address Space31                                  | IEC5 (Interrupt Enable Control 5)                 | 80  |

| Data EEPROM32                                    | IFS0 (Interrupt Flag Status 0)                    | 73  |

| Device Configuration Words32                     | IFS1 (Interrupt Flag Status 1)                    | 74  |

| Hard Memory Vectors32                            | IFS2 (Interrupt Flag Status 2)                    | 75  |

| Organization32                                   | IFS3 (Interrupt Flag Status 3)                    | 75  |

| Program Space                                    | IFS4 (Interrupt Flag Status 4)                    | 76  |

| Memory Map31                                     | IFS5 (Interrupt Flag Status 5)                    | 76  |

| Program Verification                             | INTCON 2 (Interrupt Control 2)                    |     |

| PWM (CCP Module)                                 | INTCON1 (Interrupt Control 1)                     |     |

| TMR4 to PR4 Match123                             | INTTREG (Interrupt Control and Status)            |     |

|                                                  | IPC0 (Interrupt Priority Control 0)               |     |

| R                                                | IPC1 (Interrupt Priority Control 1)               |     |

| Register Maps                                    | IPC12 (Interrupt Priority Control 12)             |     |

| A/D Converter41                                  | IPC16 (Interrupt Priority Control 16)             |     |

| Analog Select41                                  | IPC18 (Interrupt Priority Control 18)             |     |

| CCP/ECCP                                         | IPC2 (Interrupt Priority Control 2)               |     |

| Comparator                                       | IPC20 (Interrupt Priority Control 20)             |     |

| CPU Core                                         | ` ' '                                             |     |

| ICN                                              | IPC3 (Interrupt Priority Control 3)               |     |

| Interrupt Controller                             | IPC4 (Interrupt Priority Control 4)               |     |

|                                                  | IPC5 (Interrupt Priority Control 5)               |     |

| MSSP                                             | IPC6 (Interrupt Priority Control 6)               |     |

| NVM                                              | IPC7 (Interrupt Priority Control 7)               |     |

| Pad Configuration                                | IPC9 (Interrupt Priority Control 9)               |     |

| PMD42                                            | NVMCON (Flash Memory Control)                     |     |

| PORTA40                                          | NVMCON (Nonvolatile Memory Control)               |     |

| PORTB40                                          | OSCCON (Oscillator Control)                       |     |

| System, Clock Control42                          | OSCTUN (FRC Oscillator Tune)                      | 100 |

| Timer38                                          | PADCFG1 (Pad Configuration Control)               | 147 |

| UART39                                           | PSTR1CON (ECCP1 Pulse Steering Control)           |     |

| Ultra Low-Power Wake-up42                        | RCON (Reset Control)                              | 60  |

| Registers                                        | REFOCON (Reference Oscillator Control)            | 103 |

| AD1CHS (A/D Input Select)162                     | SR (ALU STATUS)                                   |     |

| AD1CON1 (A/D Control 1) 159                      | SSPxADD (MSSPx Slave Address/Baud                 | •   |

| AD1CON2 (A/D Control 2) 160                      | Rate Generator)                                   | 146 |

| AD1CON3 (A/D Control 3) 161                      | SSPxCON1 (MSSPx Control 1, I <sup>2</sup> C Mode) |     |

| AD1CSSL (A/D Input Scan Select)163               | SSPxCON1 (MSSPx Control 1, SPI Mode)              |     |

| ANCFG (Analog Input Configuration)               | SSPxCON2 (MSSPx Control 2, I <sup>2</sup> C Mode) |     |

| ANSA (PORTA Analog Selection)                    | SSPxCON3 (MSSPx Control 3, I <sup>2</sup> C Mode) |     |

| ANSB (PORTB Analog Selection)113                 | SSPxCON3 (MSSPx Control 3, SPI Mode)              |     |

| CCP1CON (ECCP1 Control, Enhanced CCP)129         | SSPxMSK (I <sup>2</sup> C Slave Address Mask)     |     |

| CCPTMRS0 (CCP Timer Select Control 0)            | SSPxSTAT (MSSPx Status, I <sup>2</sup> C Mode)    |     |

| CCPxCON (CCPx Control, Standard CCP)128          | SSPxSTAT (MSSPx Status, SPI Mode)                 |     |

| CLKDIV (Clock Divider)99                         | T1CON (Timer1 Control)                            |     |

| CMSTAT (Comparator Status)170                    | · · · · · · · · · · · · · · · · · · ·             |     |

| CMxCON (Comparator x Control)                    | T2CON (Timer2 Control)                            |     |

|                                                  | T3CON (Timer3 Control)                            |     |

| CORCON (CPU Control)                             | T3GCON (Timer3 Gate Control)                      |     |

| CVRCON (Comparator Voltage                       | T4CON (Timer4 Control)                            |     |

| Reference Control)                               | ULPWCON (ULPWU Control)                           |     |

| DEVID (Device ID)                                | UxMODE (UARTx Mode)                               |     |

| DEVREV (Device Revision)183                      | UxSTA (UARTx Status and Control)                  | 154 |

| ECCP1AS (ECCP1 Auto-Shutdown Control)130         | Resets                                            |     |

| ECCP1DEL (ECCP1 Enhanced PWM Control) 131        | Brown-out Reset (BOR)                             | 63  |

| FBS (Boot Segment Configuration) 176             | Clock Source Selection                            | 61  |

| FGS (General Segment Configuration) 176          | Delay Times                                       | 62  |

| FICD (In-Circuit Debugger Configuration)181      | Device Times                                      | 62  |

| FOSC (Oscillator Configuration)                  | RCON Flag Operation                               |     |

| FOSCSEL (Oscillator Selection Configuration) 177 | SFR States                                        |     |

| FPOR (Reset Configuration)180                    | Revision History                                  |     |

| FWDT (Watchdog Timer Configuration) 179          | •                                                 |     |

| HLVDCON (High/Low-Voltage Detect Control) 174    | S                                                 |     |

| IEC0 (Interrupt Enable Control 0)                | Serial Peripheral Interface. See SPI Mode.        |     |

| IEC1 (Interrupt Enable Control 1)                | SFR Space                                         | 34  |

| IEC2 (Interrupt Enable Control 2)                | Software Stack                                    |     |

| IEC3 (Interrupt Enable Control 3) 79             | 55510 Oldon                                       |     |

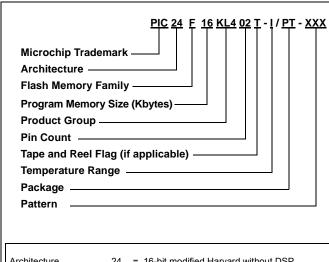

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

#### Architecture 24 = 16-bit modified Harvard without DSP

Flash Memory Family F = Standard voltage range Flash program memory

KL4 = General purpose microcontrollers KL3 KL2 Product Group

Pin Count

Package

Temperature Range = -40°C to +85°C (Industrial) E =  $-40^{\circ}$ C to  $+125^{\circ}$ C (Extended)

= SPDIP = SOIC

SP SO ST = TSSC ML, MQ = QFN

Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise) Pattern

ES = Engineering Sample

### **Examples:**

- PIC24F16KL402-I/ML: General Purpose, 16-Kbyte Program Memory, 28-Pin, Industrial Temperature, QFN Package

- PIC24F04KL101T-I/SS: General Purpose, 4-Kbyte Program Memory, 20-Pin, Industrial Temperature, SSOP Package, Tape-and-Reel