Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 17                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 20-VQFN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl201-e-mq |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

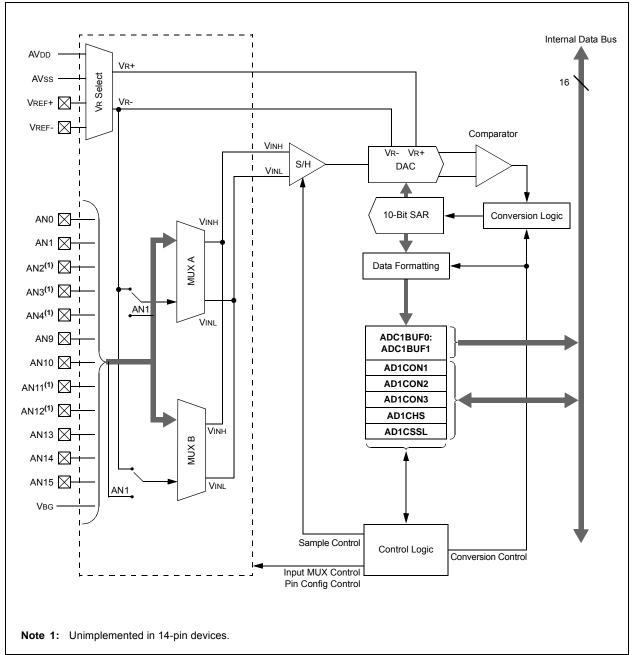

## **Analog Features:**

- 10-Bit, up to 12-Channel Analog-to-Digital (A/D) Converter:

- 500 ksps conversion rate

- Conversion available during Sleep and Idle

- Dual Rail-to-Rail Analog Comparators with Programmable Input/Output Configuration

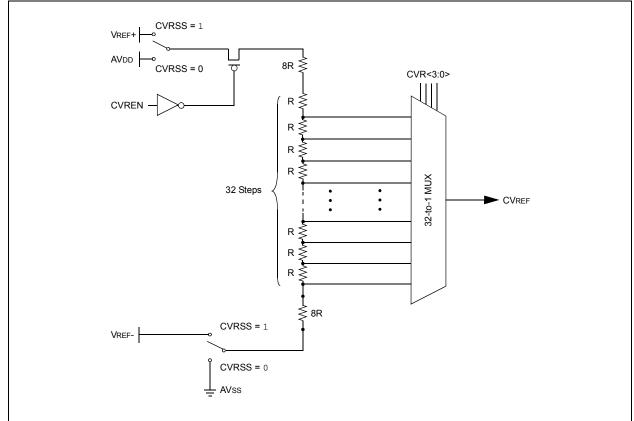

- On-Chip Voltage Reference

## **Special Microcontroller Features:**

- Operating Voltage Range of 1.8V to 3.6V

- 10,000 Erase/Write Cycle Endurance Flash Program Memory, Typical

- 100,000 Erase/Write Cycle Endurance Data EEPROM, Typical

- Flash and Data EEPROM Data Retention: 40 Years Minimum

- Self-Programmable under Software Control

- Programmable Reference Clock Output

- Fail-Safe Clock Monitor (FSCM) Operation:

- Detects clock failure and switches to on-chip, Low-Power RC (LPRC) oscillator

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT):

- Uses its own Low-Power RC oscillator

- Windowed operating modes

- Programmable period of 2 ms to 131s

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and In-Circuit Emulation (ICE) via 2 Pins

- Programmable High/Low-Voltage Detect (HLVD)

- Programmable Brown-out Reset (BOR):

- Configurable for software controlled operation and shutdown in Sleep mode

- Selectable trip points (1.8V, 2.7V and 3.0V)

- Low-power 2.0V POR re-arm

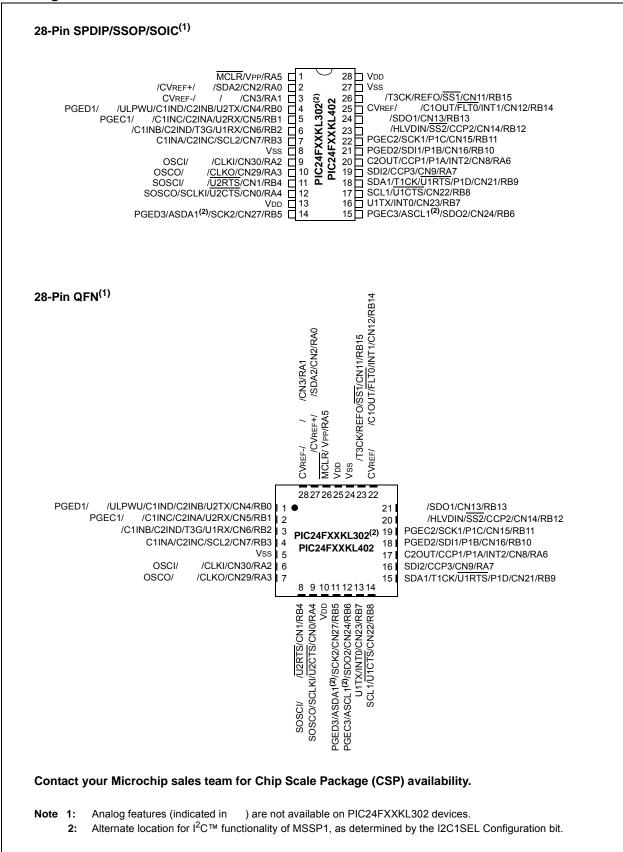

### Pin Diagrams: PIC24FXXKL302/402

## 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction                                        | Description                                                 |  |  |  |  |

|----------------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| ASR                                                | Arithmetic shift right source register by one or more bits. |  |  |  |  |

| SL Shift left source register by one or more bits. |                                                             |  |  |  |  |

| LSR                                                | Logical shift right source register by one or more bits.    |  |  |  |  |

### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address, as shown in Figure 4-2.

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

### 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 00000h and 000200h for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h, with the actual address for the start of code at 000002h.

PIC24F devices also have two Interrupt Vector Tables (IVT), located from 000004h to 0000FFh and 000104h to 0001FFh. These vector tables allow each of the many device interrupt sources to be handled by separate ISRs. A more detailed discussion of the Interrupt Vector Tables is provided in **Section 8.1** "Interrupt Vector Table (IVT)".

## 4.1.3 DATA EEPROM

In the PIC24F16KL402 family, the data EEPROM is mapped to the top of the user program memory space, starting at address, 7FFE00, and expanding up to address, 7FFFF.

The data EEPROM is organized as 16-bit wide memory and 256 words deep. This memory is accessed using Table Read and Table Write operations, similar to the user code memory.

### 4.1.4 DEVICE CONFIGURATION WORDS

Table 4-1 provides the addresses of the device Configuration Words for the PIC24F16KL402 family. Their location in the memory map is shown in Figure 4-1.

For more information on device Configuration Words, see **Section 23.0 "Special Features"**.

### TABLE 4-1: DEVICE CONFIGURATION WORDS FOR PIC24F16KL402 FAMILY DEVICES

| Configuration Words | Configuration Word<br>Addresses |

|---------------------|---------------------------------|

| FBS                 | F80000                          |

| FGS                 | F80004                          |

| FOSCSEL             | F80006                          |

| FOSC                | F80008                          |

| FWDT                | F8000A                          |

| FPOR                | F8000C                          |

| FICD                | F8000E                          |

### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| msw<br>Address | most significant wo                               | ord I   | east significant wo | rd | PC Address<br>(Isw Address) |

|----------------|---------------------------------------------------|---------|---------------------|----|-----------------------------|

|                | 23                                                | 16      | 8                   | 0  |                             |

| 000001h        | 0000000                                           |         |                     |    | 000000h                     |

| 000003h        | 0000000                                           |         |                     |    | 000002h                     |

| 000005h        | 0000000                                           |         |                     |    | 000004h                     |

| 000007h        | 0000000                                           |         |                     |    | 000006h                     |

|                |                                                   |         | $\sim$              |    |                             |

|                | Program Memory<br>'Phantom' Byte<br>(read as '0') | Instruc | tion Width          |    |                             |

### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|------------------------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY <sup>(4)</sup> | —   | —   | —   | —     |

| bit 15     |       |       |                        |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:              | SO = Settable Only bit | HC = Hardware Clearable bit |                  |  |

|----------------------|------------------------|-----------------------------|------------------|--|

| -n = Value at POR    | '1' = Bit is set       | R = Readable bit            | W = Writable bit |  |

| '0' = Bit is cleared | x = Bit is unknown     | U = Unimplemented bit,      | read as '0'      |  |

| bit 15   | WR: Write Control bit                                                                                                                                                                                                                       |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = Initiates a Flash memory program or erase operation; the operation is self-timed and the bit is cleared by hardware once the operation is complete</li> <li>0 = Program or erase operation is complete and inactive</li> </ul> |

|          |                                                                                                                                                                                                                                             |

| bit 14   | WREN: Write Enable bit                                                                                                                                                                                                                      |

|          | 1 = Enables Flash program/erase operations                                                                                                                                                                                                  |

|          | 0 = Inhibits Flash program/erase operations                                                                                                                                                                                                 |

| bit 13   | WRERR: Write Sequence Error Flag bit                                                                                                                                                                                                        |

|          | <ul> <li>1 = An improper program or erase sequence attempt, or termination, has occurred (bit is set automatically<br/>on any set attempt of the WR bit)</li> </ul>                                                                         |

|          | 0 = The program or erase operation completed normally                                                                                                                                                                                       |

| bit 12   | PGMONLY: Program Only Enable bit <sup>(4)</sup>                                                                                                                                                                                             |

| bit 11-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                  |

| bit 6    | ERASE: Erase/Program Enable bit                                                                                                                                                                                                             |

|          | 1 = Performs the erase operation specified by NVMOP<5:0> on the next WR command                                                                                                                                                             |

|          | 0 = Performs the program operation specified by NVMOP<5:0> on the next WR command                                                                                                                                                           |

| bit 5-0  | NVMOP<5:0>: Programming Operation Command Byte bits <sup>(1)</sup>                                                                                                                                                                          |

|          | Erase Operations (when ERASE bit is '1'):                                                                                                                                                                                                   |

|          | 1010xx = Erases entire boot block (including code-protected boot block) <sup>(2)</sup>                                                                                                                                                      |

|          | 1001xx = Erases entire memory (including boot block, configuration block, general block) <sup>(2)</sup>                                                                                                                                     |

|          | 011010 = Erases 4 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                                       |

|          | 011001 = Erases 2 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                                       |

|          | 011000 = Erases 1 row of Flash memory <sup>(3)</sup><br>0101xx = Erases entire configuration block (except code protection bits)                                                                                                            |

|          | 0101xx = Erases entire comiguration block (except code protection bits)<br>$0100xx = \text{Erases entire data EEPROM^{(4)}}$                                                                                                                |

|          | 0011xx = Erases entire general memory block programming operations                                                                                                                                                                          |

|          | 0001xx = Writes 1 row of Flash memory (when ERASE bit is '0') <sup>(3)</sup>                                                                                                                                                                |

|          |                                                                                                                                                                                                                                             |

|          | All other combinations of the NVMOP<5:0> bits are no operation.                                                                                                                                                                             |

| 2:       | Available in ICSP™ mode only. Refer to the device programming specification.                                                                                                                                                                |

- 3: The address in the Table Pointer decides which rows will be erased.

- 4: This bit is used only while accessing data EEPROM. It is implemented only in devices with data EEPROM.

. .. . \_

.....

**REGISTER 7-1:**

RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0     | 0 R/W-0                                | R/W-0 <sup>(3)</sup>                                                                                 | U-0                              | U-0                   | U-0                        | R/W-0            | R/W-0           |  |  |  |

|-----------|----------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|----------------------------|------------------|-----------------|--|--|--|

| TRAP      | R IOPUWR                               | SBOREN                                                                                               | _                                | _                     | _                          | CM               | PMSLP           |  |  |  |

| bit 15    |                                        |                                                                                                      |                                  |                       |                            |                  | bit 8           |  |  |  |

|           |                                        |                                                                                                      |                                  |                       |                            |                  |                 |  |  |  |

| R/W-0     | 0 R/W-0                                | R/W-0                                                                                                | R/W-0                            | R/W-0                 | R/W-0                      | R/W-1            | R/W-1           |  |  |  |

| EXTR      | R SWR                                  | SWDTEN <sup>(2)</sup>                                                                                | WDTO                             | SLEEP                 | IDLE                       | BOR              | POR             |  |  |  |

| bit 7     |                                        |                                                                                                      |                                  |                       |                            |                  | bit 0           |  |  |  |

|           |                                        |                                                                                                      |                                  |                       |                            |                  |                 |  |  |  |

| Legend:   |                                        |                                                                                                      | :4                               |                       | a a material in the second |                  |                 |  |  |  |

| R = Read  |                                        | W = Writable b                                                                                       | IT                               | •                     | nented bit, read           |                  |                 |  |  |  |

| -n = Valu | e at POR                               | '1' = Bit is set                                                                                     |                                  | '0' = Bit is cle      | ared                       | x = Bit is unkr  | nown            |  |  |  |

| bit 15    | TRAPR. Tra                             | p Reset Flag bit                                                                                     |                                  |                       |                            |                  |                 |  |  |  |

| bit io    |                                        | Conflict Reset has                                                                                   | occurred                         |                       |                            |                  |                 |  |  |  |

|           |                                        | Conflict Reset has                                                                                   |                                  | b                     |                            |                  |                 |  |  |  |

| bit 14    | IOPUWR: III                            | egal Opcode or L                                                                                     | Jninitialized V                  | V Access Reset        | Flag bit                   |                  |                 |  |  |  |

|           | 1 = An illega                          | al opcode detecti                                                                                    | on, an illegal                   | address mode          | or an Uninitial            | ized W register  | r is used as an |  |  |  |

|           |                                        | Pointer and cau                                                                                      |                                  |                       |                            |                  |                 |  |  |  |

|           | -                                      | al opcode or Unin                                                                                    |                                  | -                     | is not occurred            |                  |                 |  |  |  |

| bit 13    |                                        | <b>SBOREN:</b> Software Enable/Disable of BOR bit <sup>(3)</sup><br>1 = BOR is turned on in software |                                  |                       |                            |                  |                 |  |  |  |

|           |                                        | urned on in softw<br>urned off in softw                                                              |                                  |                       |                            |                  |                 |  |  |  |

| bit 12-10 | Unimpleme                              | nted: Read as '0                                                                                     |                                  |                       |                            |                  |                 |  |  |  |

| bit 9     | CM: Configu                            | CM: Configuration Word Mismatch Reset Flag bit                                                       |                                  |                       |                            |                  |                 |  |  |  |

|           |                                        | 1 = A Configuration Word Mismatch Reset has occurred                                                 |                                  |                       |                            |                  |                 |  |  |  |

|           | •                                      | uration Word Mis                                                                                     |                                  |                       | ed                         |                  |                 |  |  |  |

| bit 8     |                                        | • •                                                                                                  | am Memory Power During Sleep bit |                       |                            |                  |                 |  |  |  |

|           |                                        | memory bias vo<br>memory bias vo                                                                     |                                  |                       |                            |                  |                 |  |  |  |

| h:+ 7     |                                        |                                                                                                      |                                  |                       | y Sleep                    |                  |                 |  |  |  |

| bit 7     |                                        | EXTR: External Reset (MCLR) Pin bit<br>1 = A Master Clear (pin) Reset has occurred                   |                                  |                       |                            |                  |                 |  |  |  |

|           |                                        | r Clear (pin) Rese                                                                                   |                                  |                       |                            |                  |                 |  |  |  |

| bit 6     | SWR: Softwa                            | are Reset (Instru                                                                                    | ction) Flag bi                   | t                     |                            |                  |                 |  |  |  |

|           |                                        | instruction has t                                                                                    |                                  |                       |                            |                  |                 |  |  |  |

|           |                                        | r instruction has r                                                                                  |                                  |                       |                            |                  |                 |  |  |  |

| bit 5     | SWDTEN: S                              | oftware Enable/D                                                                                     | Disable of WE                    | )T bit <sup>(2)</sup> |                            |                  |                 |  |  |  |

|           | 1 = WDT is e                           |                                                                                                      |                                  |                       |                            |                  |                 |  |  |  |

| 1.11.4    | 0 = WDT is 0                           |                                                                                                      |                                  |                       |                            |                  |                 |  |  |  |

| bit 4     |                                        | chdog Timer Time                                                                                     | -                                |                       |                            |                  |                 |  |  |  |

|           |                                        | e-out has occurre                                                                                    |                                  |                       |                            |                  |                 |  |  |  |

| Note 1.   | All of the Depart                      | tatua hita may ha                                                                                    | act or closer                    | d in coffword C       | atting one of th           | ana hita in aaft | wara daga nat   |  |  |  |

| Note 1:   | All of the Reset s<br>cause a device F | •                                                                                                    | set of cleare                    | eu în soitware. S     | beaung one of th           | IESE DIIS IN SOT | ware upes not   |  |  |  |

| 2:        | If the FWDTEN (                        |                                                                                                      | is '1' (unprog                   | rammed), the V        | VDT is always o            | enabled, regard  | dless of the    |  |  |  |

|           | SWDTEN bit set                         | -                                                                                                    |                                  | ,-                    |                            |                  |                 |  |  |  |

| 3.        | The SBOREN bi                          | it is forced to '0' v                                                                                | vhen disabler                    | d by the Config       | iration hits BO            | REN<1.0> (FP     |                 |  |  |  |

**3:** The SBOREN bit is forced to '0' when disabled by the Configuration bits, BOREN<1:0> (FPOR<1:0>). When the Configuration bits are set to enable SBOREN, the default Reset state will be '1'.

### 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

### 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

## 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSC bits in the Flash Configuration Word (FOSCSEL); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

## 7.4 Brown-out Reset (BOR)

PIC24F16KL402 family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above the threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the power-up timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the BOR Reset does not automatically enable the PWRT.

## 7.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<13>). Setting SBOREN enables the BOR to function, as previously described. Clearing the SBOREN disables the BOR entirely. The SBOREN bit only operates in this mode; otherwise, it is read as '0'.

Placing BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

Note: Even when the BOR is under software control, the BOR Reset voltage level is still set by the BORV<1:0> Configuration bits; it can not be changed in software.

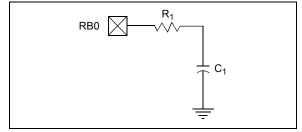

### 10.3 Ultra Low-Power Wake-up

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption. This feature provides a low-power technique for periodically waking up the device from Sleep mode.

To use this feature:

- 1. Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RB0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0. When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 10-2 for initializing the ULPWU module.

A series resistor, between RB0 and the external capacitor, provides overcurrent protection for the RB0/AN2/ULPWU pin and enables software calibration of the time-out (see Figure 10-1).

### FIGURE 10-1: SERIES RESISTOR

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

### EXAMPLE 10-2: ULTRA LOW-POWER WAKE-UP INITIALIZATION

| / / * * * * * * * * * * * * * * * * * *                                     |

|-----------------------------------------------------------------------------|

| // 1. Charge the capacitor on RB0                                           |

| / / * * * * * * * * * * * * * * * * * *                                     |

| TRISBbits.TRISB0 = 0;                                                       |

| LATBbits.LATB0 = 1;                                                         |

| for(i = 0; i < 10000; i++) Nop();                                           |

| / / * * * * * * * * * * * * * * * * * *                                     |

| //2. Stop Charging the capacitor on RB0                                     |

| / / * * * * * * * * * * * * * * * * * *                                     |

| TRISBbits.TRISB0 = 1;                                                       |

| / / * * * * * * * * * * * * * * * * * *                                     |

| //3. Enable ULPWU Interrupt                                                 |

| //*************************************                                     |

| IFS5bits.ULPWUIF = 0;                                                       |

| IEC5bits.ULPWUIE = 1;                                                       |

| IPC20bits.ULPWUIP = 0x7;                                                    |

| / / * * * * * * * * * * * * * * * * * *                                     |

| //4. Enable the Ultra Low Power Wakeup module and allow capacitor discharge |

| / / * * * * * * * * * * * * * * * * * *                                     |

| ULPWCONbits.ULPEN = 1;                                                      |

| ULPWCONbits.ULPSINK = 1;                                                    |

| //*************************************                                     |

| //5. Enter Sleep Mode                                                       |

| //*************************************                                     |

| Sleep();                                                                    |

| //for Sleep, execution will resume here                                     |

|                                                                             |

|              | (10-1. 1200                                                                      |                                                   |                |                      |                  |                    |         |  |  |  |

|--------------|----------------------------------------------------------------------------------|---------------------------------------------------|----------------|----------------------|------------------|--------------------|---------|--|--|--|

| U-0          | U-0                                                                              | U-0                                               | U-0            | U-0                  | U-0              | U-0                | U-0     |  |  |  |

|              |                                                                                  |                                                   |                |                      |                  |                    |         |  |  |  |

| bit 15       |                                                                                  |                                                   |                |                      |                  |                    | bita    |  |  |  |

|              |                                                                                  |                                                   |                |                      |                  |                    |         |  |  |  |

| U-0          | R/W-0                                                                            | R/W-0                                             | R/W-0          | R/W-0                | R/W-0            | R/W-0              | R/W-0   |  |  |  |

|              | T2OUTPS3                                                                         | T2OUTPS2                                          | T2OUTPS1       | T2OUTPS0             | TMR2ON           | T2CKPS1            | T2CKPS0 |  |  |  |

| bit 7        |                                                                                  |                                                   |                |                      |                  |                    | bit (   |  |  |  |

| Legend:      |                                                                                  |                                                   |                |                      |                  |                    |         |  |  |  |

| R = Readal   | ole bit                                                                          | W = Writable                                      | bit            | U = Unimplem         | nented bit, read | d as '0'           |         |  |  |  |

| -n = Value a | at POR                                                                           | '1' = Bit is set                                  |                | '0' = Bit is cleared |                  | x = Bit is unknown |         |  |  |  |

|              |                                                                                  |                                                   |                |                      |                  |                    |         |  |  |  |

| oit 15-7     | Unimplemen                                                                       | ted: Read as '                                    | כ'             |                      |                  |                    |         |  |  |  |

| oit 6-3      | T2OUTPS<3:                                                                       | T2OUTPS<3:0>: Timer2 Output Postscale Select bits |                |                      |                  |                    |         |  |  |  |

|              | 1111 = 1:16 Postscale                                                            |                                                   |                |                      |                  |                    |         |  |  |  |

|              | 1110 = 1:15 Postscale                                                            |                                                   |                |                      |                  |                    |         |  |  |  |

|              |                                                                                  |                                                   |                |                      |                  |                    |         |  |  |  |

|              | •                                                                                | •                                                 |                |                      |                  |                    |         |  |  |  |

|              | 0001 = 1:2 Postscale                                                             |                                                   |                |                      |                  |                    |         |  |  |  |

|              | 0000 = 1:1 Po                                                                    |                                                   |                |                      |                  |                    |         |  |  |  |

| oit 2        | -                                                                                | TMR2ON: Timer2 On bit                             |                |                      |                  |                    |         |  |  |  |

|              |                                                                                  | 1 = Timer2 is on                                  |                |                      |                  |                    |         |  |  |  |

|              | 0 = Timer2 is off<br><b>T2CKPS&lt;1:0&gt;:</b> Timer2 Clock Prescale Select bits |                                                   |                |                      |                  |                    |         |  |  |  |

| oit 1-0      |                                                                                  |                                                   | k Prescale Sel | ect bits             |                  |                    |         |  |  |  |

|              | 10 = Prescale                                                                    |                                                   |                |                      |                  |                    |         |  |  |  |

|              | 00 = Prescale                                                                    | -                                                 |                |                      |                  |                    |         |  |  |  |

|              |                                                                                  |                                                   |                |                      |                  |                    |         |  |  |  |

## REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                     | U-0                                                                                     | U-0                                                | U-0                                       |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------|--|

| _            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                         | <u> </u>                                                                                |                                                    | —                                         |  |

| bit 15       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                                         |                                                    | bit 8                                     |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                                         |                                                    |                                           |  |

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                   | R/W-0                                                                                   | R/W-0                                              | R/W-0                                     |  |