Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 17                                                                          |

| Program Memory Size        | 8KB (2.75K x 24)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 20-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl201-i-p |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-5:** PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS

|          |                                  | Pin Number    | r                        |     |        | Description                                       |  |  |  |  |

|----------|----------------------------------|---------------|--------------------------|-----|--------|---------------------------------------------------|--|--|--|--|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 14-Pin<br>PDIP/<br>TSSOP | I/O | Buffer |                                                   |  |  |  |  |

| AN0      | 2                                | 19            | 2                        | I   | ANA    | A/D Analog Inputs. Not available on PIC24F16KL10X |  |  |  |  |

| AN1      | 3                                | 20            | 3                        | Ι   | ANA    | family devices.                                   |  |  |  |  |

| AN2      | 4                                | 1             | —                        | Ι   | ANA    |                                                   |  |  |  |  |

| AN3      | 5                                | 2             | _                        | I   | ANA    |                                                   |  |  |  |  |

| AN4      | 6                                | 3             | _                        | I   | ANA    |                                                   |  |  |  |  |

| AN9      | 18                               | 15            | 12                       | I   | ANA    |                                                   |  |  |  |  |

| AN10     | 17                               | 14            | 11                       | I   | ANA    |                                                   |  |  |  |  |

| AN11     | 16                               | 13            | —                        | I   | ANA    |                                                   |  |  |  |  |

| AN12     | 15                               | 12            | _                        | I   | ANA    |                                                   |  |  |  |  |

| AN13     | 7                                | 4             | 4                        | I   | ANA    | 7                                                 |  |  |  |  |

| AN14     | 8                                | 5             | 5                        | I   | ANA    | 1                                                 |  |  |  |  |

| AN15     | 9                                | 6             | 6                        | I   | ANA    | 1                                                 |  |  |  |  |

| AVdd     | 20                               | 17            | 14                       | I   | ANA    | Positive Supply for Analog modules                |  |  |  |  |

| AVss     | 19                               | 16            | 13                       | I   | ANA    | Ground Reference for Analog modules               |  |  |  |  |

| CCP1     | 14                               | 11            | 10                       | I/O | ST     | CCP1 Capture Input/Compare and PWM Output         |  |  |  |  |

| CCP2     | 15                               | 12            | 9                        | I/O | ST     | CCP2 Capture Input/Compare and PWM Output         |  |  |  |  |

| C1INA    | 8                                | 5             | 5                        | I   | ANA    | Comparator 1 Input A (+)                          |  |  |  |  |

| C1INB    | 7                                | 4             | 4                        | I   | ANA    | Comparator 1 Input B (-)                          |  |  |  |  |

| C1INC    | 5                                | 2             | _                        | I   | ANA    | Comparator 1 Input C (+)                          |  |  |  |  |

| C1IND    | 4                                | 1             | _                        | I   | ANA    | Comparator 1 Input D (-)                          |  |  |  |  |

| C1OUT    | 17                               | 14            | 11                       | 0   | _      | Comparator 1 Output                               |  |  |  |  |

| CLK I    | 7                                | 4             | 9                        | I   | ANA    | Main Clock Input                                  |  |  |  |  |

| CLKO     | 8                                | 5             | 10                       | 0   | _      | System Clock Output                               |  |  |  |  |

| CN0      | 10                               | 7             | 7                        | I   | ST     | Interrupt-on-Change Inputs                        |  |  |  |  |

| CN1      | 9                                | 6             | 6                        | I   | ST     |                                                   |  |  |  |  |

| CN2      | 2                                | 19            | 2                        | I   | ST     |                                                   |  |  |  |  |

| CN3      | 3                                | 20            | 3                        | I   | ST     | 7                                                 |  |  |  |  |

| CN4      | 4                                | 1             | _                        | I   | ST     | 7                                                 |  |  |  |  |

| CN5      | 5                                | 2             | _                        | Ι   | ST     | ]                                                 |  |  |  |  |

| CN6      | 6                                | 3             | _                        | I   | ST     | 7                                                 |  |  |  |  |

| CN8      | 14                               | 11            | 10                       | I   | ST     | 7                                                 |  |  |  |  |

| CN9      | _                                | _             | —                        | I   | ST     | 7                                                 |  |  |  |  |

| CN11     | 18                               | 15            | 12                       | I   | ST     | 7                                                 |  |  |  |  |

| CN12     | 17                               | 14            | 11                       | I   | ST     | 7                                                 |  |  |  |  |

| CN13     | 16                               | 13            | —                        | I   | ST     | 7                                                 |  |  |  |  |

| CN14     | 15                               | 12            | _                        | Ι   | ST     | 7                                                 |  |  |  |  |

| CN21     | 13                               | 10            | 9                        | I   | ST     | 1                                                 |  |  |  |  |

| CN22     | 12                               | 9             | 8                        | I   | ST     | 1                                                 |  |  |  |  |

| CN23     | 11                               | 8             | —                        | I   | ST     | 1                                                 |  |  |  |  |

| CN29     | 8                                | 5             | 5                        | I   | ST     | 1                                                 |  |  |  |  |

| CN30     | 7                                | 4             | 4                        | 1   | ST     | 1                                                 |  |  |  |  |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

#### 2.4 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin Input Voltage High (VIH) and Input Voltage Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx) pins, programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 24.0 "Development Support**".

#### 2.5 External Oscillator Pins

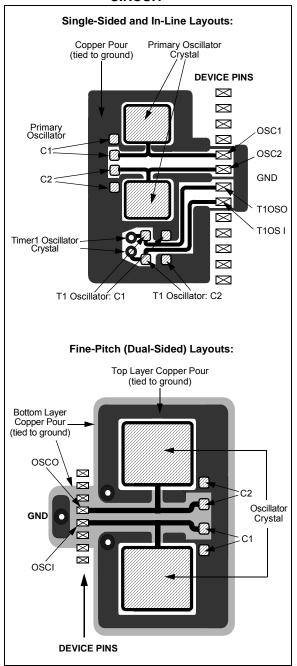

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

#### FIGURE 2-3: S

#### B: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals, in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

### 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and bussing. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 **Program Address Space**

The program address memory space of the PIC24F16KL402 family is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24F16KL402 family of devices are shown in Figure 4-1.

### FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24F16KL402 FAMILY DEVICES

|                            | PIC24F04KLXXX                                                                                                                                       | PIC24F08KL2XX                                                                                              | PIC24F08KL3XX                                                                                              |       | PIC24F08KL4XX                                                                                              | PIC24F16KLXXX                                                                                     |                                                                                    |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                            | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash<br>Program Memory<br>(1408 instructions) | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash |       | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table | 000000h<br>00002h<br>00004h<br>0000FEh<br>000100h<br>000104h<br>0001FEh<br>000200h |

| User Memory Space          |                                                                                                                                                     | Program Memory<br>(2816 instructions)                                                                      | <br>Program Memory<br>(2816 instructions)                                                                  | -     | Program Memory<br>(2816 instructions)                                                                      | <br>Flash<br>Program Memory<br>(5632 instructions)                                                | - 000AFEh                                                                          |

| User Me                    | Unimplemented<br>Read '0'                                                                                                                           | Unimplemented<br>Read '0'                                                                                  | Unimplemented<br>Read '0'                                                                                  |       | Unimplemented<br>Read '0'                                                                                  | Unimplemented                                                                                     | 002BFEh                                                                            |

|                            |                                                                                                                                                     |                                                                                                            | <br>Data EEPROM<br>(256 bytes)                                                                             | -<br> | Data EEPROM<br>(512 bytes)                                                                                 | <br>Read '0'<br>Data EEPROM<br>(512 bytes)                                                        | <ul> <li>7FFE00h</li> <li>7FFF00h</li> <li>7FFFFFh</li> <li>800000h</li> </ul>     |

| Ī                          | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | 800800h                                                                            |

| ace                        | Unique ID                                                                                                                                           | Unique ID                                                                                                  | Unique ID                                                                                                  |       | Unique ID                                                                                                  | Unique ID                                                                                         | 800802h<br>800808h                                                                 |

| lory Sp                    | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | 80080Ah                                                                            |

| Mem                        | Device Config Registers                                                                                                                             | Device Config Registers                                                                                    | Device Config Registers                                                                                    |       | Device Config Registers                                                                                    | Device Config Registers                                                                           | F80000h<br>F8000Eh                                                                 |

| Configuration Memory Space | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | F80010h<br>FEFFFEh                                                                 |

|                            | DEVID (2)                                                                                                                                           | DEVID (2)                                                                                                  | DEVID (2)                                                                                                  |       | DEVID (2)                                                                                                  | DEVID (2)                                                                                         | FF0000h<br>FFFFFFh                                                                 |

Note: Memory areas are not displayed to scale.

#### TABLE 4-10: PORTA REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 <sup>(1)</sup> | Bit 6  | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|----------------------|--------|----------------------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 02C0 | _      | _      | —      | —      | _      | _      | _     | _     | TRISA7               | TRISA6 | _                    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 00DF          |

| PORTA        | 02C2 |        | —      |        |        |        |        |       | —     | RA7                  | RA6    | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA         | 02C4 |        | —      |        |        |        |        |       | —     | LATA7                | LATA6  | —                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA         | 02C6 | -      | _      | _      | _      | _      | _      | _     | -     | ODA7                 | ODA6   | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These ports and their associated bits are unimplemented on 14-pin and 20-pin devices; read as '0'.

2: PORTA<5> is unavailable when MCLR functionality is enabled (MCLRE Configuration bit = 1).

#### TABLE 4-11: PORTB REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13 <sup>(1)</sup> | Bit 12 <sup>(1)</sup> | Bit 11 <sup>(2)</sup> | Bit 10 <sup>(2)</sup> | Bit 9  | Bit 8  | Bit 7 <sup>(1)</sup> | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3 <sup>(2)</sup> | Bit 2 <sup>(1)</sup> | Bit 1 <sup>(1)</sup> | Bit 0  | All<br>Resets |

|--------------|------|---------|---------|-----------------------|-----------------------|-----------------------|-----------------------|--------|--------|----------------------|----------------------|----------------------|--------|----------------------|----------------------|----------------------|--------|---------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13               | TRISB12               | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7               | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2               | TRISB1               | TRISB0 | FFFF          |

| PORTB        | 02CA | RB15    | RB14    | RB13                  | RB12                  | RB11                  | RB10                  | RB9    | RB8    | RB7                  | RB6                  | RB5                  | RB4    | RB3                  | RB2                  | RB1                  | RB0    | xxxx          |

| LATB         | 02CC | LATB15  | LATB14  | LATB13                | LATB12                | LATB11                | LATB10                | LATB9  | LATB8  | LATB7                | LATB6                | LATB5                | LATB4  | LATB3                | LATB2                | LATB1                | LATB0  | xxxx          |

| ODCB         | 02CE | ODB15   | ODB14   | ODB13                 | ODB12                 | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7                 | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2                 | ODB1                 | ODB0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These ports and their associated bits are unimplemented on 14-pin and 20-pin devices.

2: These ports and their associated bits are unimplemented in 14-pin devices.

#### TABLE 4-12: PAD CONFIGURATION REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11                 | Bit 10     | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|------------------------|------------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| PADCFG1      | 02FC | —      | —      | _      | —      | SDO2DIS <sup>(1)</sup> | SCK2DIS(1) | SDO1DIS | SCK1DIS | —     | _     | _     | _     | _     | —     | —     | —     | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

### 6.0 DATA EEPROM MEMORY

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information on Data       |

|       | EEPROM, refer to the "dsPIC33/PIC24        |

|       | Family Reference Manual", "Data            |

|       | EEPROM" (DS39720).                         |

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFFFh. For PIC24FXXKL4XX devices, the size of the data EEPROM is 256 words (7FFE00h to 7FFFFh). For PIC24FXXKL3XX devices, the size of the data EEPROM is 128 words (7FFF0h to 7FFFFh). The data EEPROM is not implemented in PIC24F08KL20X or PIC24F04KL10X devices.

The data EEPROM is organized as 16-bit wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

#### 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle, and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

#### 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

| //Disable Interrupts For 5 instr | uctions |

|----------------------------------|---------|

| asm volatile("disi #5");         |         |

| //Issue Unlock Sequence          |         |

| asm volatile ("mov #0x55, W0     | \n"     |

| "mov W0, NVMKEY                  | \n"     |

| "mov #0xAA, W1                   | \n"     |

| "mov W1, NVMKEY                  | \n");   |

| // Perform Write/Erase operation | S       |

| asm volatile ("bset NVMCON, #WR  | \n"     |

| "nop                             | \n"     |

| "nop                             | \n");   |

#### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|-------|-----|-----|---------|---------|--------|---------|-------|

| —     | —   | —   | MATHERR | ADDRERR | STKERR | OSCFAIL | —     |

| bit 7 |     |     |         |         |        |         | bit 0 |

| Legend:                                                                                                                      |                                                                                                                                                 |                                                                                    |                       |                    |  |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------|--------------------|--|

| R = Reada                                                                                                                    | ble bit                                                                                                                                         | W = Writable bit                                                                   | U = Unimplemented bit | , read as '0'      |  |

| -n = Value                                                                                                                   | at POR                                                                                                                                          | '1' = Bit is set                                                                   | '0' = Bit is cleared  | x = Bit is unknown |  |

| bit 15                                                                                                                       | 1 = Interr                                                                                                                                      | Interrupt Nesting Disable bit<br>upt nesting is disabled<br>upt nesting is enabled |                       |                    |  |

| bit 14-5<br>bit 4                                                                                                            | Unimplemented: Read as '0'<br>MATHERR: Arithmetic Error Trap Status bit<br>1 = Overflow trap has occurred<br>0 = Overflow trap has not occurred |                                                                                    |                       |                    |  |

| bit 3 ADDRERR: Address Error Trap Status b<br>1 = Address error trap has occurred<br>0 = Address error trap has not occurred |                                                                                                                                                 |                                                                                    | it                    |                    |  |

| bit 2                                                                                                                        | STKERR: Stack Error Trap Status bit                                                                                                             |                                                                                    |                       |                    |  |

|       | <ol> <li>1 = Stack error trap has occurred</li> <li>0 = Stack error trap has not occurred</li> </ol>            |

|-------|-----------------------------------------------------------------------------------------------------------------|

| bit 1 | OSCFAIL: Oscillator Failure Trap Status bit                                                                     |

|       | <ul><li>1 = Oscillator failure trap has occurred</li><li>0 = Oscillator failure trap has not occurred</li></ul> |

| bit 0 | Unimplemented: Read as '0'                                                                                      |

**—**

#### REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| R/W-0         | U-0                 | R/W-0                              | R/W-0           | R/W-0             | U-0              | U-0             | R/W-0       |

|---------------|---------------------|------------------------------------|-----------------|-------------------|------------------|-----------------|-------------|

| NVMIF         | _                   | AD1IF                              | U1TXIF          | U1RXIF            |                  |                 | T3IF        |

| bit 15        |                     |                                    |                 |                   |                  |                 | bit 8       |

|               | 5444.6              |                                    |                 | <b>-</b>          |                  |                 | 5444.6      |

| R/W-0         | R/W-0               | U-0                                | U-0             | R/W-0             | R/W-0            | U-0             | R/W-0       |

| T2IF          | CCP2IF              | —                                  | —               | T1IF              | CCP1IF           | —               | INTOIF      |

| bit 7         |                     |                                    |                 |                   |                  |                 | bit (       |

| Legend:       |                     |                                    |                 |                   |                  |                 |             |

| R = Readable  | e bit               | W = Writable                       | bit             | U = Unimplen      | nented bit, read | d as '0'        |             |

| -n = Value at | POR                 | '1' = Bit is set                   |                 | '0' = Bit is clea | ared             | x = Bit is unkı | nown        |

|               |                     |                                    |                 |                   |                  |                 |             |

| bit 15        | NVMIF: NVM          | I Interrupt Flag                   | Status bit      |                   |                  |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 14        | -                   | ted: Read as '                     |                 |                   |                  |                 |             |

| bit 13        | <b>AD1IF:</b> A/D ( | Conversion Cor                     | nplete Interrup | t Flag Status bit | t                |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

| h:1 40        | -                   | request has no                     |                 | Otatus hit        |                  |                 |             |

| bit 12        |                     | RT1 Transmitter                    |                 | Status bit        |                  |                 |             |

|               |                     | request has no                     |                 |                   |                  |                 |             |

| bit 11        | -                   | RT1 Receiver In                    |                 | tatus bit         |                  |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 10-9      | Unimplemer          | ted: Read as '                     | 0'              |                   |                  |                 |             |

| bit 8         | T3IF: Timer3        | Interrupt Flag                     | Status bit      |                   |                  |                 |             |

|               | •                   | request has oc                     |                 |                   |                  |                 |             |

|               |                     | request has no                     |                 |                   |                  |                 |             |

| bit 7         |                     | Interrupt Flag                     |                 |                   |                  |                 |             |

|               |                     | request has oc<br>request has no   |                 |                   |                  |                 |             |

| bit 6         |                     | -                                  |                 | ot Flag Status b  | it               |                 |             |

|               | •                   | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 5-4       | Unimplemer          | ted: Read as '                     | 0'              |                   |                  |                 |             |

| bit 3         | T1IF: Timer1        | Interrupt Flag                     | Status bit      |                   |                  |                 |             |

|               | •                   | request has oc<br>request has no   |                 |                   |                  |                 |             |

| bit 2         | -                   | -                                  |                 | ot Flag Status b  | it (ECCP1 on F   | PIC24FXXKL40    | )X devices) |

|               | 1 = Interrupt       | request has oc                     | curred          | 0                 | Υ.               |                 | ,           |

| L:1 4         | -                   | request has no                     |                 |                   |                  |                 |             |

| bit 1         | -                   | ted: Read as '                     |                 |                   |                  |                 |             |

|               |                     |                                    |                 |                   |                  |                 |             |

| bit 0         |                     | rnal Interrupt 0<br>request has oc | -               |                   |                  |                 |             |

| R/W-0        | U-0           | R/W-0                                  | R/W-0          | R/W-0             | U-0              | U-0            | R/W-0  |

|--------------|---------------|----------------------------------------|----------------|-------------------|------------------|----------------|--------|

| NVMIE        |               | AD1IE                                  | <b>U1TXIE</b>  | U1RXIE            | —                | _              | T3IE   |

| bit 15       |               |                                        |                |                   |                  |                | bit 8  |

|              |               |                                        |                |                   |                  |                |        |

| R/W-0        | R/W-0         | U-0                                    | U-0            | R/W-0             | R/W-0            | U-0            | R/W-0  |

| T2IE         | CCP2IE        | _                                      |                | T1IE              | CCP1IE           | —              | INTOIE |

| bit 7        |               |                                        |                |                   |                  |                | bit C  |

| Legend:      |               |                                        |                |                   |                  |                |        |

| R = Readab   | le bit        | W = Writable t                         | bit            | U = Unimplen      | nented bit, read | l as '0'       |        |

| -n = Value a | t POR         | '1' = Bit is set                       |                | '0' = Bit is clea | ared             | x = Bit is unk | nown   |

| L:4 / C      |               |                                        | - 1-14         |                   |                  |                |        |

| bit 15       |               | /I Interrupt Enabl<br>request is enabl |                |                   |                  |                |        |

|              |               | request is not er                      |                |                   |                  |                |        |

| bit 14       | Unimpleme     | nted: Read as '0                       | ,              |                   |                  |                |        |

| bit 13       | AD1IE: A/D    | Conversion Com                         | plete Interrup | t Enable bit      |                  |                |        |

|              |               | request is enabl                       |                |                   |                  |                |        |

| L:1 40       | -             | request is not er                      |                | <b>bla b</b> :4   |                  |                |        |

| bit 12       |               | RT1 Transmitter<br>request is enabl    | •              | DIE DIT           |                  |                |        |

|              |               | request is not er                      |                |                   |                  |                |        |

| bit 11       | U1RXIE: UA    | RT1 Receiver In                        | terrupt Enable | e bit             |                  |                |        |

|              |               | request is enabl                       |                |                   |                  |                |        |

|              | -             | request is not er                      |                |                   |                  |                |        |

| bit 10-9     | -             | nted: Read as '0                       |                |                   |                  |                |        |

| bit 8        |               | 3 Interrupt Enable                     |                |                   |                  |                |        |

|              |               | request is enabl<br>request is not er  |                |                   |                  |                |        |

| bit 7        |               | 2 Interrupt Enable                     |                |                   |                  |                |        |

|              |               | request is enabl                       |                |                   |                  |                |        |

|              | 0 = Interrupt | request is not er                      | nabled         |                   |                  |                |        |

| bit 6        |               | pture/Compare/F                        | -              | ot Enable bit     |                  |                |        |

|              |               | request is enabl<br>request is not er  |                |                   |                  |                |        |

| bit 5-4      |               | nted: Read as '0                       |                |                   |                  |                |        |

| bit 3        | -             | Interrupt Enable                       |                |                   |                  |                |        |

| bit 5        |               | request is enabl                       |                |                   |                  |                |        |

|              |               | request is not er                      |                |                   |                  |                |        |

| bit 2        | CCP1IE: Ca    | pture/Compare/F                        | WM1 Interru    | ot Enable bit     |                  |                |        |

|              |               | request is enabl                       |                |                   |                  |                |        |

| L:1 4        |               | request is not er                      |                |                   |                  |                |        |

| bit 1        | -             | nted: Read as '0                       |                |                   |                  |                |        |

| bit 0        |               | rnal Interrupt 0 E<br>request is enabl |                |                   |                  |                |        |

|              |               | TEQUEST IS ETIDDI                      | 6U             |                   |                  |                |        |

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7   | CLKLOCK: Clock Selection Lock Enable bit                                                 |

|---------|------------------------------------------------------------------------------------------|

|         | <u>If FSCM is Enabled (FCKSM1 = 1):</u>                                                  |

|         | 1 = Clock and PLL selections are locked                                                  |

|         | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit |

|         | If FSCM is Disabled (FCKSM1 = 0):                                                        |

|         | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.  |

| bit 6   | Unimplemented: Read as '0'                                                               |

| bit 5   | LOCK: PLL Lock Status bit <sup>(2)</sup>                                                 |

|         | 1 = PLL module is in lock or the PLL module start-up timer is satisfied                  |

|         | 0 = PLL module is out of lock, the PLL start-up timer is running or PLL is disabled      |

| bit 4   | Unimplemented: Read as '0'                                                               |

| bit 3   | CF: Clock Fail Detect bit                                                                |

|         | 1 = FSCM has detected a clock failure                                                    |

|         | 0 = No clock failure has been detected                                                   |

| bit 2   | SOSCDRV: Secondary Oscillator Drive Strength bit <sup>(3)</sup>                          |

|         | 1 = High-power SOSC circuit is selected                                                  |

|         | 0 = Low/high-power select is done via the SOSCSRC Configuration bit                      |

| bit 1   | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                    |

|         | 1 = Enables secondary oscillator                                                         |

|         | 0 = Disables secondary oscillator                                                        |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                      |

|         | 1 = Initiates an oscillator switch to the clock source specified by the NOSC<2:0> bits   |

|         | 0 = Oscillator switch is complete                                                        |

| Note 1: | Reset values for these bits are determined by the FNOSC<2:0> Configuration bits.         |

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- **3:** When SOSC is selected to run from a digital clock input rather than an external crystal (SOSCSRC = 0), this bit has no effect.

| ROI         DOZE2         DOZE1         DOZE0         DOZEN <sup>(1)</sup> RCDIV2         RCDIV1         RCD           bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ′W-1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0                   bit 15       Recadable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit         1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts clear the DOZEN bit         bit 14-12       DOZE         DOZE         110 = 1:64       101 = 1:32         100 = 1:16       111 = 1:32         100 = 1:1       DOZE Colspan="2">DOZE Enable bit <sup>(1)</sup> 1 = DOZE       DOZE Enable bit <sup>(1)</sup> 1 = DOZE       COCON:11:12) = 111 or 001:         101 = 1:2       DOZE         000 = 1:1       When COSC         bit 10-8       RCDIV-2:0>: FRC Postscaler Select bits         When COSC       Colspan="2">COSC         111 = 312       Colspan="2">Colspan= Set to 1:1         bit 10-8       RCDIV-2:0: FRC Postscaler Select b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DIV0  |

| -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 8 |

| -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.0   |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>bit 14-12 DOZE-2:0>: CPU-to-Peripheral Clock Ratio Select bits<br>111 = 1:128<br>100 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:3<br>010 = 1:16<br>011 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: DOZE Enable bit <sup>(1)</sup><br>1 = DOZE-2:0> bits specify the CPU-to-peripheral clock ratio<br>0 = CPU and the peripheral clock ratio are set to 1:1<br>bit 10-8 RCDIV-2:0>: FRC Postscaler Select bits<br>When COSC-2:0> (OSCCON<14:12) = 111 or 001:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-4)<br>011 = 4 MHz (divide-by-4)<br>011 = 4 MHz (divide-by-2) (offault)<br>00 = 8 MHz (divide-by-2) (offault)<br>00 = 8 MHz (divide-by-2) (00Fault)<br>110 = 156 kHz (divide-by-32)<br>110 = 156 kHz (divide-by-32)<br>110 = 156 kHz (divide-by-32)<br>111 = 1.95 kHz (divide-by-32)<br>111 = 1.95 kHz (divide-by-32)<br>111 = 1.95 kHz (divide-by-32)<br>112 = 1.05 kHz (divide-by-32)<br>113 = 1.95 kHz (divide-by-32)<br>114 = 1.95 kHz (divide-by-32)<br>115 = 1.95 kHz (divide-by-32)<br>116 = 7.81 kHz (divide-by-32)<br>117 = 1.95 kHz (divide-by-4)<br>118 = 1.95 kHz (divide-by-32)<br>119 = 31.25 kHz (divide-by-32)<br>110 = 1.55 kHz (divide-by-4)<br>111 = 1.95 kHz (divide-by-32)<br>112 = 1.95 kHz (divide-by-32)<br>113 = 1.95 kHz (divide-by-4)<br>114 = 1.95 kHz (divide-by-4)<br>115 = 1.55 kHz (divide-by-4)<br>116 = 1.55 kHz (divide-by-4)<br>117 = 1.95 kHz (divide-by-4)<br>118 = 1.95 kHz (divide-by-4)<br>119 = 1.55 kHz (divide-by-4)<br>110 = 1.55 kHz (divide-by-4)<br>111 = 1.95 kHz (divide-by-4)<br>112 = 1.95 kHz (divide-by-4)<br>113 = 1.95 kHz (divide-by-4)<br>114 = 1.95 kHz (divide-by-4)<br>115 = 1.55 kHz (divide-by-4)<br>116 = 1.55 kHz (divide-by-4)<br>117 = 1.55 kHz (divide-by-4)<br>118 = 1.55 kHz (divide-by-4)<br>119 = 1.55 kHz (divide-by-4)<br>110 = 1.55 kHz (divide-by-4)<br>111 = 1.95 kHz (divide-by-4)<br>111 = 1.95 kHz (divi       |       |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<br>.n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 15ROI: Recover on Interrupt bit<br>.1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>.1 = Interrupts have no effect on the DOZEN bitbit 14-12DOZE-2:0>: CPU-to-Peripheral Clock Ratio Select bits111 = 1:128<br>.100 = 1:6<br>.011 = 1:8<br>.000 = 1:16<br>.001 = 1:2<br>.000 = 1:1bit 11DOZEN: DOZE Enable bit(1)<br>.000 = 1:1bit 11DOZEN: DOZE Enable bit(1)<br>.000 = 1:1bit 10-RCDIV<2:0>: FRC Postscaler Select bitsWhen COSC-2:0> (DSCCON<14:12) = 111 or .001;<br>.111 = 31.25 kHz (divide-by-26)<br>.100 = 125 kHz (divide-by-4)<br>.001 = 25 kHz (divide-by-4)<br>.001 = 20 HHz (divide-by-4)<br>.001 = 20 HHz (divide-by-4)<br>.001 = 4 MHz (divide-by-4)<br>.001 = 4 MHz (divide-by-256)<br>.100 = 2.0> (OSCCON<14:12> = 110;<br>.111 = 1.95 kHz (divide-by-32)<br>.000 = 31.25 kHz (divide-by-4)<br>.011 = 62.5 kHz (divide-by-64)<br>.011 = 1.56 kHz (divide-by-64)<br>.011 = 1.56 kHz (divide-by-32)<br>.000 = 31.25 kHz (divide-by-4)<br>.011 = 25 kHz (divide-by-4)<br>.011 = 1.56 kHz (divide-by-4)<br>.011 = 1.56 kHz (divide-by-4)<br>.011 = 1.56 kHz (divide-by-4)<br>.011 = 1.56 kHz (divide-by-4)<br>.011 = 7.81 kHz (divide-by-64)<br>.011 = 1.25 kHz (divide-by-64)<br>.011 = 1.56 kHz (divide-by-64)<br>.011 = 1.56 kHz (divide-by-4)<br>.011 = 1.25 kHz (divide-by-4)<br>.011 = 1.56 kHz (divide-by-4)<br>.011 = 1.25 kHz (divide-by-4)<br><td>bit (</td>                                                                                                                                                                                                                                                                                                                                                                                                                    | bit ( |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1         0 = Interrupts have no effect on the DOZEN bit       DOZE-2:0>: CPU-to-Peripheral Clock Ratio Select bits         111 = 1:128       100 = 1:64         100 = 1:16       111 = 1:2         010 = 1:12       000 = 1:16         011 = 1:2       000 = 1:1         bit 10       DOZEE-2:0> bits specify the CPU-to-peripheral clock ratio         0 = CPU and the peripheral clock ratio are set to 1:1       bit 10-8         RCDIV<2:0>: FRC Postscaler Select bits         When COSC-2:0> (OSCCON<14:12) = 111 or 001:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>bit 14-12 DDZE<2:0>: CPU-to-Peripheral Clock Ratio Select bits<br>111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: DOZE Enable bit <sup>(1)</sup><br>1 = DOZE<2:0> bits specify the CPU-to-peripheral clock ratio<br>0 = CPU and the peripheral clock ratio are set to 1:1<br>bit 10-8 RCDIV<2:0>: FRC Postscaler Select bits<br>When COSC<2:0> (OSCCON<14:12) = 111 or 001:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-4)<br>011 = 1 MHz (divide-by-4)<br>011 = 1 MHz (divide-by-4)<br>011 = 2 MHz (divide-by-4)<br>011 = 1 MHz (divide-by-2)<br>100 = 500 kHz (divide-by-2)<br>100 = 4 MHz (divide-by-4)<br>011 = 1 MHz (divide-by-2)<br>100 = 4 MHz (divide-by-2)<br>100 = 50 KHz (divide-by-2)<br>100 = 50 KHz (divide-by-2)<br>100 = 50 KHz (divide-by-2)<br>101 = 7.81 kHz (divide-by-2)<br>102 = 7.81 kHz (divide-by-2)<br>104 = 4 MHz (divide-by-2)<br>105 = 7.81 kHz (divide-by-2)<br>105 = 7.81 kHz (divide-by-2)<br>106 = 7.81 kHz (divide-by-2)<br>107 = 7.81 kHz (divide-by-2)<br>108 = 7.81 kHz (divide-by-2)<br>109 = 3.125 kHz (divide-by-32)<br>100 = 3.125 kHz (divide-by-4)<br>101 = 1.5.62 kHz (divide-by-4)<br>102 = 3.125 kHz (divide-by-4)<br>103 = 3.125 kHz (divide-by-4)<br>104 = 3.125 kHz (divide-by-4)<br>105 = 3.125 kHz (divide-by-4)<br>105 = 3.125 kHz (divide-by-4)<br>105 = 3.125 kHz (divide-by-4)<br>105 = 3.125 kHz (divide-by-4)<br>106 = 3.125 kHz (divide-by-4)<br>107 = 3.125 kHz (divide-by-4)<br>108 = 3.125 kHz (divide-by-4)<br>109 = 3.125 kHz (divide-by-4)<br>100 = 3.125 kHz (divide-by-4)<br>101 = 1.5.5 kHz (divide-by-4)<br>102 = 3.125 kHz (divide-by-4)<br>103 = 3.5 kHz (divide-by-4)<br>104 = 3.5 kHz (divide- |       |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

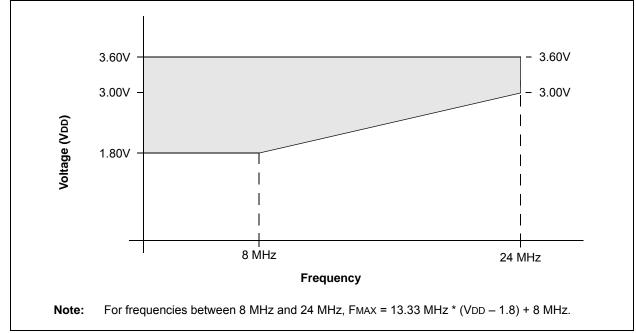

| bit 11<br>DOZEN: DOZE Enable bit <sup>(1)</sup><br>1 = DOZE<2:0> bits specify the CPU-to-peripheral clock ratio<br>0 = CPU and the peripheral clock ratio are set to 1:1<br>bit 10-8<br>RCDIV<2:0>: FRC Postscaler Select bits<br>When COSC<2:0> (OSCCON<14:12) = 111 or 001:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-3)<br>010 = 2 MHz (divide-by-3)<br>010 = 2 MHz (divide-by-4)<br>011 = 1 MHz (divide-by-2) (default)<br>000 = 8 MHz (divide-by-1)<br>When COSC<2:0> (OSCCON<14:12>) = 110:<br>111 = 1.95 kHz (divide-by-26)<br>110 = 7.81 kHz (divide-by-32)<br>100 = 31.25 kHz (divide-by-36)<br>011 = 62.5 kHz (divide-by-4)<br>010 = 125 kHz (divide-by-4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |