#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2014112                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 17                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

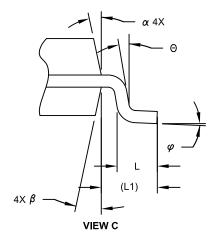

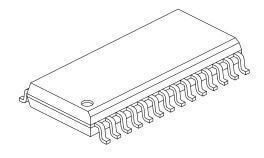

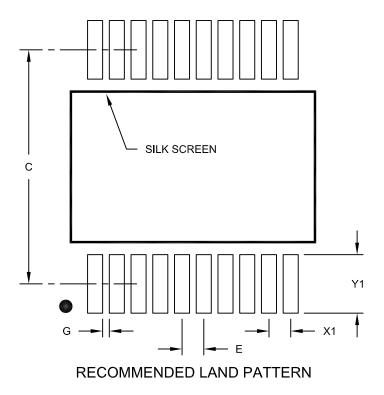

| Mounting Type              | Surface Mount                                                                |

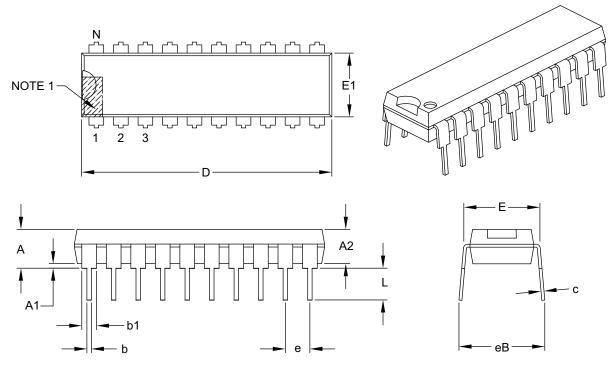

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl201-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                  | Pin N         | umber                             |               |     |                   |                                                     |

|----------|----------------------------------|---------------|-----------------------------------|---------------|-----|-------------------|-----------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | I/O | Buffer            | Description                                         |

| AN0      | 2                                | 19            | 2                                 | 27            | I   | ANA               | A/D Analog Inputs. Not available on PIC24F16KL30X   |

| AN1      | 3                                | 20            | 3                                 | 28            | I   | ANA               | family devices.                                     |

| AN2      | 4                                | 1             | 4                                 | 1             | I   | ANA               |                                                     |

| AN3      | 5                                | 2             | 5                                 | 2             | I   | ANA               |                                                     |

| AN4      | 6                                | 3             | 6                                 | 3             | Ι   | ANA               |                                                     |

| AN5      | _                                | _             | 7                                 | 4             | Ι   | ANA               |                                                     |

| AN9      | 18                               | 15            | 26                                | 23            | I   | ANA               |                                                     |

| AN10     | 17                               | 14            | 25                                | 22            | Ι   | ANA               |                                                     |

| AN11     | 16                               | 13            | 24                                | 21            | Ι   | ANA               |                                                     |

| AN12     | 15                               | 12            | 23                                | 20            | Ι   | ANA               |                                                     |

| AN13     | 7                                | 4             | 9                                 | 6             | Ι   | ANA               |                                                     |

| AN14     | 8                                | 5             | 10                                | 7             | I   | ANA               |                                                     |

| AN15     | 9                                | 6             | 11                                | 8             | I   | ANA               |                                                     |

| ASCL1    | _                                | _             | 15                                | 12            | I/O | I <sup>2</sup> C™ | Alternate MSSP1 I <sup>2</sup> C Clock Input/Output |

| ASDA1    | _                                | _             | 14                                | 11            | I/O | l <sup>2</sup> C  | Alternate MSSP1 I <sup>2</sup> C Data Input/Output  |

| AVdd     | 20                               | 17            | 28                                | 25            | Ι   | ANA               | Positive Supply for Analog modules                  |

| AVss     | 19                               | 16            | 27                                | 24            | Ι   | ANA               | Ground Reference for Analog modules                 |

| CCP1     | 14                               | 11            | 20                                | 17            | I/O | ST                | CCP1/ECCP1 Capture Input/Compare and PWM<br>Output  |

| CCP2     | 15                               | 12            | 23                                | 20            | I/O | ST                | CCP2 Capture Input/Compare and PWM Output           |

| CCP3     | 13                               | 10            | 19                                | 16            | I/O | ST                | CCP3 Capture Input/Compare and PWM Output           |

| C1INA    | 8                                | 5             | 7                                 | 4             | I   | ANA               | Comparator 1 Input A (+)                            |

| C1INB    | 7                                | 4             | 6                                 | 3             | I   | ANA               | Comparator 1 Input B (-)                            |

| C1INC    | 5                                | 2             | 5                                 | 2             | I   | ANA               | Comparator 1 Input C (+)                            |

| C1IND    | 4                                | 1             | 4                                 | 1             | I   | ANA               | Comparator 1 Input D (-)                            |

| C1OUT    | 17                               | 14            | 25                                | 22            | 0   | _                 | Comparator 1 Output                                 |

| C2INA    | 5                                | 2             | 5                                 | 2             | I   | ANA               | Comparator 2 Input A (+)                            |

| C2INB    | 4                                | 1             | 4                                 | 1             | I   | ANA               | Comparator 2 Input B (-)                            |

| C2INC    | 8                                | 5             | 7                                 | 4             | Ι   | ANA               | Comparator 2 Input C (+)                            |

| C2IND    | 7                                | 4             | 6                                 | 3             | Ι   | ANA               | Comparator 2 Input D (-)                            |

| C2OUT    | 14                               | 11            | 20                                | 17            | 0   |                   | Comparator 2 Output                                 |

| CLK I    | 7                                | 4             | 9                                 | 6             | Ι   | ANA               | Main Clock Input                                    |

| CLKO     | 8                                | 5             | 10                                | 7             | 0   | _                 | System Clock Output                                 |

## TABLE 1-4: PIC24F16KL40X/30X FAMILY PINOUT DESCRIPTIONS

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

# 3.0 CPU

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the CPU, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"CPU"** (DS39703).

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16<sup>th</sup> Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K word boundary of either program memory or data EEPROM memory, defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (i.e., A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by a 16-bit integer signed and unsigned division. All divide operations require 19 cycles to complete, but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme, with up to eight sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is illustrated in Figure 3-1.

# 3.1 Programmer's Model

Figure 3-2 displays the programmer's model for the PIC24F. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions.

Table 3-1 provides a description of each register. All registers associated with the programmer's model are memory mapped.

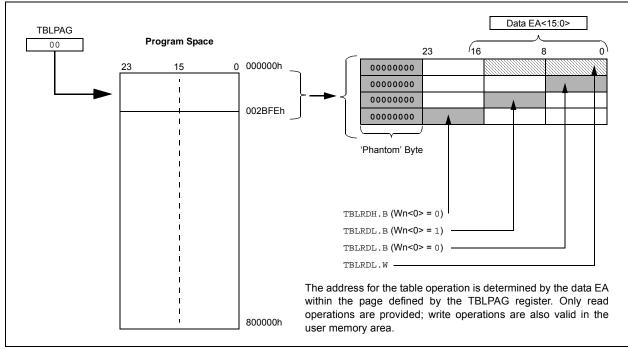

## 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through data space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

| Note: | The TBLRDH and TBLWTH instructions are |

|-------|----------------------------------------|

|       | not used while accessing data EEPROM   |

|       | memory.                                |

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when the byte select is '1'; the lower byte is selected when it is '0'.

TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

|                 | <b>D</b> 4 4 4 6                                                      | <b>D</b> 444 A                         | <b>D</b> 4 4 4 4       |                       |                       |                       |                       |  |  |  |  |

|-----------------|-----------------------------------------------------------------------|----------------------------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

| R/SO-0, HC      | R/W-0                                                                 | R/W-0                                  | R/W-0                  | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |  |

| WR              | WREN                                                                  | WRERR                                  | PGMONLY                |                       |                       | —                     | —                     |  |  |  |  |

| bit 15          |                                                                       |                                        |                        |                       |                       |                       | bit 8                 |  |  |  |  |

|                 |                                                                       |                                        |                        |                       |                       |                       |                       |  |  |  |  |

| U-0             | R/W-0                                                                 | R/W-0                                  | R/W-0                  | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |  |

| —               | ERASE                                                                 | NVMOP5 <sup>(1)</sup>                  | NVMOP4 <sup>(1)</sup>  | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |  |  |  |  |

| bit 7 bit       |                                                                       |                                        |                        |                       |                       |                       |                       |  |  |  |  |

|                 |                                                                       |                                        |                        |                       |                       |                       |                       |  |  |  |  |

| Legend:         | egend: HC = Hardware Clearable bit U = Unimplemented bit, read as '0' |                                        |                        |                       |                       |                       |                       |  |  |  |  |

| R = Readable    | bit                                                                   | W = Writable b                         | it                     | SO = Settabl          | e Only bit            |                       |                       |  |  |  |  |

| -n = Value at I | POR                                                                   | '1' = Bit is set                       |                        | '0' = Bit is cle      | ared                  | x = Bit is unk        | nown                  |  |  |  |  |

|                 |                                                                       |                                        |                        |                       |                       |                       |                       |  |  |  |  |

| bit 15          | WR: Write Co                                                          | ontrol bit (progra                     | m or erase)            |                       |                       |                       |                       |  |  |  |  |

|                 |                                                                       | a data EEPROM                          |                        | cvcle (can be s       | et but not clea       | red in software       | e)                    |  |  |  |  |

|                 |                                                                       | le is complete (                       |                        | •                     |                       |                       | - /                   |  |  |  |  |

| bit 14          | WREN: Write                                                           | Enable bit (eras                       | e or program)          |                       |                       |                       |                       |  |  |  |  |

|                 | 1 = Enables a                                                         | in erase or prog                       | ram operation          |                       |                       |                       |                       |  |  |  |  |

|                 | 0 = No operat                                                         | tion allowed (dev                      | vice clears this t     | oit on completion     | on of the write/      | erase operatio        | on)                   |  |  |  |  |

| bit 13          | WRERR: Flas                                                           | sh Error Flag bit                      |                        |                       |                       |                       |                       |  |  |  |  |

|                 | 1 = A write o                                                         | operation is pre                       | maturely termir        | nated (any MC         | LR or WDT             | Reset during          | programming           |  |  |  |  |

|                 | operation                                                             | /                                      |                        |                       |                       |                       |                       |  |  |  |  |

|                 |                                                                       | operation comp                         |                        | ліу                   |                       |                       |                       |  |  |  |  |

| bit 12          |                                                                       | Program Only En                        |                        |                       | <i>.</i>              |                       |                       |  |  |  |  |

|                 |                                                                       | eration is execute<br>c erase-before-v |                        |                       |                       | tically by an a       | rade of torget        |  |  |  |  |

|                 | address(e                                                             |                                        | ville, wille oper      | ations are pred       |                       | lucally by all e      | lase of larger        |  |  |  |  |

| bit 11-7        | •                                                                     | ted: Read as '0'                       |                        |                       |                       |                       |                       |  |  |  |  |

| bit 6           | -                                                                     | e Operation Sel                        |                        |                       |                       |                       |                       |  |  |  |  |

| Sit o           |                                                                       | an erase opera                         |                        | s set                 |                       |                       |                       |  |  |  |  |

|                 |                                                                       | a write operatio                       |                        |                       |                       |                       |                       |  |  |  |  |

| bit 5-0         | NVMOP<5:0>                                                            | . Programming                          | Operation Com          | mand Byte bits        | <sub>3</sub> (1)      |                       |                       |  |  |  |  |

|                 | Erase Operati                                                         | ions (when ERA                         | <u>SE bit is '1'):</u> | -                     |                       |                       |                       |  |  |  |  |

|                 | 011010 = Era                                                          | ases 8 words                           |                        |                       |                       |                       |                       |  |  |  |  |

|                 | 011001 = Era                                                          |                                        |                        |                       |                       |                       |                       |  |  |  |  |

|                 | 011000 = Era                                                          |                                        |                        |                       |                       |                       |                       |  |  |  |  |

|                 |                                                                       | ases entire data                       |                        | • 'o')•               |                       |                       |                       |  |  |  |  |

|                 | 001xxx = Wr                                                           | Operations (wh<br>ites 1 word          | EILERASE DIL IS        | <u> </u>              |                       |                       |                       |  |  |  |  |

|                 |                                                                       |                                        |                        |                       |                       |                       |                       |  |  |  |  |

### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

Note 1: These NVMOP configurations are unimplemented on PIC24F04KL10X and PIC24F08KL20X devices.

## REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0                       | U-0                                                                                                        | U-0               | U-0              | U-0                                     | U-0                | U-0      | U-0   |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------------------------------|--------------------|----------|-------|--|--|

| _                         | —                                                                                                          | —                 | —                | —                                       | —                  | —        | —     |  |  |

| bit 15                    |                                                                                                            |                   |                  |                                         |                    |          | bit 8 |  |  |

|                           |                                                                                                            |                   |                  |                                         |                    |          |       |  |  |

| U-0                       | U-0                                                                                                        | U-0               | U-0              | R/C-0                                   | R/W-0              | U-0      | U-0   |  |  |

| _                         | —                                                                                                          | —                 | —                | IPL3 <sup>(2)</sup>                     | PSV <sup>(1)</sup> | —        | —     |  |  |

| bit 7                     |                                                                                                            |                   |                  |                                         | •                  | •        | bit 0 |  |  |

|                           |                                                                                                            |                   |                  |                                         |                    |          |       |  |  |

| Legend: C = Clearable bit |                                                                                                            |                   |                  |                                         |                    |          |       |  |  |

| R = Readab                | le bit                                                                                                     | W = Writable      | bit              | U = Unimplem                            | nented bit, read   | l as '0' |       |  |  |

| -n = Value a              | t POR                                                                                                      | '1' = Bit is set  |                  | '0' = Bit is cleared x = Bit is unknown |                    |          |       |  |  |

|                           |                                                                                                            |                   |                  |                                         |                    |          |       |  |  |

| bit 15-4                  | Unimplemen                                                                                                 | ted: Read as 'd   | )'               |                                         |                    |          |       |  |  |

| bit 3                     | IPL3: CPU In                                                                                               | terrupt Priority  | Level Status bi  | t <sup>(2)</sup>                        |                    |          |       |  |  |

|                           | 1 = CPU Inte                                                                                               | rrupt Priority Le | vel is greater t | han 7                                   |                    |          |       |  |  |

|                           |                                                                                                            | rrupt Priority Le | •                |                                         |                    |          |       |  |  |

| bit 1-0                   |                                                                                                            |                   |                  |                                         |                    |          |       |  |  |

|                           | -<br>-                                                                                                     | fan dha alaa si i |                  | ulaiala in madella                      |                    |          | -4:   |  |  |

|                           | See Register 3-2                                                                                           |                   |                  |                                         |                    | •        |       |  |  |

| 2: 1                      | 2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level. |                   |                  |                                         |                    |          |       |  |  |

Note: Bit 2 is described in Section 3.0 "CPU".

## REGISTER 8-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0                                                                  | U-0         | U-0                                      | U-0             | U-0               | U-0                   | U-0             | R/W-0  |  |  |  |  |

|----------------------------------------------------------------------|-------------|------------------------------------------|-----------------|-------------------|-----------------------|-----------------|--------|--|--|--|--|

| _                                                                    | —           | —                                        | —               | —                 | —                     | —               | HLVDIE |  |  |  |  |

| bit 15                                                               |             |                                          |                 |                   |                       |                 | bit 8  |  |  |  |  |

|                                                                      |             |                                          |                 |                   |                       |                 |        |  |  |  |  |

| U-0                                                                  | U-0         | U-0                                      | U-0             | U-0               | R/W-0                 | R/W-0           | U-0    |  |  |  |  |

|                                                                      |             | <u> </u>                                 |                 | —                 | U2ERIE <sup>(1)</sup> | U1ERIE          |        |  |  |  |  |

| bit 7                                                                |             |                                          |                 |                   |                       |                 | bit 0  |  |  |  |  |

|                                                                      |             |                                          |                 |                   |                       |                 |        |  |  |  |  |

| Legend:                                                              |             |                                          |                 |                   |                       |                 |        |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |             |                                          |                 |                   |                       |                 |        |  |  |  |  |

| -n = Value a                                                         | at POR      | '1' = Bit is set                         | t               | '0' = Bit is clea | ared                  | x = Bit is unkr | nown   |  |  |  |  |

|                                                                      |             |                                          |                 |                   |                       |                 |        |  |  |  |  |

| bit 15-9                                                             | Unimplemer  | nted: Read as '                          | 0'              |                   |                       |                 |        |  |  |  |  |

| bit 8                                                                | HLVDIE: Hig | h/Low-Voltage                            | Detect Interrup | ot Enable bit     |                       |                 |        |  |  |  |  |

|                                                                      |             | request is enat                          |                 |                   |                       |                 |        |  |  |  |  |

|                                                                      | •           | request is not e                         |                 |                   |                       |                 |        |  |  |  |  |

| bit 7-3                                                              | Unimplemer  | nted: Read as '                          | 0'              |                   |                       |                 |        |  |  |  |  |

| bit 2                                                                | U2ERIE: UA  | RT2 Error Inter                          | rupt Enable bit | (1)               |                       |                 |        |  |  |  |  |

|                                                                      |             | request is enat                          |                 |                   |                       |                 |        |  |  |  |  |

|                                                                      | •           | request is not e                         |                 |                   |                       |                 |        |  |  |  |  |

| bit 1                                                                |             | U1ERIE: UART1 Error Interrupt Enable bit |                 |                   |                       |                 |        |  |  |  |  |

|                                                                      |             | request is enab<br>request is not e      |                 |                   |                       |                 |        |  |  |  |  |

| bit 0                                                                |             | nted: Read as '                          |                 |                   |                       |                 |        |  |  |  |  |

|                                                                      |             |                                          | •               |                   |                       |                 |        |  |  |  |  |

Note 1: This bit is unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

### REGISTER 8-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0           | U-0       | U-0              | U-0 | U-0               | U-0              | U-0             | U-0     |

|---------------|-----------|------------------|-----|-------------------|------------------|-----------------|---------|

| _             | —         | —                | _   | —                 | —                | —               | —       |

| bit 15        |           |                  |     | -                 |                  |                 | bit 8   |

|               |           |                  |     |                   |                  |                 |         |

| U-0           | U-0       | U-0              | U-0 | U-0               | U-0              | U-0             | R/W-0   |

| —             | —         | —                | —   | —                 | —                | —               | ULPWUIE |

| bit 7         |           |                  |     |                   |                  |                 | bit 0   |

|               |           |                  |     |                   |                  |                 |         |

| Legend:       |           |                  |     |                   |                  |                 |         |

| R = Readable  | e bit     | W = Writable     | bit | U = Unimplem      | nented bit, read | l as '0'        |         |

| -n = Value at | POR       | '1' = Bit is set |     | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| <u>.</u>      |           |                  |     |                   |                  |                 |         |

| bit 15-1      | Unimpleme | nted: Read as '  | o'  |                   |                  |                 |         |

| L:1 0         |           |                  | A   |                   |                  |                 |         |

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable Bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

The following code sequence for a clock switch is recommended:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- 3. Write the new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0>, in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- 8. Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

### EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator se  | lection in WO |

|-------------------------------|---------------|

| ;OSCCONH (high byte) Unlock   | Sequence      |

| MOV #OSCCONH, w1              |               |

| MOV #0x78, w2                 |               |

| MOV #0x9A, w3                 |               |

| MOV.b w2, [w1]                |               |

| MOV.b w3, [w1]                |               |

| ;Set new oscillator selection | n             |

| MOV.b WREG, OSCCONH           |               |

| ;OSCCONL (low byte) unlock s  | equence       |

| MOV #OSCCONL, w1              |               |

| MOV #0x46, w2                 |               |

| MOV #0x57, w3                 |               |

| MOV.b w2, [w1]                |               |

| MOV.b w3, [w1]                |               |

| ;Start oscillator switch oper | ration        |

| BSET OSCCON,#0                |               |

|                               |               |

# 9.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24F16KL402 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIV bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT). Therefore, if the ROSEL bit is also not set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

# 10.2.1 SLEEP MODE

Sleep mode includes these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum, provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if any active module has selected the LPRC as its source, including the WDT, Timer1 and Timer3.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features, or peripherals, may continue to operate in Sleep mode. This includes items, such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- On any form of device Reset

- On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

## 10.2.2 IDLE MODE

Idle mode has these features:

- The CPU will stop executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.5 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is re-applied to the CPU. Instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

## 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

# 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O Ports, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, *"I/O Ports with Peripheral Pin Select (PPS)"* (DS39711). Note that the PIC24F16KL402 family devices do not support Peripheral Pin Select features.

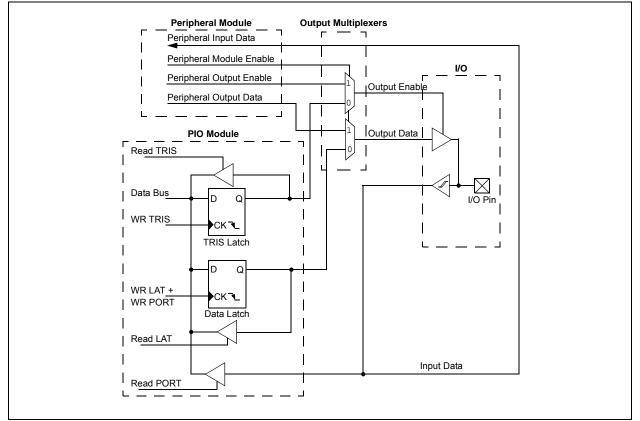

All of the device pins (except VDD and VSS) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

# 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LATx), read the latch. Writes to the Data Latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers, that are not valid for a particular device, will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless, regarded as a dedicated port because there is no other competing source of outputs.

## FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED I/O PORT STRUCTURE

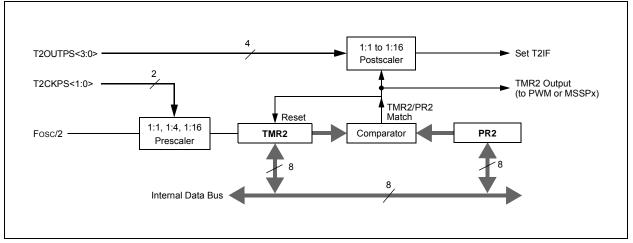

# 13.0 TIMER2 MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704).

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional Timer3 gate on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP modules

This module is controlled through the T2CON register (Register 13-1), which enables or disables the timer and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMR2 register

- · A write to the T2CON register

- Any device Reset (POR, BOR, MCLR or WDT Reset)

TMR2 is not cleared when T2CON is written.

A simplified block diagram of the module is shown in Figure 13-1.

## FIGURE 13-1: TIMER2 BLOCK DIAGRAM

'1' = Bit is set

## REGISTER 17-8: SSPxADD: MSSPx SLAVE ADDRESS/BAUD RATE GENERATOR REGISTER

| U-0          | U-0   | U-0            | U-0   | U-0          | U-0              | U-0      | U-0   |

|--------------|-------|----------------|-------|--------------|------------------|----------|-------|

| —            | _     | —              | —     | —            | —                | —        | —     |

| bit 15       |       |                |       |              |                  |          | bit 8 |

|              |       |                |       |              |                  |          |       |

| R/W-0        | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|              |       |                | ADD   | <7:0>        |                  |          |       |

| bit 7        |       |                |       |              |                  |          | bit 0 |

|              |       |                |       |              |                  |          |       |

| Legend:      |       |                |       |              |                  |          |       |

| R = Readable | e bit | W = Writable b | it    | U = Unimplem | nented bit, read | l as '0' |       |

'0' = Bit is cleared

bit 15-8 Unimplemented: Read as '0'

-n = Value at POR

bit 7-0 ADD<7:0>: Slave Address/Baud Rate Generator Value bits SPI Master and I<sup>2</sup>C<sup>™</sup> Master modes: Reloads value for Baud Rate Generator. Clock period is (([SPxADD] + 1) \*2)/Fosc. I<sup>2</sup>C Slave modes: Represents 7 or 8 bits of the slave address, depending on the addressing mode used: 7-Bit mode: Address is ADD<7:1>; ADD<0> is ignored. 10-Bit LSb mode: ADD<7:0> are the Least Significant bits of the address. 10-Bit MSb mode: ADD<2:1> are the two Most Significant bits of the address; ADD<7:3> are always '11110' as a specification requirement, ADD<0> is ignored.

# REGISTER 17-9: SSPxMSK: I<sup>2</sup>C<sup>™</sup> SLAVE ADDRESS MASK REGISTER

| U-0          | U-0       | U-0               | U-0   | U-0               | U-0             | U-0             | U-0   |

|--------------|-----------|-------------------|-------|-------------------|-----------------|-----------------|-------|

| _            | _         | —                 | _     | —                 | _               | —               | —     |

| bit 15       | ·         |                   |       |                   |                 | ·               | bit 8 |

| R/W-1        | R/W-1     | R/W-1             | R/W-1 | R/W-1             | R/W-1           | R/W-1           | R/W-1 |

|              |           |                   | MSK   | <7:0>(1)          |                 |                 |       |

| bit 7        |           |                   |       |                   |                 |                 | bit 0 |

| Legend:      |           |                   |       |                   |                 |                 |       |

| R = Readab   | ole bit   | W = Writable b    | bit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR    | '1' = Bit is set  |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |           |                   |       |                   |                 |                 |       |

| bit 15-8     | Unimpleme | ented: Read as '0 | '     |                   |                 |                 |       |

| 1.1.7.0      |           |                   |       | ··· (1)           |                 |                 |       |

bit 7-0 MSK<7:0>: Slave Address Mask Select bits<sup>(1)</sup>

1 = Masking of corresponding bit of SSPxADD is enabled

0 = Masking of corresponding bit of SSPxADD is disabled

**Note 1:** MSK0 is not used as a mask bit in 7-bit addressing.

x = Bit is unknown

| R/W-0                      | R-0                                                                                       | R/W-0                                                                                                                       | R/W-0                                 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|----------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|------------------|-----------------|-------|

| ADRC                       | EXTSAM                                                                                    | PUMPEN                                                                                                                      | SAMC4                                 | SAMC3             | SAMC2            | SAMC1           | SAMC0 |

| bit 15                     | ·                                                                                         | •                                                                                                                           |                                       |                   |                  |                 | bit 8 |

| U-0                        | U-0                                                                                       | R/W-0                                                                                                                       | R/W-0                                 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                            |                                                                                           | ADCS5                                                                                                                       | ADCS4                                 | ADCS3             | ADCS2            | ADCS1           | ADCS0 |

| bit 7                      |                                                                                           |                                                                                                                             |                                       |                   |                  |                 | bit ( |

| Legend:                    |                                                                                           |                                                                                                                             |                                       |                   |                  |                 |       |

| R = Readab                 | ole bit                                                                                   | W = Writable                                                                                                                | bit                                   | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value a               | at POR                                                                                    | '1' = Bit is set                                                                                                            |                                       | '0' = Bit is clea | ared             | x = Bit is unkr | iown  |

| bit 15<br>bit 14<br>bit 13 | 1 = A/D inten<br>0 = Clock der<br><b>EXTSAM:</b> Ext<br>1 = A/D is stil<br>0 = A/D is fin | onversion Cloc<br>nal RC clock<br>rived from syste<br>tended Samplin<br>Il sampling afte<br>ished sampling<br>parge Pump En | em clock<br>ng Time bit<br>r SAMP = 0 |                   |                  |                 |       |

|                            | 1 = Charge p                                                                              | ump for switch                                                                                                              | es is enabled                         |                   |                  |                 |       |

| bit 12-8                   | SAMC<4:0>:<br>11111 = 31 T<br>•<br>•<br>•<br>00001 = 1 TA                                 | Auto-Sample T<br>AD                                                                                                         | īme bits                              |                   |                  |                 |       |

| bit 7-6                    | Unimplemen                                                                                | ted: Maintain a                                                                                                             | <b>s</b> '0'                          |                   |                  |                 |       |

| bit 5-0                    | ADCS<5:0>:<br>11111 = 64 •<br>11110 = 63 •<br>•<br>•<br>00001 = 2 • T<br>00000 = Tcy      | Тсү                                                                                                                         | n Clock Select                        | bits              |                  |                 |       |

## REGISTER 19-3: AD1CON3: A/D CONTROL REGISTER 3

## 23.5 Program Verification and Code Protection

For all devices in the PIC24F16KL402 family, code protection for the Boot Segment is controlled by the BSS<2:0> Configuration bits and the General Segment by the Configuration bit, GSS0. These bits inhibit external reads and writes to the program memory space This has no direct effect in normal execution mode.

Write protection is controlled by bit, BWRP, for the Boot Segment and bit, GWRP, for the General Segment in the Configuration Word. When these bits are programmed to '0', internal write and erase operations to program memory are blocked.

# 23.6 In-Circuit Serial Programming

PIC24F16KL402 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGECx) and data (PGEDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 23.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3, MPLAB REAL ICE<sup>™</sup> or PICkit<sup>™</sup> 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx and PGEDx pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGECx, PGEDx and the pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

# 24.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 24.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 24.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 24.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

| Assembly<br>Mnemonic |               | Assembly Syntax     | Description                                | # of<br>Words | # of<br>Cycles            | Status Flags<br>Affected |

|----------------------|---------------|---------------------|--------------------------------------------|---------------|---------------------------|--------------------------|

| ADD                  | ADD           | f                   | f = f + WREG                               | 1             | 1                         | C, DC, N, OV, Z          |

|                      | ADD           | f,WREG              | WREG = f + WREG                            | 1             | 1                         | C, DC, N, OV, Z          |

|                      | ADD           | #lit10,Wn           | Wd = lit10 + Wd                            | 1             | 1                         | C, DC, N, OV, Z          |

|                      | ADD           | Wb,Ws,Wd            | Wd = Wb + Ws                               | 1             | 1                         | C, DC, N, OV, Z          |

|                      | ADD           | Wb,#lit5,Wd         | Wd = Wb + lit5                             | 1             | 1                         | C, DC, N, OV, Z          |

| ADDC                 | ADDC          | f                   | f = f + WREG + (C)                         | 1             | 1                         | C, DC, N, OV, Z          |

|                      | ADDC          | f,WREG              | WREG = f + WREG + (C)                      | 1             | 1                         | C, DC, N, OV, Z          |

|                      | ADDC          | #lit10,Wn           | Wd = lit10 + Wd + (C)                      | 1             | 1                         | C, DC, N, OV, Z          |

|                      | ADDC          | Wb,Ws,Wd            | Wd = Wb + Ws + (C)                         | 1             | 1                         | C, DC, N, OV, Z          |

|                      | ADDC          | Wb,#lit5,Wd         | Wd = Wb + Iit5 + (C)                       | 1             | 1                         | C, DC, N, OV, Z          |

| AND                  | AND           | f                   | f = f .AND. WREG                           | 1             | 1                         | N, Z                     |

|                      | AND           | f,WREG              | WREG = f .AND. WREG                        | 1             | 1                         | N, Z                     |

|                      | AND           | #lit10,Wn           | Wd = lit10 .AND. Wd                        | 1             | 1                         | N, Z                     |

|                      | AND           | Wb,Ws,Wd            | Wd = Wb .AND. Ws                           | 1             | 1                         | N, Z                     |

|                      | AND           | Wb,#lit5,Wd         | Wd = Wb .AND. lit5                         | 1             | 1                         | N, Z                     |

| ASR                  | ASR           | f                   | f = Arithmetic Right Shift f               | 1             | 1                         | C, N, OV, Z              |

|                      | ASR           | f,WREG              | WREG = Arithmetic Right Shift f            | 1             | 1                         | C, N, OV, Z              |

|                      | ASR           | Ws,Wd               | Wd = Arithmetic Right Shift Ws             | 1             | 1                         | C, N, OV, Z              |

|                      | ASR           | Wb,Wns,Wnd          | Wnd = Arithmetic Right Shift Wb by Wns     | 1             | 1                         | N, Z                     |

|                      | ASR           | Wb,#lit5,Wnd        | Wnd = Arithmetic Right Shift Wb by lit5    | 1             | 1                         | N, Z                     |

| BCLR                 | BCLR          | f,#bit4             | Bit Clear f                                | 1             | 1                         | None                     |

|                      | BCLR          | Ws,#bit4            | Bit Clear Ws                               | 1             | 1                         | None                     |

| BRA                  | BRA           | C,Expr              | Branch if Carry                            | 1             | 1 (2)                     | None                     |

|                      | BRA           | GE, Expr            | Branch if Greater than or Equal            | 1             | 1 (2)                     | None                     |

|                      | BRA           | GEU, Expr           | Branch if Unsigned Greater than or Equal   | 1             | 1 (2)                     | None                     |

|                      | BRA           | GT,Expr             | Branch if Greater than                     | 1             | 1 (2)                     | None                     |

|                      | BRA           | GTU, Expr           | Branch if Unsigned Greater than            | 1             | 1 (2)                     | None                     |

|                      | BRA           | LE,Expr             | Branch if Less than or Equal               | 1             | 1 (2)                     | None                     |

|                      | BRA           | LEU, Expr           | Branch if Unsigned Less than or Equal      | 1             | 1 (2)                     | None                     |

|                      | BRA           | LT,Expr             | Branch if Less than                        | 1             | 1 (2)                     | None                     |

|                      | BRA           | LTU, Expr           | Branch if Unsigned Less than               | 1             | 1 (2)                     | None                     |

|                      | BRA           | N,Expr              | Branch if Negative                         | 1             | 1 (2)                     | None                     |

|                      | BRA           | NC,Expr             | Branch if Not Carry                        | 1             | 1 (2)                     | None                     |

|                      | BRA           | NN, Expr            | Branch if Not Negative                     | 1             | 1 (2)                     | None                     |

|                      | BRA           | NOV, Expr           | Branch if Not Overflow                     | 1             | 1 (2)                     | None                     |

|                      | BRA           | NZ, Expr            | Branch if Not Zero                         | 1             | 1 (2)                     | None                     |

|                      | BRA           | OV, Expr            | Branch if Overflow                         | 1             | 1 (2)                     | None                     |

|                      | BRA           | Expr                | Branch Unconditionally                     | 1             | 2                         | None                     |

|                      | BRA           | Z,Expr              | Branch if Zero                             | 1             | 1 (2)                     | None                     |

|                      | BRA           | Wn                  | Computed Branch                            | 1             | 2                         | None                     |

| BSET                 | BSET          | f,#bit4             | Bit Set f                                  | 1             | 1                         | None                     |

| DOLI                 | BSET          |                     | Bit Set Ws                                 | 1             | 1                         | None                     |

| BSW                  | BSEI<br>BSW.C | Ws,#bit4<br>Ws,Wb   | Write C bit to Ws <wb></wb>                | 1             | 1                         | None                     |

| WGG                  | BSW.C         |                     | Write Z bit to Ws <wb></wb>                | 1             | 1                         |                          |

| PTC                  |               | Ws,Wb               |                                            | 1             | 1                         | None                     |

| BTG                  | BTG           | f,#bit4             | Bit Toggle f                               |               |                           | None                     |

| BTSC                 | BTG<br>BTSC   | Ws,#bit4<br>f,#bit4 | Bit Toggle Ws<br>Bit Test f, Skip if Clear | 1             | 1<br>1<br>(2 or 3)        | None<br>None             |

|                      | BTSC          | Ws,#bit4            | Bit Test Ws, Skip if Clear                 | 1             | (2 or 3)<br>1<br>(2 or 3) | None                     |

| TABLE 25-2: | <b>INSTRUCTION SET</b> | <b>OVERVIEW</b> |

|-------------|------------------------|-----------------|

|             |                        | •••             |

| DC CHARACTERISTICS |                        |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |