# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 17                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 512 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

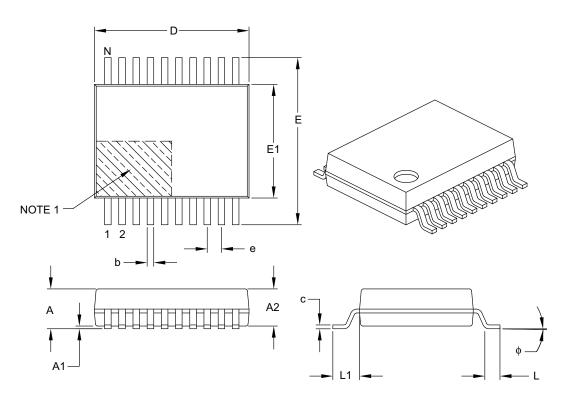

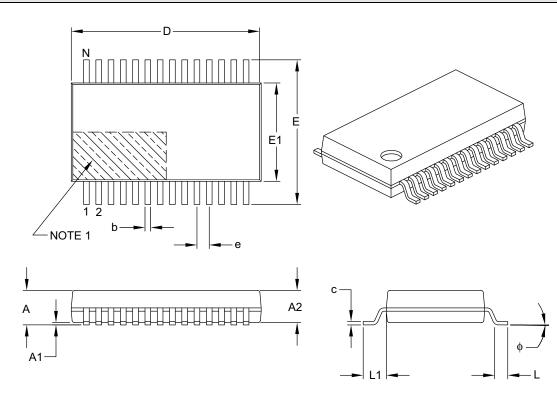

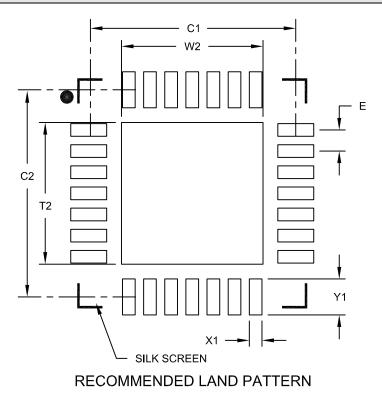

| Mounting Type              | Surface Mount                                                                 |

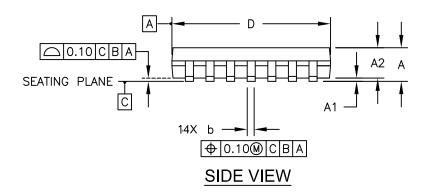

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

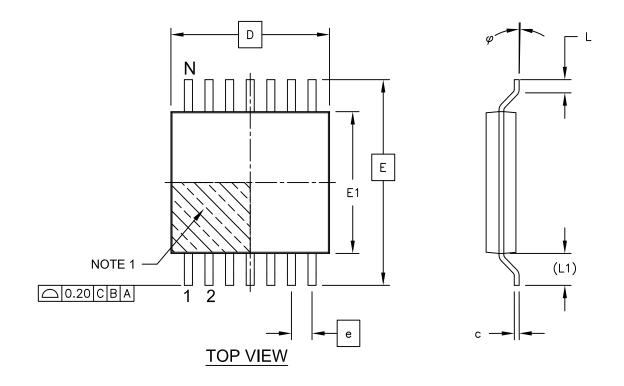

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl201t-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### TABLE 4-16: SYSTEM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | SBOREN | —      | —      | _      | CM     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 3100          |

| OSCTUN    | 0748 | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 074E | ROEN   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN | -      | HLSIDL | _      | —      | -      | _      | _      | VDIR    | BGVST | IRVST  | -     | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on configuration fuses and by type of Reset.

### TABLE 4-17: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7            | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|---------|--------|--------|-------|-------|------------------|-------|--------|--------|--------|--------|--------|--------|---------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | PGMONLY |        | _      | _     |       | —                | ERASE | NVMOP5 | NVMOP4 | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMKEY    | 0766 | _      | -      | -      | —       | —      |        | _     |       | NVM Key Register |       |        |        |        | 0000   |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-18: ULTRA LOW-POWER WAKE-UP REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|---------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ULPWCON   | 0768 | ULPEN  | _      | ULPSIDL |        | —      | _      |       | ULPSINK |       | _     |       | _     | _     |       | _     | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-19: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|---------|-------|-------|-------|--------|--------|--------|--------|------------|

| PMD1      | 0770 | _      | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     |       | SSP1MD  | U2MD  | U1MD  |       | —      | _      |        | ADC1MD | 0000       |

| PMD2      | 0772 | _      | —      | —      | _      | —      | —      | _     | -     | _       | _     | —     | _     | —      | CCP3MD | CCP2MD | CCP1MD | 0000       |

| PMD3      | 0774 | _      | _      | _      |        |        | CMPMD  | _     | -     | —       | _     | _     |       | —      | _      | SSP2MD | —      | 0000       |

| PMD4      | 0776 |        | _      | _      | _      | _      | _      | -     | —     | ULPWUMD |       | _     | EEMD  | REFOMD | —      | HLVDMD | _      | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS30001037C-page 42

### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

| // C example using MPLAB C30                                                                  |                                                                                     |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| <pre>intattribute ((space(auto_psv))) progAddr = &amp;progAddr<br/>unsigned int offset;</pre> | // Global variable located in Pgm Memory $% \mathcal{T}_{\mathcal{T}}$              |

| //Set up pointer to the first memory location to be written                                   |                                                                                     |

| <pre>TBLPAG =builtin_tblpage(&amp;progAddr); offset = &amp;progAddr &amp; 0xFFFF;</pre>       | // Initialize PM Page Boundary SFR<br>// Initialize lower word of address           |

| <pre>builtin_tblwtl(offset, 0x0000);</pre>                                                    | <pre>// Set base address of erase block // with dummy latch write</pre>             |

| NVMCON = $0 \times 4058$ ;                                                                    | // Initialize NVMCON                                                                |

| <pre>asm("DISI #5");</pre>                                                                    | <pre>// Block all interrupts for next 5 // instructions</pre>                       |

| builtin_write_NVM();                                                                          | <pre>// Instructions // C30 function to perform unlock // sequence and set WR</pre> |

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| MOV #0x4004, W0 ;                                                     |       |

|-----------------------------------------------------------------------|-------|

|                                                                       |       |

| MOV W0, NVMCON ; Initialize NVMCON                                    |       |

| ; Set up a pointer to the first program memory location to be written |       |

| ; program memory selected, and writes enabled                         |       |

| MOV #0x0000, W0 ;                                                     |       |

| MOV W0, TBLPAG ; Initialize PM Page Boundary SFR                      |       |

| MOV #0x6000, W0 ; An example program memory addre                     | SS    |

| ; Perform the TBLWT instructions to write the latches                 |       |

| ; 0th_program_word                                                    |       |

| MOV #LOW_WORD_0, W2 ;                                                 |       |

| MOV #HIGH_BYTE_0, W3 ;                                                |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      | latch |

| TBLWTH W3, [W0++] ; Write PM high byte into program                   | latch |

| ; lst_program_word                                                    |       |

| MOV #LOW_WORD_1, W2 ;                                                 |       |

| MOV #HIGH_BYTE_1, W3 ;                                                |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      | latch |

| TBLWTH W3, [W0++] ; Write PM high byte into program                   | latch |

| ; 2nd_program_word                                                    |       |

| MOV #LOW_WORD_2, W2 ;                                                 |       |

| MOV #HIGH_BYTE_2, W3 ;                                                |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      | latch |

| TBLWTH W3, [W0++] ; Write PM high byte into program                   | latch |

| •                                                                     |       |

| •                                                                     |       |

|                                                                       |       |

| ; 32nd_program_word                                                   |       |

| MOV #LOW_WORD_31, W2 ;                                                |       |

| MOV #HIGH_BYTE_31, W3 ;                                               |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      |       |

| TBLWTH W3, [W0]   ; Write PM high byte into program                   | latch |

# 7.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 7-3. Note that the System Reset Signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| Reset Type         | Clock Source | SYSRST Delay | System Clock<br>Delay | Notes      |

|--------------------|--------------|--------------|-----------------------|------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT | —                     | 1, 2       |

|                    | FRC, FRCDIV  | TPOR + TPWRT | TFRC                  | 1, 2, 3    |

|                    | LPRC         | TPOR + TPWRT | TLPRC                 | 1, 2, 3    |

|                    | ECPLL        | TPOR + TPWRT | Тьоск                 | 1, 2, 4    |

|                    | FRCPLL       | TPOR + TPWRT | TFRC + TLOCK          | 1, 2, 3, 4 |

|                    | XT, HS, SOSC | TPOR+ TPWRT  | Тоѕт                  | 1, 2, 5    |

|                    | XTPLL, HSPLL | TPOR + TPWRT | TOST + TLOCK          | 1, 2, 4, 5 |

| BOR                | EC           | TPWRT        | —                     | 2          |

|                    | FRC, FRCDIV  | TPWRT        | TFRC                  | 2, 3       |

|                    | LPRC         | TPWRT        | TLPRC                 | 2, 3       |

|                    | ECPLL        | TPWRT        | Тьоск                 | 2, 4       |

|                    | FRCPLL       | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

|                    | XT, HS, SOSC | TPWRT        | Тоѕт                  | 2, 5       |

|                    | XTPLL, HSPLL | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

| All Others         | Any Clock    | _            | —                     | None       |

## TABLE 7-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

Note 1: TPOR = Power-on Reset delay.

2: TPWRT = 64 ms nominal if the Power-up Timer is enabled; otherwise, it is zero.

3: TFRC and TLPRC = RC oscillator start-up times.

**4:** TLOCK = PLL lock time.

**5:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

**6:** If Two-Speed Start-up is enabled, regardless of the primary oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

Note: For detailed operating frequency and timing specifications, see Section 26.0 "Electrical Characteristics".

## REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0          | U-0               | U-0               | U-0                                                 | U-0                 | U-0                | U-0              | U-0          |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-----------------------------------------------------|---------------------|--------------------|------------------|--------------|--|--|--|--|--|--|

| _            | —                 | —                 | —                                                   | —                   | —                  | —                | —            |  |  |  |  |  |  |

| bit 15       |                   |                   |                                                     |                     |                    |                  | bit 8        |  |  |  |  |  |  |

|              |                   |                   |                                                     |                     |                    |                  |              |  |  |  |  |  |  |

| U-0          | U-0               | U-0               | U-0                                                 | R/C-0               | R/W-0              | U-0              | U-0          |  |  |  |  |  |  |

| _            | —                 | —                 | —                                                   | IPL3 <sup>(2)</sup> | PSV <sup>(1)</sup> | —                | —            |  |  |  |  |  |  |

| bit 7        |                   |                   |                                                     |                     | •                  | •                | bit 0        |  |  |  |  |  |  |

|              |                   |                   |                                                     |                     |                    |                  |              |  |  |  |  |  |  |

| Legend:      |                   | C = Clearable     | bit                                                 |                     |                    |                  |              |  |  |  |  |  |  |

| R = Readab   | le bit            | W = Writable      | / = Writable bit U = Unimplemented bit, read as '0' |                     |                    |                  |              |  |  |  |  |  |  |

| -n = Value a | t POR             | '1' = Bit is set  |                                                     | '0' = Bit is clea   | ared               | x = Bit is unkr  | iown         |  |  |  |  |  |  |

|              |                   |                   |                                                     |                     |                    |                  |              |  |  |  |  |  |  |

| bit 15-4     | Unimplemen        | ted: Read as 'd   | )'                                                  |                     |                    |                  |              |  |  |  |  |  |  |

| bit 3        | IPL3: CPU In      | terrupt Priority  | Level Status bi                                     | t <sup>(2)</sup>    |                    |                  |              |  |  |  |  |  |  |

|              | 1 = CPU Inte      | rrupt Priority Le | vel is greater t                                    | han 7               |                    |                  |              |  |  |  |  |  |  |

|              |                   | rrupt Priority Le | •                                                   |                     |                    |                  |              |  |  |  |  |  |  |

| bit 1-0      | Unimplemen        | ted: Read as 'o   | )'                                                  |                     |                    |                  |              |  |  |  |  |  |  |

|              | -<br>-            | fan dha alaa si i |                                                     | ubiele is used du   |                    |                  | -4:          |  |  |  |  |  |  |

|              | See Register 3-2  |                   |                                                     |                     |                    | •                |              |  |  |  |  |  |  |

| <b>2:</b> T  | he IPL3 bit is co | incatenated with  | n the IPL<2:0>                                      | DITS (SR<7:5>)      | ) to form the CF   | 20 Interrupt Pri | ority Level. |  |  |  |  |  |  |

Note: Bit 2 is described in Section 3.0 "CPU".

# 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Oscillator Configuration, refer to the "dsPIC33/PIC24 Family Reference Manual", "Oscillator with 500 kHz Low-Power FRC" (DS39726).

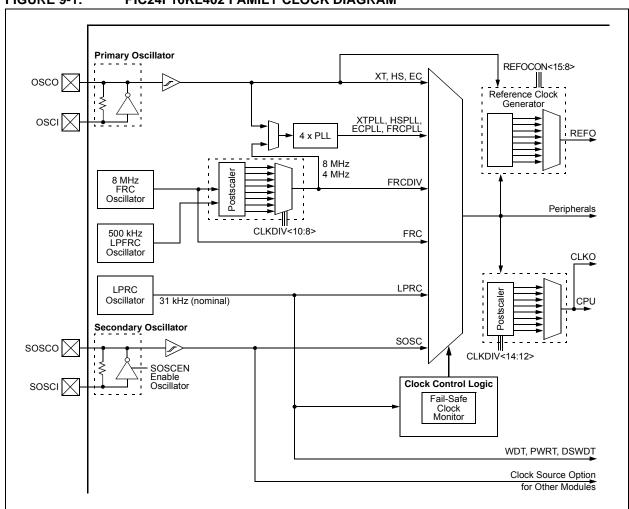

The oscillator system for the PIC24F16KL402 family of devices has the following features:

- A total of five external and internal oscillator options as clock sources, providing 11 different clock modes.

- On-chip, 4x Phase Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources.

- Software-controllable switching between various clock sources.

- Software-controllable postscaler for selective clocking of CPU for system power savings.

- System frequency range declaration bits for EC mode. When using an external clock source, the current consumption is reduced by setting the declaration bits to the expected frequency range.

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown.

A simplified diagram of the oscillator system is shown in Figure 9-1.

## FIGURE 9-1: PIC24F16KL402 FAMILY CLOCK DIAGRAM

The following code sequence for a clock switch is recommended:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- 3. Write the new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0>, in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- 8. Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

#### EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator se  | lection in WO |

|-------------------------------|---------------|

| ;OSCCONH (high byte) Unlock   | Sequence      |

| MOV #OSCCONH, w1              |               |

| MOV #0x78, w2                 |               |

| MOV #0x9A, w3                 |               |

| MOV.b w2, [w1]                |               |

| MOV.b w3, [w1]                |               |

| ;Set new oscillator selection | n             |

| MOV.b WREG, OSCCONH           |               |

| ;OSCCONL (low byte) unlock s  | equence       |

| MOV #OSCCONL, w1              |               |

| MOV #0x46, w2                 |               |

| MOV #0x57, w3                 |               |

| MOV.b w2, [w1]                |               |

| MOV.b w3, [w1]                |               |

| ;Start oscillator switch oper | ration        |

| BSET OSCCON,#0                |               |

|                               |               |

# 9.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24F16KL402 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIV bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT). Therefore, if the ROSEL bit is also not set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

| R/W-0        | U-0            | R/W-0            | U-0             | U-0               | U-0              | U-0                | R/W-0   |  |  |  |

|--------------|----------------|------------------|-----------------|-------------------|------------------|--------------------|---------|--|--|--|

| ULPEN        |                | ULPSIDL          | _               | —                 | _                |                    | ULPSINK |  |  |  |

| bit 15       |                |                  |                 |                   |                  |                    | bit 8   |  |  |  |

|              |                |                  |                 |                   |                  |                    |         |  |  |  |

| U-0          | U-0            | U-0              | U-0             | U-0               | U-0              | U-0                | U-0     |  |  |  |

|              |                | —                | —               |                   | —                |                    |         |  |  |  |

| bit 7        |                |                  |                 |                   |                  |                    | bit 0   |  |  |  |

| l            |                |                  |                 |                   |                  |                    | 1       |  |  |  |

| Legend:      |                |                  |                 |                   |                  |                    |         |  |  |  |

| R = Readat   | ole bit        | W = Writable     | bit             | U = Unimplem      | nented bit, read | d as '0'           |         |  |  |  |

| -n = Value a | at POR         | '1' = Bit is set |                 | '0' = Bit is clea | ared             | x = Bit is unknown |         |  |  |  |

|              |                |                  |                 |                   |                  |                    |         |  |  |  |

| bit 15       | ULPEN: ULP     | WU Module En     | able bit        |                   |                  |                    |         |  |  |  |

|              | 1 = Module is  |                  |                 |                   |                  |                    |         |  |  |  |

|              | 0 = Module is  | disabled         |                 |                   |                  |                    |         |  |  |  |

| bit 14       | Unimplemen     | ted: Read as '   | כ'              |                   |                  |                    |         |  |  |  |

| bit 13       | ULPSIDL: UL    | PWU Stop in I    | dle Select bit  |                   |                  |                    |         |  |  |  |

|              |                |                  |                 | ne device enters  | s Idle mode      |                    |         |  |  |  |

|              | 0 = Continues  | s module opera   | tion in Idle mo | de                |                  |                    |         |  |  |  |

| bit 12-9     | Unimplemen     | ted: Read as '   | כ'              |                   |                  |                    |         |  |  |  |

| bit 8        | ULPSINK: UL    | _PWU Current     | Sink Enable bi  | t                 |                  |                    |         |  |  |  |

|              | 1 = Current si | ink is enabled   |                 |                   |                  |                    |         |  |  |  |

|              | 0 = Current si | ink is disabled  |                 |                   |                  |                    |         |  |  |  |

| bit 7-0      | Unimplemen     | ted: Read as '   | כ'              |                   |                  |                    |         |  |  |  |

|              |                |                  |                 |                   |                  |                    |         |  |  |  |

## REGISTER 10-1: ULPWCON: ULPWU CONTROL REGISTER

REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0                | U-0                            | R/W-0                            | U-0              | U-0               | U-0              | R/W-0                 | R/W-0                 |

|----------------------|--------------------------------|----------------------------------|------------------|-------------------|------------------|-----------------------|-----------------------|

| TON                  | _                              | TSIDL                            | _                | _                 | _                | T1ECS1 <sup>(1)</sup> | T1ECS0 <sup>(1)</sup> |

| bit 15               |                                | I                                |                  |                   |                  | •                     | bit 8                 |

|                      |                                |                                  |                  |                   |                  |                       |                       |

| U-0                  | R/W-0                          | R/W-0                            | R/W-0            | U-0               | R/W-0            | R/W-0                 | U-0                   |

| _                    | TGATE                          | TCKPS1                           | TCKPS0           | —                 | TSYNC            | TCS                   | —                     |

| bit 7                |                                |                                  |                  |                   |                  |                       | bit (                 |

| Legend:              |                                |                                  |                  |                   |                  |                       |                       |

| R = Readabl          | e bit                          | W = Writable                     | bit              | U = Unimplerr     | nented bit. read | d as '0'              |                       |

| -n = Value at        | POR                            | '1' = Bit is set                 |                  | '0' = Bit is clea |                  | x = Bit is unkr       | iown                  |

|                      |                                |                                  |                  |                   |                  |                       |                       |

| bit 15               | TON: Timer1                    | On bit                           |                  |                   |                  |                       |                       |

|                      | 1 = Starts 16-                 |                                  |                  |                   |                  |                       |                       |

|                      | 0 = Stops 16-                  | bit Timer1                       |                  |                   |                  |                       |                       |

| bit 14               | Unimplement                    | ted: Read as '                   | )'               |                   |                  |                       |                       |

| bit 13               |                                | 1 Stop in Idle N                 |                  |                   |                  |                       |                       |

|                      |                                |                                  |                  | device enters Idl | e mode           |                       |                       |

| h:+ 40 40            |                                | module opera                     |                  | de                |                  |                       |                       |

| bit 12-10<br>bit 9-8 | -                              | ted: Read as '<br>: Timer1 Exten |                  | La at hita(1)     |                  |                       |                       |

| DIL 9-0              | 11 = Reserve                   |                                  |                  | lect bits ?       |                  |                       |                       |

|                      |                                | ises the LPRC                    | as the clock s   | ource             |                  |                       |                       |

|                      |                                | ises the extern                  |                  |                   |                  |                       |                       |

|                      | 00 <b>= Timer1</b> u           | ises the Secon                   | dary Oscillato   | r (SOSC) as the   | clock source     |                       |                       |

| bit 7                | Unimplement                    | ted: Read as '                   | י'               |                   |                  |                       |                       |

| bit 6                | TGATE: Time                    | r1 Gated Time                    | Accumulation     | Enable bit        |                  |                       |                       |

|                      | When TCS =                     | -                                |                  |                   |                  |                       |                       |

|                      | This bit is igno<br>When TCS = |                                  |                  |                   |                  |                       |                       |

|                      |                                | <u>u.</u><br>ne accumulatio      | n is enabled     |                   |                  |                       |                       |

|                      |                                | ne accumulatio                   |                  |                   |                  |                       |                       |

| bit 5-4              | TCKPS<1:0>                     | : Timer1 Input                   | Clock Prescal    | e Select bits     |                  |                       |                       |

|                      | 11 <b>= 1:256</b>              |                                  |                  |                   |                  |                       |                       |

|                      | 10 = 1:64                      |                                  |                  |                   |                  |                       |                       |

|                      | 01 = 1:8<br>00 = 1:1           |                                  |                  |                   |                  |                       |                       |

| bit 3                |                                | ted: Read as '                   | )'               |                   |                  |                       |                       |

| bit 2                | -                              |                                  |                  | hronization Sele  | ect bit          |                       |                       |

|                      | When TCS =                     |                                  | , ,              |                   |                  |                       |                       |

|                      | 1 = Synchron                   | nizes external (                 |                  |                   |                  |                       |                       |

|                      |                                | t synchronize e                  | external clock i | input             |                  |                       |                       |

|                      | When TCS =                     |                                  |                  |                   |                  |                       |                       |

| hit 1                | This bit is igno               | Clock Source S                   | Soloct bit       |                   |                  |                       |                       |

| bit 1                |                                | ock source is s                  |                  | ECS<1.05          |                  |                       |                       |

|                      |                                | clock (Fosc/2)                   |                  |                   |                  |                       |                       |

|                      |                                |                                  |                  |                   |                  |                       |                       |

| bit 0                | Unimplement                    | ted: Read as '                   | כ'               |                   |                  |                       |                       |

| U-0           | U-0            | U-0                                                      | U-0                            | U-0               | U-0              | U-0             | U-0    |

|---------------|----------------|----------------------------------------------------------|--------------------------------|-------------------|------------------|-----------------|--------|

|               | —              | _                                                        | —                              |                   | —                | _               | —      |

| bit 15        |                |                                                          |                                |                   |                  |                 | bit    |

|               |                |                                                          |                                |                   |                  |                 |        |

| R/W-0         | R/W-0          | R/W-0                                                    | R/W-0                          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| ECCPASE       | ECCPAS2        | ECCPAS1                                                  | ECCPAS0                        | PSSAC1            | PSSAC0           | PSSBD1          | PSSBD0 |

| bit 7         |                |                                                          |                                |                   |                  |                 | bit    |

| Legend:       |                |                                                          |                                |                   |                  |                 |        |

| R = Readable  | a hit          | W = Writable                                             | hit                            | II = I Inimplen   | nented bit, read | as '0'          |        |

| -n = Value at |                | '1' = Bit is set                                         |                                | '0' = Bit is clea |                  | x = Bit is unkr |        |

|               |                |                                                          |                                |                   |                  |                 |        |

| bit 15-8      | Unimplemen     | ted: Read as                                             | 0'                             |                   |                  |                 |        |

| bit 7         | -              |                                                          | nutdown Event                  | Status bit        |                  |                 |        |

|               | 1 = A shutdow  | wn event has c                                           | ccurred; ECCP                  | outputs are in    | a shutdown sta   | ate             |        |

|               | 0 = ECCP ou    | tputs are opera                                          | ating                          |                   |                  |                 |        |

| bit 6-4       |                |                                                          | to-Shutdown So                 |                   |                  |                 |        |

|               |                |                                                          | ther C1OUT or<br>2OUT comparat |                   |                  |                 |        |

|               | 101 = VIL ON   | FLT0 pin or C2                                           | IOUT comparat                  | tor output is hig | ih               |                 |        |

|               | 100 = VIL on   | FLT0 pin                                                 |                                | 5                 | ,                |                 |        |

|               |                | C1OUT or C20                                             |                                |                   |                  |                 |        |

|               |                | T comparator o<br>T comparator o                         |                                |                   |                  |                 |        |

|               |                | hutdown is dis                                           |                                |                   |                  |                 |        |

| bit 3-2       | PSSAC<1:0>     | : P1A and P10                                            | C Pins Shutdow                 | n State Contro    | l bits           |                 |        |

|               |                | l P1C pins tri-s                                         |                                |                   |                  |                 |        |

|               |                | ns, P1A and P <sup>-</sup><br>ns, P1A and P <sup>-</sup> |                                |                   |                  |                 |        |

| bit 1-0       | •              |                                                          | D Pins Shutdow                 | in State Control  | l bite           |                 |        |

|               |                | P1D pins tri-s                                           |                                |                   | i bits           |                 |        |

|               |                | ns, P1B and P                                            |                                |                   |                  |                 |        |

|               |                |                                                          |                                |                   |                  |                 |        |

|               | 00 = Drive pir | ns, P1B and P                                            | 1D, to '0'                     |                   |                  |                 |        |

**Note 1:** The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.

2: Writing to the ECCPASE bit is disabled while an auto-shutdown condition persists.

**3:** Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

| U-0<br>U-0<br>W = Writable<br>'1' = Bit is set<br>nented: Read as '<br>0>: Complementa<br>plementary output<br>ring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele | t<br>'o'<br>ary Mode Output<br>ut assignment<br>ected as the com<br>ected as the com                                                                                                   | '0' = Bit is clear<br>Assignment S<br>is disabled; th<br>plementary ou                                                                                                                                                               | teering bits<br>he STR <d:a><br/>itput pair</d:a>                                                                                                                                                                                                                                                                    | x = Bit is unkn                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W = Writable<br>'1' = Bit is se<br>nented: Read as '<br>0>: Complementa<br>plementary output<br>ring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                | strasync<br>bit<br>t<br>'o'<br>ury Mode Output<br>ut assignment<br>ected as the com<br>ected as the com                                                                                | STRD<br>U = Unimplen<br>'0' = Bit is clea<br>Assignment S<br>is disabled; the<br>plementary out                                                                                                                                      | STRC<br>nented bit, read<br>ared<br>iteering bits<br>ne STR <d:a></d:a>                                                                                                                                                                                                                                              | STRB<br>d as '0'<br>x = Bit is unkn                                                                                                                                                                                                                                                                                                                      | R/W-1<br>STRA<br>bit C                                                                                                                                                                                                                                                                                                                |

| W = Writable<br>'1' = Bit is se<br>nented: Read as '<br>0>: Complementa<br>plementary output<br>ring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                | strasync<br>bit<br>t<br>'o'<br>ury Mode Output<br>ut assignment<br>ected as the com<br>ected as the com                                                                                | STRD<br>U = Unimplen<br>'0' = Bit is clea<br>Assignment S<br>is disabled; the<br>plementary out                                                                                                                                      | STRC<br>nented bit, read<br>ared<br>iteering bits<br>ne STR <d:a></d:a>                                                                                                                                                                                                                                              | STRB<br>d as '0'<br>x = Bit is unkn                                                                                                                                                                                                                                                                                                                      | STRA<br>bit (<br>own                                                                                                                                                                                                                                                                                                                  |

| W = Writable<br>'1' = Bit is se<br>nented: Read as '<br>0>: Complementa<br>plementary output<br>ring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                | bit<br>t<br>'0'<br>ary Mode Output<br>ut assignment i<br>ected as the com                                                                                                              | U = Unimplen<br>'0' = Bit is clea<br>Assignment S<br>is disabled; the<br>plementary ou                                                                                                                                               | nented bit, read<br>ared<br>teering bits<br>ne STR <d:a></d:a>                                                                                                                                                                                                                                                       | d as '0'<br>x = Bit is unkn                                                                                                                                                                                                                                                                                                                              | bit (<br>own                                                                                                                                                                                                                                                                                                                          |

| '1' = Bit is se<br><b>nented:</b> Read as<br><b>D&gt;:</b> Complementa<br>plementary output<br>ring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                 | t<br>'o'<br>ary Mode Output<br>ut assignment<br>ected as the com<br>ected as the com                                                                                                   | '0' = Bit is clear<br>Assignment S<br>is disabled; th<br>plementary ou                                                                                                                                                               | ared<br>iteering bits<br>ne STR <d:a><br/>itput pair</d:a>                                                                                                                                                                                                                                                           | x = Bit is unkn                                                                                                                                                                                                                                                                                                                                          | own                                                                                                                                                                                                                                                                                                                                   |

| '1' = Bit is se<br><b>nented:</b> Read as<br><b>D&gt;:</b> Complementa<br>plementary output<br>ring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                 | t<br>'o'<br>ary Mode Output<br>ut assignment<br>ected as the com<br>ected as the com                                                                                                   | '0' = Bit is clear<br>Assignment S<br>is disabled; th<br>plementary ou                                                                                                                                                               | ared<br>iteering bits<br>ne STR <d:a><br/>itput pair</d:a>                                                                                                                                                                                                                                                           | x = Bit is unkn                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                       |

| '1' = Bit is se<br><b>nented:</b> Read as<br><b>D&gt;:</b> Complementa<br>plementary output<br>ring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                 | t<br>'o'<br>ary Mode Output<br>ut assignment<br>ected as the com<br>ected as the com                                                                                                   | '0' = Bit is clear<br>Assignment S<br>is disabled; th<br>plementary ou                                                                                                                                                               | ared<br>iteering bits<br>ne STR <d:a><br/>itput pair</d:a>                                                                                                                                                                                                                                                           | x = Bit is unkn                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                       |

| nented: Read as<br><b>0&gt;:</b> Complementa<br>plementary outpu-<br>ring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                                           | <sup>'0'</sup><br>ary Mode Output<br>ut assignment i<br>ected as the com<br>ected as the com                                                                                           | '0' = Bit is clear<br>Assignment S<br>is disabled; th<br>plementary ou                                                                                                                                                               | ared<br>iteering bits<br>ne STR <d:a><br/>itput pair</d:a>                                                                                                                                                                                                                                                           | x = Bit is unkn                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                       |

| 0>: Complementa<br>plementary outpuring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                                                                             | try Mode Output<br>at assignment i<br>acted as the com<br>acted as the com                                                                                                             | : Assignment S<br>is disabled; th<br>nplementary ou                                                                                                                                                                                  | teering bits<br>he STR <d:a><br/>itput pair</d:a>                                                                                                                                                                                                                                                                    | bits are used                                                                                                                                                                                                                                                                                                                                            | to determine                                                                                                                                                                                                                                                                                                                          |

| 0>: Complementa<br>plementary outpuring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                                                                             | try Mode Output<br>at assignment i<br>acted as the com<br>acted as the com                                                                                                             | is disabled; th                                                                                                                                                                                                                      | ne STR <d:a></d:a>                                                                                                                                                                                                                                                                                                   | bits are used                                                                                                                                                                                                                                                                                                                                            | to determine                                                                                                                                                                                                                                                                                                                          |

| plementary outputring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                                                                                               | ut assignment i<br>ected as the com<br>ected as the com                                                                                                                                | is disabled; th                                                                                                                                                                                                                      | ne STR <d:a></d:a>                                                                                                                                                                                                                                                                                                   | bits are used                                                                                                                                                                                                                                                                                                                                            | to determine                                                                                                                                                                                                                                                                                                                          |

| ring mode<br>and P1B are sele<br>and P1C are sele<br>and P1D are sele                                                                                                                | ected as the com<br>ected as the com                                                                                                                                                   | plementary ou                                                                                                                                                                                                                        | Itput pair                                                                                                                                                                                                                                                                                                           | bits are used                                                                                                                                                                                                                                                                                                                                            | to determine                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                      |                                                                                                                                                                                        | plementary ou                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                       |

| nented: Read as                                                                                                                                                                      | '0'                                                                                                                                                                                    |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                       |

| : Steering Sync b                                                                                                                                                                    |                                                                                                                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                       |

| ut steering update<br>ut steering update                                                                                                                                             |                                                                                                                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                      | le boundary                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                       |

| eering Enable D b                                                                                                                                                                    | it                                                                                                                                                                                     |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                      |                                                                                                                                                                                        | olarity control                                                                                                                                                                                                                      | from CCP1M<                                                                                                                                                                                                                                                                                                          | 1:0>                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                       |

| eering Enable C b                                                                                                                                                                    | bit                                                                                                                                                                                    |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                      | •                                                                                                                                                                                      | olarity control                                                                                                                                                                                                                      | from CCP1M<                                                                                                                                                                                                                                                                                                          | 1:0>                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                       |