Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 8KB (2.75K x 24)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 20-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl301-e-p |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                  | Pin Number    | •                        |     |        |                                                                               |

|----------|----------------------------------|---------------|--------------------------|-----|--------|-------------------------------------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 14-Pin<br>PDIP/<br>TSSOP | I/O | Buffer | Description                                                                   |

| CVREF    | 17                               | 14            | 11                       | Ι   | ANA    | Comparator Voltage Reference Output                                           |

| CVREF+   | 2                                | 19            | 2                        | I   | ANA    | Comparator Reference Positive Input Voltage                                   |

| CVREF-   | 3                                | 20            | 3                        | I   | ANA    | Comparator Reference Negative Input Voltage                                   |

| HLVDIN   | 15                               | 12            | 6                        | I   | ST     | High/Low-Voltage Detect Input                                                 |

| INT0     | 11                               | 8             | 12                       | I   | ST     | Interrupt 0 Input                                                             |

| INT1     | 17                               | 14            | 11                       | I   | ST     | Interrupt 1 Input                                                             |

| INT2     | 14                               | 11            | 10                       | I   | ST     | Interrupt 2 Input                                                             |

| MCLR     | 1                                | 18            | 1                        | I   | ST     | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |

| OSCI     | 7                                | 4             | 4                        | I   | ANA    | Main Oscillator Input                                                         |

| OSCO     | 8                                | 5             | 5                        | 0   | ANA    | Main Oscillator Output                                                        |

| PGEC1    | 5                                | 2             | _                        | I/O | ST     | ICSP™ Clock 1                                                                 |

| PCED1    | 4                                | 1             | _                        | I/O | ST     | ICSP Data 1                                                                   |

| PGEC2    | 2                                | 19            | 2                        | I/O | ST     | ICSP Clock 2                                                                  |

| PGED2    | 3                                | 20            | 3                        | I/O | ST     | ICSP Data 2                                                                   |

| PGEC3    | 10                               | 7             | 7                        | I/O | ST     | ICSP Clock 3                                                                  |

| PGED3    | 9                                | 6             | 6                        | I/O | ST     | ICSP Data 3                                                                   |

| RA0      | 2                                | 19            | 2                        | I/O | ST     | PORTA Pins                                                                    |

| RA1      | 3                                | 20            | 3                        | I/O | ST     | 7                                                                             |

| RA2      | 7                                | 4             | 4                        | I/O | ST     | 7                                                                             |

| RA3      | 8                                | 5             | 5                        | I/O | ST     |                                                                               |

| RA4      | 10                               | 7             | 7                        | I/O | ST     | 7                                                                             |

| RA5      | 1                                | 18            | 1                        | I   | ST     | 7                                                                             |

| RA6      | 14                               | 11            | 10                       | I/O | ST     | 7                                                                             |

| RB0      | 4                                | 1             |                          | I/O | ST     | PORTB Pins                                                                    |

| RB1      | 5                                | 2             |                          | I/O | ST     |                                                                               |

| RB2      | 6                                | 3             |                          | I/O | ST     |                                                                               |

| RB4      | 9                                | 6             | 6                        | I/O | ST     |                                                                               |

| RB7      | 11                               | 8             | —                        | I/O | ST     |                                                                               |

| RB8      | 12                               | 9             | 8                        | I/O | ST     | 1                                                                             |

| RB9      | 13                               | 10            | 9                        | I/O | ST     |                                                                               |

| RB12     | 15                               | 12            | _                        | I/O | ST     |                                                                               |

| RB13     | 16                               | 13            | —                        | I/O | ST     | 1                                                                             |

| RB14     | 17                               | 14            | 11                       | I/O | ST     | 1                                                                             |

| RB15     | 18                               | 15            | 12                       | I/O | ST     | 1                                                                             |

| REFO     | 18                               | 15            | 12                       | 0   | —      | Reference Clock Output                                                        |

#### PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS (CONTINUED) **TABLE 1-5:**

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

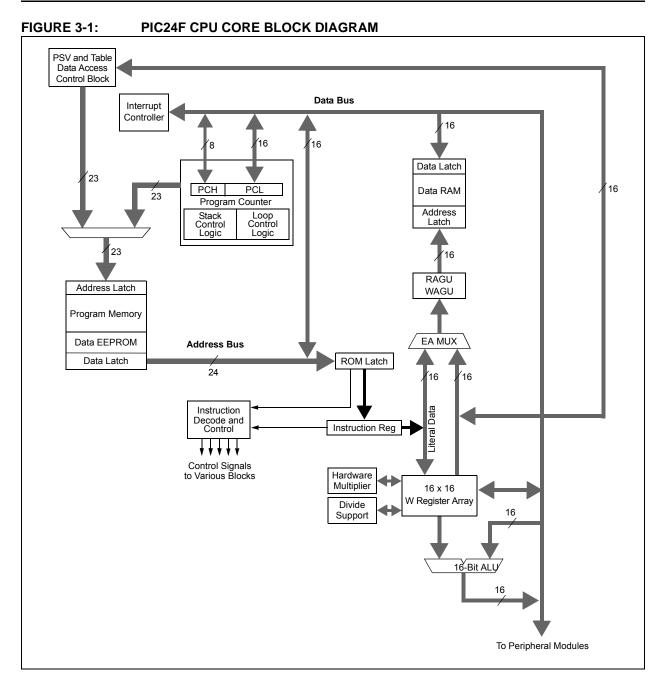

| TABLE 3-1: 0 | CPU CORE REGISTERS |

|--------------|--------------------|

|--------------|--------------------|

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | REPEAT Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

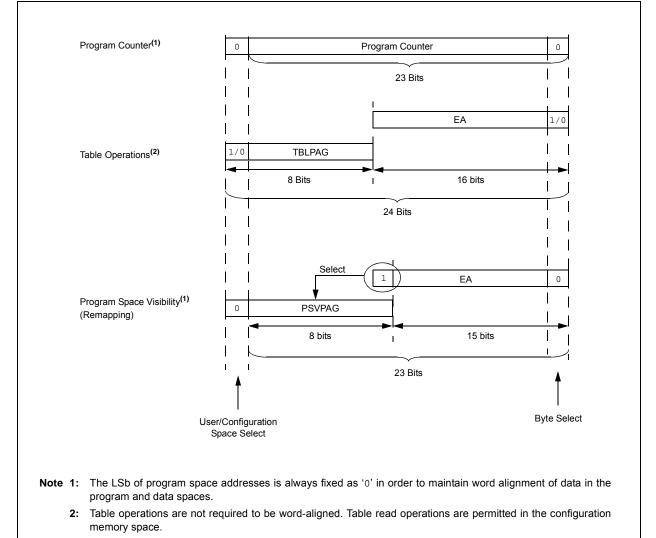

|                                       | Access        | Program Space Address        |           |                          |                    |                |  |  |

|---------------------------------------|---------------|------------------------------|-----------|--------------------------|--------------------|----------------|--|--|

| Access Type                           | Space         | <23>                         | <22:16>   | <15>                     | <14:1>             | <0>            |  |  |

| Instruction Access                    | User          | 0                            |           | PC<22:1>                 | > 0                |                |  |  |

| (Code Execution)                      |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |                          |                    |                |  |  |

| TBLRD/TBLWT<br>(Byte/Word Read/Write) | User          | TBI                          | _PAG<7:0> | Data EA<15:0>            |                    |                |  |  |

|                                       |               | د0                           | xxx xxxx  | XXXX XXXX XXXX XXXX      |                    |                |  |  |

|                                       | Configuration | TBLPAG<7:0>                  |           | Data EA<15:0>            |                    |                |  |  |

|                                       |               | 12                           | xxx xxxx  | XXXX XXXX XXXX XXXX      |                    |                |  |  |

| Program Space Visibility              | User          | 0 PSVPAG<7:                  |           | 7:0>(2) Data EA<14:0>(1) |                    | :0> <b>(1)</b> |  |  |

| (Block Remap/Read)                    |               | 0                            | xxxx xxxx |                          | xxx xxxx xxxx xxxx |                |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) on PIC24F16KL402 family devices.

## 5.0 FLASH PROGRAM MEMORY

| Note: | This data sheet summarizes the features of this group of PIC24F devices. It is not |

|-------|------------------------------------------------------------------------------------|

|       | intended to be a comprehensive reference                                           |

|       | source. For more information on Flash                                              |

|       | Programming, refer to the "dsPIC33/PIC24                                           |

|       | Family Reference Manual", "Program                                                 |

|       | Memory" (DS39715).                                                                 |

The PIC24F16KL402 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 1.8V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24F device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear/Program mode Entry voltage (MCLR/VPP). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed. Run-Time Self Programming (RTSP) is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 32 instructions (96 bytes) at a time, and erase program memory in blocks of 32, 64 and 128 instructions (96,192 and 384 bytes) at a time.

The NVMOP<1:0> (NVMCON<1:0>) bits decide the erase block size.

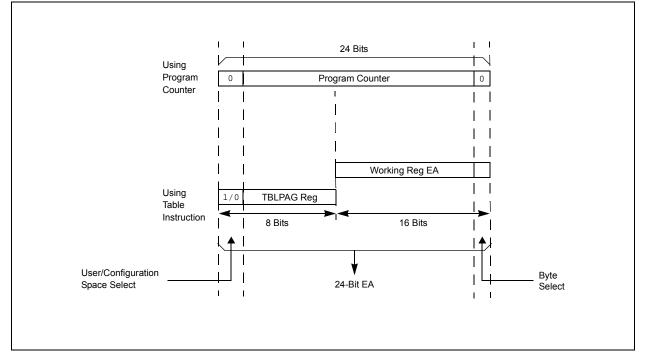

### 5.1 Table Instructions and Flash Programming

Regardless of the method used, Flash memory programming is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as depicted in Figure 5-1.

The TBLRDL and TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

|                 | <b>D</b> 4 4 4 6                                                                                                                                                                                          | <b>D</b> 444 A                | <b>D</b> 4 4 4 4       |                       |                       |                       |                       |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| R/SO-0, HC      | R/W-0                                                                                                                                                                                                     | R/W-0                         | R/W-0                  | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |

| WR              | WREN                                                                                                                                                                                                      | WRERR                         | PGMONLY                |                       |                       | —                     | —                     |  |  |  |

| bit 15          |                                                                                                                                                                                                           |                               |                        |                       |                       |                       | bit 8                 |  |  |  |

|                 |                                                                                                                                                                                                           |                               |                        |                       |                       |                       |                       |  |  |  |

| U-0             | R/W-0                                                                                                                                                                                                     | R/W-0                         | R/W-0                  | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

| —               | ERASE                                                                                                                                                                                                     | NVMOP5 <sup>(1)</sup>         | NVMOP4 <sup>(1)</sup>  | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |  |  |  |

| bit 7           |                                                                                                                                                                                                           |                               |                        |                       |                       |                       | bit 0                 |  |  |  |

|                 |                                                                                                                                                                                                           |                               |                        |                       |                       |                       |                       |  |  |  |

| Legend:         | end: HC = Hardware Clearable bit U = Unimplemented bit, read as '0'                                                                                                                                       |                               |                        |                       |                       |                       |                       |  |  |  |

| R = Readable    | bit                                                                                                                                                                                                       | W = Writable b                | it                     | SO = Settabl          | e Only bit            |                       |                       |  |  |  |

| -n = Value at I | POR                                                                                                                                                                                                       | '1' = Bit is set              |                        | '0' = Bit is cle      | ared                  | x = Bit is unk        | nown                  |  |  |  |

|                 |                                                                                                                                                                                                           |                               |                        |                       |                       |                       |                       |  |  |  |

| bit 15          | WR: Write Co                                                                                                                                                                                              | ontrol bit (progra            | m or erase)            |                       |                       |                       |                       |  |  |  |

|                 |                                                                                                                                                                                                           | a data EEPROM                 |                        | cvcle (can be s       | et but not clea       | red in software       | e)                    |  |  |  |

|                 |                                                                                                                                                                                                           | le is complete (              |                        | •                     |                       |                       | - /                   |  |  |  |

| bit 14          | WREN: Write                                                                                                                                                                                               | Enable bit (eras              | e or program)          |                       |                       |                       |                       |  |  |  |

|                 | 1 = Enables a                                                                                                                                                                                             | in erase or prog              | ram operation          |                       |                       |                       |                       |  |  |  |

|                 | 0 = No operat                                                                                                                                                                                             | tion allowed (dev             | vice clears this t     | oit on completion     | on of the write/      | erase operatio        | on)                   |  |  |  |

| bit 13          | WRERR: Flas                                                                                                                                                                                               | sh Error Flag bit             |                        |                       |                       |                       |                       |  |  |  |

|                 | 1 = A write o                                                                                                                                                                                             | operation is pre              | maturely termir        | nated (any MC         | LR or WDT             | Reset during          | programming           |  |  |  |

|                 | operation                                                                                                                                                                                                 | /                             |                        |                       |                       |                       |                       |  |  |  |

|                 |                                                                                                                                                                                                           | operation comp                |                        | ліу                   |                       |                       |                       |  |  |  |

| bit 12          |                                                                                                                                                                                                           | Program Only En               |                        |                       | <i>.</i>              |                       |                       |  |  |  |

|                 | <ul> <li>1 = Write operation is executed without erasing target address(es) first</li> <li>0 = Automatic erase-before-write; write operations are preceded automatically by an erase of target</li> </ul> |                               |                        |                       |                       |                       |                       |  |  |  |

|                 | address(e                                                                                                                                                                                                 |                               | ville, wille oper      | ations are pred       |                       | lucally by all e      | lase of larger        |  |  |  |

| bit 11-7        | •                                                                                                                                                                                                         | ted: Read as '0'              |                        |                       |                       |                       |                       |  |  |  |

| bit 6           | -                                                                                                                                                                                                         | e Operation Sel               |                        |                       |                       |                       |                       |  |  |  |

| Sit o           |                                                                                                                                                                                                           | an erase opera                |                        | s set                 |                       |                       |                       |  |  |  |

|                 |                                                                                                                                                                                                           | a write operatio              |                        |                       |                       |                       |                       |  |  |  |

| bit 5-0         | NVMOP<5:0>                                                                                                                                                                                                | . Programming                 | Operation Com          | mand Byte bits        | <sub>3</sub> (1)      |                       |                       |  |  |  |

|                 | Erase Operati                                                                                                                                                                                             | ions (when ERA                | <u>SE bit is '1'):</u> | -                     |                       |                       |                       |  |  |  |

|                 | 011010 = Era                                                                                                                                                                                              | ases 8 words                  |                        |                       |                       |                       |                       |  |  |  |

|                 | 011001 = Era                                                                                                                                                                                              |                               |                        |                       |                       |                       |                       |  |  |  |

|                 | 011000 = Era                                                                                                                                                                                              |                               | EEDDOM                 |                       |                       |                       |                       |  |  |  |

|                 |                                                                                                                                                                                                           | ases entire data              |                        | • 'o')•               |                       |                       |                       |  |  |  |

|                 | 001xxx = Wr                                                                                                                                                                                               | Operations (wh<br>ites 1 word | EILERASE DIL IS        | <u> </u>              |                       |                       |                       |  |  |  |

|                 |                                                                                                                                                                                                           |                               |                        |                       |                       |                       |                       |  |  |  |

#### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

Note 1: These NVMOP configurations are unimplemented on PIC24F04KL10X and PIC24F08KL20X devices.

| U-0          | U-0             | U-0              | U-0              | U-0                  | U-0                   | U-0             | R/W-0  |

|--------------|-----------------|------------------|------------------|----------------------|-----------------------|-----------------|--------|

|              | —               |                  | —                | —                    | —                     | —               | HLVDIF |

| bit 15       |                 |                  |                  |                      |                       |                 | bit 8  |

|              |                 |                  |                  |                      |                       |                 |        |

| U-0          | U-0             | U-0              | U-0              | U-0                  | R/W-0                 | R/W-0           | U-0    |

|              |                 |                  |                  |                      | U2ERIF <sup>(1)</sup> | U1ERIF          |        |

| bit 7        |                 |                  |                  |                      |                       |                 | bit 0  |

|              |                 |                  |                  |                      |                       |                 |        |

| Legend:      |                 |                  |                  |                      |                       |                 |        |

| R = Readal   | ble bit         | W = Writable     | bit              | U = Unimplem         | nented bit, read      | l as '0'        |        |

| -n = Value a | at POR          | '1' = Bit is set |                  | '0' = Bit is clea    | ared                  | x = Bit is unkn | iown   |

|              |                 |                  |                  |                      |                       |                 |        |

| bit 15-9     | Unimplemen      | ted: Read as '   | 0'               |                      |                       |                 |        |

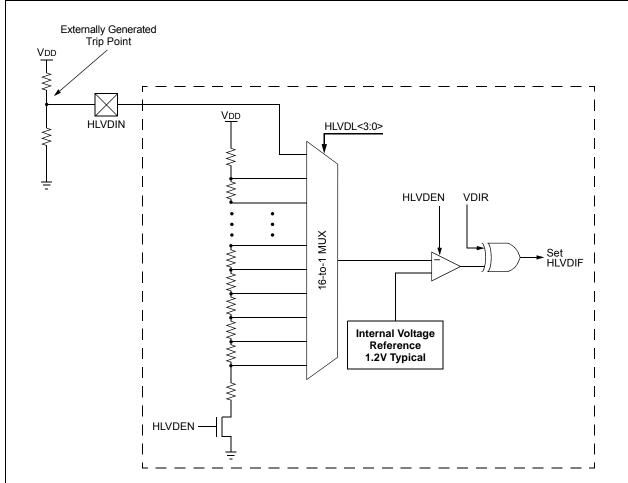

| bit 8        | HLVDIF: High    | n/Low-Voltage [  | Detect Interrupt | t Flag Status bit    | t                     |                 |        |

|              |                 | request has occ  |                  |                      |                       |                 |        |

|              | 0 = Interrupt i | request has not  | t occurred       |                      |                       |                 |        |

| bit 7-3      | Unimplemen      | ted: Read as '   | 0'               |                      |                       |                 |        |

| bit 2        | U2ERIF: UAF     | RT2 Error Interr | upt Flag Status  | s bit <sup>(1)</sup> |                       |                 |        |

|              |                 | request has occ  |                  |                      |                       |                 |        |

|              | 0 = Interrupt i | request has not  | t occurred       |                      |                       |                 |        |

| bit 1        | U1ERIF: UAF     | RT1 Error Interr | upt Flag Status  | s bit                |                       |                 |        |

|              |                 | request has occ  |                  |                      |                       |                 |        |

|              |                 | request has not  |                  |                      |                       |                 |        |

| bit 0        | Unimplemen      | ted: Read as '   | 0'               |                      |                       |                 |        |

#### REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

Note 1: This bit is unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

### REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0           | U-0                                                               | U-0              | U-0 | U-0                                     | U-0  | U-0  | U-0     |

|---------------|-------------------------------------------------------------------|------------------|-----|-----------------------------------------|------|------|---------|

| _             | —                                                                 | _                | —   | —                                       | —    | —    | —       |

| bit 15        |                                                                   |                  |     |                                         |      |      | bit 8   |

|               |                                                                   |                  |     |                                         |      |      |         |

| U-0           | U-0                                                               | U-0              | U-0 | U-0                                     | U-0  | U-0  | R/W-0   |

| —             | —                                                                 | —                | —   | —                                       | —    | —    | ULPWUIF |

| bit 7         |                                                                   |                  |     |                                         |      |      | bit 0   |

|               |                                                                   |                  |     |                                         |      |      |         |

| Legend:       |                                                                   |                  |     |                                         |      |      |         |

| R = Readable  | R = Readable bit W = Writable bit                                 |                  | bit | U = Unimplemented bit, read as '0'      |      |      |         |

| -n = Value at | POR                                                               | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |      | nown |         |

|               | R = Readable bitW = Writable bit-n = Value at POR'1' = Bit is set |                  |     |                                         | nown |      |         |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

### REGISTER 8-21: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0          | R/W-1                                                      | R/W-0                                | R/W-0             | U-0                | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |  |

|--------------|------------------------------------------------------------|--------------------------------------|-------------------|--------------------|------------------|-----------------|---------|--|--|--|--|--|--|

| _            | CNIP2                                                      | CNIP1                                | CNIP0             | _                  | CMIP2            | CMIP1           | CMIP0   |  |  |  |  |  |  |

| bit 15       |                                                            |                                      |                   |                    |                  | •               | bit 8   |  |  |  |  |  |  |

|              |                                                            |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                | R/W-0             | U-0                | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |  |

|              | BCL1IP2                                                    | BCL1IP1                              | BCL1IP0           | —                  | SSP1IP2          | SSP1IP1         | SSP1IP0 |  |  |  |  |  |  |

| bit 7        |                                                            |                                      |                   |                    |                  |                 | bit (   |  |  |  |  |  |  |

| Legend:      |                                                            |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

| R = Readab   | le bit                                                     | W = Writable                         | bit               | U = Unimpler       | nented bit, read | l as '0'        |         |  |  |  |  |  |  |

| -n = Value a | t POR                                                      | '1' = Bit is set                     |                   | '0' = Bit is cle   | ared             | x = Bit is unkr | nown    |  |  |  |  |  |  |

| bit 15       | Unimplemer                                                 | nted: Read as '                      | 0'                |                    |                  |                 |         |  |  |  |  |  |  |

| bit 14-12    | CNIP<2:0>:                                                 | Input Change N                       | Iotification Inte | rrupt Priority bit | ts               |                 |         |  |  |  |  |  |  |

|              | 111 = Interru                                              | pt is Priority 7 (                   | highest priority  | / interrupt)       |                  |                 |         |  |  |  |  |  |  |

|              | •                                                          |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              | •                                                          | •                                    |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1                         |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              | 000 = Interru                                              | ipt source is dis                    | abled             |                    |                  |                 |         |  |  |  |  |  |  |

| bit 11       | Unimplemer                                                 | nted: Read as '                      | 0'                |                    |                  |                 |         |  |  |  |  |  |  |

| bit 10-8     | CMIP<2:0>: Comparator Interrupt Priority bits              |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt) |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              | •                                                          |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              | •                                                          |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              |                                                            | pt is Priority 1                     |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              |                                                            | pt source is dis                     |                   |                    |                  |                 |         |  |  |  |  |  |  |

| bit 7        | -                                                          | nted: Read as '                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

| bit 6-4      |                                                            | >: MSSP1 I <sup>2</sup> C™           |                   | •                  | ity bits         |                 |         |  |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt) |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              | •                                                          |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              | •                                                          |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              |                                                            | pt is Priority 1                     |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              |                                                            | pt source is dis                     |                   |                    |                  |                 |         |  |  |  |  |  |  |

| bit 3        | -                                                          | Unimplemented: Read as '0'           |                   |                    |                  |                 |         |  |  |  |  |  |  |

| bit 2-0      |                                                            | >: MSSP1 SPI/                        |                   | 1 2                | S                |                 |         |  |  |  |  |  |  |

|              | 111 = Interru                                              | pt is Priority 7 (                   | highest priority  | / interrupt)       |                  |                 |         |  |  |  |  |  |  |

|              | •                                                          |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              |                                                            |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              | •                                                          |                                      |                   |                    |                  |                 |         |  |  |  |  |  |  |

|              |                                                            | pt is Priority 1<br>pt source is dis |                   |                    |                  |                 |         |  |  |  |  |  |  |

### 8.4 Interrupt Setup Procedures

### 8.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS Control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and the type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits, for all enabled interrupt sources, may be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized, such that all user interrupt sources are assigned to Priority Level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

### 8.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (i.e., C or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

### 8.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 8.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, OEh, with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period. Level 7 interrupt sources are not disabled by the DISI instruction.

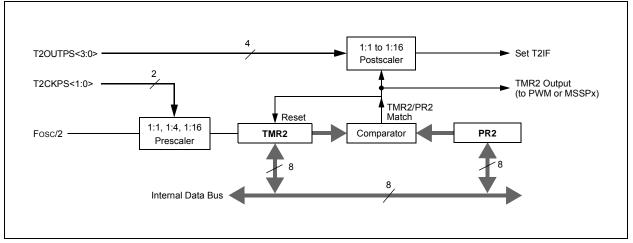

# 13.0 TIMER2 MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704).

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional Timer3 gate on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP modules

This module is controlled through the T2CON register (Register 13-1), which enables or disables the timer and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMR2 register

- · A write to the T2CON register

- Any device Reset (POR, BOR, MCLR or WDT Reset)

TMR2 is not cleared when T2CON is written.

A simplified block diagram of the module is shown in Figure 13-1.

### FIGURE 13-1: TIMER2 BLOCK DIAGRAM

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                    | U-0                                                                                                                                     | U-0                                                                                     | U-0                                                | U-0                                       |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------|--|--|--|--|

| _            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                      |                                                                                                                                         | —                                                                                       |                                                    | —                                         |  |  |  |  |

| bit 15       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |                                                                                                                                         |                                                                                         |                                                    | bit 8                                     |  |  |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |                                                                                                                                         |                                                                                         |                                                    |                                           |  |  |  |  |

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                  | R/W-0                                                                                                                                   | R/W-0                                                                                   | R/W-0                                              | R/W-0<br>CCPxM0 <sup>(1)</sup>            |  |  |  |  |

|              | — DCxB1 DCxB0 CCPxM3 <sup>(1)</sup> CCPxM2 <sup>(1)</sup> CCPxM <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |                                                                                                                                         |                                                                                         |                                                    |                                           |  |  |  |  |

| bit 7        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |                                                                                                                                         |                                                                                         |                                                    | bit (                                     |  |  |  |  |

| Legend:      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |                                                                                                                                         |                                                                                         |                                                    |                                           |  |  |  |  |

| R = Readal   | ble bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                    | U = Unimplem                                                                                                                            | nented bit, read                                                                        | l as '0'                                           |                                           |  |  |  |  |