Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| 201010                     |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

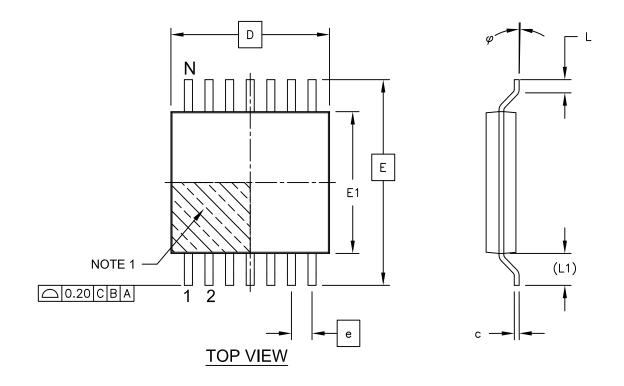

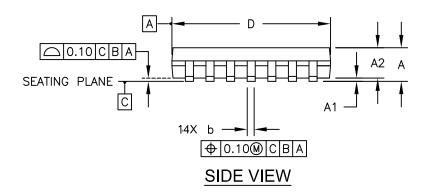

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 20-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl301-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Analog Features:**

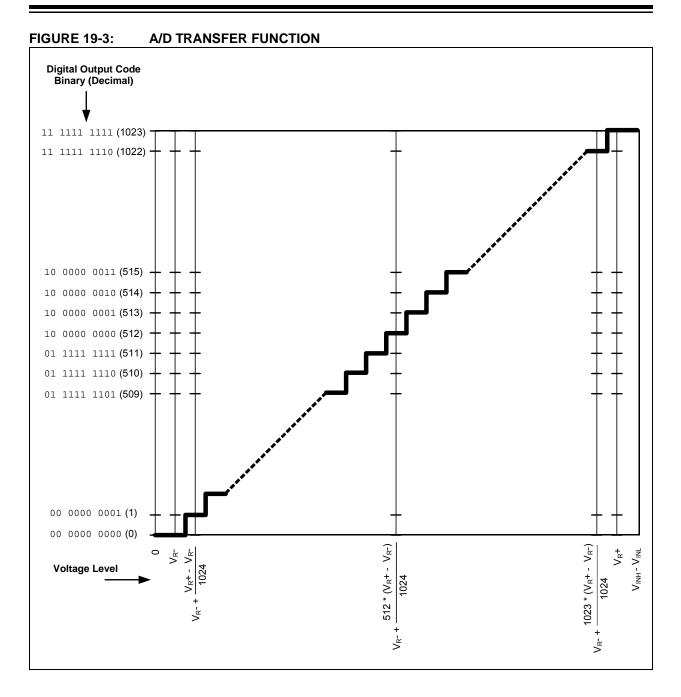

- 10-Bit, up to 12-Channel Analog-to-Digital (A/D) Converter:

- 500 ksps conversion rate

- Conversion available during Sleep and Idle

- Dual Rail-to-Rail Analog Comparators with Programmable Input/Output Configuration

- On-Chip Voltage Reference

## **Special Microcontroller Features:**

- Operating Voltage Range of 1.8V to 3.6V

- 10,000 Erase/Write Cycle Endurance Flash Program Memory, Typical

- 100,000 Erase/Write Cycle Endurance Data EEPROM, Typical

- Flash and Data EEPROM Data Retention: 40 Years Minimum

- Self-Programmable under Software Control

- Programmable Reference Clock Output

- Fail-Safe Clock Monitor (FSCM) Operation:

- Detects clock failure and switches to on-chip, Low-Power RC (LPRC) oscillator

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT):

- Uses its own Low-Power RC oscillator

- Windowed operating modes

- Programmable period of 2 ms to 131s

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and In-Circuit Emulation (ICE) via 2 Pins

- Programmable High/Low-Voltage Detect (HLVD)

- Programmable Brown-out Reset (BOR):

- Configurable for software controlled operation and shutdown in Sleep mode

- Selectable trip points (1.8V, 2.7V and 3.0V)

- Low-power 2.0V POR re-arm

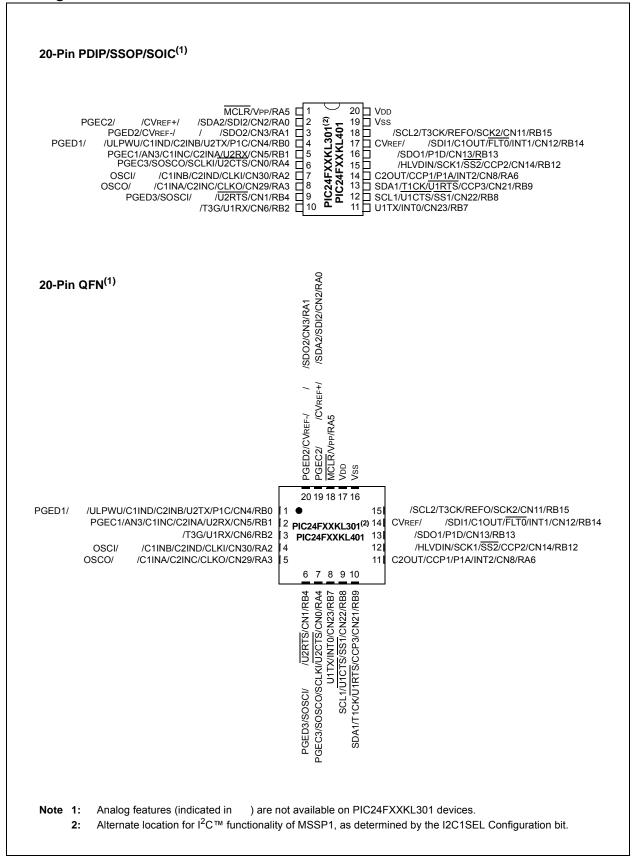

## Pin Diagrams: PIC24FXXKL301/401

## 2.2 Power Supply Pins

### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ .

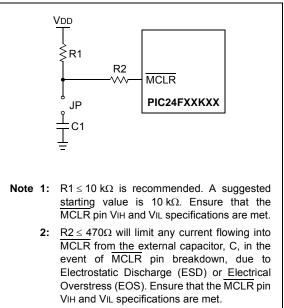

## 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12    | Bit 11                | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5 | Bit 4                | Bit 3                | Bit 2                | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|-----------|-----------------------|--------|--------|--------|---------|-------|-------|----------------------|----------------------|----------------------|--------|--------|---------------|

| ADC1BUF0     | 0300 |        |        |        |           |                       |        |        | A/D Bu | uffer 0 |       |       |                      |                      |                      |        |        | xxxx          |

| ADC1BUF1     | 0302 |        |        |        |           |                       |        |        | A/D Bu | uffer 1 |       |       |                      |                      |                      |        |        | xxxx          |

| AD1CON1      | 0320 | ADON   | —      | ADSIDL | —         | _                     | _      | FORM1  | FORM0  | SSRC2   | SSRC1 | SSRC0 | _                    |                      | ASAM                 | SAMP   | DONE   | 0000          |

| AD1CON2      | 0322 | VCFG2  | VCFG1  | VCFG0  | OFFCAL    | _                     | CSCNA  |        | _      | r       |       | SMPI3 | SMPI2                | SMPI1                | SMPI0                | r      | ALTS   | 0000          |

| AD1CON3      | 0324 | ADRC   | EXTSAM | PUMPEN | SAMC4     | SAMC3                 | SAMC2  | SAMC1  | SAMC0  |         |       | ADCS5 | ADCS4                | ADCS3                | ADCS2                | ADCS1  | ADCS0  | 0000          |

| AD1CHS       | 0328 | CH0NB  | —      |        | —         | CH0SB3                | CH0SB2 | CH0SB1 | CH0SB0 | CH0NA   |       | _     | _                    | CH0SA3               | CH0SA2               | CH0SA1 | CH0SA0 | 0000          |

| AD1CSSL      | 0330 | CSSL15 | CSSL14 | CSSL13 | CSSL12(1) | CSSL11 <sup>(1)</sup> | CSSL10 | CSSL9  | CSSL8  | CSSL7   | CSSL6 | _     | CSSL4 <sup>(1)</sup> | CSSL3 <sup>(1)</sup> | CSSL2 <sup>(1)</sup> | CSSL1  | CSSL0  | 0000          |

Legend: — = unimplemented, read as '0', r = reserved bit. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 14-pin devices; read as '0'.

#### TABLE 4-14: ANALOG SELECT REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12                | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2                | Bit 1                | Bit 0                | All<br>Resets       |

|-----------|------|--------|--------|--------|-----------------------|--------|--------|-------|-------|-------|-------|-------|-------|----------|----------------------|----------------------|----------------------|---------------------|

| ANCFG     | 04DE | _      | —      | —      | —                     | _      | _      |       | _     | _     | _     |       |       | _        | —                    |                      | VBGEN                | 0000                |

| ANSA      | 04E0 | -      | _      | -      | —                     | _      | -      | _     | _     | _     | _     | _     | _     | ANSA3    | ANSA2                | ANSA1                | ANSA0                | 000F                |

| ANSB      | 04E2 | ANSB15 | ANSB14 | ANSB13 | ANSB12 <sup>(1)</sup> | —      | _      | _     | _     | —     | —     | _     | ANSB4 | ANSB3(2) | ANSB2 <sup>(1)</sup> | ANSB1 <sup>(1)</sup> | ANSB0 <sup>(1)</sup> | F01F <sup>(3)</sup> |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 14-pin devices; read as '0'.

2: These bits are unimplemented in 14-pin and 20-pin devices; read as '0'

3: Reset value for 28-pin devices is shown.

#### TABLE 4-15: COMPARATOR REGISTER MAP

| File<br>Name          | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------------------|------|--------|--------|--------|--------|--------|--------|----------------------|-------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT                | 0630 | CMIDL  | —      | _      |        | _      | _      | C2EVT <sup>(1)</sup> | C1EVT | —      | —      | _     |       | _     | _     | C2OUT | C1OUT | xxxx          |

| CVRCON                | 0632 | _      | _      | _      | _      | _      | _      | _                    | _     | CVREN  | CVROE  | CVRSS | CVR4  | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON                | 0634 | CON    | COE    | CPOL   | CLPWR  | —      | _      | CEVT                 | COUT  | EVPOL1 | EVPOL0 | —     | CREF  | —     | _     | CCH1  | CCH0  | xxxx          |

| CM2CON <sup>(1)</sup> | 0636 | CON    | COE    | CPOL   | CLPWR  | _      | _      | CEVT                 | COUT  | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented in PIC24FXXKL10X/20X devices; read as '0'.

## REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| R/W-0         | U-0                 | R/W-0                              | R/W-0           | R/W-0             | U-0              | U-0             | R/W-0       |

|---------------|---------------------|------------------------------------|-----------------|-------------------|------------------|-----------------|-------------|

| NVMIF         | _                   | AD1IF                              | U1TXIF          | U1RXIF            |                  |                 | T3IF        |

| bit 15        |                     |                                    |                 |                   |                  |                 | bit 8       |

|               | 5444.6              |                                    |                 | 5444              |                  |                 | 5444.6      |

| R/W-0         | R/W-0               | U-0                                | U-0             | R/W-0             | R/W-0            | U-0             | R/W-0       |

| T2IF          | CCP2IF              | —                                  | —               | T1IF              | CCP1IF           | —               | INTOIF      |

| bit 7         |                     |                                    |                 |                   |                  |                 | bit (       |

| Legend:       |                     |                                    |                 |                   |                  |                 |             |

| R = Readable  | e bit               | W = Writable                       | bit             | U = Unimplen      | nented bit, read | d as '0'        |             |

| -n = Value at | POR                 | '1' = Bit is set                   |                 | '0' = Bit is clea | ared             | x = Bit is unkı | nown        |

|               |                     |                                    |                 |                   |                  |                 |             |

| bit 15        | NVMIF: NVM          | I Interrupt Flag                   | Status bit      |                   |                  |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 14        | -                   | ted: Read as '                     |                 |                   |                  |                 |             |

| bit 13        | <b>AD1IF:</b> A/D ( | Conversion Cor                     | nplete Interrup | t Flag Status bit | t                |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

| h:1 40        | -                   | request has no                     |                 | Otatus hit        |                  |                 |             |

| bit 12        |                     | RT1 Transmitter                    |                 | Status bit        |                  |                 |             |

|               |                     | request has no                     |                 |                   |                  |                 |             |

| bit 11        | -                   | RT1 Receiver In                    |                 | tatus bit         |                  |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 10-9      | Unimplemer          | ted: Read as '                     | 0'              |                   |                  |                 |             |

| bit 8         | T3IF: Timer3        | Interrupt Flag                     | Status bit      |                   |                  |                 |             |

|               | •                   | request has oc                     |                 |                   |                  |                 |             |

|               |                     | request has no                     |                 |                   |                  |                 |             |

| bit 7         |                     | Interrupt Flag                     |                 |                   |                  |                 |             |

|               |                     | request has oc<br>request has no   |                 |                   |                  |                 |             |

| bit 6         |                     | -                                  |                 | ot Flag Status b  | it               |                 |             |

|               | •                   | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 5-4       | Unimplemer          | ted: Read as '                     | 0'              |                   |                  |                 |             |

| bit 3         | T1IF: Timer1        | Interrupt Flag                     | Status bit      |                   |                  |                 |             |

|               | •                   | request has oc<br>request has no   |                 |                   |                  |                 |             |

| bit 2         | -                   | -                                  |                 | ot Flag Status b  | it (ECCP1 on F   | PIC24FXXKL40    | )X devices) |

|               | 1 = Interrupt       | request has oc                     | curred          | 0                 | Υ.               |                 | ,           |

| L:1 4         | -                   | request has no                     |                 |                   |                  |                 |             |

| bit 1         | -                   | ted: Read as '                     |                 |                   |                  |                 |             |

|               |                     |                                    |                 |                   |                  |                 |             |

| bit 0         |                     | rnal Interrupt 0<br>request has oc | -               |                   |                  |                 |             |

|                    | R/W-1                                                                                              | R/W-0                                                                                                   | R/W-0                                                     | U-0              | R/W-1            | R/W-0           | R/W-0   |

|--------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------|------------------|-----------------|---------|

| _                  | T2IP2                                                                                              | T2IP1                                                                                                   | T2IP0                                                     | _                | CCP2IP2          | CCP2IP1         | CCP2IP0 |

| bit 15             |                                                                                                    |                                                                                                         |                                                           |                  |                  | 1               | bit 8   |

|                    |                                                                                                    |                                                                                                         |                                                           |                  |                  |                 |         |

| U-0                | U-0                                                                                                | U-0                                                                                                     | U-0                                                       | U-0              | U-0              | U-0             | U-0     |

| —                  | _                                                                                                  | _                                                                                                       |                                                           | —                | _                |                 | _       |

| bit 7              |                                                                                                    |                                                                                                         |                                                           |                  |                  |                 | bit C   |

|                    |                                                                                                    |                                                                                                         |                                                           |                  |                  |                 |         |

| Legend:            |                                                                                                    |                                                                                                         |                                                           |                  |                  |                 |         |

| R = Readab         | ole bit                                                                                            | W = Writable                                                                                            | oit                                                       | U = Unimple      | mented bit, read | l as '0'        |         |

| -n = Value a       | at POR                                                                                             | '1' = Bit is set                                                                                        |                                                           | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |

|                    |                                                                                                    |                                                                                                         |                                                           |                  |                  |                 |         |

| bit 15             | Unimplemen                                                                                         | ted: Read as 'd                                                                                         | )'                                                        |                  |                  |                 |         |

| bit 14-12          | T2IP<2:0>: ⊺                                                                                       | ïmer2 Interrupt                                                                                         | Priority bits                                             |                  |                  |                 |         |

|                    | 111 = Interru                                                                                      | pt is Priority 7 (                                                                                      | nighest priorit                                           | y interrupt)     |                  |                 |         |

|                    | •                                                                                                  |                                                                                                         |                                                           |                  |                  |                 |         |

|                    | •                                                                                                  |                                                                                                         |                                                           |                  |                  |                 |         |

|                    | •                                                                                                  |                                                                                                         |                                                           |                  |                  |                 |         |

|                    |                                                                                                    | pt is Priority 1                                                                                        |                                                           |                  |                  |                 |         |

|                    | 000 = Interru                                                                                      | pt source is dis                                                                                        |                                                           |                  |                  |                 |         |

| bit 11             | 000 = Interru<br>Unimplemen                                                                        | pt source is dis<br>ited: Read as '(                                                                    | )'                                                        |                  |                  |                 |         |

| bit 11<br>bit 10-8 | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:                                                         | pt source is dis<br><b>ited:</b> Read as '(<br>>: Capture/Corr                                          | )'<br>pare/PWM2 I                                         |                  | / bits           |                 |         |

|                    | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:                                                         | pt source is dis<br>ited: Read as '(                                                                    | )'<br>pare/PWM2 I                                         |                  | / bits           |                 |         |

|                    | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:                                                         | pt source is dis<br><b>ited:</b> Read as '(<br>>: Capture/Corr                                          | )'<br>pare/PWM2 I                                         |                  | ∕ bits           |                 |         |

|                    | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:                                                         | pt source is dis<br><b>ited:</b> Read as '(<br>>: Capture/Corr                                          | )'<br>pare/PWM2 I                                         |                  | / bits           |                 |         |

|                    | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:<br>111 = Interru<br>•<br>•<br>001 = Interru             | pt source is dis<br><b>ited:</b> Read as '(<br>>: Capture/Com<br>pt is Priority 7 (<br>pt is Priority 1 | <sup>)'</sup><br>pare/PWM2 I<br>nighest priorit           |                  | / bits           |                 |         |

|                    | 000 = Interru<br>Unimplemen<br>CCP2IP<2:0:<br>111 = Interru<br>•<br>001 = Interru<br>000 = Interru | pt source is dis<br><b>ited:</b> Read as '(<br>>: Capture/Com<br>pt is Priority 7 ()                    | <sub>)</sub> '<br>pare/PWM2 I<br>nighest priorit<br>abled |                  | ∕ bits           |                 |         |

#### REGISTER 8-18: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

#### REGISTER 8-28: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|--------|-----|-----|-----|-----|---------|---------|---------|

|        | _   | _   | _   | _   | _       | _       | _       |

| bit 15 |     |     |     |     |         |         | bit 8   |

|        |     |     |     |     |         |         |         |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| —      | —   | —   | —   | —   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7  |     |     |     |     |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

## bit 15-3 Unimplemented: Read as '0'

bit 2-0 HLVDIP<2:0>: High/Low-Voltage Detect Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

## REGISTER 8-29: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| -n = Value at | POR   | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                  |          |          |  |  |

|---------------|-------|------------------|-----|-----------------------------------------|------------------|----------|----------|--|--|

| R = Readable  | e bit | W = Writable     | bit | U = Unimplen                            | nented bit, read | l as '0' |          |  |  |

| Legend:       |       |                  |     |                                         |                  |          |          |  |  |

|               |       |                  |     |                                         |                  |          |          |  |  |

| bit 7         |       |                  | •   | 4                                       |                  | •        | bit      |  |  |

| _             |       |                  |     |                                         | ULPWUIP2         | ULPWUIP1 | ULPWUIP0 |  |  |

| U-0           | U-0   | U-0              | U-0 | U-0                                     | R/W-1            | R/W-0    | R/W-0    |  |  |

|               |       |                  |     |                                         |                  |          |          |  |  |

| bit 15        |       |                  | •   |                                         |                  | •        | bit      |  |  |

| _             | —     | —                | —   | —                                       | —                | —        | _        |  |  |

| U-0           | U-0   | U-0              | U-0 | U-0                                     | U-0              | U-0      | U-0      |  |  |

bit 15-3 Unimplemented: Read as '0'

bit 6-4 ULPWUIP<2:0>: Ultra Low-Power Wake-up Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

.

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

## REGISTER 8-30: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| R-0           | r-0                                     | R/W-0                                                                         | U-0                           | R-0                              | R-0                                                                           | R-0                                    | R-0            |

|---------------|-----------------------------------------|-------------------------------------------------------------------------------|-------------------------------|----------------------------------|-------------------------------------------------------------------------------|----------------------------------------|----------------|

| CPUIRQ        | r                                       | VHOLD                                                                         | —                             | ILR3                             | ILR2                                                                          | ILR1                                   | ILR0           |

| bit 15        |                                         |                                                                               |                               | •                                |                                                                               | ·                                      | bit 8          |

|               |                                         |                                                                               |                               |                                  |                                                                               |                                        |                |

| U-0           |                                         | R-0                                                                           |                               |                                  |                                                                               |                                        |                |

|               | VECNUM6                                 | VECNUM5                                                                       | VECNUM4                       | VECNUM3                          | VECNUM2                                                                       | VECNUM1                                | VECNUM0        |

| bit 7         |                                         |                                                                               |                               |                                  |                                                                               |                                        | bit (          |

| Legend:       |                                         | r = Reserved                                                                  | bit                           |                                  |                                                                               |                                        |                |

| R = Readable  | e bit                                   | W = Writable                                                                  | bit                           | U = Unimpler                     | nented bit, read                                                              | as '0'                                 |                |

| -n = Value at | POR                                     | '1' = Bit is set                                                              |                               | '0' = Bit is cle                 |                                                                               | x = Bit is unkr                        | nown           |

| bit 14        | 0 = No interr                           | vhen the CPU p<br>upt request is le<br>aintain as '0'                         |                               |                                  | errupt priority)                                                              |                                        |                |

| bit 14        | Reserved: M                             |                                                                               |                               | 0                                |                                                                               |                                        |                |

| bit 13        | VHOLD: Vect                             | tor Hold bit                                                                  |                               |                                  |                                                                               |                                        |                |

|               | 1 = VECNUN<br>current in<br>0 = VECNUN  | //<6:0> will cor<br>nterrupt<br>//<6:0> will con                              | tain the value                | e of the highe<br>of the last Ac | rupt is Stored in<br>st priority pend<br>knowledged inte<br>ther interrupts a | ling interrupt, i<br>errupt (last inte | instead of the |

| bit 12        | Unimplemen                              | ted: Read as '                                                                | )'                            |                                  |                                                                               |                                        |                |

| bit 11-8      | 1111 = CPU<br>•<br>•<br>•<br>0001 = CPU | w CPU Interrup<br>Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit | y Level is 15<br>y Level is 1 | el bits                          |                                                                               |                                        |                |

| bit 7         | Unimplemen                              | ted: Read as '                                                                | )'                            |                                  |                                                                               |                                        |                |

| bit 6-0       | VECNUM<6:                               | 0>: Vector Num                                                                | ber of Pendin                 | g Interrupt bits                 | 5                                                                             |                                        |                |

|               | 0111111 = Ir<br>•<br>•                  | nterrupt vector p                                                             | pending is Nu                 | mber 135                         |                                                                               |                                        |                |

|               |                                         | nterrupt vector p<br>nterrupt vector p                                        |                               |                                  |                                                                               |                                        |                |

### REGISTER 11-1: ANSA: PORTA ANALOG SELECTION REGISTER

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —      | —   |     |     |     |     |     | —     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | ANSA3 | ANSA2 | ANSA1 | ANSA0 |

| bit 7 |     |     |     |       |       |       | bit 0 |

## Legend:

bit 3-0

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

ANSA<3:0>: Analog Select Control bits

1 = Digital input buffer is not active (use for analog input)

0 = Digital input buffer is active

## REGISTER 11-2: ANSB: PORTB ANALOG SELECTION REGISTER

| R/W-1  | R/W-1  | R/W-1                 | R/W-1                 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|-----------------------|-----------------------|-----|-----|-----|-------|

| ANSB15 | ANSB14 | ANSB13 <sup>(1)</sup> | ANSB12 <sup>(1)</sup> | —   | —   | —   | —     |

| bit 15 |        | •                     |                       |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1                | R/W-1                | R/W-1                | R/W-1                |

|-------|-----|-----|-------|----------------------|----------------------|----------------------|----------------------|

| _     | —   | —   | ANSB4 | ANSB3 <sup>(2)</sup> | ANSB2 <sup>(1)</sup> | ANSB1 <sup>(1)</sup> | ANSB0 <sup>(1)</sup> |

| bit 7 |     |     |       |                      |                      |                      | bit 0                |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-12 | ANSB<15:12>: Analog Select Control bits <sup>(1)</sup><br>1 = Digital input buffer is not active (use for analog input)<br>0 = Digital input buffer is active |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-5  | Unimplemented: Read as '0'                                                                                                                                    |

| bit 4-0   | ANSB<4:0>: Analog Select Control bits <sup>(2)</sup>                                                                                                          |

|           | <ul><li>1 = Digital input buffer is not active (use for analog input)</li><li>0 = Digital input buffer is active</li></ul>                                    |

|           |                                                                                                                                                               |

**Note 1:** ANSB<13:12,2:0> are unimplemented on 14-pin devices.

2: ANSB<3> is unimplemented on 14-pin and 20-pin devices.

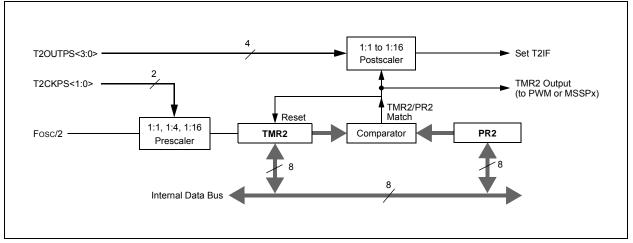

## 13.0 TIMER2 MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704).

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional Timer3 gate on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP modules

This module is controlled through the T2CON register (Register 13-1), which enables or disables the timer and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMR2 register

- · A write to the T2CON register

- Any device Reset (POR, BOR, MCLR or WDT Reset)

TMR2 is not cleared when T2CON is written.

A simplified block diagram of the module is shown in Figure 13-1.

## FIGURE 13-1: TIMER2 BLOCK DIAGRAM

NOTES:

## 23.0 SPECIAL FEATURES

- Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Watchdog Timer, High-Level Device Integration and Programming Diagnostics, refer to the individual sections of the "dsPIC33/PIC24 Family Reference Manual" provided below:

"Watchdog Timer (WDT)" (DS39697)

- "High-Level Integration with Programmable High/Low-Voltage Detect (HLVD)" (DS39725)

- "Programming and Diagnostics" (DS39716)

PIC24F16KL402 family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

- Factory Programmed Unique ID

## 23.1 Code Protect Security Options

The Boot Segment (BS) and General Segment (GS) are two segments on this device with separate programmable security levels. The Boot Segment, configured via the FBS Configuration register, can have three possible levels of security:

- No Security (BSS = 111): The Boot Segment is not utilized and all addresses in program memory are part of the General Segment (GS).

- Standard Security (BSS = 110 or 101): The Boot Segment is enabled and code-protected, preventing ICSP reads of the Flash memory. Standard security also prevents Flash reads and writes of the BS from the GS. The BS can still read and write to itself.

- High Security (BSS = 010 or 001): The Boot Segment is enabled with all of the security provided by Standard Security mode. In addition, in High-Security mode, there are program flow change restrictions in place. While executing from the GS, program flow changes that attempt to enter the BS (e.g., branch (BRA) or CALL instructions) can only enter the BS at one of the first 32 instruction locations (0x200 to 0x23F). Attempting to jump into the BS at an instruction higher than this will result in an Illegal Opcode Reset.

The General Segment, configured via the FGS Configuration register, can have two levels of security:

- No Security (GSS0 = 1): The GS is not code-protected and can be read in all modes.

- Standard Security (GSS0 = 0): The GS is code-protected, preventing ICSP reads of the Flash memory.

For more detailed information on these Security modes, refer to the *"dsPlC33/PlC24 Family Reference Manual"*, **"CodeGuard™ Security"** (DS70199).

## 23.2 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location, F80000h. A complete list is provided in Table 23-1. A detailed explanation of the various bit functions is provided in Register 23-1 through Register 23-7.

The address, F80000h, is beyond the user program memory space. In fact, it belongs to the configuration memory space (800000h-FFFFFh), which can only be accessed using Table Reads and Table Writes.

| TABLE 23-1: | <b>CONFIGURATION REGISTERS</b> |

|-------------|--------------------------------|

|             | LOCATIONS                      |

| Configuration<br>Register | Address |

|---------------------------|---------|

| FBS                       | F80000  |

| FGS                       | F80004  |

| FOSCSEL                   | F80006  |

| FOSC                      | F80008  |

| FWDT                      | F8000A  |

| FPOR                      | F8000C  |

| FICD                      | F8000E  |

| R/P-0        | R/P-0                               | R/P-1            | R/P-1             | R/P-1             | R/P-0           | R/P-1           | R/P-1   |

|--------------|-------------------------------------|------------------|-------------------|-------------------|-----------------|-----------------|---------|

| FCKSM1       | FCKSM0                              | SOSCSEL          | POSCFREQ1         | POSCFREQ0         | OSCIOFNC        | POSCMD1         | POSCMD0 |

| bit 7        |                                     |                  |                   |                   |                 |                 | bit 0   |

|              |                                     |                  |                   |                   |                 |                 |         |

| Legend:      |                                     |                  |                   |                   |                 |                 |         |

| R = Readab   | le bit                              | P = Program      | nable bit         | U = Unimplem      | ented bit, read | as '0'          |         |

| -n = Value a | It POR                              | '1' = Bit is set |                   | '0' = Bit is clea | red             | x = Bit is unkr | nown    |

|              |                                     |                  |                   |                   |                 |                 |         |

| bit 7-6      | FCKSM<1:0>                          | Clock Switch     | ing and Monito    | r Selection Con   | figuration bits |                 |         |

|              |                                     | 0                | •                 | Clock Monitor is  |                 |                 |         |

|              |                                     | 0                |                   | Clock Monitor is  |                 |                 |         |

|              |                                     | 0                |                   | Clock Monitor is  |                 |                 |         |

| bit 5        |                                     |                  |                   | election Configu  |                 |                 |         |

|              |                                     | •                | •                 | igh-power opera   |                 |                 |         |

| bit 4-3      |                                     |                  | 0                 | uency Range C     |                 | te.             |         |

| DIL 4-3      |                                     |                  |                   | frequency is gre  | 0               |                 |         |

|              |                                     |                  |                   | frequency is be   |                 |                 |         |

|              |                                     |                  |                   | frequency is les  |                 |                 |         |

|              | 00 = Reserve                        | ed; do not use   |                   |                   |                 |                 |         |

| bit 2        | OSCIOFNC:                           | CLKO Enable      | Configuration b   | it                |                 |                 |         |

|              |                                     |                  |                   | SCO pin; prima    |                 |                 |         |

|              |                                     |                  |                   | e CLKO to be a    | active (POSCM   | ID<1:0> = 11 c  | r 00)   |

|              |                                     | Itput is disable |                   |                   |                 |                 |         |

| bit 1-0      |                                     | •                | scillator Configu | iration bits      |                 |                 |         |

|              |                                     | Oscillator mod   |                   |                   |                 |                 |         |

|              |                                     | llator mode is a |                   |                   |                 |                 |         |

|              | 01 = XT Oscillator mode is selected |                  |                   |                   |                 |                 |         |

#### REGISTER 23-4: FOSC: OSCILLATOR CONFIGURATION REGISTER

00 = External Clock mode is selected

| R/P-1               | R/P-1                                 | R/P-1                | R/P-1                                 | R/P-1             | U-0              | R/P-1             | R/P-1                      |

|---------------------|---------------------------------------|----------------------|---------------------------------------|-------------------|------------------|-------------------|----------------------------|

| MCLRE <sup>(1</sup> | ) BORV1 <sup>(2)</sup>                | BORV0 <sup>(2)</sup> | I2C1SEL <sup>(3)</sup>                | PWRTEN            |                  | BOREN1            | BOREN0                     |

| bit 7               |                                       |                      |                                       |                   |                  |                   | bit C                      |

| Logondi             |                                       |                      |                                       |                   |                  |                   |                            |

| Legend:             |                                       |                      |                                       |                   |                  | 1                 |                            |

| R = Reada           |                                       | P = Program          |                                       | •                 | nented bit, read |                   |                            |

| -n = Value          | at POR                                | '1' = Bit is set     |                                       | '0' = Bit is clea | ared             | x = Bit is unkr   | nown                       |

| bit 7               |                                       | R Pin Enable         | hit(1)                                |                   |                  |                   |                            |

|                     |                                       |                      | A5 input pin is o                     | lisabled          |                  |                   |                            |

|                     |                                       |                      | ; MCLR is disa                        |                   |                  |                   |                            |

| bit 6-5             | BORV<1:0>:                            | Brown-out Res        | set Enable bits <sup>(</sup>          | 2)                |                  |                   |                            |

|                     | 11 = Brown-o                          | ut Reset is set      | to the low trip p                     | point             |                  |                   |                            |

|                     |                                       |                      | to the middle to                      |                   |                  |                   |                            |

|                     |                                       |                      | to the high trip<br>POR is enable ו   |                   |                  | ad)               |                            |

| bit 4               |                                       | -                    | I <sup>2</sup> C <sup>™</sup> Pin Map | -                 | DON 13 SEIECI    | eu)               |                            |

|                     |                                       |                      | 1/SDA1 pins (R                        | U U               |                  |                   |                            |

|                     |                                       |                      | L1/SDA1 pins (                        | ,                 | nd ASDA1/RB      | 5)                |                            |

| bit 3               |                                       | wer-up Timer         | -                                     |                   |                  |                   |                            |

|                     | 1 = PWRT is                           | enabled              |                                       |                   |                  |                   |                            |

|                     | 0 = PWRT is                           | disabled             |                                       |                   |                  |                   |                            |

| bit 2               | Unimplemen                            | ted: Read as '       | 0'                                    |                   |                  |                   |                            |

| bit 1-0             | BOREN<1:0>                            | Brown-out R          | eset Enable bit                       | S                 |                  |                   |                            |

|                     |                                       |                      | dware; SBOREI                         |                   |                  |                   |                            |

|                     |                                       |                      | hile device is a                      |                   | oled in Sleep; S | BOREN bit is o    | disabled                   |

|                     |                                       |                      | the SBOREN b<br>dware; SBORE          | •                 | Ч                |                   |                            |

|                     |                                       |                      | ·                                     |                   |                  |                   |                            |

|                     | The MCLRE fuse                        |                      |                                       |                   |                  | node entry. This  | s prevents a               |

|                     | user from accider                     |                      |                                       |                   | age test entry.  |                   |                            |

|                     | Refer to Table 26-                    |                      |                                       |                   | rogrommod (-     | 1) in all other a | $lowiooo for l^2$          |

|                     | Implemented in 28 functionality to be |                      | nny. This dit pos                     | muon must de p    | rogrammed (=     | ⊥) in all other c | ievices for I <sup>2</sup> |

### **REGISTER 23-6: FPOR: RESET CONFIGURATION REGISTER**

## 23.5 Program Verification and Code Protection

For all devices in the PIC24F16KL402 family, code protection for the Boot Segment is controlled by the BSS<2:0> Configuration bits and the General Segment by the Configuration bit, GSS0. These bits inhibit external reads and writes to the program memory space This has no direct effect in normal execution mode.

Write protection is controlled by bit, BWRP, for the Boot Segment and bit, GWRP, for the General Segment in the Configuration Word. When these bits are programmed to '0', internal write and erase operations to program memory are blocked.

## 23.6 In-Circuit Serial Programming

PIC24F16KL402 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGECx) and data (PGEDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

## 23.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3, MPLAB REAL ICE<sup>™</sup> or PICkit<sup>™</sup> 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx and PGEDx pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGECx, PGEDx and the pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

## 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

## TABLE 26-4: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

Standard Operating Conditions (unless otherwise stated)

Operating temperature ~40°C  $\leq$  TA  $\leq$  +85°C for industrial

$-40^{\circ}C \le TA \le +125^{\circ}C$  for Extended

|              | $-40^{\circ}C \le IA \le +125^{\circ}C$ for Extended |                     |                   |      |      |      |       |            |  |  |

|--------------|------------------------------------------------------|---------------------|-------------------|------|------|------|-------|------------|--|--|

| Param<br>No. | Symbol                                               | Charact             | eristic           | Min  | Тур  | Max  | Units | Conditions |  |  |

| DC18         | Vhlvd                                                | HLVD Voltage on VDD | HLVDL<3:0> = 0000 | _    | 1.85 | 1.94 | V     |            |  |  |

|              |                                                      | Transition          | HLVDL<3:0> = 0001 | 1.81 | 1.90 | 2.00 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 0010 | 1.85 | 1.95 | 2.05 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 0011 | 1.90 | 2.00 | 2.10 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 0100 | 1.95 | 2.05 | 2.15 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 0101 | 2.06 | 2.17 | 2.28 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 0110 | 2.12 | 2.23 | 2.34 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 0111 | 2.24 | 2.36 | 2.48 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 1000 | 2.31 | 2.43 | 2.55 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 1001 | 2.47 | 2.60 | 2.73 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 1010 | 2.64 | 2.78 | 2.92 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 1011 | 2.74 | 2.88 | 3.02 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 1100 | 2.85 | 3.00 | 3.15 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 1101 | 2.96 | 3.12 | 3.28 | V     |            |  |  |

|              |                                                      |                     | HLVDL<3:0> = 1110 | 3.22 | 3.39 | 3.56 | V     |            |  |  |

#### TABLE 26-5: BOR TRIP POINTS

|              | Standard Operating Conditions: 1.8V to 3.6VOperating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                    |           |      |      |       |            |        |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|------|------|-------|------------|--------|--|--|--|

| Param<br>No. | Symbol                                                                                                                                                                      | Characteristic     | Min       | Тур  | Max  | Units | Conditions |        |  |  |  |

| DC19         |                                                                                                                                                                             | BOR Voltage on VDD | BORV = 00 | 1.85 | 2.0  | 2.15  | V          | Note 1 |  |  |  |

|              |                                                                                                                                                                             | Transition         | BORV = 01 | 2.90 | 3.0  | 3.38  | V          |        |  |  |  |

|              |                                                                                                                                                                             |                    | BORV = 10 | 2.53 | 2.7  | 3.07  | V          |        |  |  |  |

|              |                                                                                                                                                                             |                    | BORV = 11 | 1.75 | 1.85 | 2.05  | V          |        |  |  |  |

Note 1: LPBOR re-arms the POR circuit but does not cause a BOR.

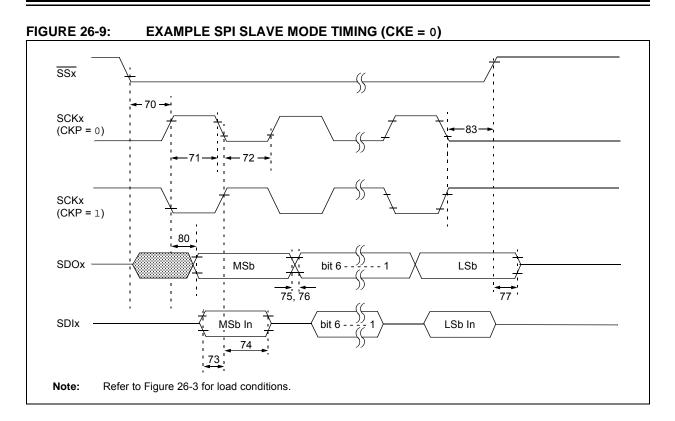

#### TABLE 26-29: EXAMPLE SPI MODE REQUIREMENTS (SLAVE MODE TIMING, CKE = 0)

| Param<br>No. | Symbol                | Characteristic                                                            |                   | Min           | Max | Units | Conditions |

|--------------|-----------------------|---------------------------------------------------------------------------|-------------------|---------------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input |                   | 3 Тсү         |     | ns    |            |

| 70A          | TssL2WB               | SSx to Write to SSPxBUF                                                   |                   | 3 Tcy         | _   | ns    |            |

| 71           | TscH                  | SCKx Input High Time                                                      | Continuous        | 1.25 Tcy + 30 |     | ns    |            |

| 71A          |                       | (Slave mode)                                                              | Single Byte       | 40            |     | ns    | (Note 1)   |

| 72           | TscL                  | SCKx Input Low Time                                                       | Continuous        | 1.25 Tcy + 30 | _   | ns    |            |