Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8КВ (2.75К х 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl302-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.2 Other Special Features

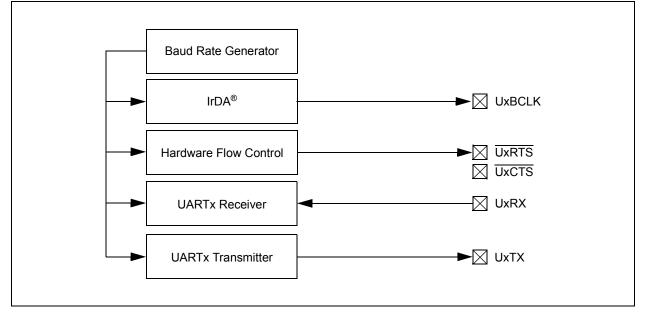

- Communications: The PIC24F16KL402 family incorporates multiple serial communication peripherals to handle a range of application requirements. The MSSP module implements both SPI and I<sup>2</sup>C™ protocols, and supports both Master and Slave modes of operation for each. Devices also include one of two UARTs with built-in IrDA<sup>®</sup> encoders/decoders.

- Analog Features: Select members of the PIC24F16KL402 family include a 10-bit A/D Converter module. The A/D module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, as well as faster sampling speeds.

The comparator modules are configurable for a wide range of operations and can be used as either a single or double comparator module.

# 1.3 Details on Individual Family Members

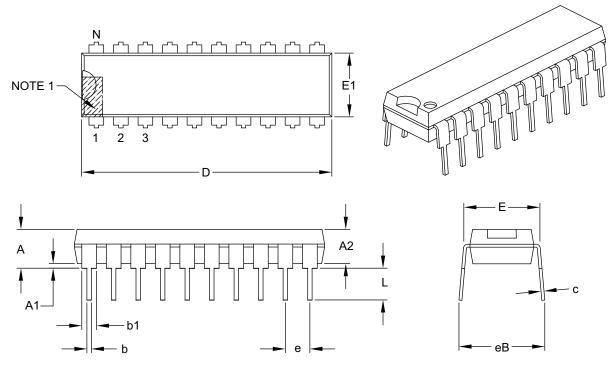

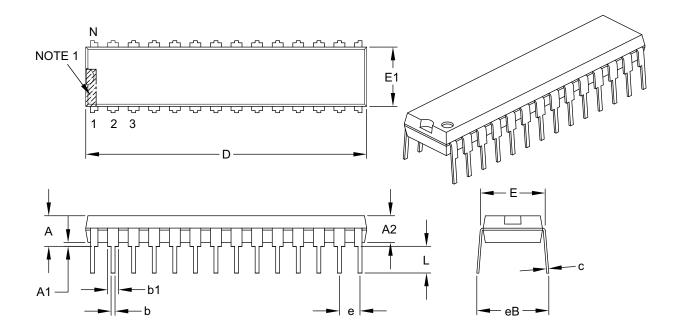

Devices in the PIC24F16KL402 family are available in 14-pin, 20-pin and 28-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The PIC24F16KL402 family may be thought of as four different device groups, each offering a slightly different set of features. These differ from each other in multiple ways:

- · The size of the Flash program memory

- The presence and size of data EEPROM

- The presence of an A/D Converter and the number of external analog channels available

- · The number of analog comparators

- The number of general purpose timers

- The number and type of CCP modules (i.e., CCP vs. ECCP)

- The number of serial communications modules (both MSSPs and UARTs)

The general differences between the different sub-families are shown in Table 1-1. The feature sets for specific devices are summarized in Table 1-2 and Table 1-3.

A list of the individual pin features available on the PIC24F16KL402 family devices, sorted by function, is provided in Table 1-4 (for PIC24FXXKL40X/30X devices) and Table 1-5 (for PIC24FXXKL20X/10X devices). Note that these tables show the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

| Device Group  | Program<br>Memory<br>(bytes) | Data<br>EEPROM<br>(bytes) | Timers<br>(8/16-bit) | CCP and<br>ECCP | Serial<br>(MSSP/<br>UART) | A/D<br>(channels) | Comparators |

|---------------|------------------------------|---------------------------|----------------------|-----------------|---------------------------|-------------------|-------------|

| PIC24FXXKL10X | 4K                           | _                         | 1/2                  | 2/0             | 1/1                       | _                 | 1           |

| PIC24FXXKL20X | 8K                           | —                         | 1/2                  | 2/0             | 1/1                       | 7 or 12           | 1           |

| PIC24FXXKL30X | 8K                           | 256                       | 2/2                  | 2/1             | 2/2                       | —                 | 2           |

| PIC24FXXKL40X | 8K or 16K                    | 512                       | 2/2                  | 2/1             | 2/2                       | 12                | 2           |

#### TABLE 1-1:FEATURE COMPARISON FOR PIC24F16KL402 FAMILY GROUPS

|          |                                  | Pin N         | umber                             |               |     |        |                                                                               |

|----------|----------------------------------|---------------|-----------------------------------|---------------|-----|--------|-------------------------------------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | I/O | Buffer | Description                                                                   |

| CN0      | 10                               | 7             | 12                                | 9             | I   | ST     | Interrupt-on-Change Inputs                                                    |

| CN1      | 9                                | 6             | 11                                | 8             | I   | ST     |                                                                               |

| CN2      | 2                                | 19            | 2                                 | 27            | I   | ST     |                                                                               |

| CN3      | 3                                | 20            | 3                                 | 28            | I   | ST     |                                                                               |

| CN4      | 4                                | 1             | 4                                 | 1             | Ι   | ST     |                                                                               |

| CN5      | 5                                | 2             | 5                                 | 2             | I   | ST     |                                                                               |

| CN6      | 6                                | 3             | 6                                 | 3             | I   | ST     |                                                                               |

| CN7      | _                                | _             | 7                                 | 4             | I   | ST     |                                                                               |

| CN8      | 14                               | 11            | 20                                | 17            | I   | ST     |                                                                               |

| CN9      | —                                | —             | 19                                | 16            | I   | ST     | ]                                                                             |

| CN11     | 18                               | 15            | 26                                | 23            | I   | ST     |                                                                               |

| CN12     | 17                               | 14            | 25                                | 22            | I   | ST     |                                                                               |

| CN13     | 16                               | 13            | 24                                | 21            | I   | ST     |                                                                               |

| CN14     | 15                               | 12            | 23                                | 20            | I   | ST     |                                                                               |

| CN15     | _                                | _             | 22                                | 19            | I   | ST     |                                                                               |

| CN16     | —                                | _             | 21                                | 18            | I   | ST     |                                                                               |

| CN21     | 13                               | 10            | 18                                | 15            | I   | ST     |                                                                               |

| CN22     | 12                               | 9             | 17                                | 14            | I   | ST     |                                                                               |

| CN23     | 11                               | 8             | 16                                | 13            | I   | ST     |                                                                               |

| CN24     | _                                | _             | 15                                | 12            | I   | ST     |                                                                               |

| CN27     | _                                | _             | 14                                | 11            | I   | ST     |                                                                               |

| CN29     | 8                                | 5             | 10                                | 7             | I   | ST     |                                                                               |

| CN30     | 7                                | 4             | 9                                 | 6             | I   | ST     |                                                                               |

| CVREF    | 17                               | 14            | 25                                | 22            | I   | ANA    | Comparator Voltage Reference Output                                           |

| CVREF+   | 2                                | 19            | 2                                 | 27            | I   | ANA    | Comparator Reference Positive Input Voltage                                   |

| CVREF-   | 3                                | 20            | 3                                 | 28            | I   | ANA    | Comparator Reference Negative Input Voltage                                   |

| FLT0     | 17                               | 14            | 25                                | 22            | I   | ST     | ECCP1 Enhanced PWM Fault Input                                                |

| HLVDIN   | 15                               | 12            | 23                                | 20            | I   | ST     | High/Low-Voltage Detect Input                                                 |

| INT0     | 11                               | 8             | 16                                | 13            | I   | ST     | Interrupt 0 Input                                                             |

| INT1     | 17                               | 14            | 25                                | 22            | I   | ST     | Interrupt 1 Input                                                             |

| INT2     | 14                               | 11            | 20                                | 17            | I   | ST     | Interrupt 2 Input                                                             |

| MCLR     | 1                                | 18            | 1                                 | 26            | I   | ST     | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |

| OSCI     | 7                                | 4             | 9                                 | 6             | I   | ANA    | Main Oscillator Input                                                         |

| OSCO     | 8                                | 5             | 10                                | 7             | 0   | ANA    | Main Oscillator Output                                                        |

| P1A      | 14                               | 11            | 20                                | 17            | 0   | —      | ECCP1 Output A (Enhanced PWM Mode)                                            |

| P1B      | 5                                | 2             | 21                                | 18            | 0   | _      | ECCP1 Output B (Enhanced PWM Mode)                                            |

| P1C      | 4                                | 1             | 22                                | 19            | 0   | _      | ECCP1 Output C (Enhanced PWM Mode)                                            |

| P1D      | 16                               | 13            | 18                                | 15            | 0   | _      | ECCP1 Output D (Enhanced PWM Mode)                                            |

| TABLE 1-4: | PIC24F16KL40X/30X FAMILY PINOUT DESCRIPTIONS ( | (CONTINUED) |

|------------|------------------------------------------------|-------------|

|            |                                                |             |

Legend:

TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12    | Bit 11                | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5 | Bit 4                | Bit 3                | Bit 2                | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|-----------|-----------------------|--------|--------|--------|---------|-------|-------|----------------------|----------------------|----------------------|--------|--------|---------------|

| ADC1BUF0     | 0300 |        |        |        |           |                       |        |        | A/D Bu | uffer 0 |       |       |                      |                      |                      |        |        | xxxx          |

| ADC1BUF1     | 0302 |        |        |        |           |                       |        |        | A/D Bu | uffer 1 |       |       |                      |                      |                      |        |        | xxxx          |

| AD1CON1      | 0320 | ADON   | —      | ADSIDL | —         | _                     | _      | FORM1  | FORM0  | SSRC2   | SSRC1 | SSRC0 | _                    |                      | ASAM                 | SAMP   | DONE   | 0000          |

| AD1CON2      | 0322 | VCFG2  | VCFG1  | VCFG0  | OFFCAL    | _                     | CSCNA  |        | _      | r       |       | SMPI3 | SMPI2                | SMPI1                | SMPI0                | r      | ALTS   | 0000          |

| AD1CON3      | 0324 | ADRC   | EXTSAM | PUMPEN | SAMC4     | SAMC3                 | SAMC2  | SAMC1  | SAMC0  |         |       | ADCS5 | ADCS4                | ADCS3                | ADCS2                | ADCS1  | ADCS0  | 0000          |

| AD1CHS       | 0328 | CH0NB  | —      |        | —         | CH0SB3                | CH0SB2 | CH0SB1 | CH0SB0 | CH0NA   |       | _     | _                    | CH0SA3               | CH0SA2               | CH0SA1 | CH0SA0 | 0000          |

| AD1CSSL      | 0330 | CSSL15 | CSSL14 | CSSL13 | CSSL12(1) | CSSL11 <sup>(1)</sup> | CSSL10 | CSSL9  | CSSL8  | CSSL7   | CSSL6 | _     | CSSL4 <sup>(1)</sup> | CSSL3 <sup>(1)</sup> | CSSL2 <sup>(1)</sup> | CSSL1  | CSSL0  | 0000          |

Legend: — = unimplemented, read as '0', r = reserved bit. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 14-pin devices; read as '0'.

#### TABLE 4-14: ANALOG SELECT REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12                | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2                | Bit 1                | Bit 0                | All<br>Resets       |

|-----------|------|--------|--------|--------|-----------------------|--------|--------|-------|-------|-------|-------|-------|-------|----------|----------------------|----------------------|----------------------|---------------------|

| ANCFG     | 04DE | _      | —      | —      | —                     | _      | _      |       | _     | _     | _     |       |       | _        | —                    |                      | VBGEN                | 0000                |

| ANSA      | 04E0 | -      | _      | -      | —                     | _      | -      | _     | _     | _     | _     | _     | _     | ANSA3    | ANSA2                | ANSA1                | ANSA0                | 000F                |

| ANSB      | 04E2 | ANSB15 | ANSB14 | ANSB13 | ANSB12 <sup>(1)</sup> | —      | _      | _     | _     | —     | —     | _     | ANSB4 | ANSB3(2) | ANSB2 <sup>(1)</sup> | ANSB1 <sup>(1)</sup> | ANSB0 <sup>(1)</sup> | F01F <sup>(3)</sup> |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 14-pin devices; read as '0'.

2: These bits are unimplemented in 14-pin and 20-pin devices; read as '0'

3: Reset value for 28-pin devices is shown.

#### TABLE 4-15: COMPARATOR REGISTER MAP

| File<br>Name          | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------------------|------|--------|--------|--------|--------|--------|--------|----------------------|-------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT                | 0630 | CMIDL  | —      | _      |        | _      | _      | C2EVT <sup>(1)</sup> | C1EVT | —      | —      | _     |       | _     | _     | C2OUT | C1OUT | xxxx          |

| CVRCON                | 0632 | _      | _      | _      | _      | _      | _      | _                    | _     | CVREN  | CVROE  | CVRSS | CVR4  | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON                | 0634 | CON    | COE    | CPOL   | CLPWR  | —      | _      | CEVT                 | COUT  | EVPOL1 | EVPOL0 | —     | CREF  | —     | _     | CCH1  | CCH0  | xxxx          |

| CM2CON <sup>(1)</sup> | 0636 | CON    | COE    | CPOL   | CLPWR  | _      | _      | CEVT                 | COUT  | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented in PIC24FXXKL10X/20X devices; read as '0'.

# PIC24F16KL402 FAMILY

#### REGISTER 8-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1                  | R/W-0                  | R/W-0                  |

|--------|-----|-----|-----|-----|------------------------|------------------------|------------------------|

| —      | —   | —   | —   | —   | U2ERIP2 <sup>(1)</sup> | U2ERIP1 <sup>(1)</sup> | U2ERIP0 <sup>(1)</sup> |

| bit 15 |     |     |     |     |                        |                        | bit 8                  |

| U-0   | R/W-1                  | R/W-0                  | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|-------|------------------------|------------------------|------------------------|-----|-----|-----|-------|

| _     | U1ERIP2 <sup>(1)</sup> | U1ERIP1 <sup>(1)</sup> | U1ERIP0 <sup>(1)</sup> |     |     | —   | —     |

| bit 7 |                        |                        |                        |     |     |     | bit 0 |

| Legend:      |            |                                 |                                |                    |

|--------------|------------|---------------------------------|--------------------------------|--------------------|

| R = Readat   | ole bit    | W = Writable bit                | U = Unimplemented bit,         | read as '0'        |

| -n = Value a | at POR     | '1' = Bit is set                | '0' = Bit is cleared           | x = Bit is unknown |

|              |            |                                 |                                |                    |

| bit 15-11    | -          | nented: Read as '0'             |                                |                    |

| bit 10-8     | U2ERIP<2   | 2:0>: UART2 Error Interrupt     | t Priority bits <sup>(1)</sup> |                    |

|              | 111 = Inte | errupt is Priority 7 (highest p | priority interrupt)            |                    |

|              | •          |                                 |                                |                    |

|              | •          |                                 |                                |                    |

|              | •          |                                 |                                |                    |

|              |            | errupt is Priority 1            |                                |                    |

|              |            | errupt source is disabled       |                                |                    |

| bit 7        | -          | nented: Read as '0'             |                                |                    |

| bit 6-4      | U1ERIP<    | 2:0>: UART1 Error Interrupt     | t Priority bits <sup>(1)</sup> |                    |

|              | 111 = Inte | errupt is Priority 7 (highest p | priority interrupt)            |                    |

|              | •          |                                 |                                |                    |

|              | •          |                                 |                                |                    |

|              | •          |                                 |                                |                    |

|              |            | errupt is Priority 1            |                                |                    |

|              |            | errupt source is disabled       |                                |                    |

| bit 3-0      | Unimplen   | nented: Read as '0'             |                                |                    |

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

# 8.4 Interrupt Setup Procedures

#### 8.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS Control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and the type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits, for all enabled interrupt sources, may be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized, such that all user interrupt sources are assigned to Priority Level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 8.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (i.e., C or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

# 8.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 8.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, OEh, with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period. Level 7 interrupt sources are not disabled by the DISI instruction.

# PIC24F16KL402 FAMILY

# REGISTER 9-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REGISTER      | 9-4: REFU                                                                                                                                                                                                                     | CON: REFER                                                                                                                                                                                                                                                                                                                   | KENCE USC                                                                                                                                                                              | ILLATOR CC        | INTROL REC       | 515TER          |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|---------------|

| bit 15       bit 5         U-0       U-0       U-0       U-0       U-0       U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0         | U-0                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                  | R/W-0             | R/W-0            | R/W-0           | R/W-0         |

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ROEN          | —                                                                                                                                                                                                                             | ROSSLP                                                                                                                                                                                                                                                                                                                       | ROSEL                                                                                                                                                                                  | RODIV3            | RODIV2           | RODIV1          | RODIV0        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 15        |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 | bit 8         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 |               |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       0       = Reference oscillator output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference oscillator is disabled in Sleep       0 = Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         111 = Base clock value divid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0           | 0-0                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                    | 0-0               | 0-0              | 0-0             | U-0           |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       1 = Reference oscillator continues to run in Sleep       0 = Reference oscillator continues to run in Sleep         0 = Reference oscillator is disabled in Sleep       0 = Reference oscillator is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         111 = Base clock value divided by 32,768       1100 = Base clock value divided by 4,966         1101 = Base clock value divided by 4,096       1011 = Base clock value divided by 1,024         1000 = Base clock value divided by 1,024       1001 = Base clock value divided by 128         0111 = Base clock value di                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                                                                                                                                                                                                                               | _                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                        | _                 | _                | _               |               |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       0'       Bit 13       ROSSLP: Reference Oscillator Output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference Oscillator Source Select bit       1 = Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock (*1)       0 = System clock is used as the base clock reflects any clock switching of the device         bit 11-8       RODIV-3:0>: Reference Oscillator Divisor Select bits       1111 = Base clock value divided by 32,768         1110 = Base clock value divided by 10:       100 = Base clock value divided by 10:       100 = Base clock value divided by 2,048         1011 = Base clock value divided by 20:       100 = Base clock value divided by 256       111 = Base clock value divided by 22:         0100 = Base clock value divided by 10:       011 = Base clock value divided by 10:       011 = Base clock value divided by 12:         0100 = Base clock value divided by 10:       011 = Base clock value divided by 22:       0100 = Base clock value divided by 22:         0100 = Base clock value divided by 16:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 | DILU          |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       1       ROSSLP: Reference Oscillator Output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference Oscillator Source Select bit       1 = Reference oscillator is used as the base clock '1)         0 = System clock is used as the base clock '10       0 = System clock value divided by 32,768       1111 = Base clock value divided by 4,096         1111 = Base clock value divided by 10,384       100 = Base clock value divided by 1,024       100 = Base clock value divided by 1,024         100 = Base clock value divided by 128       010 = Base clock value divided by 128       010 = Base clock value divided by 128         010 = Base clock value divided by 16       011 = Base clock value divided by 128       010 = Base clock value divided by 128         010 = Base clock value divided by 16       011 = Base clock value divided by 16       011 = Base clock value divided by 128         010 = Base clock value divided by 16       011 = Base clock value divided by 18       010 = Base clock value divided by 18         010 = Base clock value divided by 16       011 = Base clock value divided by 18       010 = Base clock value divided by 18         010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Legend:       |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 |               |

| bit 15 <b>ROEN:</b> Reference Oscillator Output Enable bit<br>1 = Reference oscillator is enabled on REFO pin<br>0 = Reference oscillator is disabled<br>bit 14 <b>Unimplemented:</b> Read as '0'<br>bit 13 <b>ROSSLP:</b> Reference Oscillator Output Stop in Sleep bit<br>1 = Reference oscillator continues to run in Sleep<br>0 = Reference oscillator is disabled in Sleep<br>bit 12 <b>ROSEL:</b> Reference Oscillator Source Select bit<br>1 = Primary oscillator is used as the base clock <sup>(1)</sup><br>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br>bit 11-8 <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 22,768<br>1110 = Base clock value divided by 4,192<br>1100 = Base clock value divided by 4,192<br>1100 = Base clock value divided by 1,192<br>1100 = Base clock value divided by 1,024<br>1011 = Base clock value divided by 1,28<br>0110 = Base clock value divided by 2,208<br>0110 = Base clock value divided by 1,28<br>0110 = Base clock value divided by 2,208<br>0110 = Base clock | R = Readabl   | le bit                                                                                                                                                                                                                        | W = Writable I                                                                                                                                                                                                                                                                                                               | oit                                                                                                                                                                                    | U = Unimplen      | nented bit, read | d as '0'        |               |

| <ul> <li>1 = Reference oscillator is enabled on REFO pin<br/>0 = Reference oscillator is disabled</li> <li>bit 14 Unimplemented: Read as '0'</li> <li>bit 13 ROSSLP: Reference Oscillator Output Stop in Sleep bit<br/>1 = Reference oscillator is disabled in Sleep<br/>0 = Reference oscillator is disabled in Sleep</li> <li>bit 12 ROSEL: Reference Oscillator Source Select bit<br/>1 = Primary oscillator is used as the base clock<sup>(1)</sup><br/>0 = System clock is used as the base clock (1)<br/>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br/>bit 11-8 RODIV-3:0&gt;: Reference Oscillator Divisor Select bits</li> <li>111 = Base clock value divided by 32,768</li> <li>1110 = Base clock value divided by 8,192</li> <li>1100 = Base clock value divided by 4,096</li> <li>1011 = Base clock value divided by 1,024</li> <li>1001 = Base clock value divided by 512</li> <li>1000 = Base clock value divided by 256</li> <li>0111 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 20</li> <li>010 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 26</li> <li>011 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 2</li> <li>011 = Base clock value divided by 2</li> <li>011 = Base clock</li></ul>                                                                                  | -n = Value at | t POR                                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                        | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |

| 1 = Reference oscillator continues to run in Sleep         0 = Reference oscillator is disabled in Sleep         bit 12 <b>ROSEL:</b> Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock; the base clock reflects any clock switching of the device         bit 11-8 <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits         111 = Base clock value divided by 32,768         110 = Base clock value divided by 16,384         100 = Base clock value divided by 4,096         1011 = Base clock value divided by 1,024         1001 = Base clock value divided by 1,024         1001 = Base clock value divided by 128         110 = Base clock value divided by 128         111 = Base clock value divided by 32         100 = Base clock value divided by 32         100 = Base clock value divided by 32         100 = Base clock value divided by 32         110 = Base clock value divided by 4         101 = Base clock value divided by 128         111 = Base clock value divided by 32         110 = Base clock value divided by 4         111 = Base clock value divided by 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               | 1 = Reference<br>0 = Reference                                                                                                                                                                                                | e oscillator is er<br>e oscillator is di                                                                                                                                                                                                                                                                                     | nabled on REF<br>sabled                                                                                                                                                                |                   |                  |                 |               |

| 1 = Reference oscillator continues to run in Sleep         0 = Reference oscillator is disabled in Sleep         bit 12 <b>ROSEL:</b> Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock; the base clock reflects any clock switching of the device         bit 11-8 <b>RODIV-3:0&gt;:</b> Reference Oscillator Divisor Select bits         1111 = Base clock value divided by 32,768         1100 = Base clock value divided by 16,384         1101 = Base clock value divided by 4,096         1011 = Base clock value divided by 1,024         1001 = Base clock value divided by 1,024         1001 = Base clock value divided by 1,024         1001 = Base clock value divided by 128         0110 = Base clock value divided by 128         0110 = Base clock value divided by 32         0101 = Base clock value divided by 32         0100 = Base clock value divided by 32         0101 = Base clock value divided by 40         0111 = Base clock value divided by 16         0111 = Base clock v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 13        | -                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        | o in Sleep bit    |                  |                 |               |

| bit 12 ROSEL: Reference Oscillator Source Select bit<br>1 = Primary oscillator is used as the base clock <sup>(1)</sup><br>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br>bit 11-8 RODIV<3:0>: Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 32,768<br>1110 = Base clock value divided by 4,096<br>1011 = Base clock value divided by 4,096<br>1011 = Base clock value divided by 2,048<br>1010 = Base clock value divided by 1,024<br>1001 = Base clock value divided by 512<br>1000 = Base clock value divided by 256<br>0111 = Base clock value divided by 128<br>0110 = Base clock value divided by 32<br>1000 = Base clock value divided by 44<br>011 = Base clock value divided by 32<br>0100 = Base clock value divided by 4<br>011 = Base clock value divided by 4<br>010 = Base clock value divided by 266<br>0111 = Base clock value divided by 4<br>0101 = Base clock value divided by 4<br>0101 = Base clock value divided by 4<br>0101 = Base clock value divided by 32<br>0100 = Base clock value divided by 4<br>001 = Base clock value divided by 2<br>000 = Base clock value divided by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                                                      | -                 |                  |                 |               |

| 1 = Primary oscillator is used as the base clock <sup>(1)</sup><br>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br>bit 11-8 <b>RODIV-3:0&gt;:</b> Reference Oscillator Divisor Select bits 1111 = Base clock value divided by 32,768 1100 = Base clock value divided by 4,096 1011 = Base clock value divided by 4,096 1011 = Base clock value divided by 1,024 1000 = Base clock value divided by 512 1000 = Base clock value divided by 128 0110 = Base clock value divided by 256 0111 = Base clock value divided by 4 000 = Base clock value divided by 4 010 = Base cloc                                                                                                                                                                                                                                                                                                                                                                                                                            |               | 0 = Reference                                                                                                                                                                                                                 | e oscillator is di                                                                                                                                                                                                                                                                                                           | sabled in Slee                                                                                                                                                                         | p                 |                  |                 |               |

| 0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br>bit 11-8 RODIV<3:0>: Reference Oscillator Divisor Select bits 1111 = Base clock value divided by 32,768 1100 = Base clock value divided by 16,384 1101 = Base clock value divided by 4,096 1011 = Base clock value divided by 2,048 1010 = Base clock value divided by 1,024 1001 = Base clock value divided by 512 1000 = Base clock value divided by 256 0111 = Base clock value divided by 44 0101 = Base clock value divided by 42 0101 = Base clock value divided by 42 0101 = Base clock value divided by 42 0101 = Base clock value divided by 4 0                                                                                                                                  | bit 12        |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 |               |

| bit 11-8 <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 32,768<br>1110 = Base clock value divided by 16,384<br>1101 = Base clock value divided by 8,192<br>1100 = Base clock value divided by 2,048<br>1010 = Base clock value divided by 1,024<br>1001 = Base clock value divided by 512<br>1000 = Base clock value divided by 256<br>0111 = Base clock value divided by 128<br>0110 = Base clock value divided by 32<br>0101 = Base clock value divided by 32<br>0101 = Base clock value divided by 4<br>001 = Base clock value divided by 2<br>0000 = Base clock value divided by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   | ck reflects anv  | clock switching | of the device |