Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 256 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | -                                                                             |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl302t-i-so |

TABLE 1-4: PIC24F16KL40X/30X FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  | Pin N         | umber                             |               |     |                  |                                           |

|----------|----------------------------------|---------------|-----------------------------------|---------------|-----|------------------|-------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | I/O | Buffer           | Description                               |

| PGEC1    | 5                                | 2             | 5                                 | 2             | I/O | ST               | ICSP™ Clock 1                             |

| PCED1    | 4                                | 1             | 4                                 | 1             | I/O | ST               | ICSP Data 1                               |

| PGEC2    | 2                                | 19            | 22                                | 19            | I/O | ST               | ICSP Clock 2                              |

| PGED2    | 3                                | 20            | 21                                | 18            | I/O | ST               | ICSP Data 2                               |

| PGEC3    | 10                               | 7             | 15                                | 12            | I/O | ST               | ICSP Clock 3                              |

| PGED3    | 9                                | 6             | 14                                | 11            | I/O | ST               | ICSP Data 3                               |

| RA0      | 2                                | 19            | 2                                 | 27            | I/O | ST               | PORTA Pins                                |

| RA1      | 3                                | 20            | 3                                 | 28            | I/O | ST               |                                           |

| RA2      | 7                                | 4             | 9                                 | 6             | I/O | ST               |                                           |

| RA3      | 8                                | 5             | 10                                | 7             | I/O | ST               |                                           |

| RA4      | 10                               | 7             | 12                                | 9             | I/O | ST               |                                           |

| RA5      | 1                                | 18            | 1                                 | 26            | I   | ST               |                                           |

| RA6      | 14                               | 11            | 20                                | 17            | I/O | ST               |                                           |

| RA7      | _                                | _             | 19                                | 16            | I/O | ST               |                                           |

| RB0      | 4                                | 1             | 4                                 | 1             | I/O | ST               | PORTB Pins                                |

| RB1      | 5                                | 2             | 5                                 | 2             | I/O | ST               |                                           |

| RB2      | 6                                | 3             | 6                                 | 3             | I/O | ST               |                                           |

| RB3      | _                                | _             | 7                                 | 4             | I/O | ST               |                                           |

| RB4      | 9                                | 6             | 11                                | 8             | I/O | ST               |                                           |

| RB5      | _                                | _             | 14                                | 11            | I/O | ST               |                                           |

| RB6      | _                                | _             | 15                                | 12            | I/O | ST               |                                           |

| RB7      | 11                               | 8             | 16                                | 13            | I/O | ST               |                                           |

| RB8      | 12                               | 9             | 17                                | 14            | I/O | ST               |                                           |

| RB9      | 13                               | 10            | 18                                | 15            | I/O | ST               |                                           |

| RB10     | _                                | _             | 21                                | 18            | I/O | ST               |                                           |

| RB11     | _                                | _             | 22                                | 19            | I/O | ST               |                                           |

| RB12     | 15                               | 12            | 23                                | 20            | I/O | ST               |                                           |

| RB13     | 16                               | 13            | 24                                | 21            | I/O | ST               |                                           |

| RB14     | 17                               | 14            | 25                                | 22            | I/O | ST               |                                           |

| RB15     | 18                               | 15            | 26                                | 23            | I/O | ST               |                                           |

| REFO     | 18                               | 15            | 26                                | 23            | 0   | _                | Reference Clock Output                    |

| SCK1     | 15                               | 12            | 22                                | 19            | I/O | ST               | MSSP1 SPI Serial Input/Output Clock       |

| SCK2     | 18                               | 15            | 14                                | 11            | I/O | ST               | MSSP2 SPI Serial Input/Output Clock       |

| SCL1     | 12                               | 9             | 17                                | 14            | I/O | I <sup>2</sup> C | MSSP1 I <sup>2</sup> C Clock Input/Output |

| SCL2     | 18                               | 15            | 7                                 | 4             | I/O | I <sup>2</sup> C | MSSP2 I <sup>2</sup> C Clock Input/Output |

| SCLKI    | 10                               | 7             | 12                                | 9             | I   | ST               | Digital Secondary Clock Input             |

| SDA1     | 13                               | 10            | 18                                | 15            | I/O | I <sup>2</sup> C | MSSP1 I <sup>2</sup> C Data Input/Output  |

| SDA2     | 2                                | 19            | 2                                 | 27            | I/O | I <sup>2</sup> C | MSSP2 I <sup>2</sup> C Data Input/Output  |

| SDI1     | 17                               | 14            | 21                                | 18            | I   | ST               | MSSP1 SPI Serial Data Input               |

| SDI2     | 2                                | 19            | 19                                | 16            | I   | ST               | MSSP2 SPI Serial Data Input               |

| SDO1     | 16                               | 13            | 24                                | 21            | 0   | _                | MSSP1 SPI Serial Data Output              |

| SDO2     | 3                                | 20            | 15                                | 12            | 0   |                  | MSSP2 SPI Serial Data Output              |

**Legend:** TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer I<sup>2</sup>C = I<sup>2</sup>C™/SMBus input buffer

FIGURE 3-2: PROGRAMMER'S MODEL 15 0 W0 (WREG) **Divider Working Registers** W2 Multiplier Registers W3 W4 W5 W6 W7 Working/Address Registers W8 W9 W10 W11 W12 W13 W14 Frame Pointer W15 Stack Pointer 0 Stack Pointer Limit **SPLIM** 0 Value Register PC 0 **Program Counter** 0 Table Memory Page Address Register **TBLPAG** Program Space Visibility **PSVPAG** Page Address Register 15 REPEAT Loop Counter **RCOUNT** Register 15 SRH SRL ALU STATUS Register (SR) ra n ov CPU Control Register (CORCON) Registers or bits are shadowed for  ${\tt PUSH.S}$  and  ${\tt POP.S}$  instructions.

#### 8.0 INTERRUPT CONTROLLER

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Interrupt Controller, refer to the "dsPIC33/PIC24 Family Reference Manual", "Interrupts" (DS39707).

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. It has the following features:

- Up to eight processor exceptions and software traps

- · Seven user-selectable priority levels

- · Interrupt Vector Table (IVT) with up to 118 vectors

- Unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- · Fixed interrupt entry and return latencies

#### 8.1 Interrupt Vector Table (IVT)

The IVT is shown in Figure 8-1. The IVT resides in the program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of eight non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

PIC24F16KL402 family devices implement 32 non-maskable traps and unique interrupts; these are summarized in Table 8-1 and Table 8-2.

# 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE (AIVT)

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

#### 8.2 Reset Sequence

A device Reset is not a true exception, because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset, which forces the Program Counter (PC) to zero. The microcontroller then begins program execution at location, 000000h. The user programs a GOTO instruction at the Reset address, which redirects the program execution to the appropriate start-up routine.

Note:

Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 8-18: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

|--------|-------|-------|-------|-----|---------|---------|---------|

| _      | T2IP2 | T2IP1 | T2IP0 | _   | CCP2IP2 | CCP2IP1 | CCP2IP0 |

| bit 15 |       |       |       |     |         |         | bit 8   |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 **T2IP<2:0>:** Timer2 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 **CCP2IP<2:0>:** Capture/Compare/PWM2 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

-

\_

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7-0 **Unimplemented:** Read as '0'

#### 11.3 Input Change Notification

The Input Change Notification (ICN) function of the I/O ports allows the PIC24F16KL402 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 23 external signals that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the Change Notification (CN) module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to Vss, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately, using the CNPD1 and CNPD2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to Vss by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

Note:

Pull-ups and pull-downs on Change Notification pins should always be disabled whenever the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE (ASSEMBLY LANGUAGE)

```

MOV #0xFF00, W0 ; Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs

MOV W0, TRISB

MOV #0x00FF, W0 ; Enable PORTB<15:8> digital input buffers

MOV W0, ANSB

NOP ; Delay 1 cycle

BTSS PORTB, #13 ; Next Instruction

```

#### **EXAMPLE 11-2: PORT WRITE/READ EXAMPLE (C LANGUAGE)**

```

TRISB = 0xFF00; // Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs

ANSB = 0x00FF; // Enable PORTB<15:8> digital input buffers

NOP(); // Delay 1 cycle

if(PORTBbits.RB13 == 1) // execute following code if PORTB pin 13 is set.

{

}

```

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                 |

|--------|-----|-------|-----|-----|-----|-----------------------|-----------------------|

| TON    | _   | TSIDL | _   | _   | _   | T1ECS1 <sup>(1)</sup> | T1ECS0 <sup>(1)</sup> |

| bit 15 |     |       |     |     |     |                       | bit 8                 |

| U-0   | R/W-0 | R/W-0  | R/W-0  | U-0 | R/W-0 | R/W-0 | U-0   |

|-------|-------|--------|--------|-----|-------|-------|-------|

| _     | TGATE | TCKPS1 | TCKPS0 | _   | TSYNC | TCS   | _     |

| bit 7 |       |        |        |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 TON: Timer1 On bit

1 = Starts 16-bit Timer1

0 = Stops 16-bit Timer1

bit 14 Unimplemented: Read as '0'

bit 13 TSIDL: Timer1 Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-10 **Unimplemented:** Read as '0'

bit 9-8 T1ECS <1:0>: Timer1 Extended Clock Select bits<sup>(1)</sup>

11 = Reserved; do not use

10 = Timer1 uses the LPRC as the clock source

01 = Timer1 uses the external clock from T1CK

00 = Timer1 uses the Secondary Oscillator (SOSC) as the clock source

bit 7 **Unimplemented:** Read as '0'

bit 6 TGATE: Timer1 Gated Time Accumulation Enable bit

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation is enabled0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timer1 Input Clock Prescale Select bits

11 = 1:256

10 = 1:64

01 = 1:8

00 = 1:1

bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer1 External Clock Input Synchronization Select bit

When TCS = 1:

1 = Synchronizes external clock input

0 = Does not synchronize external clock input

When TCS = 0: This bit is ignored.

bit 1 TCS: Timer1 Clock Source Select bit

1 = Timer1 clock source is selected by T1ECS<1:0>

0 = Internal clock (Fosc/2)

bit 0 **Unimplemented:** Read as '0'

**Note 1:** The T1ECSx bits are valid only when TCS = 1.

#### REGISTER 14-1: T3CON: TIMER3 CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | U-0 | R/W-0  |

|---------|---------|---------|---------|---------|--------|-----|--------|

| TMR3CS1 | TMR3CS0 | T3CKPS1 | T3CKPS0 | T3OSCEN | T3SYNC | _   | TMR3ON |

| bit 7   |         |         |         |         |        |     | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-6 TMR3CS<1:0>: Timer3 Clock Source Select bits

11 = Low-Power RC Oscillator (LPRC)

10 = External clock source (selected by T3CON<3>)

01 = Instruction clock (Fosc/2) 00 = System clock (Fosc)<sup>(1)</sup>

bit 5-4 T3CKPS<1:0>: Timer3 Input Clock Prescale Select bits

11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value

bit 3 T3OSCEN: Timer3 Oscillator Enable bit

1 = SOSC (Secondary Oscillator) is used as a clock source

0 = T3CK digital input pin is used as a clock source

bit 2 T3SYNC: Timer3 External Clock Input Synchronization Control bit

When TMR3CS<1:0> = 1x:

1 = Does not synchronize the external clock input 0 = Synchronizes the external clock input<sup>(2)</sup>

When TMR3CS<1:0> = 0x:

This bit is ignored; Timer3 uses the internal clock.

bit 1 **Unimplemented:** Read as '0' bit 0 **TMR3ON:** Timer3 On bit

1 = Enables Timer3

0 = Stops Timer3

Note 1: The Fosc clock source should not be selected if the timer will be used with the ECCP capture or compare features.

2: This option must be selected when the timer will be used with ECCP/CCP.

#### 18.1 UART Baud Rate Generator (BRG)

The UART module includes a dedicated 16-bit Baud Rate Generator (BRG). The UxBRG register controls the period of a free-running, 16-bit timer. Equation 18-1 provides the formula for computation of the baud rate with BRGH = 0.

## EQUATION 18-1: UARTX BAUD RATE WITH BRGH = $0^{(1)}$

Baud Rate =

$$\frac{FCY}{16 \cdot (UxBRG + 1)}$$

$$UxBRG = \frac{FCY}{16 \cdot Baud Rate} - 1$$

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

Example 18-1 provides the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is Fcy/16 (for UxBRG = 0) and the minimum baud rate possible is Fcy/(16 \* 65536).

Equation 18-2 shows the formula for computation of the baud rate with BRGH = 1.

### EQUATION 18-2: UARTX BAUD RATE WITH BRGH = 1<sup>(1)</sup>

Baud Rate =

$$\frac{FCY}{4 \cdot (UxBRG + 1)}$$

$$UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$$

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is Fcy/4 (for UxBRG = 0) and the minimum baud rate possible is Fcy/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

### EXAMPLE 18-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

Desired Baud Rate = FCY/(16 (UxBRG + 1))

Solving for UxBRG Value:

UxBRG = ((FCY/Desired Baud Rate)/16) - 1

UxBRG = ((4000000/9600)/16) - 1

UxBRG = 25

Calculated Baud Rate = 4000000/(16(25+1))

= 9615

Error = (Calculated Baud Rate – Desired Baud Rate)

Desired Baud Rate = (9615 – 9600)/9600

= 0.16%

Note 1: Based on FcY = Fosc/2; Doze mode and PLL are disabled.

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0  | U-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup> |

|--------|-----|-------|---------------------|-------|-----|----------------------|----------------------|

| UARTEN | _   | USIDL | IREN <sup>(1)</sup> | RTSMD | _   | UEN1                 | UEN0                 |

| bit 15 |     |       |                     |       |     |                      | bit 8                |

| R/C-0, HC | R/W-0  | R/W-0, HC | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0 |

|-----------|--------|-----------|-------|-------|--------|--------|-------|

| WAKE      | LPBACK | ABAUD     | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL |

| bit 7     |        |           |       |       |        |        | bit 0 |

| Legend:           | C = Clearable bit | HC = Hardware Clearable bit        |                    |  |

|-------------------|-------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15 **UARTEN:** UARTx Enable bit

1 = UARTx is enabled; all UARTx pins are controlled by UARTx as defined by UEN<1:0>

0 = UARTx is disabled; all UARTx pins are controlled by port latches, UARTx power consumption is minimal

bit 14 Unimplemented: Read as '0'

bit 13 USIDL: UARTx Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 IREN: IrDA® Encoder and Decoder Enable bit(1)

1 = IrDA encoder and decoder are enabled

0 = IrDA encoder and decoder are disabled

bit 11 RTSMD: Mode Selection for UxRTS Pin bit

$1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

$0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

bit 10 **Unimplemented:** Read as '0'

bit 9-8 **UEN<1:0>:** UARTx Enable bits<sup>(2)</sup>

11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by port latches

10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

01 = UxTX, UxRX and  $\overline{\text{UxRTS}}$  pins are enabled and used;  $\overline{\text{UxCTS}}$  pin is controlled by port latches

00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by port latches

bit 7 WAKE: Wake-up on Start Bit Detect During Sleep Mode Enable bit

1 = UARTx will continue to sample the UxRX pin; interrupt is generated on the falling edge, bit is cleared in hardware on the following rising edge

0 = No wake-up is enabled

bit 6 LPBACK: UARTx Loopback Mode Select bit

1 = Enables Loopback mode

0 = Loopback mode is disabled

bit 5 ABAUD: Auto-Baud Enable bit

1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h); cleared in hardware upon completion

0 = Baud rate measurement is disabled or completed

bit 4 RXINV: Receive Polarity Inversion bit

1 = UxRX Idle state is '0'

0 = UxRX Idle state is '1'

**Note 1:** This feature is is only available for the  $16x BRG \mod (BRGH = 0)$ .

2: Bit availability depends on pin availability.

# 19.0 10-BIT HIGH-SPEED A/D CONVERTER

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 10-Bit High-Speed A/D Converter, refer to the "dsPIC33/PIC24 Family Reference Manual", "10-Bit A/D Converter" (DS39705).

The 10-bit A/D Converter has the following key features:

- · Successive Approximation (SAR) conversion

- · Conversion speeds of up to 500 ksps

- · Up to 12 analog input pins

- · External voltage reference input pins

- · Internal band gap reference input

- · Automatic Channel Scan mode

- · Selectable conversion trigger source

- · Two-word conversion result buffer

- · Selectable Buffer Fill modes

- · Four result alignment options

- · Operation during CPU Sleep and Idle modes

Depending on the particular device, PIC24F16KL402 family devices implement up to 12 analog input pins, designated AN0 through AN4 and AN9 through AN15. In addition, there are two analog input pins for external voltage reference connections (VREF+ and VREF-). These voltage reference inputs may be shared with other analog input pins.

A block diagram of the A/D Converter is displayed in Figure 19-1.

To perform an A/D conversion:

- 1. Configure the A/D module:

- a) Configure port pins as analog inputs and/ or select band gap reference inputs (ANSA<3:0>, ANSB<15:12,4:0> and ANCFG<0>).

- Select the voltage reference source to match the expected range on analog inputs (AD1CON2<15:13>).

- Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- e) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select interrupt rate (AD1CON2<5:2>).

- g) Turn on A/D module (AD1CON1<15>).

- Configure A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select A/D interrupt priority.

#### REGISTER 19-4: **AD1CHS: A/D INPUT SELECT REGISTER**

| R/W-0  | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-----|-----|--------|--------|--------|--------|

| CH0NB  | _   | _   | _   | CH0SB3 | CH0SB2 | CH0SB1 | CH0SB0 |

| bit 15 |     |     |     |        |        |        | bit 8  |

| R/W-0       | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------------|-----|-----|-----|--------|--------|--------|--------|

| CH0NA       | _   | _   | _   | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 |

| bit 7 bit 0 |     |     |     |        |        |        |        |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CH0NB: Channel 0 Negative Input Select for MUX B Multiplexer Setting bit

> 1 = Channel 0 negative input is AN1 0 = Channel 0 negative input is VR-

bit 14-12 Unimplemented: Read as '0'

bit 11-8 CH0SB<3:0>: Channel 0 Positive Input Select for MUX B Multiplexer Setting bits

1111 = AN15

1110 **= AN14**

1101 **= AN13**

1100 = AN12<sup>(1)</sup>

1011 = AN11<sup>(1)</sup> 1010 **= AN10**

1001 **= AN9**

1000 = Upper guardband rail (0.785 \* VDD)

0111 = Lower guardband rail (0.215 \* VDD)

0110 = Internal band gap reference (VBG)

0101 = Reserved; do not use

0100 = AN4<sup>(1)</sup>

$0011 = AN3^{(1)}$

0010 = AN2<sup>(1)</sup>

0001 = AN1

0000 = ANO

bit 7 CHONA: Channel 0 Negative Input Select for MUX A Multiplexer Setting bit

1 = Channel 0 negative input is AN1

0 = Channel 0 negative input is VR-

bit 6-4 Unimplemented: Read as '0'

bit 3-0 CH0SA<3:0>: Channel 0 Positive Input Select for MUX A Multiplexer Setting bits

Bit combinations are identical to those for CH0SB<3:0> (above).

Note 1: Unimplemented on 14-pin devices; do not use.

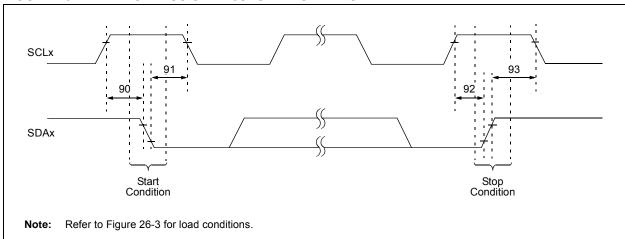

FIGURE 26-11: I<sup>2</sup>C™ BUS START/STOP BITS TIMING

TABLE 26-31: I<sup>2</sup>C™ BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

| Param.<br>No. | Symbol  | Characteristic  |              | Min  | Max | Units | Conditions                   |

|---------------|---------|-----------------|--------------|------|-----|-------|------------------------------|

| 90            | Tsu:sta | Start Condition | 100 kHz mode | 4700 | _   | ns    | Only relevant for Repeated   |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       | Start condition              |

| 91            | THD:STA | Start Condition | 100 kHz mode | 4000 | _   | ns    | After this period, the first |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       | clock pulse is generated     |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode | 4700 | _   | ns    |                              |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       |                              |

| 93            | THD:STO | Stop Condition  | 100 kHz mode | 4000 | _   | ns    |                              |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       |                              |

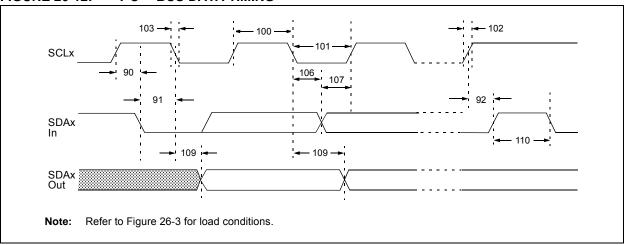

FIGURE 26-12: I<sup>2</sup>C™ BUS DATA TIMING

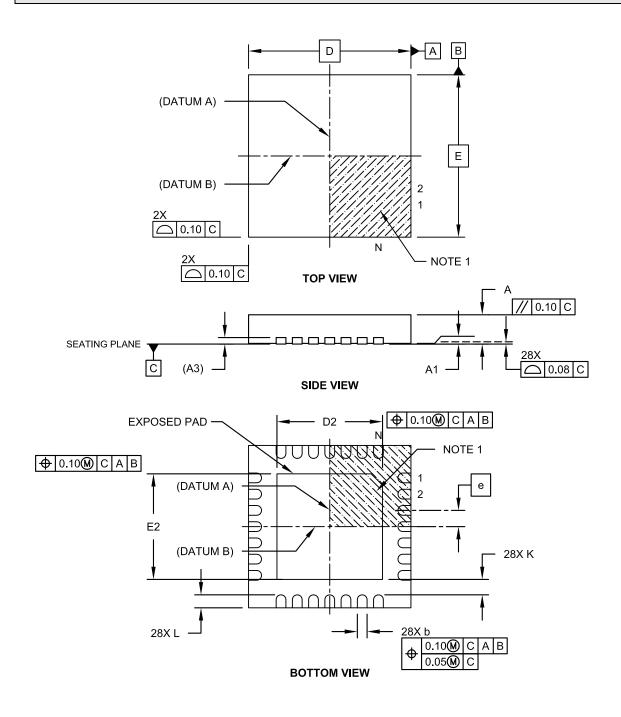

#### 28-Lead Plastic Quad Flat, No Lead Package (MQ) - 5x5x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-140B Sheet 1 of 2

#### APPENDIX A: REVISION HISTORY

#### **Revision A (September 2011)**

Original data sheet for the PIC24F16KL402 family of devices.

#### **Revision B (November 2011)**

Updates DC Specifications in Tables 26-6 through 26-9 (all Typical and Maximum values).

Updates AC Specifications in Tables 26-7 through 26-30 (SPI Timing Requirements) with the addition of the FSCK specification.

Other minor typographic corrections throughout.

#### **Revision C (October 2013)**

Adds +125°C Extended Temperature information.

Updates several packaging drawings in **Section 27.0** "Packaging Information". Other minor typographic corrections throughout.

# APPENDIX B: MIGRATING FROM PIC18/PIC24 TO PIC24F16KL402

The PIC24F16KL402 family combines traditional PIC18 peripherals with a faster PIC24 core to provide a low-cost, high-performance microcontroller with low-power consumption.

Code written for PIC18 devices can be migrated to the PIC24F16KL402 by using a C compiler that generates PIC24 machine level instructions. Assembly language code will need to be rewritten using PIC24 instructions. The PIC24 instruction set shares similarities to the PIC18 instruction set, which should ease porting of assembly code. Application code will require changes to support certain PIC24 peripherals.

Code written for PIC24 devices can be migrated to the PIC24F16KL402 without many code changes. Certain peripherals, however, will require application changes to support modules that were traditionally available only on PIC18 devices.

Refer to Table B-1 for a list of peripheral modules on the PIC24F16KL402 and where they originated from.

TABLE B-1: TABLE B-1: PIC24F16KL402

PERIPHERAL MODULE

ORIGINATING

ARCHITECTURE

| Peripheral Module               | PIC18 | PIC24 |

|---------------------------------|-------|-------|

| ECCP/CCP                        | Х     |       |

| MSSP (I <sup>2</sup> C™/SPI)    | Х     | _     |

| Timer2/4 (8-bit)                | X     | _     |

| Timer3 (16-bit)                 | X     | _     |

| Timer1 (16-bit)                 | _     | X     |

| 10-Bit A/D Converter            | _     | X     |

| Comparator                      | _     | X     |

| Comparator Voltage<br>Reference | _     | Х     |

| UART                            | _     | Х     |

| HLVD                            | _     | Х     |

#### **INDEX**

| A                                           |     | C                                              |            |

|---------------------------------------------|-----|------------------------------------------------|------------|

| A/D                                         |     | C Compilers                                    |            |

| 10-Bit High-Speed A/D Converter             | 157 | MPLAB XC Compilers                             | 188        |

| Conversion Timing Requirements              |     | Capture/Compare/PWM (CCP)                      |            |

| Module Specifications                       |     | CCP/ECCP \( \)                                 |            |

| A/D Converter                               |     | CCP I/O Pins                                   | 125        |

| Analog Input Model                          | 164 | Timer Selection                                | 125        |

| Transfer Function                           |     | Code Examples                                  |            |

| AC Characteristics                          |     | Data EEPROM Bulk Erase                         | 57         |

| A/D Module                                  | 223 | Data EEPROM Unlock Sequence                    | 53         |

| Capacitive Loading Requirements on          |     | Erasing a Program Memory Row,                  |            |

| Output Pins                                 | 209 | Assembly Language                              | 50         |

| Internal RC Oscillator Accuracy             |     | Erasing a Program Memory Row, C Language       |            |

| Internal RC Oscillator Specifications       | 211 | I/O Port Write/Read (Assembly Language)        | 114        |

| Load Conditions and Requirements            | 209 | I/O Port Write/Read (C Language)               |            |

| Temperature and Voltage Specifications      |     | Initiating a Programming Sequence,             |            |

| Assembler                                   |     | Assembly Language                              | 52         |

| MPASM Assembler                             | 188 | Initiating a Programming Sequence, C Language. | 52         |

| B                                           |     | Loading the Write Buffers, Assembly Language   | 51         |

| В                                           |     | Loading the Write Buffers, C Language          | 52         |

| Block Diagrams                              |     | PWRSAV Instruction Syntax                      | 105        |

| 10-Bit High-Speed A/D Converter             | 158 | Reading Data EEPROM Using the                  |            |

| 16-Bit Timer1                               | 115 | TBLRD Command                                  | 58         |

| Accessing Program Memory with               |     | Sequence for Clock Switching                   | 102        |

| Table Instructions                          |     | Single-Word Erase                              | 56         |

| CALL Stack Frame                            |     | Single-Word Write to Data EEPROM               | 57         |

| Capture Mode Operation                      |     | Ultra Low-Power Wake-up Initialization         | 107        |

| Comparator Module                           |     | Code Protection                                | 185        |

| Comparator Voltage Reference Module         |     | Comparator                                     | 167        |

| Compare Mode Operation                      |     | Comparator Voltage Reference                   | 171        |

| CPU Programmer's Model                      | 27  | Configuring                                    | 171        |

| Data Access From Program Space              |     | Configuration Bits                             |            |

| Address Generation                          |     | Core Features                                  | 9          |

| Data EEPROM Addressing with TBLPAG and      |     | CPU                                            |            |

| NVM Registers                               |     | ALU                                            |            |

| Enhanced PWM Mode                           |     | Control Registers                              |            |

| High/Low-Voltage Detect (HLVD) Module       |     | Core Registers                                 |            |

| Individual Comparator Configurations        |     | Programmer's Model                             |            |

| MCLR Pin Connections Example                |     | Customer Change Notification Service           | 257        |

| MSSPx Module (I <sup>2</sup> C Master Mode) | 137 | Customer Notification Service                  |            |

| MSSPx Module (I <sup>2</sup> C Mode)        | 137 | Customer Support                               | 257        |

| MSSPx Module (SPI Mode)                     |     | D                                              |            |

| PIC24F CPU Core                             |     | _                                              |            |

| PIC24F16KL402 Family (General)              |     | Data EEPROM Memory                             |            |

| PSV Operation (Circulified)                 |     | Erasing                                        | 56         |

| PWM Operation (Simplified)                  |     | Nonvolatile Memory Registers                   | E2         |

| Recommended Minimum Connections             |     | NVMCON                                         |            |

| Reset System                                |     | NVMKEY                                         |            |

| Serial ResistorShared I/O Port Structure    |     | NVMADR(U)                                      |            |

|                                             |     | Operations                                     | 55         |

| Simplified UARTx                            |     | Programming                                    | <b>5</b> 7 |

| SPI Master/Slave Connection                 |     | Bulk Erase                                     |            |

| Suggested Placement of Oscillator Circuit   |     | Reading Data EEPROM                            |            |

| System Clock                                |     | Single-Word Write                              | 5/         |

| Table Register Addressing                   |     | Data Memory Address Space                      | 22         |

| Timer2<br>Timer3                            |     | •                                              |            |

| Timer4                                      |     | Memory Map<br>Near Data Space                  |            |

| Watchdog Timer (WDT)                        |     | Organization                                   |            |

| vvalundeg Tillier (vvDT)                    | 104 | SFR Space                                      |            |

|                                             |     | Software Stack                                 |            |

|                                             |     | Space Width                                    |            |

|                                             |     | Opace Width                                    | 55         |

| DC Characteristics                         |          | Inter-Integrated Circuit. See I <sup>2</sup> C. |     |

|--------------------------------------------|----------|-------------------------------------------------|-----|

| BOR Trip Points                            | 202      | Internet Address                                | 257 |

| Comparator                                 | 208      | Interrupt Sources                               |     |

| Comparator Voltage Reference               | 208      | TMR3 Overflow                                   | 119 |

| Data EEPROM Memory                         | 208      | TMR4 to PR4 Match (PWM)                         | 123 |

| High/Low-Voltage Detect                    | 202      | Interrupts                                      |     |

| I/O Pin Input Specifications               | 206      | Alternate Interrupt Vector Table (AIVT)         | 65  |

| I/O Pin Output Specifications              | 207      | Control and Status Registers                    | 68  |

| Idle Current (IDLE)                        | 203      | Implemented Vectors                             | 67  |

| Operating Current (IDD)                    |          | Interrupt Vector Table (IVT)                    | 65  |

| Power-Down Current (IPD)                   | 204, 205 | Reset Sequence                                  | 65  |

| Program Memory                             | 207      | Setup Procedures                                |     |

| Temperature and Voltage Specifications     |          | Trap Vectors                                    |     |

| Demo/Development Boards, Evaluation and    |          | Vector Table                                    | 66  |

| Starter Kits                               | 190      |                                                 |     |

| Development Support                        |          | M                                               |     |

| Third-Party Tools                          |          | Master Synchronous Serial Port (MSSP)           | 135 |

| Device Features for PIC24F16KL20X/10X      |          | I/O Pin Configuration for SPI                   | 135 |

| Devices (Summary)                          | 12       | Microchip Internet Web Site                     |     |

| Device Features for PIC24F16KL40X/30X      |          | MPLAB Assembler, Linker, Librarian              |     |

| Devices (Summary)                          | 11       | MPLAB ICD 3 In-Circuit Debugger                 |     |

| Devices (Gariniary)                        |          | MPLAB PM3 Device Programmer                     |     |

| E                                          |          | MPLAB REAL ICE In-Circuit Emulator System       |     |

| Electrical Characteristics                 |          | MPLAB X Integrated Development                  |     |

| Absolute Maximum Ratings                   | 199      | Environment Software                            | 187 |

| Thermal Operating Conditions               |          | MPLAB X SIM Software Simulator                  |     |

| Thermal Packaging Characteristics          |          | MPLIB Object Librarian                          |     |

| V/F Graph, Extended                        |          | MPLINK Object Linker                            |     |

| V/F Graph, Industrial                      |          | WI LINK Object Linker                           | 100 |

| Enhanced CCP                               |          | N                                               |     |

| Equations                                  | 125      | Near Data Space                                 | 34  |

| A/D Conversion Clock Period                | 164      | Near Bata Opace                                 |     |

| UARTx Baud Rate with BRGH = 0              |          | 0                                               |     |

| UARTX Baud Rate with BRGH = 0              |          | Oscillator Configuration                        |     |

|                                            |          | Clock Switching                                 | 101 |

| Errata                                     | /        | Sequence                                        |     |

| Examples                                   | 450      | Configuration Bit Values for Clock Selection    |     |

| Baud Rate Error Calculation (BRGH = 0)     | 150      | CPU Clocking Scheme                             |     |

| F                                          |          | Initial Configuration on POR                    |     |

| Floob December Manager                     |          | Reference Clock Output                          |     |

| Flash Program Memory                       | 40       | Oscillator, Timer3                              |     |

| Control Registers                          |          | Oscillator, Timers                              | 118 |

| Enhanced ICSP Operation                    |          | Р                                               |     |

| Programming Algorithm                      |          | Packaging                                       |     |

| Programming Operations                     |          | Details                                         | 229 |

| RTSP Operation                             |          | Marking                                         |     |

| Table Instructions                         | 47       |                                                 |     |

| G                                          |          | PICkit 3 In-Circuit Debugger/Programmer         | 109 |

|                                            | 0.4      | Pinout Descriptions                             | 4.0 |

| Getting Started Guidelines for 16-Bit MCUs | 21       | PIC24F16KL20X/10X Devices                       |     |

| Н                                          |          | PIC24F16KL40X/30X Devices                       |     |

|                                            | 470      | Power-Saving                                    |     |

| High/Low-Voltage Detect (HLVD)             | 1/3      | Power-Saving Features                           |     |

| 1                                          |          | Clock Frequency, Clock Switching                |     |

| 10.5                                       |          | Coincident Interrupts                           |     |

| I/O Ports                                  |          | Instruction-Based Modes                         |     |

| Analog Port Configuration                  |          | Idle                                            |     |

| Analog Selection Registers                 |          | Sleep                                           |     |

| Input Change Notification                  |          | Selective Peripheral Control                    |     |

| Open-Drain Configuration                   |          | Ultra Low-Power Wake-up (ULPWU)                 |     |

| Parallel (PIO)                             |          | Product Identification System                   | 259 |

| In-Circuit Debugger                        |          | Program and Data Memory                         |     |

| In-Circuit Serial Programming (ICSP)       | 185      | Access Using Table Instructions                 | 45  |

| Instruction Set                            |          | Program Space Visibility                        |     |

| Opcode Symbols                             | 192      | Program and Data Memory Spaces                  |     |

| Overview                                   |          | Addressing                                      | 43  |

| Summary                                    | 191      | Interfacing                                     |     |

|                                            |          | <u>~</u>                                        |     |