#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 256 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | -                                                                             |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl302t-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Analog Features:**

- 10-Bit, up to 12-Channel Analog-to-Digital (A/D) Converter:

- 500 ksps conversion rate

- Conversion available during Sleep and Idle

- Dual Rail-to-Rail Analog Comparators with Programmable Input/Output Configuration

- On-Chip Voltage Reference

### **Special Microcontroller Features:**

- Operating Voltage Range of 1.8V to 3.6V

- 10,000 Erase/Write Cycle Endurance Flash Program Memory, Typical

- 100,000 Erase/Write Cycle Endurance Data EEPROM, Typical

- Flash and Data EEPROM Data Retention: 40 Years Minimum

- Self-Programmable under Software Control

- Programmable Reference Clock Output

- Fail-Safe Clock Monitor (FSCM) Operation:

- Detects clock failure and switches to on-chip, Low-Power RC (LPRC) oscillator

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT):

- Uses its own Low-Power RC oscillator

- Windowed operating modes

- Programmable period of 2 ms to 131s

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and In-Circuit Emulation (ICE) via 2 Pins

- Programmable High/Low-Voltage Detect (HLVD)

- Programmable Brown-out Reset (BOR):

- Configurable for software controlled operation and shutdown in Sleep mode

- Selectable trip points (1.8V, 2.7V and 3.0V)

- Low-power 2.0V POR re-arm

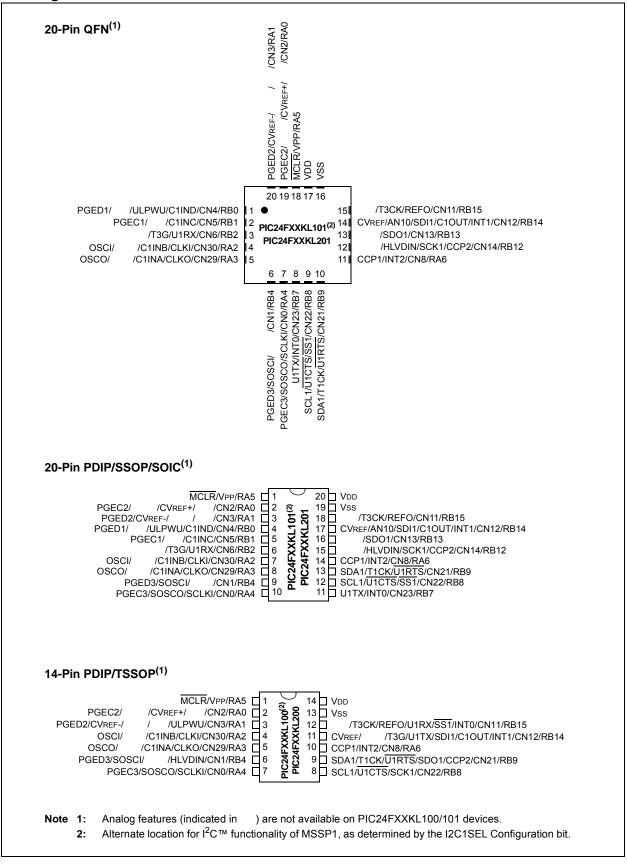

#### Pin Diagrams: PIC24FXXKL10X/20X

### 2.4 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin Input Voltage High (VIH) and Input Voltage Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx) pins, programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 24.0 "Development Support**".

### 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

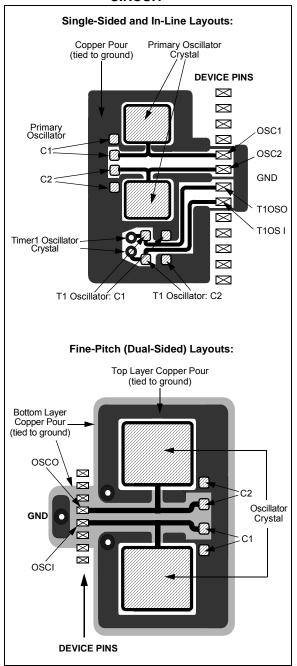

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

#### FIGURE 2-3: S

#### B: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals, in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

| IABLE 4-4: ICN REGISTER MAP | TABLE 4-4: | ICN REGISTER MAP |

|-----------------------------|------------|------------------|

|-----------------------------|------------|------------------|

|    |                          | Bit 15                                             | Bit 14                                                    | Bit 13                                                    | Bit 12                 | Bit 11                                     | Bit 10 | Bit 9                                              | Bit 8                                    | D:4 7                                                                  |                                                         |                                                          |                                                    |               | 1      |        |                                              | All                                                                |

|----|--------------------------|----------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|------------------------|--------------------------------------------|--------|----------------------------------------------------|------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|---------------|--------|--------|----------------------------------------------|--------------------------------------------------------------------|

|    |                          | (4)                                                |                                                           |                                                           |                        |                                            |        | 2.10                                               | DILO                                     | Bit 7                                                                  | Bit 6                                                   | Bit 5                                                    | Bit 4                                              | Bit 3         | Bit 2  | Bit 1  | Bit 0                                        | Resets                                                             |

| '  | 030 011                  | 15PDE <sup>(1)</sup>                               | CN14PDE <sup>(1)</sup>                                    | CN13PDE <sup>(1)</sup>                                    | CN12PDE                | CN11PDE                                    | —      | CN9PDE <sup>(2)</sup>                              | CN8PDE                                   | CN7PDE <sup>(2)</sup>                                                  | CN6PDE(1)                                               | CN5PDE <sup>(1)</sup>                                    | CN4PDE <sup>(1)</sup>                              | CN3PDE        | CN2PDE | CN1PDE | CN0PDE                                       | 0000                                                               |

| 5  | 058                      | _                                                  | CN30PDE                                                   | CN29PDE                                                   | _                      | CN27PDE <sup>(2)</sup>                     | _      | _                                                  | CN24PDE <sup>(2)</sup>                   | CN23PDE <sup>(1)</sup>                                                 | CN22PDE                                                 | CN21PDE                                                  | _                                                  | _             | —      | _      | CN16PDE <sup>(2)</sup>                       | 0000                                                               |

| 5  | 062 CN                   | N15IE <sup>(1)</sup>                               | CN14IE <sup>(1)</sup>                                     | CN13IE <sup>(1)</sup>                                     | CN12IE                 | CN11IE                                     | _      | CN9IE <sup>(1)</sup>                               | CN8IE                                    | CN7IE <sup>(1)</sup>                                                   | CN6IE <sup>(2)</sup>                                    | CN5PIE <sup>(2)</sup>                                    | CN4IE <sup>(2)</sup>                               | CN3IE         | CNIE   | CN1IE  | CN0IE                                        | 0000                                                               |

| ;. | 064                      | _                                                  | CN30IE                                                    | CN29IE                                                    | _                      | CN27IE <sup>(2)</sup>                      | _      | _                                                  | CN24IE <sup>(2)</sup>                    | CN23IE <sup>(1)</sup>                                                  | CN22IE                                                  | CN21IE                                                   | _                                                  | _             | —      | _      | CN16IE <sup>(2)</sup>                        | 0000                                                               |

| 1  | 06E CN1                  | 15PUE <sup>(1)</sup>                               | CN14PUE <sup>(1)</sup>                                    | CN13PUE <sup>(1)</sup>                                    | CN12PUE                | CN11PUE                                    | —      | CN9PUE <sup>(1)</sup>                              | CN8PUE                                   | CN7PUE <sup>(1)</sup>                                                  | CN6PUE <sup>(2)</sup>                                   | CN5PUE <sup>(2)</sup>                                    | CN4PUE <sup>(2)</sup>                              | <b>CN3PUE</b> | CN2PUE | CN1PUE | CN0PUE                                       | 0000                                                               |

| 1  | 070                      | —                                                  | CN30PUE                                                   | CN29PUE                                                   | —                      | CN27PUE <sup>(2)</sup>                     | —      | _                                                  | CN24PUE <sup>(2)</sup>                   | CN23PUE <sup>(1)</sup>                                                 | CN22PUE                                                 | CN21PUE                                                  | —                                                  | _             | —      | _      | CN16PUE <sup>(2)</sup>                       | 0000                                                               |

|    | 062 CN<br>064<br>06E CN1 | N15IE <sup>(1)</sup><br>—<br>N15PUE <sup>(1)</sup> | CN14IE <sup>(1)</sup><br>CN30IE<br>CN14PUE <sup>(1)</sup> | CN13IE <sup>(1)</sup><br>CN29IE<br>CN13PUE <sup>(1)</sup> | CN12IE<br>—<br>CN12PUE | CN11IE<br>CN27IE <sup>(2)</sup><br>CN11PUE |        | CN9IE <sup>(1)</sup><br>—<br>CN9PUE <sup>(1)</sup> | CN8IE<br>CN24IE <sup>(2)</sup><br>CN8PUE | CN7IE <sup>(1)</sup><br>CN23IE <sup>(1)</sup><br>CN7PUE <sup>(1)</sup> | CN6IE <sup>(2)</sup><br>CN22IE<br>CN6PUE <sup>(2)</sup> | CN5PIE <sup>(2)</sup><br>CN21IE<br>CN5PUE <sup>(2)</sup> | CN4IE <sup>(2)</sup><br>—<br>CN4PUE <sup>(2)</sup> |               | _      |        | CN3IE CNIE CN1IE<br><br>CN3PUE CN2PUE CN1PUE | CN3IE         CNIE         CN0IE             CN16IE <sup>(2)</sup> |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 14-pin devices; read as '0'.

2: These bits are unimplemented in 14-pin and 20-pin devices; read as '0'.

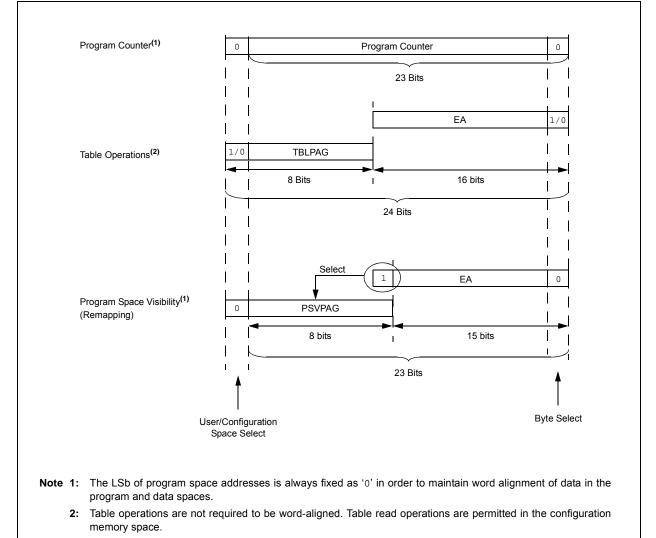

| A                        | Access        | Program Space Address        |             |                                                 |               |                |  |  |  |

|--------------------------|---------------|------------------------------|-------------|-------------------------------------------------|---------------|----------------|--|--|--|

| Access Type              | Space         | <23>                         | <22:16>     | <15>                                            | <14:1>        | <0>            |  |  |  |

| Instruction Access       | User          | 0                            |             | 0                                               |               |                |  |  |  |

| (Code Execution)         |               | 0xx xxxx xxxx xxxx xxxx xxx0 |             |                                                 |               |                |  |  |  |

| TBLRD/TBLWT              | User          | TBI                          | _PAG<7:0>   | Data EA<15:0>                                   |               |                |  |  |  |

| (Byte/Word Read/Write)   |               | د0                           | xxx xxxx    | XXXX XXXX XXXX XXXX                             |               |                |  |  |  |

|                          | Configuration | TBI                          | TBLPAG<7:0> |                                                 | Data EA<15:0> |                |  |  |  |

|                          |               | 12                           | xxx xxxx    | XXX                                             | ***           | xxx            |  |  |  |

| Program Space Visibility | User          | 0                            | PSVPAG<7:   | :0> <sup>(2)</sup> Data EA<14:0> <sup>(1)</sup> |               | :0> <b>(1)</b> |  |  |  |

| (Block Remap/Read)       |               | 0                            | XXXX XXX    | xx                                              | XXX XXXX XXX  | x xxxx         |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) on PIC24F16KL402 family devices.

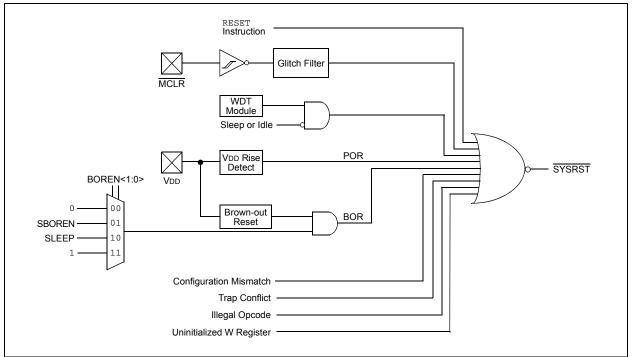

## 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Resets, refer to the "dsPIC33/PIC24 Family Reference Manual", "Reset with Programmable Brown-out Reset" (DS39728).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- · UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on a Power-on Reset (POR) and unchanged by all other Resets.

**Note:** Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A POR will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer (WDT) and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value, after a device Reset, will be meaningful.

### FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

## 8.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Interrupt Controller, refer to the "dsPIC33/PIC24 Family Reference Manual", "Interrupts" (DS39707).

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. It has the following features:

- Up to eight processor exceptions and software traps

- · Seven user-selectable priority levels

- · Interrupt Vector Table (IVT) with up to 118 vectors

- Unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

### 8.1 Interrupt Vector Table (IVT)

The IVT is shown in Figure 8-1. The IVT resides in the program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of eight non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

PIC24F16KL402 family devices implement 32 non-maskable traps and unique interrupts; these are summarized in Table 8-1 and Table 8-2.

#### 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE (AIVT)

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

### 8.2 Reset Sequence

A device Reset is not a true exception, because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset, which forces the Program Counter (PC) to zero. The microcontroller then begins program execution at location, 000000h. The user programs a GOTO instruction at the Reset address, which redirects the program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 8-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0                                                                        | U-0         | U-0                                 | U-0             | U-0           | U-0                   | U-0    | R/W-0  |  |

|----------------------------------------------------------------------------|-------------|-------------------------------------|-----------------|---------------|-----------------------|--------|--------|--|

| _                                                                          | —           | —                                   | —               | —             | —                     | —      | HLVDIE |  |

| bit 15                                                                     |             |                                     |                 |               |                       |        | bit 8  |  |

|                                                                            |             |                                     |                 |               |                       |        |        |  |

| U-0                                                                        | U-0         | U-0                                 | U-0             | U-0           | R/W-0                 | R/W-0  | U-0    |  |

|                                                                            |             | <u> </u>                            |                 | —             | U2ERIE <sup>(1)</sup> | U1ERIE |        |  |

| bit 7                                                                      |             |                                     |                 |               |                       |        | bit 0  |  |

|                                                                            |             |                                     |                 |               |                       |        |        |  |

| Legend:                                                                    |             |                                     |                 |               |                       |        |        |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |             |                                     |                 |               |                       |        |        |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |             |                                     |                 |               |                       |        | nown   |  |

|                                                                            |             |                                     |                 |               |                       |        |        |  |

| bit 15-9                                                                   | Unimplemer  | nted: Read as '                     | 0'              |               |                       |        |        |  |

| bit 8                                                                      | HLVDIE: Hig | h/Low-Voltage                       | Detect Interrup | ot Enable bit |                       |        |        |  |

|                                                                            |             | request is enat                     |                 |               |                       |        |        |  |

|                                                                            | •           | request is not e                    |                 |               |                       |        |        |  |

| bit 7-3                                                                    | Unimplemer  | nted: Read as '                     | 0'              |               |                       |        |        |  |

| bit 2                                                                      | U2ERIE: UA  | RT2 Error Inter                     | rupt Enable bit | (1)           |                       |        |        |  |

|                                                                            |             | request is enat                     |                 |               |                       |        |        |  |

|                                                                            | •           | request is not e                    |                 |               |                       |        |        |  |

| bit 1                                                                      |             | RT1 Error Inter                     | •               |               |                       |        |        |  |

|                                                                            |             | request is enab<br>request is not e |                 |               |                       |        |        |  |

| bit 0                                                                      |             | nted: Read as '                     |                 |               |                       |        |        |  |

|                                                                            |             |                                     |                 |               |                       |        |        |  |

Note 1: This bit is unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

#### REGISTER 8-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0           | U-0       | U-0              | U-0 | U-0               | U-0              | U-0             | U-0     |

|---------------|-----------|------------------|-----|-------------------|------------------|-----------------|---------|

| _             | —         | —                | _   | —                 | —                | —               | —       |

| bit 15        |           |                  |     | -<br>-            |                  |                 | bit 8   |

|               |           |                  |     |                   |                  |                 |         |

| U-0           | U-0       | U-0              | U-0 | U-0               | U-0              | U-0             | R/W-0   |

| —             | —         | —                | —   | —                 | —                | —               | ULPWUIE |

| bit 7         |           |                  |     |                   |                  |                 | bit 0   |

|               |           |                  |     |                   |                  |                 |         |

| Legend:       |           |                  |     |                   |                  |                 |         |

| R = Readable  | e bit     | W = Writable     | bit | U = Unimplem      | nented bit, read | l as '0'        |         |

| -n = Value at | POR       | '1' = Bit is set |     | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| <u>.</u>      |           |                  |     |                   |                  |                 |         |

| bit 15-1      | Unimpleme | nted: Read as '  | o'  |                   |                  |                 |         |

| L:1 0         |           |                  | A   |                   |                  |                 |         |

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable Bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

## **10.0 POWER-SAVING FEATURES**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Power-Saving Features, refer to the "dsPIC33/PIC24 Family Reference Manual", "Power-Saving Features with Deep Sleep" (DS39727).

The PIC24F16KL402 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption using several strategies:

- Clock frequency

- · Instruction-based Idle and Sleep modes

- · Hardware-based periodic wake-up from Sleep

- · Software Controlled Doze mode

- · Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

#### 10.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

#### 10.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation.

The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | SLEEP mode |

|--------|-------------|---|-----|-----|--------|------|------------|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | IDLE mode  |

### 11.3 Input Change Notification

The Input Change Notification (ICN) function of the I/O ports allows the PIC24F16KL402 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 23 external signals that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the Change Notification (CN) module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately, using the CNPD1 and CNPD2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to VSS by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

**Note:** Pull-ups and pull-downs on Change Notification pins should always be disabled whenever the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE (ASSEMBLY LANGUAGE)

| MOV  | #0xFF00, W0 | ; Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|------|-------------|-------------------------------------------------------------|

| MOV  | W0, TRISB   |                                                             |

| MOV  | #0x00FF, W0 | ; Enable PORTB<15:8> digital input buffers                  |

| MOV  | W0, ANSB    |                                                             |

| NOP  |             | ; Delay 1 cycle                                             |

| BTSS | PORTB, #13  | ; Next Instruction                                          |

|      |             |                                                             |

#### EXAMPLE 11-2: PORT WRITE/READ EXAMPLE (C LANGUAGE)

| TRISB = 0xFF00;          | // Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|--------------------------|--------------------------------------------------------------|

| ANSB = $0 \times 00 FF;$ | // Enable PORTB<15:8> digital input buffers                  |

| NOP();                   | // Delay 1 cycle                                             |

| if(PORTBbits.RB13 == 1)  | // execute following code if PORTB pin 13 is set.            |

| {                        |                                                              |

| }                        |                                                              |

NOTES:

## REGISTER 17-5: SSPxCON2: MSSPx CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MODE)

| U-0        | U-0                            | U-0                                | U-0                  | U-0                     | U-0                     | U-0                 | U-0                |

|------------|--------------------------------|------------------------------------|----------------------|-------------------------|-------------------------|---------------------|--------------------|

|            | —                              |                                    | —                    | _                       | —                       | —                   | _                  |

| bit 15     |                                |                                    |                      |                         |                         |                     | bit 8              |

|            |                                |                                    |                      |                         |                         |                     |                    |

| R/W-0      | R/W-0                          | R/W-0                              | R/W-0                | R/W-0                   | R/W-0                   | R/W-0               | R/W-0              |

| GCEN       | ACKSTAT                        | ACKDT <sup>(1)</sup>               | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>     | PEN <sup>(2)</sup>      | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7      |                                |                                    |                      |                         |                         |                     | bit (              |

| Legend:    |                                |                                    |                      |                         |                         |                     |                    |

| R = Reada  | able bit                       | W = Writable                       | bit                  | U = Unimpler            | nented bit, read        | d as '0'            |                    |

| -n = Value |                                | '1' = Bit is set                   |                      | '0' = Bit is cle        |                         | x = Bit is unkn     | nown               |

|            |                                |                                    |                      |                         |                         |                     |                    |

| bit 15-8   | Unimplemen                     | ted: Read as '                     | )'                   |                         |                         |                     |                    |

| bit 7      | GCEN: Gene                     | ral Call Enable                    | bit (Slave mod       | e only)                 |                         |                     |                    |

|            |                                | nterrupt when a                    |                      | ddress (0000h           | ) is received in        | the SSPxSR          |                    |

|            |                                | call address is o                  |                      |                         |                         |                     |                    |

| bit 6      |                                | cknowledge Sta                     | -                    |                         | e only)                 |                     |                    |

|            |                                | edge was not re<br>edge was receiv |                      | ave                     |                         |                     |                    |

| bit 5      |                                | nowledge Data                      |                      | ceive mode on           | <sub>Խ/</sub> (1)       |                     |                    |

| DIL 5      | 1 = No Ackno                   |                                    |                      |                         | iy).                    |                     |                    |

|            | 0 = Acknowle                   | 0                                  |                      |                         |                         |                     |                    |

| bit 4      | ACKEN: Ack                     | nowledge Sequ                      | ience Enable b       | it (Master mod          | le only) <sup>(2)</sup> |                     |                    |

|            |                                |                                    |                      | SDAx and SO             | CLx pins, and           | transmits ACI       | KDT data bit       |

|            |                                | cally cleared by                   |                      |                         |                         |                     |                    |

|            |                                | edge sequence                      |                      | (2)                     |                         |                     |                    |

| bit 3      |                                | ive Enable bit (<br>Receive mode f | _                    | e mode only)-           |                         |                     |                    |

|            | 1 = Enables i<br>0 = Receive i |                                    |                      |                         |                         |                     |                    |

| bit 2      |                                | ondition Enable                    | bit (Master mo       | de only) <sup>(2)</sup> |                         |                     |                    |

| 5.12       |                                | Stop condition o                   |                      |                         | matically cleare        | ed by hardware      |                    |

|            | 0 = Stop cond                  |                                    |                      | 1 /                     | ,                       | ,                   |                    |

| bit 1      | RSEN: Repea                    | ated Start Cond                    | lition Enable bi     | t (Master mode          | e only) <sup>(2)</sup>  |                     |                    |

|            |                                |                                    |                      | DAx and SCLx            | c pins; automat         | ically cleared by   | y hardware         |

|            | -                              | d Start condition                  |                      |                         |                         |                     |                    |

| bit 0      |                                | ondition Enable                    | bit <sup>(2)</sup>   |                         |                         |                     |                    |

|            | Master Mode                    |                                    | n SDAx and S         | CL x nins: auto         | matically cleare        | ed by hardware      |                    |

|            | 0 = Start cond                 |                                    |                      |                         |                         |                     |                    |

|            | Slave Mode:                    |                                    |                      |                         |                         |                     |                    |

|            |                                |                                    |                      | ve transmit and         | d slave receive         | (stretch is enab    | oled)              |

|            | 0 = Clock stre                 | etching is disab                   | led                  |                         |                         |                     |                    |

| Note 1:    | The value that wi              | II be transmitte                   | d when the use       | r initiates an A        | .cknowledge se          | equence at the e    | end of a           |

|            | receive.                       |                                    |                      |                         |                         |                     |                    |

| 2:         | If the I <sup>2</sup> C module |                                    |                      | e set (no spoo          | ling) and the S         | SPxBUF may n        | ot be written      |

|            | (or writes to the S            | SHXROF are d                       | isabled).            |                         |                         |                     |                    |

| R/P-1               | R/P-1                                 | R/P-1                                    | R/P-1                                 | R/P-1             | U-0              | R/P-1             | R/P-1                      |  |  |  |

|---------------------|---------------------------------------|------------------------------------------|---------------------------------------|-------------------|------------------|-------------------|----------------------------|--|--|--|

| MCLRE <sup>(1</sup> | ) BORV1 <sup>(2)</sup>                | BORV0 <sup>(2)</sup>                     | I2C1SEL <sup>(3)</sup>                | PWRTEN            |                  | BOREN1            | BOREN0                     |  |  |  |

| bit 7               |                                       |                                          |                                       |                   |                  |                   | bit C                      |  |  |  |

| Logondi             |                                       |                                          |                                       |                   |                  |                   |                            |  |  |  |

| Legend:             |                                       |                                          |                                       |                   |                  | 1                 |                            |  |  |  |

| R = Reada           |                                       | P = Program                              |                                       | •                 | nented bit, read |                   |                            |  |  |  |

| -n = Value          | at POR                                | '1' = Bit is set                         |                                       | '0' = Bit is clea | ared             | x = Bit is unkr   | nown                       |  |  |  |

| bit 7               |                                       | R Pin Enable                             | hit(1)                                |                   |                  |                   |                            |  |  |  |

|                     |                                       |                                          | A5 input pin is o                     | lisabled          |                  |                   |                            |  |  |  |

|                     |                                       |                                          | ; MCLR is disa                        |                   |                  |                   |                            |  |  |  |

| bit 6-5             | BORV<1:0>:                            | Brown-out Res                            | set Enable bits <sup>(</sup>          | 2)                |                  |                   |                            |  |  |  |

|                     | 11 = Brown-o                          | ut Reset is set                          | to the low trip p                     | point             |                  |                   |                            |  |  |  |

|                     |                                       | ut Reset is set to the middle trip point |                                       |                   |                  |                   |                            |  |  |  |

|                     |                                       |                                          | to the high trip<br>POR is enable ו   |                   |                  | ad)               |                            |  |  |  |

| bit 4               |                                       | -                                        | I <sup>2</sup> C <sup>™</sup> Pin Map | -                 | DON 13 SEIECI    | eu)               |                            |  |  |  |

|                     |                                       |                                          | 1/SDA1 pins (R                        | U U               |                  |                   |                            |  |  |  |

|                     |                                       |                                          | L1/SDA1 pins (                        | ,                 | nd ASDA1/RB      | 5)                |                            |  |  |  |

| bit 3               |                                       | wer-up Timer                             |                                       |                   |                  |                   |                            |  |  |  |

|                     | 1 = PWRT is                           | enabled                                  |                                       |                   |                  |                   |                            |  |  |  |

|                     | 0 = PWRT is                           | disabled                                 |                                       |                   |                  |                   |                            |  |  |  |

| bit 2               | Unimplemen                            | ted: Read as '                           | 0'                                    |                   |                  |                   |                            |  |  |  |

| bit 1-0             | BOREN<1:0>                            | Brown-out R                              | eset Enable bit                       | S                 |                  |                   |                            |  |  |  |

|                     |                                       |                                          | dware; SBOREI                         |                   |                  |                   |                            |  |  |  |

|                     |                                       |                                          | hile device is a                      |                   | oled in Sleep; S | BOREN bit is o    | disabled                   |  |  |  |

|                     |                                       |                                          | the SBOREN b<br>dware; SBORE          | •                 | Ч                |                   |                            |  |  |  |

|                     |                                       |                                          | ·                                     |                   |                  |                   |                            |  |  |  |

|                     | The MCLRE fuse                        |                                          |                                       |                   |                  | node entry. This  | s prevents a               |  |  |  |

|                     | user from accider                     |                                          |                                       |                   | age test entry.  |                   |                            |  |  |  |

|                     | Refer to Table 26-                    |                                          |                                       |                   | rogrommod (-     | 1) in all other a | $lowiooo for l^2$          |  |  |  |

|                     | Implemented in 28 functionality to be |                                          | nny. This dit pos                     | muon must de p    | rogrammed (=     | ⊥) in all other c | ievices for I <sup>2</sup> |  |  |  |

#### **REGISTER 23-6: FPOR: RESET CONFIGURATION REGISTER**

| DC CHARACTERISTIC | Standard Operating Conditions:1.8V to 3.6VOperating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |       |                  |       |              |                                    |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|-------|--------------|------------------------------------|--|

| Parameter No.     | Typical <sup>(1)</sup>                                                                                                                                                     | Max   | Units Conditions |       |              |                                    |  |

| IDD Current       |                                                                                                                                                                            |       |                  |       |              |                                    |  |

| DC20              | 0.154                                                                                                                                                                      | 0.350 | m (              | 1.8V  |              |                                    |  |

|                   | 0.301                                                                                                                                                                      | 0.630 | – mA             | 3.3V  | +85V°C       | 0.5 MIPS,<br>Fosc = 1 MHz          |  |

|                   |                                                                                                                                                                            | .500  | mA               | 1.8V  | +125°C       |                                    |  |

|                   | —                                                                                                                                                                          | .800  |                  | 3.3V  | +125 C       |                                    |  |

| DC22              | 0.300                                                                                                                                                                      |       |                  | 1.8V  | 10500        | 1 MIPS,                            |  |

|                   | 0.585 —                                                                                                                                                                    | - mA  | 3.3V             | +85°C | Fosc = 2 MHz |                                    |  |

| DC24              | 7.76                                                                                                                                                                       | 12.0  | m (              | 3.3V  | +85°C        | 16 MIPS,                           |  |

|                   |                                                                                                                                                                            | 18.0  | - mA             | 3.3V  | +125°C       | Fosc = 32 MHz                      |  |

| DC26              | 1.44                                                                                                                                                                       | _     | m۸               | 1.8V  | +85°C        | FRC (4 MIPS),                      |  |

|                   | 2.71                                                                                                                                                                       | _     | - mA             | 3.3V  | +05 C        | Fosc = 8 MHz                       |  |

| DC30              | 4.00                                                                                                                                                                       | 28.0  |                  | 1.8V  | 195%         |                                    |  |

|                   | 9.00                                                                                                                                                                       | 55.0  | μA               | 3.3V  | +85°C        | LPRC (15.5 KIPS),<br>Fosc = 31 kHz |  |

|                   |                                                                                                                                                                            | 45.0  | μA               | 1.8V  | 112500       |                                    |  |

|                   | _                                                                                                                                                                          | 90.0  |                  | 3.3V  | +125°C       |                                    |  |

#### TABLE 26-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)<sup>(2)</sup>

Note 1: Data in the Typical column is at 3.3V, +25°C, unless otherwise stated.

2: IDD is measured with all peripherals disabled. All I/Os are configured as outputs and set low; PMDx bits are set to '1' and WDT, etc., are all disabled.

## TABLE 26-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)<sup>(2)</sup>

| DC CHARACTERIST     | Standard Operating Conditions:1.8V to 3.6VOperating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |       |                  |      |          |                   |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|------|----------|-------------------|--|--|--|

| Parameter No.       | Typical <sup>(1)</sup>                                                                                                                                                     | Max   | Units Conditions |      |          |                   |  |  |  |

| Idle Current (IDLE) |                                                                                                                                                                            |       |                  |      |          |                   |  |  |  |

| DC40                | 0.035                                                                                                                                                                      | 0.080 | ~^^              | 1.8V | 195°C    |                   |  |  |  |

|                     | 0.077                                                                                                                                                                      | 0.150 | - mA             | 3.3V | - +85°C  | 0.5 MIPS,         |  |  |  |

|                     | —                                                                                                                                                                          | 0.160 | ~ ^              | 1.8V | +125°C   | Fosc = 1 MHz      |  |  |  |

|                     | _                                                                                                                                                                          | 0.300 | - mA             | 3.3V | +125 C   |                   |  |  |  |

| DC42                | 0.076                                                                                                                                                                      | _     |                  | 1.8V | +85°C    | 1 MIPS,           |  |  |  |

|                     | 0.146                                                                                                                                                                      | _     | - mA             | 3.3V |          | Fosc = 2 MHz      |  |  |  |

| DC44                | 2.52                                                                                                                                                                       | 3.20  | mA               | 3.3V | +85°C    | 16 MIPS,          |  |  |  |

|                     | _                                                                                                                                                                          | 5.00  | mA               | 3.3V | +125°C   | Fosc = 32 MHz     |  |  |  |

| DC46                | 0.45                                                                                                                                                                       | —     | mA               | 1.8V | +85°C    | FRC (4 MIPS),     |  |  |  |

|                     | 0.76                                                                                                                                                                       | —     | mA               | 3.3V | +05 C    | Fosc = 8 MHz      |  |  |  |

| DC50                | 0.87                                                                                                                                                                       | 18.0  | μA               | 1.8V | 195°C    |                   |  |  |  |

|                     | 1.55                                                                                                                                                                       | 40.0  | μA               | 3.3V | - +85°C  | LPRC (15.5 KIPS), |  |  |  |

|                     | —                                                                                                                                                                          | 27.0  | μA               | 1.8V | +125°C   | Fosc = 31 kHz     |  |  |  |

|                     | _                                                                                                                                                                          | 50.0  | μA               | 3.3V | - +125°C |                   |  |  |  |

Note 1: Data in the Typical column is at 3.3V, +25°C, unless otherwise stated.

2: IIDLE is measured with all I/Os configured as outputs and set low; PMDx bits are set to '1' and WDT, etc., are all disabled.

| DC CHARACTERIS   |                        | <b>Operating C</b><br>temperature |       | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |      |                           |

|------------------|------------------------|-----------------------------------|-------|-----------------------------------------------------------------|------|---------------------------|

| Parameter No.    | Typical <sup>(1)</sup> | Max                               | Units |                                                                 | Con  | ditions                   |

| Power-Down Curre | nt (IPD)               |                                   |       |                                                                 |      |                           |

| DC60             | 0.01                   | 0.20                              | μA    | -40°C                                                           |      |                           |

|                  | 0.03                   | 0.20                              | μA    | +25°C                                                           |      |                           |

|                  | 0.06                   | 0.87                              | μA    | +60°C                                                           | 1.8V |                           |

|                  | 0.20                   | 1.35                              | μA    | +85°C                                                           |      |                           |

|                  | —                      | 8.00                              | μA    | +125°C                                                          |      | Sleep Mode <sup>(2)</sup> |

|                  | 0.01                   | 0.54                              | μA    | -40°C                                                           |      | Sleep Mode                |

|                  | 0.03                   | 0.54                              | μA    | +25°C                                                           |      |                           |

|                  | 0.08                   | 1.68                              | μA    | +60°C                                                           | 3.3V |                           |

|                  | 0.25                   | 2.45                              | μA    | +85°C                                                           |      |                           |

|                  | _                      | 10.00                             | μA    | +125°C                                                          |      |                           |

#### Т

**Note 1:** Data in the Typical column is at 3.3V, +25°C unless otherwise stated.

2: Base IPD is measured with all peripherals and clocks disabled. All I/Os are configured as outputs and set low; PMDx bits are set to '1' and WDT, etc., are all disabled

## TABLE 26-23: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                | Standard Operating Conditions: 1.8V to 3.6V |                    |      |       |                                                                           |  |

|--------------------|--------|----------------------------------------------------------------|---------------------------------------------|--------------------|------|-------|---------------------------------------------------------------------------|--|

|                    |        |                                                                | Operating temperature                       |                    |      |       | $A \le +85^{\circ}C$ for Industrial<br>$A \le +125^{\circ}C$ for Extended |  |

| Param<br>No.       | Symbol | Characteristic                                                 | Min.                                        | Typ <sup>(1)</sup> | Max. | Units | Conditions                                                                |  |

| SY10               | TmcL   | MCLR Pulse Width (low)                                         | 2                                           | —                  | _    | μS    |                                                                           |  |

| SY11               | TPWRT  | Power-up Timer Period                                          | 50                                          | 64                 | 90   | ms    |                                                                           |  |

| SY12               | TPOR   | Power-on Reset Delay                                           | 1                                           | 5                  | 10   | μS    |                                                                           |  |

| SY13               | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | _                                           | —                  | 100  | ns    |                                                                           |  |

| SY20               | Twdt   | Watchdog Timer Time-out                                        | 0.85                                        | 1.0                | 1.15 | ms    | 1.32 prescaler                                                            |  |

|                    |        | Period                                                         | 3.4                                         | 4.0                | 4.6  | ms    | 1:128 prescaler                                                           |  |

| SY25               | TBOR   | Brown-out Reset Pulse<br>Width                                 | 1                                           | —                  | —    | μs    |                                                                           |  |

| SY45               | TRST   | Internal State Reset Time                                      |                                             | 5                  |      | μS    |                                                                           |  |

| SY55               | TLOCK  | PLL Start-up Time                                              | —                                           | 100                | _    | μS    |                                                                           |  |

| SY65               | Tost   | Oscillator Start-up Time                                       | _                                           | 1024               |      | Tosc  |                                                                           |  |

| SY71               | Трм    | Program Memory Wake-up<br>Time                                 | —                                           | 1                  |      | μs    | Sleep wake-up with<br>PMSLP = 0                                           |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

#### TABLE 26-24: COMPARATOR TIMINGS

| Param<br>No. | Symbol | Characteristic                                           | Min | Тур | Мах | Units | Comments |

|--------------|--------|----------------------------------------------------------|-----|-----|-----|-------|----------|

| 300          | TRESP  | Response Time <sup>(1,2)</sup>                           |     | 150 | 400 | ns    |          |

| 301          | Тмс2о∨ | Comparator Mode Change to<br>Output Valid <sup>(2)</sup> | _   | —   | 10  | μS    |          |

**Note 1:** Response time is measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

#### TABLE 26-25: COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| Param<br>No. | Symbol | Characteristic               | Min | Тур | Max | Units | Comments |

|--------------|--------|------------------------------|-----|-----|-----|-------|----------|

| VR310        | TSET   | Settling Time <sup>(1)</sup> |     | _   | 10  | μS    |          |

**Note 1:** Settling time is measured while CVRSS = 1 and the CVR<3:0> bits transition from '0000' to '1111'.

<sup>2:</sup> Parameters are characterized but not tested.

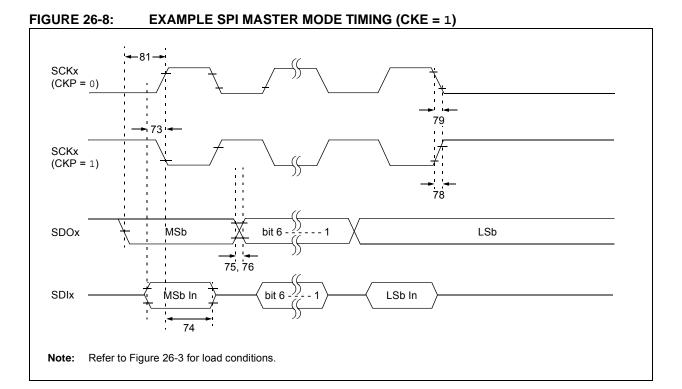

#### TABLE 26-28: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

| Param.<br>No. | Symbol                | Characteristic                             | Min | Мах | Units | Conditions |

|---------------|-----------------------|--------------------------------------------|-----|-----|-------|------------|

| 73            | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 35  | —   | ns    |            |

| 74            | TscH2dlL,<br>TscL2dlL | Hold Time of SDIx Data Input to SCKx Edge  | 40  | —   | ns    |            |

| 75            | TDOR                  | SDOx Data Output Rise Time                 | _   | 25  | ns    |            |

| 76            | TDOF                  | SDOx Data Output Fall Time                 | _   | 25  | ns    |            |

| 78            | TscR                  | SCKx Output Rise Time (Master mode)        | _   | 25  | ns    |            |

| 79            | TscF                  | SCKx Output Fall Time (Master mode)        | _   | 25  | ns    |            |

| 81            | TDOV2scH,<br>TDOV2scL | SDOx Data Output Setup to SCKx Edge        | Тсү | —   | ns    |            |

|               | FSCK                  | SCKx Frequency                             | _   | 10  | MHz   |            |

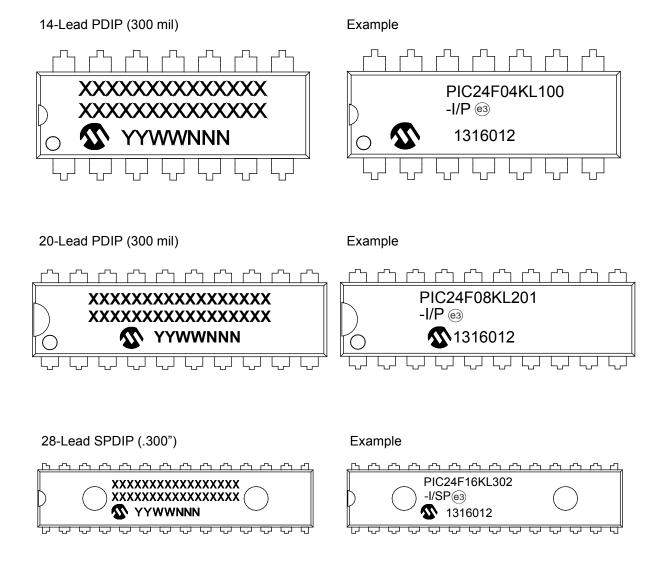

## 27.0 PACKAGING INFORMATION

## 27.1 Package Marking Information

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3 | Product-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|---------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:   | will be                           | event the full Microchip part number cannot be marked on one line, it carried over to the next line, thus limiting the number of available ters for customer-specific information.                                                                                                                                                                                          |

© 2011-2013 Microchip Technology Inc.

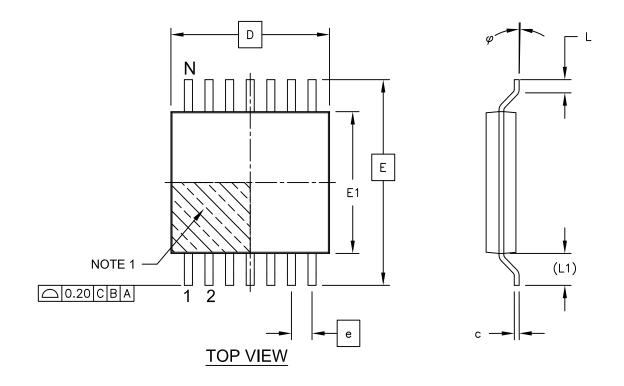

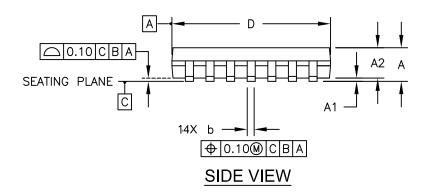

## 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-087C Sheet 1 of 2

## INDEX

| 1 | • |

|---|---|

| • | ١ |

| A/D                                    |     |

|----------------------------------------|-----|

| 10-Bit High-Speed A/D Converter        | 157 |

| Conversion Timing Requirements         | 224 |

| Module Specifications                  | 223 |

| A/D Converter                          |     |

| Analog Input Model                     | 164 |

| Transfer Function                      | 165 |

| AC Characteristics                     |     |

| A/D Module                             | 223 |

| Capacitive Loading Requirements on     |     |

| Output Pins                            |     |

| Internal RC Oscillator Accuracy        | 211 |

| Internal RC Oscillator Specifications  | 211 |

| Load Conditions and Requirements       | 209 |

| Temperature and Voltage Specifications |     |

| Assembler                              |     |

| MPASM Assembler                        |     |

## В

| Block Diagrams                              |     |

|---------------------------------------------|-----|

| 10-Bit High-Speed A/D Converter             | 158 |

| 16-Bit Timer1                               | 115 |

| Accessing Program Memory with               |     |

| Table Instructions                          |     |

| CALL Stack Frame                            | 43  |

| Capture Mode Operation                      | 126 |

| Comparator Module                           |     |

| Comparator Voltage Reference Module         | 171 |

| Compare Mode Operation                      |     |

| CPU Programmer's Model                      |     |

| Data Access From Program Space              |     |

| Address Generation                          | 44  |

| Data EEPROM Addressing with TBLPAG and      |     |

| NVM Registers                               | 55  |

| Enhanced PWM Mode                           | 127 |

| High/Low-Voltage Detect (HLVD) Module       | 173 |

| Individual Comparator Configurations        | 168 |

| MCLR Pin Connections Example                |     |

| MSSPx Module (I <sup>2</sup> C Master Mode) | 137 |

| MSSPx Module (I <sup>2</sup> C Mode)        |     |

| MSSPx Module (SPI Mode)                     |     |

| PIC24F CPU Core                             |     |

| PIC24F16KL402 Family (General)              | 13  |

| PSV Operation                               | 46  |

| PWM Operation (Simplified)                  | 126 |

| Recommended Minimum Connections             |     |

| Reset System                                |     |