#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| 2 0 0 0 0 0 0              |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 20-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl401-e-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                  | Pin N         | umber                             |               |     |                   |                                                     |

|----------|----------------------------------|---------------|-----------------------------------|---------------|-----|-------------------|-----------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | I/O | Buffer            | Description                                         |

| AN0      | 2                                | 19            | 2                                 | 27            | I   | ANA               | A/D Analog Inputs. Not available on PIC24F16KL30X   |

| AN1      | 3                                | 20            | 3                                 | 28            | I   | ANA               | family devices.                                     |

| AN2      | 4                                | 1             | 4                                 | 1             | I   | ANA               |                                                     |

| AN3      | 5                                | 2             | 5                                 | 2             | I   | ANA               |                                                     |

| AN4      | 6                                | 3             | 6                                 | 3             | Ι   | ANA               |                                                     |

| AN5      | _                                | _             | 7                                 | 4             | Ι   | ANA               |                                                     |

| AN9      | 18                               | 15            | 26                                | 23            | I   | ANA               |                                                     |

| AN10     | 17                               | 14            | 25                                | 22            | Ι   | ANA               |                                                     |

| AN11     | 16                               | 13            | 24                                | 21            | Ι   | ANA               |                                                     |

| AN12     | 15                               | 12            | 23                                | 20            | Ι   | ANA               |                                                     |

| AN13     | 7                                | 4             | 9                                 | 6             | Ι   | ANA               |                                                     |

| AN14     | 8                                | 5             | 10                                | 7             | I   | ANA               |                                                     |

| AN15     | 9                                | 6             | 11                                | 8             | I   | ANA               |                                                     |

| ASCL1    | _                                | _             | 15                                | 12            | I/O | I <sup>2</sup> C™ | Alternate MSSP1 I <sup>2</sup> C Clock Input/Output |

| ASDA1    | _                                | _             | 14                                | 11            | I/O | l <sup>2</sup> C  | Alternate MSSP1 I <sup>2</sup> C Data Input/Output  |

| AVdd     | 20                               | 17            | 28                                | 25            | Ι   | ANA               | Positive Supply for Analog modules                  |

| AVss     | 19                               | 16            | 27                                | 24            | Ι   | ANA               | Ground Reference for Analog modules                 |

| CCP1     | 14                               | 11            | 20                                | 17            | I/O | ST                | CCP1/ECCP1 Capture Input/Compare and PWM<br>Output  |

| CCP2     | 15                               | 12            | 23                                | 20            | I/O | ST                | CCP2 Capture Input/Compare and PWM Output           |

| CCP3     | 13                               | 10            | 19                                | 16            | I/O | ST                | CCP3 Capture Input/Compare and PWM Output           |

| C1INA    | 8                                | 5             | 7                                 | 4             | I   | ANA               | Comparator 1 Input A (+)                            |

| C1INB    | 7                                | 4             | 6                                 | 3             | I   | ANA               | Comparator 1 Input B (-)                            |

| C1INC    | 5                                | 2             | 5                                 | 2             | I   | ANA               | Comparator 1 Input C (+)                            |

| C1IND    | 4                                | 1             | 4                                 | 1             | I   | ANA               | Comparator 1 Input D (-)                            |

| C1OUT    | 17                               | 14            | 25                                | 22            | 0   | _                 | Comparator 1 Output                                 |

| C2INA    | 5                                | 2             | 5                                 | 2             | I   | ANA               | Comparator 2 Input A (+)                            |

| C2INB    | 4                                | 1             | 4                                 | 1             | Ι   | ANA               | Comparator 2 Input B (-)                            |

| C2INC    | 8                                | 5             | 7                                 | 4             | Ι   | ANA               | Comparator 2 Input C (+)                            |

| C2IND    | 7                                | 4             | 6                                 | 3             | Ι   | ANA               | Comparator 2 Input D (-)                            |

| C2OUT    | 14                               | 11            | 20                                | 17            | 0   |                   | Comparator 2 Output                                 |

| CLK I    | 7                                | 4             | 9                                 | 6             | Ι   | ANA               | Main Clock Input                                    |

| CLKO     | 8                                | 5             | 10                                | 7             | 0   | _                 | System Clock Output                                 |

#### TABLE 1-4: PIC24F16KL40X/30X FAMILY PINOUT DESCRIPTIONS

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

#### **TABLE 1-5:** PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS

|          |                                  | r             |                          |     |        |                                                   |  |  |

|----------|----------------------------------|---------------|--------------------------|-----|--------|---------------------------------------------------|--|--|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 14-Pin<br>PDIP/<br>TSSOP | I/O | Buffer | Description                                       |  |  |

| AN0      | 2                                | 19            | 2                        | I   | ANA    | A/D Analog Inputs. Not available on PIC24F16KL10X |  |  |

| AN1      | 3                                | 20            | 3                        | Ι   | ANA    | family devices.                                   |  |  |

| AN2      | 4                                | 1             | —                        | Ι   | ANA    |                                                   |  |  |

| AN3      | 5                                | 2             | _                        | I   | ANA    |                                                   |  |  |

| AN4      | 6                                | 3             | _                        | I   | ANA    |                                                   |  |  |

| AN9      | 18                               | 15            | 12                       | I   | ANA    |                                                   |  |  |

| AN10     | 17                               | 14            | 11                       | I   | ANA    |                                                   |  |  |

| AN11     | 16                               | 13            | —                        | I   | ANA    |                                                   |  |  |

| AN12     | 15                               | 12            | _                        | I   | ANA    |                                                   |  |  |

| AN13     | 7                                | 4             | 4                        | I   | ANA    | 7                                                 |  |  |

| AN14     | 8                                | 5             | 5                        | I   | ANA    | 1                                                 |  |  |

| AN15     | 9                                | 6             | 6                        | I   | ANA    | 1                                                 |  |  |

| AVdd     | 20                               | 17            | 14                       | I   | ANA    | Positive Supply for Analog modules                |  |  |

| AVss     | 19                               | 16            | 13                       | I   | ANA    | Ground Reference for Analog modules               |  |  |

| CCP1     | 14                               | 11            | 10                       | I/O | ST     | CCP1 Capture Input/Compare and PWM Output         |  |  |

| CCP2     | 15                               | 12            | 9                        | I/O | ST     | CCP2 Capture Input/Compare and PWM Output         |  |  |

| C1INA    | 8                                | 5             | 5                        | I   | ANA    | Comparator 1 Input A (+)                          |  |  |

| C1INB    | 7                                | 4             | 4                        | I   | ANA    | Comparator 1 Input B (-)                          |  |  |

| C1INC    | 5                                | 2             | _                        | I   | ANA    | Comparator 1 Input C (+)                          |  |  |

| C1IND    | 4                                | 1             | _                        | I   | ANA    | Comparator 1 Input D (-)                          |  |  |

| C1OUT    | 17                               | 14            | 11                       | 0   | _      | Comparator 1 Output                               |  |  |

| CLK I    | 7                                | 4             | 9                        | I   | ANA    | Main Clock Input                                  |  |  |

| CLKO     | 8                                | 5             | 10                       | 0   | _      | System Clock Output                               |  |  |

| CN0      | 10                               | 7             | 7                        | I   | ST     | Interrupt-on-Change Inputs                        |  |  |

| CN1      | 9                                | 6             | 6                        | I   | ST     |                                                   |  |  |

| CN2      | 2                                | 19            | 2                        | I   | ST     |                                                   |  |  |

| CN3      | 3                                | 20            | 3                        | I   | ST     | 7                                                 |  |  |

| CN4      | 4                                | 1             | _                        | I   | ST     | 7                                                 |  |  |

| CN5      | 5                                | 2             | _                        | Ι   | ST     | ]                                                 |  |  |

| CN6      | 6                                | 3             | _                        | I   | ST     | 7                                                 |  |  |

| CN8      | 14                               | 11            | 10                       | I   | ST     | 7                                                 |  |  |

| CN9      | _                                | _             | —                        | I   | ST     | 7                                                 |  |  |

| CN11     | 18                               | 15            | 12                       | I   | ST     | 7                                                 |  |  |

| CN12     | 17                               | 14            | 11                       | I   | ST     | 7                                                 |  |  |

| CN13     | 16                               | 13            | —                        | I   | ST     | 7                                                 |  |  |

| CN14     | 15                               | 12            | _                        | Ι   | ST     | 7                                                 |  |  |

| CN21     | 13                               | 10            | 9                        | I   | ST     | 1                                                 |  |  |

| CN22     | 12                               | 9             | 8                        | I   | ST     | 1                                                 |  |  |

| CN23     | 11                               | 8             | —                        | I   | ST     | 1                                                 |  |  |

| CN29     | 8                                | 5             | 5                        | I   | ST     | 1                                                 |  |  |

| CN30     | 7                                | 4             | 4                        | 1   | ST     | 1                                                 |  |  |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

|          |                                  | Pin Number                                                          | r  |             |                  |                                                           |  |

|----------|----------------------------------|---------------------------------------------------------------------|----|-------------|------------------|-----------------------------------------------------------|--|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | OIP/ 20-Pin 14-Pin I/O Buffer<br>OIP/ 20-Pin PDIP/<br>OP/ QFN TSSOP |    | Description |                  |                                                           |  |

| SCK1     | 15                               | 12                                                                  | 8  | I/O         | ST               | MSSP1 SPI Serial Input/Output Clock                       |  |

| SCL1     | 12                               | 9                                                                   | 8  | I/O         | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C Clock Input/Output                 |  |

| SCLKI    | 10                               | 7                                                                   | 12 | I           | ST               | Digital Secondary Clock Input                             |  |

| SDA1     | 13                               | 10                                                                  | 9  | I/O         | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C Data Input/Output                  |  |

| SDI1     | 17                               | 14                                                                  | 11 | Ι           | ST               | MSSP1 SPI Serial Data Input                               |  |

| SDO1     | 16                               | 13                                                                  | 9  | 0           | _                | MSSP1 SPI Serial Data Output                              |  |

| SOSCI    | 9                                | 6                                                                   | 11 | I           | ANA              | Secondary Oscillator Input                                |  |

| SOSCO    | 10                               | 7                                                                   | 12 | 0           | ANA              | Secondary Oscillator Output                               |  |

| SS1      | 12                               | 9                                                                   | 12 | 0           | _                | SPI1 Slave Select                                         |  |

| T1CK     | 13                               | 10                                                                  | 9  | I           | ST               | Timer1 Clock                                              |  |

| ТЗСК     | 18                               | 15                                                                  | 12 | I           | ST               | Timer3 Clock                                              |  |

| T3G      | 6                                | 3                                                                   | 11 | Ι           | ST               | Timer3 External Gate Input                                |  |

| U1CTS    | 12                               | 9                                                                   | 8  | Ι           | ST               | UART1 Clear-to-Send Input                                 |  |

| U1RTS    | 13                               | 10                                                                  | 9  | 0           | _                | UART1 Request-to-Send Output                              |  |

| U1RX     | 6                                | 3                                                                   | 12 | I           | ST               | UART1 Receive                                             |  |

| U1TX     | 11                               | 8                                                                   | 11 | 0           | _                | UART1 Transmit                                            |  |

| ULPWU    | 3                                | 1                                                                   | 3  | I           | ANA              | Ultra Low-Power Wake-up Input                             |  |

| VDD      | 20                               | 17                                                                  | 14 | Р           |                  | Positive Supply for Peripheral Digital Logic and I/O Pins |  |

| VREF+    | 2                                | 19                                                                  | 2  | I           | ANA              | A/D Reference Voltage Input (+)                           |  |

| VREF-    | 3                                | 20                                                                  | 3  | I           | ANA              | A/D Reference Voltage Input (-)                           |  |

| Vss      | 19                               | 16                                                                  | 13 | Р           | _                | - Ground Reference for Logic and I/O Pins                 |  |

#### **TABLE 1-5**: PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

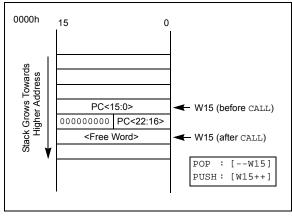

#### 4.2.5 SOFTWARE STACK

In addition to its use as a Working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer. The pointer always points to the first available free word and grows from lower to higher addresses. It predecrements for stack pops and post-increments for stack pushes, as shown in Figure 4-4.

Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

|       | will concatenate the SRL register to the |  |  |  |  |  |  |  |

|       | MSB of the PC prior to the push.         |  |  |  |  |  |  |  |

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated, using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation.

Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 0DF6, in RAM, initialize the SPLIM with the value, 0DF4.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the Special Function Register (SFR) space.

**Note:** A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

FIGURE 4-4: CALL STACK FRAME

## 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit wide program space and 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Apart from the normal execution, the PIC24F architecture provides two methods by which the program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space, PSV

Table instructions allow an application to read or write small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. It can only access the least significant word (lsw) of the program word.

#### 4.3.1 ADDRESSING PROGRAM SPACE

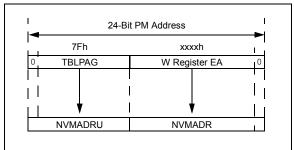

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit (MSb) of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility Page Address register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike the table operations, this limits remapping operations strictly to the user memory area.

Table 4-20 and Figure 4-5 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> bits refer to a program space word, whereas the D<15:0> bits refer to a data space word.

## 6.3 NVM Address Register

As with Flash program memory, the NVM Address Registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space; instead, they directly capture the EA<23:0> of the last Table Write instruction that has been executed and selects the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", is unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

#### FIGURE 6-1: DATA EEPROM ADDRESSING WITH TBLPAG AND NVM ADDRESS REGISTERS

## 6.4 Data EEPROM Operations

The EEPROM block is accessed using Table Read and Table Write operations, similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- Bulk erase the entire data EEPROM

- Write one word

- Read one word

| Note: | Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | The C30 C compiler includes library<br>procedures to automatically perform the<br>Table Read and Table Write operations,<br>manage the Table Pointer and write<br>buffers, and unlock and initiate memory<br>write sequences. This eliminates the need<br>to create assembler macros or time<br>critical routines in C for each application. |

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the C30 compiler libraries.

#### REGISTER 8-25: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0                                | U-0           | U-0                 | U-0              | U-0                                | U-0             | U-0  | U-0   |  |  |

|------------------------------------|---------------|---------------------|------------------|------------------------------------|-----------------|------|-------|--|--|

| —                                  | _             | —                   | —                | —                                  | —               | —    | —     |  |  |

| bit 15                             |               |                     |                  |                                    |                 |      | bit 8 |  |  |

|                                    |               |                     |                  |                                    |                 |      |       |  |  |

| U-0                                | R/W-1         | R/W-0               | R/W-0            | U-0                                | U-0             | U-0  | U-0   |  |  |

| _                                  | T3GIP2        | T3GIP1              | T3GIP0           | —                                  | —               | —    | —     |  |  |

| bit 7                              |               |                     |                  |                                    |                 |      | bit 0 |  |  |

|                                    |               |                     |                  |                                    |                 |      |       |  |  |

| Legend:                            |               |                     |                  |                                    |                 |      |       |  |  |

| R = Readab                         | le bit        | W = Writable        | bit              | U = Unimplemented bit, read as '0' |                 |      |       |  |  |

| -n = Value at POR '1' = Bit is set |               |                     |                  | '0' = Bit is clea                  | x = Bit is unkr | nown |       |  |  |

|                                    |               |                     |                  |                                    |                 |      |       |  |  |

| bit 15-7                           | Unimplemen    | ted: Read as 'd     | כי               |                                    |                 |      |       |  |  |

| bit 6-4                            | T3GIP<2:0>:   | Timer3 Externa      | al Gate Interru  | pt Priority bits                   |                 |      |       |  |  |

|                                    | 111 = Interru | pt is Priority 7 (l | highest priority | / interrupt)                       |                 |      |       |  |  |

|                                    | •             |                     |                  |                                    |                 |      |       |  |  |

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

#### REGISTER 8-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1                  | R/W-0                  | R/W-0                  |

|--------|-----|-----|-----|-----|------------------------|------------------------|------------------------|

| —      | —   | —   | —   | —   | U2ERIP2 <sup>(1)</sup> | U2ERIP1 <sup>(1)</sup> | U2ERIP0 <sup>(1)</sup> |

| bit 15 |     |     |     |     |                        |                        | bit 8                  |

| U-0   | R/W-1                  | R/W-0                  | R/W-0                  | U-0 | U-0 | U-0 | U-0 |  |  |

|-------|------------------------|------------------------|------------------------|-----|-----|-----|-----|--|--|

| _     | U1ERIP2 <sup>(1)</sup> | U1ERIP1 <sup>(1)</sup> | U1ERIP0 <sup>(1)</sup> |     |     | —   | —   |  |  |

| bit 7 | bit 7 bit 0            |                        |                        |     |     |     |     |  |  |

| Legend:                    |                                                            |                                 |                                |                    |  |  |  |  |

|----------------------------|------------------------------------------------------------|---------------------------------|--------------------------------|--------------------|--|--|--|--|

| R = Readable bit W = Writa |                                                            | W = Writable bit                | U = Unimplemented bit,         | read as '0'        |  |  |  |  |

| -n = Value a               | at POR                                                     | '1' = Bit is set                | '0' = Bit is cleared           | x = Bit is unknown |  |  |  |  |

|                            |                                                            |                                 |                                |                    |  |  |  |  |

| bit 15-11                  | -                                                          | nented: Read as '0'             |                                |                    |  |  |  |  |

| bit 10-8                   | U2ERIP<2                                                   | 2:0>: UART2 Error Interrupt     | t Priority bits <sup>(1)</sup> |                    |  |  |  |  |

|                            | 111 = Inte                                                 | errupt is Priority 7 (highest p | priority interrupt)            |                    |  |  |  |  |

|                            | •                                                          |                                 |                                |                    |  |  |  |  |

|                            | •                                                          |                                 |                                |                    |  |  |  |  |

|                            | •                                                          |                                 |                                |                    |  |  |  |  |

|                            |                                                            | errupt is Priority 1            |                                |                    |  |  |  |  |

|                            |                                                            | errupt source is disabled       |                                |                    |  |  |  |  |

| bit 7                      | -                                                          | nented: Read as '0'             |                                |                    |  |  |  |  |

| bit 6-4                    | U1ERIP<                                                    | 2:0>: UART1 Error Interrupt     | t Priority bits <sup>(1)</sup> |                    |  |  |  |  |

|                            | 111 = Interrupt is Priority 7 (highest priority interrupt) |                                 |                                |                    |  |  |  |  |

|                            | •                                                          |                                 |                                |                    |  |  |  |  |

|                            | •                                                          |                                 |                                |                    |  |  |  |  |

|                            | •                                                          |                                 |                                |                    |  |  |  |  |

|                            |                                                            | errupt is Priority 1            |                                |                    |  |  |  |  |

|                            |                                                            | errupt source is disabled       |                                |                    |  |  |  |  |

| bit 3-0                    | Unimplen                                                   | nented: Read as '0'             |                                |                    |  |  |  |  |

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

#### REGISTER 8-28: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|--------|-----|-----|-----|-----|---------|---------|---------|

|        | _   | _   | _   | _   | _       | _       | _       |

| bit 15 |     |     |     |     |         |         | bit 8   |

|        |     |     |     |     |         |         |         |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| —      | —   | —   | —   | —   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7  |     |     |     |     |         |         | bit 0   |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | d as '0'         |                      |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 HLVDIP<2:0>: High/Low-Voltage Detect Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

### REGISTER 8-29: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| -n = Value at POR '1' = Bit is set |       |              | '0' = Bit is cleared x = Bit is unknown |                                    |          |          |          |

|------------------------------------|-------|--------------|-----------------------------------------|------------------------------------|----------|----------|----------|

| R = Readable                       | e bit | W = Writable | bit                                     | U = Unimplemented bit, read as '0' |          |          |          |

| Legend:                            |       |              |                                         |                                    |          |          |          |

|                                    |       |              |                                         |                                    |          |          |          |

| bit 7                              |       |              | •                                       | 4                                  |          | •        | bit      |

| _                                  |       |              |                                         |                                    | ULPWUIP2 | ULPWUIP1 | ULPWUIP0 |

| U-0                                | U-0   | U-0          | U-0                                     | U-0                                | R/W-1    | R/W-0    | R/W-0    |

|                                    |       |              |                                         |                                    |          |          |          |

| bit 15                             |       |              | •                                       |                                    |          | •        | bit      |

| _                                  | —     | —            | —                                       | —                                  | —        | —        | _        |

| U-0                                | U-0   | U-0          | U-0                                     | U-0                                | U-0      | U-0      | U-0      |

bit 15-3 Unimplemented: Read as '0'

bit 6-4 ULPWUIP<2:0>: Ultra Low-Power Wake-up Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

.

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

NOTES:

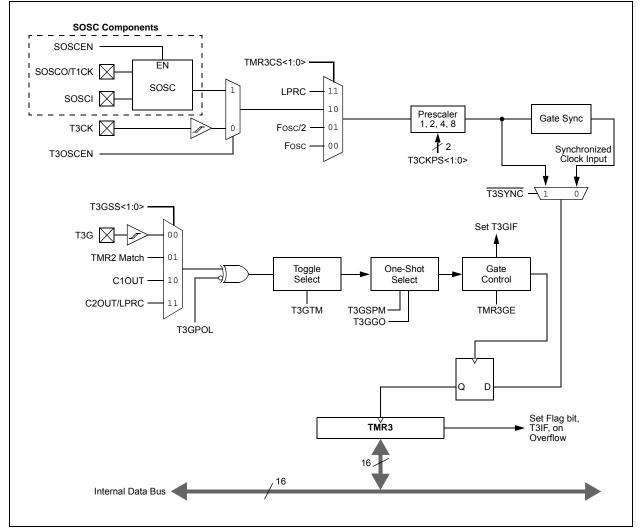

# 14.0 TIMER3 MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704).

The Timer3 timer/counter modules incorporate these features:

- Software-selectable operation as a 16-bit timer or counter

- One 16-bit readable and writable Timer Value register

- Selectable clock source (internal or external) with device clock, SOSC or LPRC oscillator options

- · Interrupt-on-overflow

- Multiple timer gating options, including:

- User-selectable gate sources and polarity

- Gate/toggle operation

- Single Pulse (One-Shot) mode

- Module Reset on ECCP Special Event Trigger

The Timer3 module is controlled through the T3CON register (Register 14-1). A simplified block diagram of the Timer3 module is shown in Figure 14-1.

The Fosc clock source should not be used with the ECCP capture/compare features. If the timer will be used with the capture or compare features, always select one of the other timer clocking options.

### FIGURE 14-1: TIMER3 BLOCK DIAGRAM

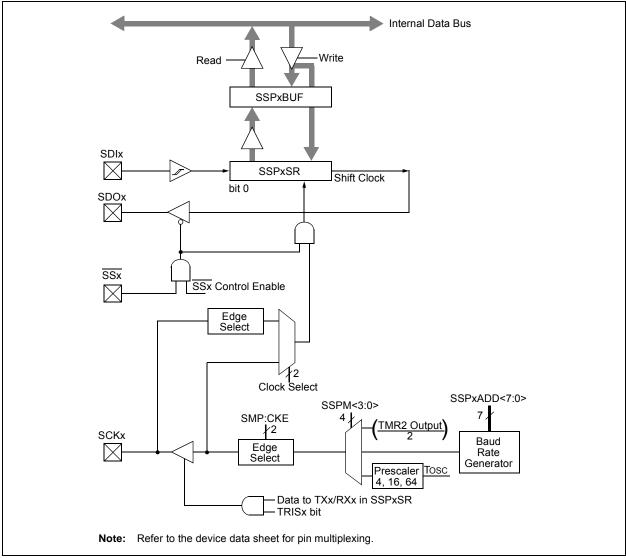

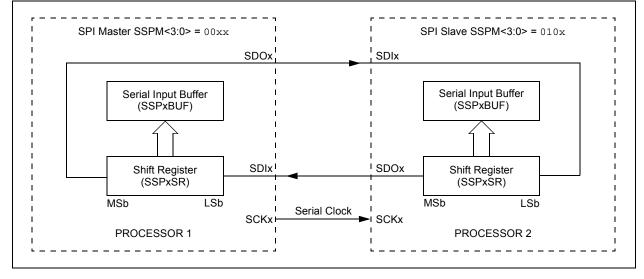

#### FIGURE 17-2: SPI MASTER/SLAVE CONNECTION

| U-0          | U-0                                   | U-0                           | U-0            | U-0               | U-0           | U-0             | U-0         |  |

|--------------|---------------------------------------|-------------------------------|----------------|-------------------|---------------|-----------------|-------------|--|

|              | —                                     | —                             |                | —                 | _             | —               |             |  |

| bit 15       |                                       |                               |                |                   |               |                 | bit         |  |

|              |                                       |                               |                |                   |               |                 |             |  |

| R/W-0        | R/W-0                                 | R-0                           | R-0            | R-0               | R-0           | R-0             | R-0         |  |

| SMP          | CKE <sup>(1)</sup>                    | D/A                           | Р              | S                 | R/W           | UA              | BF          |  |

| bit 7        |                                       |                               |                |                   |               |                 | bit         |  |

|              |                                       |                               |                |                   |               |                 |             |  |

| Legend:      |                                       |                               |                |                   |               |                 |             |  |

| R = Readab   |                                       | W = Writable                  |                | U = Unimplen      |               |                 |             |  |

| -n = Value a | t POR                                 | '1' = Bit is set              |                | '0' = Bit is clea | ared          | x = Bit is unkn | own         |  |

| bit 15-8     | Unimplome                             | nted: Read as '               | o'             |                   |               |                 |             |  |

| bit 7        | SMP: Sampl                            |                               | 0              |                   |               |                 |             |  |

|              | SPI Master n                          |                               |                |                   |               |                 |             |  |

|              |                                       | a is sampled at               | the end of dat | ta output time    |               |                 |             |  |

|              |                                       |                               |                | data output time  | 9             |                 |             |  |

|              | SPI Slave me                          |                               |                |                   |               |                 |             |  |

|              |                                       | e cleared when                |                | Slave mode.       |               |                 |             |  |

| bit 6        |                                       | ock Select bit <sup>(1)</sup> |                |                   |               |                 |             |  |

|              |                                       |                               |                | to active clock   |               |                 |             |  |

| bit 5        | D/A: Data/Ad                          | ddress bit                    |                |                   |               |                 |             |  |

|              | Used in I <sup>2</sup> C <sup>⊤</sup> | <sup>™</sup> mode only.       |                |                   |               |                 |             |  |

| bit 4        | P: Stop bit                           |                               |                |                   |               |                 |             |  |

|              | Used in I <sup>2</sup> C r            | mode only. This               | bit is cleared | when the MSSF     | x module is d | isabled; SSPEN  | is cleared. |  |

| bit 3        | S: Start bit                          |                               |                |                   |               |                 |             |  |

|              | Used in I <sup>2</sup> C r            | mode only.                    |                |                   |               |                 |             |  |

| bit 2        | R/W: Read/V                           | Vrite Informatio              | n bit          |                   |               |                 |             |  |

|              | Used in I <sup>2</sup> C r            | mode only.                    |                |                   |               |                 |             |  |

| bit 1        | UA: Update Address bit                |                               |                |                   |               |                 |             |  |

|              | Used in I <sup>2</sup> C r            | -                             |                |                   |               |                 |             |  |

| bit 0        | BF: Buffer Fi                         |                               |                |                   |               |                 |             |  |

|              |                                       | is complete, SS               |                |                   |               |                 |             |  |

|              | 0 = Receive                           | is not complete               | , SSPxBUF is   | empty             |               |                 |             |  |

| Note 1: ⊺    | he polarity of th                     | e clock state is              | set by the CK  | P bit (SSPxCON    | V1<4>).       |                 |             |  |

# REGISTER 17-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

#### REGISTER 21-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| U-0           | U-0                                           | U-0                                    | U-0                                                      | U-0                  | U-0             | U-0             | U-0   |  |

|---------------|-----------------------------------------------|----------------------------------------|----------------------------------------------------------|----------------------|-----------------|-----------------|-------|--|

| _             | —                                             | —                                      | _                                                        | _                    | _               | —               | _     |  |

| bit 15        |                                               |                                        |                                                          |                      |                 |                 | bit 8 |  |

| DAMO          |                                               |                                        | DAMA                                                     | D 444 0              | DAMA            | DAMA            | DAALO |  |

| R/W-0         | R/W-0                                         | R/W-0                                  | R/W-0                                                    | R/W-0                | R/W-0           | R/W-0           | R/W-0 |  |

| CVREN         | CVROE                                         | CVRSS                                  | CVR4                                                     | CVR3                 | CVR2            | CVR1            | CVR0  |  |

| bit 7         |                                               |                                        |                                                          |                      |                 |                 | bit ( |  |

| Legend:       |                                               |                                        |                                                          |                      |                 |                 |       |  |

| R = Readabl   | e bit                                         | W = Writable I                         | oit                                                      | U = Unimplen         | nented bit, rea | d as '0'        |       |  |

| -n = Value at | POR                                           | '1' = Bit is set                       |                                                          | '0' = Bit is clea    | ared            | x = Bit is unkr | nown  |  |

| bit 15-8      | Unimpleme                                     | nted: Read as 'd                       | )'                                                       |                      |                 |                 |       |  |

| bit 7         | CVREN: Co                                     | mparator Voltage                       | e Reference E                                            | Enable bit           |                 |                 |       |  |

|               | 1 = CVREF C                                   | circuit is powered                     | lon                                                      |                      |                 |                 |       |  |

|               | 0 = CVREF c                                   | circuit is powered                     | l down                                                   |                      |                 |                 |       |  |

| bit 6         | CVROE: Co                                     | mparator VREF C                        | Output Enable                                            | bit                  |                 |                 |       |  |

|               |                                               | voltage level is o                     |                                                          |                      |                 |                 |       |  |

|               |                                               | voltage level is d                     |                                                          | •                    | pin             |                 |       |  |

| bit 5         |                                               | mparator VREF S                        |                                                          |                      |                 |                 |       |  |

|               |                                               | ator reference so<br>ator reference so |                                                          |                      |                 |                 |       |  |

| bit 4-0       | CVR<4:0>: (                                   | Comparator VRE                         | F Value Selec                                            | tion $0 \le CVR < 4$ | :0> ≤ 31 bits   |                 |       |  |

|               | When CVRSS = 1:                               |                                        |                                                          |                      |                 |                 |       |  |

|               | •                                             | EF-) + (CVR<4:0                        | )>/32) • (VREF                                           | *+ – VREF-)          |                 |                 |       |  |

|               | $\frac{\text{When CVRS}}{\text{CVPER}} = (A)$ |                                        | 22) . (A)/pp</td <td></td> <td></td> <td></td> <td></td> |                      |                 |                 |       |  |

|               | OVREF = (AV                                   | ′ss) + (CVR<4:0                        | ~132) • (AVDD                                            | -AVSS)               |                 |                 |       |  |

### 23.5 Program Verification and Code Protection

For all devices in the PIC24F16KL402 family, code protection for the Boot Segment is controlled by the BSS<2:0> Configuration bits and the General Segment by the Configuration bit, GSS0. These bits inhibit external reads and writes to the program memory space This has no direct effect in normal execution mode.

Write protection is controlled by bit, BWRP, for the Boot Segment and bit, GWRP, for the General Segment in the Configuration Word. When these bits are programmed to '0', internal write and erase operations to program memory are blocked.

# 23.6 In-Circuit Serial Programming

PIC24F16KL402 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGECx) and data (PGEDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 23.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3, MPLAB REAL ICE<sup>™</sup> or PICkit<sup>™</sup> 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx and PGEDx pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGECx, PGEDx and the pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

### TABLE 25-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                          |

|-----------------|--------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                      |

| (text)          | Means "content of text"                                                              |

| [text]          | Means "the location addressed by text"                                               |

| { }             | Optional field or operation                                                          |

| <n:m></n:m>     | Register bit field                                                                   |

| .b              | Byte mode selection                                                                  |

| .d              | Double-Word mode selection                                                           |

| .S              | Shadow register select                                                               |

| .w              | Word mode selection (default)                                                        |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |

| f               | File register address ∈ {0000h1FFFh}                                                 |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4            | 4-bit unsigned literal ∈ {015}                                                       |

| lit5            | 5-bit unsigned literal ∈ {031}                                                       |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                      |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                   |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                   |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be '0'                                |

| None            | Field does not require an entry, may be blank                                        |

| PC              | Program Counter                                                                      |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                       |

| Wb              | Base W register ∈ {W0W15}                                                            |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm,Wn           | Dividend, Divisor Working register pair (direct addressing)                          |

| Wn              | One of 16 Working registers ∈ {W0W15}                                                |

| Wnd             | One of 16 destination Working registers ∈ {W0W15}                                    |

| Wns             | One of 16 source Working registers ∈ {W0W15}                                         |

| WREG            | W0 (Working register used in File register instructions)                             |

| Ws              | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                         |

| Wso             | Source W register ∈ { Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }         |

| Assembly<br>Mnemonic |        |             | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-------------|------------------------------|---------------|----------------|--------------------------|

| TBLRDH               | TBLRDH | Ws,Wd       | Read Prog<23:16> to Wd<7:0>  | 1             | 2              | None                     |

| TBLRDL               | TBLRDL | Ws,Wd       | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| TBLWTH               | TBLWTH | Ws,Wd       | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| TBLWTL               | TBLWTL | Ws,Wd       | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| ULNK                 | ULNK   |             | Unlink Frame Pointer         | 1             | 1              | None                     |

| XOR                  | XOR    | f           | f = f .XOR. WREG             | 1             | 1              | N, Z                     |

|                      | XOR    | f,WREG      | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |

|                      | XOR    | #lit10,Wn   | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |

|                      | XOR    | Wb,Ws,Wd    | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |

|                      | XOR    | Wb,#lit5,Wd | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |

| ZE                   | ZE     | Ws,Wnd      | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |

#### TABLE 25-2: INSTRUCTION SET OVERVIEW (CONTINUED)

#### TABLE 26-13: DC CHARACTERISTICS: DATA EEPROM MEMORY

| DC CHA       | RACTER | ISTICS                                                  | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |      | $\leq$ +85°C for Industrial                   |

|--------------|--------|---------------------------------------------------------|-------------------------------------------------------|-----|-----|------|-----------------------------------------------|

| Param<br>No. | Sym    | Characteristic                                          | Min Typ <sup>(1)</sup> Max Units Conditions           |     |     |      |                                               |

|              |        | Data EEPROM Memory                                      |                                                       |     |     |      |                                               |

| D140         | Epd    | Cell Endurance                                          | 100,000                                               | _   | —   | E/W  |                                               |

| D141         | Vprd   | VDD for Read                                            | VMIN                                                  | —   | 3.6 | V    | Vмın = Minimum operating<br>voltage           |

| D143A        | Tiwd   | Self-Timed Write Cycle<br>Time                          | —                                                     | 4   | —   | ms   |                                               |

| D143B        | Tref   | Number of Total<br>Write/Erase Cycles Before<br>Refresh | —                                                     | 10M | _   | E/W  |                                               |

| D144         | TRETDD | Characteristic Retention                                | 40                                                    | —   | —   | Year | Provided no other specifications are violated |

| D145         | Iddpd  | Supply Current during<br>Programming                    | —                                                     | 7   | —   | mA   |                                               |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

#### TABLE 26-14: DC CHARACTERISTICS: COMPARATOR

|              | Standard Operating Conditions: $2.0V < VDD < 3.6V$ Operating temperature $-40^{\circ}C < TA \le +85^{\circ}C$ (unless otherwise stated) $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                           |   |    |     |    |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---|----|-----|----|--|--|--|

| Param<br>No. | Symbol Characteristic Min Typ Max Units Comments                                                                                                                                             |                           |   |    |     |    |  |  |  |

| D300         | VIOFF                                                                                                                                                                                        | Input Offset Voltage      |   | 20 | 40  | mV |  |  |  |

| D301         | VICM                                                                                                                                                                                         | Input Common-Mode Voltage | 0 | _  | Vdd | V  |  |  |  |

| D302         |                                                                                                                                                                                              |                           |   |    |     |    |  |  |  |

### TABLE 26-15: DC CHARACTERISTICS: COMPARATOR VOLTAGE REFERENCE

|              | Standard Operating Conditions: $2.0V < VDD < 3.6V$ Operating temperature $-40^{\circ}C < TA \le +85^{\circ}C$ (unless otherwise stated) $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |            |   |  |        |     |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|--|--------|-----|--|--|

| Param<br>No. | Symbol Characteristic Min Typ Max Units Comments                                                                                                                                             |            |   |  |        |     |  |  |

| VRD310       | CVRES                                                                                                                                                                                        | Resolution | _ |  | VDD/32 | LSb |  |  |

| VRD311       | VRD311 CVRAA Absolute Accuracy — AVDD – 1.5 LSb                                                                                                                                              |            |   |  |        |     |  |  |

| VRD312       | VRD312 CVRur Unit Resistor Value (R) – 2k – Ω                                                                                                                                                |            |   |  |        |     |  |  |

### 26.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC24F16KL402 Family AC characteristics and timing parameters.

#### TABLE 26-16: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions:    | 1.8V to 3.6V                                  |

|--------------------|-----------------------------------|-----------------------------------------------|

| AC CHARACTERISTICS | Operating temperature             | -40°C $\leq$ TA $\leq$ +85°C for Industrial   |

|                    | Operating voltage VDD range as de | scribed in Section 26.1 "DC Characteristics". |

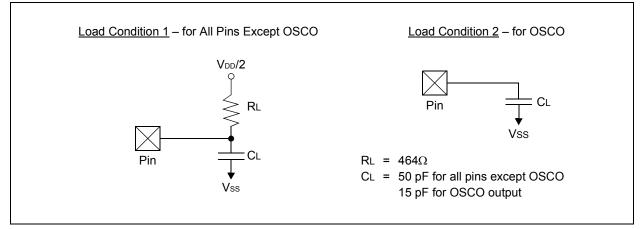

#### FIGURE 26-3: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 26-17: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosc2  | OSCO/CLKO Pin         | _   | _                  | 15  | pF    | In XT and HS modes when<br>external clock is used to drive<br>OSCI |

| DO56         | Сю     | All I/O Pins and OSCO | —   | _                  | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            |     |                    | 400 | pF    | In l <sup>2</sup> C™ mode                                          |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

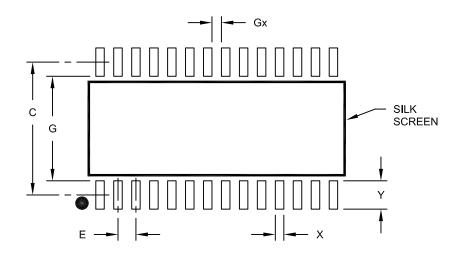

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units            |      |          |      |  |

|--------------------------|------------------|------|----------|------|--|

| Dimensior                | Dimension Limits |      |          | MAX  |  |

| Contact Pitch            | E                |      | 1.27 BSC |      |  |

| Contact Pad Spacing      | С                |      | 9.40     |      |  |

| Contact Pad Width (X28)  | X                |      |          | 0.60 |  |

| Contact Pad Length (X28) | Y                |      |          | 2.00 |  |

| Distance Between Pads    | Gx               | 0.67 |          |      |  |

| Distance Between Pads    | G                | 7.40 |          |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

## 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |  |

|--------------------------|-------------|----------|----------|------|--|

| Dimension                | Limits      | MIN      | NOM      | MAX  |  |

| Number of Pins           | N           |          | 14       |      |  |

| Pitch                    | е           |          | 0.65 BSC |      |  |

| Overall Height           | A           | -        | -        | 1.20 |  |

| Molded Package Thickness | A2          | 0.80     | 1.00     | 1.05 |  |

| Standoff                 | A1          | 0.05     | -        | 0.15 |  |

| Overall Width            | E           | 6.40 BSC |          |      |  |

| Molded Package Width     | E1          | 4.30     | 4.40     | 4.50 |  |

| Molded Package Length    | D           | 4.90     | 5.00     | 5.10 |  |

| Foot Length              | L           | 0.45     | 0.60     | 0.75 |  |

| Footprint                | (L1)        |          | 1.00 REF |      |  |

| Foot Angle               | φ           | 0°       | -        | 8°   |  |

| Lead Thickness           | С           | 0.09     | -        | 0.20 |  |

| Lead Width               | b           | 0.19     | -        | 0.30 |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-087C Sheet 2 of 2