Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

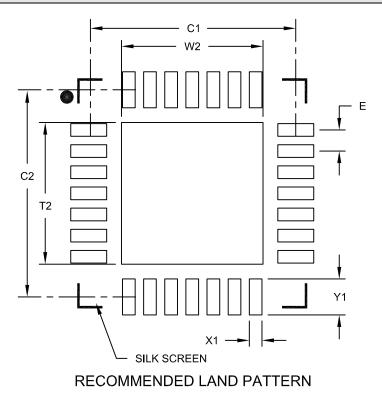

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 20-VQFN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl401-i-mq |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

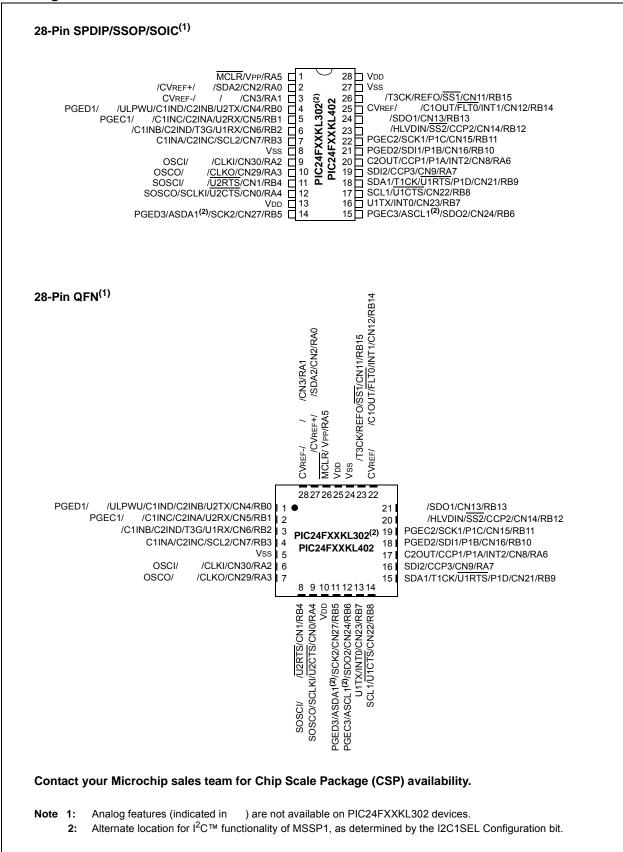

#### Pin Diagrams: PIC24FXXKL302/402

#### 1.2 Other Special Features

- Communications: The PIC24F16KL402 family incorporates multiple serial communication peripherals to handle a range of application requirements. The MSSP module implements both SPI and I<sup>2</sup>C™ protocols, and supports both Master and Slave modes of operation for each. Devices also include one of two UARTs with built-in IrDA<sup>®</sup> encoders/decoders.

- Analog Features: Select members of the PIC24F16KL402 family include a 10-bit A/D Converter module. The A/D module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, as well as faster sampling speeds.

The comparator modules are configurable for a wide range of operations and can be used as either a single or double comparator module.

#### 1.3 Details on Individual Family Members

Devices in the PIC24F16KL402 family are available in 14-pin, 20-pin and 28-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The PIC24F16KL402 family may be thought of as four different device groups, each offering a slightly different set of features. These differ from each other in multiple ways:

- · The size of the Flash program memory

- The presence and size of data EEPROM

- The presence of an A/D Converter and the number of external analog channels available

- · The number of analog comparators

- The number of general purpose timers

- The number and type of CCP modules (i.e., CCP vs. ECCP)

- The number of serial communications modules (both MSSPs and UARTs)

The general differences between the different sub-families are shown in Table 1-1. The feature sets for specific devices are summarized in Table 1-2 and Table 1-3.

A list of the individual pin features available on the PIC24F16KL402 family devices, sorted by function, is provided in Table 1-4 (for PIC24FXXKL40X/30X devices) and Table 1-5 (for PIC24FXXKL20X/10X devices). Note that these tables show the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

| Device Group  | Program<br>Memory<br>(bytes) | Data<br>EEPROM<br>(bytes) | Timers<br>(8/16-bit) | CCP and<br>ECCP | Serial<br>(MSSP/<br>UART) | A/D<br>(channels) | Comparators |

|---------------|------------------------------|---------------------------|----------------------|-----------------|---------------------------|-------------------|-------------|

| PIC24FXXKL10X | 4K                           | _                         | 1/2                  | 2/0             | 1/1                       | _                 | 1           |

| PIC24FXXKL20X | 8K                           | —                         | 1/2                  | 2/0             | 1/1                       | 7 or 12           | 1           |

| PIC24FXXKL30X | 8K                           | 256                       | 2/2                  | 2/1             | 2/2                       | —                 | 2           |

| PIC24FXXKL40X | 8K or 16K                    | 512                       | 2/2                  | 2/1             | 2/2                       | 12                | 2           |

#### TABLE 1-1:FEATURE COMPARISON FOR PIC24F16KL402 FAMILY GROUPS

|          |                                  | Pin N         | umber                             |               |     |        |                                                                               |

|----------|----------------------------------|---------------|-----------------------------------|---------------|-----|--------|-------------------------------------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | I/O | Buffer | Description                                                                   |

| CN0      | 10                               | 7             | 12                                | 9             | I   | ST     | Interrupt-on-Change Inputs                                                    |

| CN1      | 9                                | 6             | 11                                | 8             | I   | ST     |                                                                               |

| CN2      | 2                                | 19            | 2                                 | 27            | I   | ST     |                                                                               |

| CN3      | 3                                | 20            | 3                                 | 28            | Ι   | ST     |                                                                               |

| CN4      | 4                                | 1             | 4                                 | 1             | Ι   | ST     |                                                                               |

| CN5      | 5                                | 2             | 5                                 | 2             | I   | ST     |                                                                               |

| CN6      | 6                                | 3             | 6                                 | 3             | I   | ST     |                                                                               |

| CN7      | _                                | _             | 7                                 | 4             | I   | ST     |                                                                               |

| CN8      | 14                               | 11            | 20                                | 17            | I   | ST     |                                                                               |

| CN9      | —                                | —             | 19                                | 16            | I   | ST     | ]                                                                             |

| CN11     | 18                               | 15            | 26                                | 23            | I   | ST     |                                                                               |

| CN12     | 17                               | 14            | 25                                | 22            | I   | ST     |                                                                               |

| CN13     | 16                               | 13            | 24                                | 21            | I   | ST     |                                                                               |

| CN14     | 15                               | 12            | 23                                | 20            | I   | ST     |                                                                               |

| CN15     | _                                | _             | 22                                | 19            | I   | ST     |                                                                               |

| CN16     | —                                | _             | 21                                | 18            | I   | ST     |                                                                               |

| CN21     | 13                               | 10            | 18                                | 15            | I   | ST     |                                                                               |

| CN22     | 12                               | 9             | 17                                | 14            | I   | ST     |                                                                               |

| CN23     | 11                               | 8             | 16                                | 13            | I   | ST     |                                                                               |

| CN24     | _                                | _             | 15                                | 12            | I   | ST     |                                                                               |

| CN27     | _                                | _             | 14                                | 11            | I   | ST     |                                                                               |

| CN29     | 8                                | 5             | 10                                | 7             | I   | ST     |                                                                               |

| CN30     | 7                                | 4             | 9                                 | 6             | I   | ST     |                                                                               |

| CVREF    | 17                               | 14            | 25                                | 22            | I   | ANA    | Comparator Voltage Reference Output                                           |

| CVREF+   | 2                                | 19            | 2                                 | 27            | I   | ANA    | Comparator Reference Positive Input Voltage                                   |

| CVREF-   | 3                                | 20            | 3                                 | 28            | I   | ANA    | Comparator Reference Negative Input Voltage                                   |

| FLT0     | 17                               | 14            | 25                                | 22            | I   | ST     | ECCP1 Enhanced PWM Fault Input                                                |

| HLVDIN   | 15                               | 12            | 23                                | 20            | I   | ST     | High/Low-Voltage Detect Input                                                 |

| INT0     | 11                               | 8             | 16                                | 13            | I   | ST     | Interrupt 0 Input                                                             |

| INT1     | 17                               | 14            | 25                                | 22            | I   | ST     | Interrupt 1 Input                                                             |

| INT2     | 14                               | 11            | 20                                | 17            | I   | ST     | Interrupt 2 Input                                                             |

| MCLR     | 1                                | 18            | 1                                 | 26            | I   | ST     | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |

| OSCI     | 7                                | 4             | 9                                 | 6             | I   | ANA    | Main Oscillator Input                                                         |

| OSCO     | 8                                | 5             | 10                                | 7             | 0   | ANA    | Main Oscillator Output                                                        |

| P1A      | 14                               | 11            | 20                                | 17            | 0   | —      | ECCP1 Output A (Enhanced PWM Mode)                                            |

| P1B      | 5                                | 2             | 21                                | 18            | 0   | _      | ECCP1 Output B (Enhanced PWM Mode)                                            |

| P1C      | 4                                | 1             | 22                                | 19            | 0   | _      | ECCP1 Output C (Enhanced PWM Mode)                                            |

| P1D      | 16                               | 13            | 18                                | 15            | 0   | _      | ECCP1 Output D (Enhanced PWM Mode)                                            |

| TABLE 1-4: | PIC24F16KL40X/30X FAMILY PINOUT DESCRIPTIONS ( | (CONTINUED) |

|------------|------------------------------------------------|-------------|

|            |                                                |             |

Legend:

TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

### 3.0 CPU

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the CPU, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"CPU"** (DS39703).

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16<sup>th</sup> Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K word boundary of either program memory or data EEPROM memory, defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (i.e., A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by a 16-bit integer signed and unsigned division. All divide operations require 19 cycles to complete, but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme, with up to eight sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is illustrated in Figure 3-1.

#### 3.1 Programmer's Model

Figure 3-2 displays the programmer's model for the PIC24F. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions.

Table 3-1 provides a description of each register. All registers associated with the programmer's model are memory mapped.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> devices and improve data space memory usage efficiency, the PIC24F instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address (EA) calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word, which contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and the registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register, which matches the byte address.

All word accesses must be aligned to an even address. Mis-aligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a mis-aligned read or write is attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed, but the write will not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow the users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users

can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions operate only on words.

#### 4.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is referred to as the Near Data Space (NDS). Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. The remainder of the data space is addressable indirectly. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing (MDA) with a 16-bit address field. For PIC24F16KL402 family devices, the entire implemented data memory lies in Near Data Space.

#### 4.2.4 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0000h to 07FFh, are primarily occupied with Special Function Registers (SFRs). These are used by the PIC24F core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by the module. Much of the SFR space contains unused addresses; these are read as '0'. The SFR space, where the SFRs are actually implemented, is provided in Table 4-2. Each implemented area indicates a 32-byte region, where at least one address is implemented as an SFR. A complete listing of implemented SFRs, including their addresses, is provided in Table 4-3 through Table 4-18.

|      |        |     |     | SFR    | Space Add | ress |    |       |       |    |    |     |    |

|------|--------|-----|-----|--------|-----------|------|----|-------|-------|----|----|-----|----|

|      | xx00   | xx  | 20  | xx40   | xx60      | хх   | 80 | xx    | :A0   | xx | C0 | xx  | E0 |

| 000h |        | Со  | re  |        | ICN       |      |    | Inter | rupts |    |    | _   | _  |

| 100h | Timers | —   | TMR | —      | _         | _    | CC | CP    | —     |    | _  | _   | -  |

| 200h | MSSP   | UAI | RT  | —      | _         | -    | _  | -     | _     | 1/ | 0  | _   | -  |

| 300h | A      | /D  |     | _      | _         | _    | _  | -     | _     | _  | _  | _   | -  |

| 400h | —      | _   | -   | —      | _         | _    | _  | -     | _     | _  | AN | SEL |    |

| 500h | _      | _   | -   |        | _         | _    | _  | -     | _     |    | -  | _   | _  |

| 600h |        | CMP |     |        |           |      | _  | -     | _     |    | _  |     | _  |

| 700h |        | _   | -   | System | NVM/PMD   | _    | _  | -     | _     | _  | _  | _   | _  |

#### TABLE 4-2: IMPLEMENTED REGIONS OF SFR DATA SPACE

**Legend:** — = No implemented SFRs in this block.

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

|              | чυ.  |        |                      | 1 001                |                      |                     |            |                       |            |       |            |            |            |         |                       |                       |          |               |

|--------------|------|--------|----------------------|----------------------|----------------------|---------------------|------------|-----------------------|------------|-------|------------|------------|------------|---------|-----------------------|-----------------------|----------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14               | Bit 13               | Bit 12               | Bit 11              | Bit 10     | Bit 9                 | Bit 8      | Bit 7 | Bit 6      | Bit 5      | Bit 4      | Bit 3   | Bit 2                 | Bit 1                 | Bit 0    | All<br>Resets |

| INTCON1      | 0080 | NSTDIS | —                    | —                    | —                    | —                   | —          | —                     | —          | _     | —          | —          | MATHERR    | ADDRERR | STKERR                | OSCFAIL               | —        | 0000          |

| INTCON2      | 0082 | ALTIVT | DISI                 | _                    | —                    | —                   | _          | _                     | —          | _     | _          | _          | _          | _       | INT2EP                | INT1EP                | INT0EP   | 0000          |

| IFS0         | 0084 | NVMIF  | _                    | AD1IF                | U1TXIF               | U1RXIF              | _          | _                     | T3IF       | T2IF  | CCP2IF     | _          | _          | T1IF    | CCP1IF                | _                     | INT0IF   | 0000          |

| IFS1         | 0086 | U2TXIF | U2RXIF               | INT2IF               | _                    | T4IF <sup>(1)</sup> | _          | CCP3IF <sup>(1)</sup> | _          | _     | _          | _          | INT1IF     | CNIF    | CMIF                  | BCL1IF                | SSP1IF   | 0000          |

| IFS2         | 8800 |        | _                    | _                    | _                    |                     | _          | _                     | _          | _     | _          | T3GIF      | _          | _       | _                     | _                     | _        | 0000          |

| IFS3         | 008A | —      | _                    | _                    | —                    | —                   | _          | _                     | —          | —     | _          | —          | _          | _       | BCL2IF <sup>(1)</sup> | SSP2IF <sup>(1)</sup> | —        | 0000          |

| IFS4         | 008C | —      | _                    | _                    | —                    | _                   | _          | _                     | HLVDIF     | _     | _          | _          | _          | _       | U2ERIF                | U1ERIF                | _        | 0000          |

| IFS5         | 008E | —      | _                    | _                    | —                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | _                     | _                     | ULPWUIF  | 0000          |

| IEC0         | 0094 | NVMIE  | _                    | AD1IE                | U1TXIE               | U1RXIE              | _          | _                     | T3IE       | T2IE  | CCP2IE     | _          | _          | T1IE    | CCP1IE                | _                     | INT0IE   | 0000          |

| IEC1         | 0096 | U2TXIE | U2RXIE               | INT2IE               | —                    | T4IE <sup>(1)</sup> | _          | CCP3IE <sup>(1)</sup> | _          | _     | _          | _          | INT1IE     | CNIE    | CMIE                  | BCL1IE                | SSP1IE   | 0000          |

| IEC2         | 0098 | _      | _                    | -                    | —                    | _                   | _          | _                     | _          |       | _          | T3GIE      | _          | _       | _                     | _                     | -        | 0000          |

| IEC3         | 009A | _      | _                    |                      | —                    | _                   | _          | _                     | _          |       | _          | _          | -          | _       | BCL2IE <sup>(1)</sup> | SSP2IE <sup>(1)</sup> |          | 0000          |

| IEC4         | 009C | _      | _                    |                      | —                    | _                   | _          | _                     | HLVDIE     |       | _          | _          | -          | _       | U2ERIE                | U1ERIE                |          | 0000          |

| IEC5         | 009E | _      | _                    |                      | —                    | _                   | _          | _                     | _          |       | _          | _          | -          | _       | _                     | _                     | ULPWUIE  | 0000          |

| IPC0         | 00A4 | —      | T1IP2                | T1IP1                | T1IP0                | _                   | CCP1IP2    | CCP1IP1               | CCP1IP0    | _     | _          | _          | _          | _       | INT0IP2               | INT0IP1               | INT0IP0  | 4404          |

| IPC1         | 00A6 | _      | T2IP2                | T2IP1                | T2IP0                | _                   | CCP2IP2    | CCP2IP1               | CCP2IP0    |       | _          | _          | -          | _       | _                     | _                     | -        | 4400          |

| IPC2         | 00A8 | _      | U1RXIP2              | U1RXIP1              | U1RXIP0              | _                   | _          | _                     | _          |       | _          | _          | -          | _       | T3IP2                 | T3IP1                 | T3IP0    | 4004          |

| IPC3         | 00AA | _      | NVMIP2               | NVMIP1               | NVMIP0               | _                   | _          | _                     | _          |       | AD1IP2     | AD1IP1     | AD1IP0     | _       | U1TXIP2               | U1TXIP1               | U1TXIP0  | 4044          |

| IPC4         | 00AC | _      | CNIP2                | CNIP1                | CNIP0                | _                   | CMIP2      | CMIP1                 | CMIP0      |       | BCL1IP2    | BCL1IP1    | BCL1IP0    | _       | SSP1IP2               | SSP1IP1               | SS1IP0   | 4444          |

| IPC5         | 00AE | _      | _                    | -                    | —                    | _                   | _          | _                     | _          |       | _          | _          | _          | _       | INT1IP2               | INT1IP1               | INT1IP0  | 0004          |

| IPC6         | 00B0 | _      | T4IP2 <sup>(1)</sup> | T4IP1 <sup>(1)</sup> | T4IP0 <sup>(1)</sup> | _                   | _          | _                     | _          |       | CCP3IP2(1) | CCP3IP1(1) | CCP3IP0(1) | _       | —                     | —                     | -        | 4040          |

| IPC7         | 00B2 | _      | U2TXIP2              | U2TXIP1              | U2TXIP0              | _                   | U2RXIP2    | U2RXIP1               | U2RXIP0    |       | INT2IP2    | INT2IP1    | INT2IP0    | _       | _                     | _                     |          | 4440          |

| IPC9         | 00B6 | _      | _                    | _                    | —                    | _                   | _          | —                     | _          |       | T3GIP2     | T3GIP1     | T3GIP0     | _       | _                     | _                     |          | 0040          |

| IPC12        | 00BC | _      | _                    | _                    | —                    | _                   | BCL2IP2(1) | BCL2IP1(1)            | BCL2IP0(1) |       | SSP2IP2(1) | SSP2IP1(1) | SSP2IP0(1) | _       | _                     | _                     |          | 0440          |

| IPC16        | 00C4 | _      | _                    | _                    | _                    | _                   | U2ERIP2    | U2ERIP1               | U2ERIP0    | _     | U1ERIP2    | U1ERIP1    | U1ERIP0    | _       | _                     | —                     | _        | 0440          |

| IPC18        | 00C8 | _      | _                    | _                    | _                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | HLVDIP2               | HLVDIP1               | HLVDIP0  | 0004          |

| IPC20        | 00CC | _      | _                    | _                    | _                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | ULPWUIP2              | ULPWUIP1              | ULPWUIP0 | 0004          |

| INTTREG      | 00E0 | CPUIRQ | r                    | VHOLD                | _                    | ILR3                | ILR2       | ILR1                  | ILR0       | _     | VECNUM6    | VECNUM5    | VECNUM4    | VECNUM3 | VECNUM2               | VECNUM1               | VECNUM0  | 0000          |

Legend: Note 1:

Legend: — = unimplemented, read as '0', r = reserved. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

#### TABLE 4-10: PORTA REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 <sup>(1)</sup> | Bit 6  | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|----------------------|--------|----------------------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 02C0 | _      | _      | —      | —      | _      | _      | _     | _     | TRISA7               | TRISA6 | _                    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 00DF          |

| PORTA        | 02C2 |        | —      |        |        |        |        |       | —     | RA7                  | RA6    | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA         | 02C4 |        | —      |        |        |        |        |       | —     | LATA7                | LATA6  | —                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA         | 02C6 | -      | _      | _      | _      | _      | _      | _     | -     | ODA7                 | ODA6   | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These ports and their associated bits are unimplemented on 14-pin and 20-pin devices; read as '0'.

2: PORTA<5> is unavailable when MCLR functionality is enabled (MCLRE Configuration bit = 1).

#### TABLE 4-11: PORTB REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13 <sup>(1)</sup> | Bit 12 <sup>(1)</sup> | Bit 11 <sup>(2)</sup> | Bit 10 <sup>(2)</sup> | Bit 9  | Bit 8  | Bit 7 <sup>(1)</sup> | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3 <sup>(2)</sup> | Bit 2 <sup>(1)</sup> | Bit 1 <sup>(1)</sup> | Bit 0  | All<br>Resets |

|--------------|------|---------|---------|-----------------------|-----------------------|-----------------------|-----------------------|--------|--------|----------------------|----------------------|----------------------|--------|----------------------|----------------------|----------------------|--------|---------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13               | TRISB12               | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7               | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2               | TRISB1               | TRISB0 | FFFF          |

| PORTB        | 02CA | RB15    | RB14    | RB13                  | RB12                  | RB11                  | RB10                  | RB9    | RB8    | RB7                  | RB6                  | RB5                  | RB4    | RB3                  | RB2                  | RB1                  | RB0    | xxxx          |

| LATB         | 02CC | LATB15  | LATB14  | LATB13                | LATB12                | LATB11                | LATB10                | LATB9  | LATB8  | LATB7                | LATB6                | LATB5                | LATB4  | LATB3                | LATB2                | LATB1                | LATB0  | xxxx          |

| ODCB         | 02CE | ODB15   | ODB14   | ODB13                 | ODB12                 | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7                 | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2                 | ODB1                 | ODB0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These ports and their associated bits are unimplemented on 14-pin and 20-pin devices.

2: These ports and their associated bits are unimplemented in 14-pin devices.

#### TABLE 4-12: PAD CONFIGURATION REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11                 | Bit 10     | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|------------------------|------------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| PADCFG1      | 02FC | —      | —      | _      | —      | SDO2DIS <sup>(1)</sup> | SCK2DIS(1) | SDO1DIS | SCK1DIS | —     | _     | _     | _     | _     | —     | —     | —     | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

#### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is as follows:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '000100' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-5.

| ; Set up  | NVMCON for re | ow erase operation               |                                     |

|-----------|---------------|----------------------------------|-------------------------------------|

| M         | OV #0x405     | 8, WO ;                          |                                     |

| M         | OV WO, NVI    | MCON ;                           | Initialize NVMCON                   |

| ; Init po | inter to row  | to be ERASED                     |                                     |

| M         | OV #tblpag    | ge(PROG_ADDR), W0 ;              |                                     |

| M         | OV WO, TB     | LPAG ;                           | Initialize PM Page Boundary SFR     |

| M         | OV #tblof:    | <pre>fset(PROG_ADDR), W0 ;</pre> | Initialize in-page EA[15:0] pointer |

| TI        | BLWTL WO, [W  | 0] ;                             | Set base address of erase block     |

| D         | ISI #5        | ;                                | Block all interrupts                |

|           |               |                                  | for next 5 instructions             |

| MO        | OV #0x55,     | WO                               |                                     |

| M         | OV WO, NVI    | MKEY ;                           | Write the 55 key                    |

| MO        | OV #0xAA,     | W1 ;                             |                                     |

| MO        | OV W1, NVI    | MKEY ;                           | Write the AA key                    |

| B         | SET NVMCON    | , #WR ;                          | Start the erase sequence            |

| NO        | ЭР            | ;                                | Insert two NOPs after the erase     |

| N         | OP            | ;                                | command is asserted                 |

|           |               |                                  |                                     |

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE

### 8.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Interrupt Controller, refer to the "dsPIC33/PIC24 Family Reference Manual", "Interrupts" (DS39707).

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. It has the following features:

- Up to eight processor exceptions and software traps

- · Seven user-selectable priority levels

- · Interrupt Vector Table (IVT) with up to 118 vectors

- Unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

#### 8.1 Interrupt Vector Table (IVT)

The IVT is shown in Figure 8-1. The IVT resides in the program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of eight non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

PIC24F16KL402 family devices implement 32 non-maskable traps and unique interrupts; these are summarized in Table 8-1 and Table 8-2.

#### 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE (AIVT)

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

#### 8.2 Reset Sequence

A device Reset is not a true exception, because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset, which forces the Program Counter (PC) to zero. The microcontroller then begins program execution at location, 000000h. The user programs a GOTO instruction at the Reset address, which redirects the program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 8-25: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0          | U-0           | U-0                 | U-0              | U-0               | U-0              | U-0             | U-0   |

|--------------|---------------|---------------------|------------------|-------------------|------------------|-----------------|-------|

| —            | _             | —                   | —                | —                 | —                | —               | —     |

| bit 15       |               |                     |                  |                   |                  |                 | bit 8 |

|              |               |                     |                  |                   |                  |                 |       |

| U-0          | R/W-1         | R/W-0               | R/W-0            | U-0               | U-0              | U-0             | U-0   |

| _            | T3GIP2        | T3GIP1              | T3GIP0           | —                 | —                | —               | —     |

| bit 7        |               |                     |                  |                   |                  |                 | bit 0 |

|              |               |                     |                  |                   |                  |                 |       |

| Legend:      |               |                     |                  |                   |                  |                 |       |

| R = Readab   | le bit        | W = Writable        | bit              | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value a | t POR         | '1' = Bit is set    |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|              |               |                     |                  |                   |                  |                 |       |

| bit 15-7     | Unimplemen    | ted: Read as 'd     | כי               |                   |                  |                 |       |

| bit 6-4      | T3GIP<2:0>:   | Timer3 Externa      | al Gate Interru  | pt Priority bits  |                  |                 |       |

|              | 111 = Interru | pt is Priority 7 (l | highest priority | / interrupt)      |                  |                 |       |

|              | •             |                     |                  |                   |                  |                 |       |

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

#### 10.4 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted, synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption. Meanwhile, the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

#### 10.5 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing, with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMD Control registers.

Both bits have similar functions in enabling or disabling its associated module. Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect, and read values will be invalid. Many peripheral modules have a corresponding PMD bit.

In contrast, disabling a module by clearing its XXXEN bit, disables its functionality, but leaves its registers available to be read and written to. Power consumption is reduced, but not by as much as when the PMD bits are used.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature disables the module while in Idle mode, allowing further reduction of power consumption during Idle mode. This enhances power savings for extremely critical power applications.

#### U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 \_ \_ bit 15 bit 8 R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 P(1) S(1) R/W SMP CKE D/A UA BF bit 7 bit 0 Leaend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-8 Unimplemented: Read as '0' bit 7 SMP: Slew Rate Control bit In Master or Slave mode: 1 = Slew rate control is disabled for Standard Speed mode (100 kHz and 1 MHz) 0 = Slew rate control is enabled for High-Speed mode (400 kHz) bit 6 CKE: SMBus Select bit In Master or Slave mode: 1 = Enables SMBus specific inputs 0 = Disables SMBus specific inputs D/A: Data/Address bit bit 5 In Master mode: Reserved. In Slave mode: 1 = Indicates that the last byte received or transmitted was data 0 = Indicates that the last byte received or transmitted was address P: Stop bit<sup>(1)</sup> bit 4 1 = Indicates that a Stop bit has been detected last 0 = Stop bit was not detected last S: Start bit(1) bit 3 1 = Indicates that a Start bit has been detected last 0 = Start bit was not detected last bit 2 R/W: Read/Write Information bit In Slave mode:(2) 1 = Read 0 = Write In Master mode:(3) 1 = Transmit is in progress 0 = Transmit is not in progress bit 1 **UA:** Update Address bit (10-Bit Slave mode only) 1 = Indicates that the user needs to update the address in the SSPxADD register 0 = Address does not need to be updated Note 1: This bit is cleared on RESET and when SSPEN is cleared. This bit holds the R/W bit information following the last address match. This bit is only valid from the 2: address match to the next Start bit, Stop bit or not ACK bit.

SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C<sup>™</sup> MODE)

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSPx is in Active mode.

**REGISTER 17-2:**

### REGISTER 17-4: SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

| U-0        | U-0                                                                   | U-0                                     | U-0                | U-0                    | U-0                  | U-0                  | U-0                  |

|------------|-----------------------------------------------------------------------|-----------------------------------------|--------------------|------------------------|----------------------|----------------------|----------------------|

| —          | _                                                                     | —                                       |                    | —                      | —                    | —                    | —                    |

| bit 15     |                                                                       |                                         |                    |                        |                      |                      | bit 8                |

|            |                                                                       |                                         |                    |                        |                      |                      |                      |

| R/W-0      | R/W-0                                                                 | R/W-0                                   | R/W-0              | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| WCOL       | SSPOV                                                                 | SSPEN <sup>(1)</sup>                    | CKP                | SSPM3 <sup>(2)</sup>   | SSPM2 <sup>(2)</sup> | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |

| bit 7      |                                                                       |                                         |                    |                        |                      |                      | bit 0                |

|            |                                                                       |                                         |                    |                        |                      |                      |                      |

| Legend:    |                                                                       |                                         |                    |                        |                      |                      |                      |

| R = Read   |                                                                       | W = Writable bi                         | t                  | -                      | ented bit, read      |                      |                      |

| -n = Value | e at POR                                                              | '1' = Bit is set                        |                    | '0' = Bit is clea      | ared                 | x = Bit is unkn      | own                  |

|            |                                                                       |                                         |                    |                        |                      |                      |                      |

| bit 15-8   | -                                                                     | ted: Read as '0'                        |                    |                        |                      |                      |                      |

| bit 7      |                                                                       | e Collision Detect                      | bit                |                        |                      |                      |                      |

|            | $\frac{\text{In Master Tra}}{1 = A \text{ write}}$                    | i <u>nsmit mode:</u><br>to the SSPxBUF  | register wa        | s attempted wh         | ile the $l^2$ C co   | nditions were r      | not valid for a      |

|            |                                                                       | sion to be started                      |                    |                        |                      |                      |                      |

|            | 0 = No collis                                                         | ion                                     |                    |                        |                      |                      |                      |

|            | In Slave Tran                                                         |                                         |                    |                        |                      | .,                   |                      |

|            | 1 = The SSP<br>0 = No collisi                                         | xBUF register is w<br>ion               | ritten while it is | s still transmitting   | the previous wo      | rd (must be clea     | red in software)     |

|            |                                                                       | ode (Master or SI                       | ave modes):        |                        |                      |                      |                      |

|            | This is a "don                                                        |                                         |                    |                        |                      |                      |                      |

| bit 6      | SSPOV: MSS                                                            | SPx Receive Over                        | flow Indicator     | bit                    |                      |                      |                      |

|            | In Receive m                                                          |                                         |                    |                        |                      |                      |                      |

|            | 1 = A byte is<br>0 = No overf                                         | received while the<br>low               | SSPxBUF reg        | ister is still holding | g the previous by    | /te (must be clea    | ired in software)    |

|            | In Transmit m                                                         |                                         |                    |                        |                      |                      |                      |

|            |                                                                       | n't care" bit in Trar                   | smit mode.         |                        |                      |                      |                      |

| bit 5      | SSPEN: MSS                                                            | SPx Enable bit <sup>(1)</sup>           |                    |                        |                      |                      |                      |

|            |                                                                       | the serial port and the serial port and |                    |                        |                      | serial port pins     |                      |

| bit 4      |                                                                       | Release Control bi                      | -                  | lese pills as i/O      | port pins            |                      |                      |

| DIL 4      | In Slave mod                                                          |                                         | ι                  |                        |                      |                      |                      |

|            | 1 = Releases                                                          |                                         |                    |                        |                      |                      |                      |

|            | 0 = Holds clo                                                         | ck low (clock strei                     | ch); used to e     | ensure data setu       | ıp time              |                      |                      |

|            | In Master mo                                                          |                                         |                    |                        |                      |                      |                      |

|            | Unused in thi                                                         |                                         | (2)                |                        |                      |                      |                      |

| bit 3-0    |                                                                       | MSSPx Mode Se                           |                    |                        |                      |                      |                      |

|            |                                                                       | lave mode, 10-bit<br>lave mode, 7-bit a |                    |                        |                      |                      |                      |

|            |                                                                       | irmware Controlle                       |                    |                        |                      | labica               |                      |

|            | 1000 = I <sup>2</sup> C N                                             | laster mode, Cloc                       | k = Fosc/(2 *      |                        | 1)) <sup>(3)</sup>   |                      |                      |

|            |                                                                       | lave mode, 10-bit<br>lave mode, 7-bit a |                    |                        |                      |                      |                      |

|            | $\mathbf{U} \mathbf{T} \mathbf{U} = \mathbf{L} \mathbf{C} \mathbf{S}$ | nave moue, 7-bit a                      | auuress            |                        |                      |                      |                      |

| Note 1:    |                                                                       | d, the SDAx and S                       | -                  | -                      | -                    |                      |                      |

| 2:         | Bit combination                                                       | ons not specifically                    | y listed here a    | are either reserv      | ed or implemen       | ted in SPI mode      | e only.              |

SSPxADD values of 0, 1 or 2 are not supported when the Baud Rate Generator is used with I<sup>2</sup>C mode.

NOTES:

| R/W-0                                                     | U-0                                                                                                                                                                                                          | R/W-0                                                    | U-0           | U-0               | U-0              | U-0            | U-0           |  |  |  |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------|-------------------|------------------|----------------|---------------|--|--|--|

| HLVDEN                                                    |                                                                                                                                                                                                              | HLSIDL                                                   | —             | _                 |                  |                | —             |  |  |  |

| bit 15                                                    |                                                                                                                                                                                                              | -                                                        |               | -                 |                  |                | bit 8         |  |  |  |

|                                                           |                                                                                                                                                                                                              |                                                          |               |                   |                  |                |               |  |  |  |

| R/W-0                                                     | R/W-0                                                                                                                                                                                                        | R/W-0                                                    | U-0           | R/W-0             | R/W-0            | R/W-0          | R/W-0         |  |  |  |

| VDIR                                                      | BGVST                                                                                                                                                                                                        | IRVST                                                    |               | HLVDL3            | HLVDL2           | HLVDL1         | HLVDL0        |  |  |  |

| bit 7                                                     |                                                                                                                                                                                                              |                                                          |               |                   |                  |                | bit C         |  |  |  |

| Legend:                                                   |                                                                                                                                                                                                              |                                                          |               |                   |                  |                |               |  |  |  |

| R = Readabl                                               | le bit                                                                                                                                                                                                       | W = Writable I                                           | oit           | U = Unimplem      | nented bit, read | l as '0'       |               |  |  |  |

| -n = Value at                                             | t POR                                                                                                                                                                                                        | '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |               |                   |                  |                |               |  |  |  |

|                                                           |                                                                                                                                                                                                              |                                                          |               |                   |                  |                |               |  |  |  |

| bit 15                                                    | HLVDEN: Hig                                                                                                                                                                                                  | gh/Low-Voltage                                           | Detect Power  | Enable bit        |                  |                |               |  |  |  |

|                                                           | 1 = HLVD is enabled                                                                                                                                                                                          |                                                          |               |                   |                  |                |               |  |  |  |

|                                                           | 0 = HLVD is                                                                                                                                                                                                  |                                                          |               |                   |                  |                |               |  |  |  |

| bit 14                                                    | Unimplemented: Read as '0'                                                                                                                                                                                   |                                                          |               |                   |                  |                |               |  |  |  |

| bit 13                                                    | HLSIDL: HLVD Stop in Idle Mode bit                                                                                                                                                                           |                                                          |               |                   |                  |                |               |  |  |  |

|                                                           | <ul> <li>1 = Discontinues module operation when the device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                  |                                                          |               |                   |                  |                |               |  |  |  |

| bit 12-8                                                  | Unimplemented: Read as '0'                                                                                                                                                                                   |                                                          |               |                   |                  |                |               |  |  |  |

| bit 7                                                     | VDIR: Voltage Change Direction Select bit                                                                                                                                                                    |                                                          |               |                   |                  |                |               |  |  |  |

|                                                           | 1 = Event occurs when the voltage equals or exceeds the trip point (HLVDL<3:0>)                                                                                                                              |                                                          |               |                   |                  |                |               |  |  |  |

|                                                           | 0 = Event occurs when the voltage equals or falls below the trip point (HLVDL<3:0>)                                                                                                                          |                                                          |               |                   |                  |                |               |  |  |  |

| bit 6                                                     | BGVST: Band Gap Voltage Stable Flag bit                                                                                                                                                                      |                                                          |               |                   |                  |                |               |  |  |  |

|                                                           | <ol> <li>I = Indicates that the band gap voltage is stable</li> <li>Indicates that the band gap voltage is unstable</li> </ol>                                                                               |                                                          |               |                   |                  |                |               |  |  |  |

| bit 5                                                     | 0 = Indicates that the band gap voltage is unstable<br>IRVST: Internal Reference Voltage Stable Flag bit                                                                                                     |                                                          |               |                   |                  |                |               |  |  |  |

| DIL 5                                                     | 1 = Indicates that the internal reference voltage is stable and the High-Voltage Detect logic generates                                                                                                      |                                                          |               |                   |                  |                |               |  |  |  |

|                                                           | the interrupt flag at the specified voltage range                                                                                                                                                            |                                                          |               |                   |                  |                |               |  |  |  |

|                                                           | 0 = Indicates that the internal reference voltage is unstable and the High-Voltage Detect logic will not<br>generate the interrupt flag at the specified voltage range, and the HLVD interrupt should not be |                                                          |               |                   |                  |                |               |  |  |  |

|                                                           | generate<br>enabled                                                                                                                                                                                          | ine interrupt fla                                        | ay at the spe | cilled voltage ra | inge, and the H  | ILVD Interrupt | snould not be |  |  |  |

| bit 4                                                     |                                                                                                                                                                                                              | ted: Read as '0                                          | )'            |                   |                  |                |               |  |  |  |

| bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits |                                                                                                                                                                                                              |                                                          |               |                   |                  |                |               |  |  |  |