Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| 2 0 0 0 0 0                |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 20-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl401-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Analog Features:**

- 10-Bit, up to 12-Channel Analog-to-Digital (A/D) Converter:

- 500 ksps conversion rate

- Conversion available during Sleep and Idle

- Dual Rail-to-Rail Analog Comparators with Programmable Input/Output Configuration

- On-Chip Voltage Reference

### **Special Microcontroller Features:**

- Operating Voltage Range of 1.8V to 3.6V

- 10,000 Erase/Write Cycle Endurance Flash Program Memory, Typical

- 100,000 Erase/Write Cycle Endurance Data EEPROM, Typical

- Flash and Data EEPROM Data Retention: 40 Years Minimum

- Self-Programmable under Software Control

- Programmable Reference Clock Output

- Fail-Safe Clock Monitor (FSCM) Operation:

- Detects clock failure and switches to on-chip, Low-Power RC (LPRC) oscillator

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT):

- Uses its own Low-Power RC oscillator

- Windowed operating modes

- Programmable period of 2 ms to 131s

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and In-Circuit Emulation (ICE) via 2 Pins

- Programmable High/Low-Voltage Detect (HLVD)

- Programmable Brown-out Reset (BOR):

- Configurable for software controlled operation and shutdown in Sleep mode

- Selectable trip points (1.8V, 2.7V and 3.0V)

- Low-power 2.0V POR re-arm

## 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and bussing. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 **Program Address Space**

The program address memory space of the PIC24F16KL402 family is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24F16KL402 family of devices are shown in Figure 4-1.

## FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24F16KL402 FAMILY DEVICES

|                            | PIC24F04KLXXX                                                                                                                                       | PIC24F08KL2XX                                                                                              |  | PIC24F08KL3XX                                                                                              |       | PIC24F08KL4XX                                                                                              | PIC24F16KLXXX                                                                                     |                                                                                    |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                            | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash<br>Program Memory<br>(1408 instructions) | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash |  | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash |       | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table | 000000h<br>00002h<br>00004h<br>0000FEh<br>000100h<br>000104h<br>0001FEh<br>000200h |

| User Memory Space          |                                                                                                                                                     | Program Memory<br>(2816 instructions)                                                                      |  | Program Memory<br>(2816 instructions)                                                                      | -     | Program Memory<br>(2816 instructions)                                                                      | <br>Flash<br>Program Memory<br>(5632 instructions)                                                | - 000AFEh                                                                          |

| User Me                    | Unimplemented<br>Read '0'                                                                                                                           |                                                                                                            |  | Unimplemented<br>Read '0'                                                                                  |       | Unimplemented<br>Read '0'                                                                                  | Unimplemented                                                                                     | 002BFEh                                                                            |

|                            |                                                                                                                                                     |                                                                                                            |  | Data EEPROM<br>(256 bytes)                                                                                 | -<br> | Data EEPROM<br>(512 bytes)                                                                                 | <br>Read '0'<br>Data EEPROM<br>(512 bytes)                                                        | <ul> <li>7FFE00h</li> <li>7FFF00h</li> <li>7FFFFFh</li> <li>800000h</li> </ul>     |

| Ī                          | Reserved                                                                                                                                            | Reserved                                                                                                   |  | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | 800800h                                                                            |

| ace                        | Unique ID                                                                                                                                           | Unique ID                                                                                                  |  | Unique ID                                                                                                  |       | Unique ID                                                                                                  | Unique ID                                                                                         | 800802h<br>800808h                                                                 |

| lory Sp                    | Reserved                                                                                                                                            | Reserved                                                                                                   |  | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | 80080Ah                                                                            |

| Mem                        | Device Config Registers                                                                                                                             | Device Config Registers                                                                                    |  | Device Config Registers                                                                                    |       | Device Config Registers                                                                                    | Device Config Registers                                                                           | F80000h<br>F8000Eh                                                                 |

| Configuration Memory Space | Reserved                                                                                                                                            | Reserved                                                                                                   |  | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | F80010h<br>FEFFFEh                                                                 |

|                            | DEVID (2)                                                                                                                                           | DEVID (2)                                                                                                  |  | DEVID (2)                                                                                                  |       | DEVID (2)                                                                                                  | DEVID (2)                                                                                         | FF0000h<br>FFFFFFh                                                                 |

Note: Memory areas are not displayed to scale.

#### 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

#### 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSC bits in the Flash Configuration Word (FOSCSEL); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

## 7.4 Brown-out Reset (BOR)

PIC24F16KL402 family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above the threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the power-up timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the BOR Reset does not automatically enable the PWRT.

## 7.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<13>). Setting SBOREN enables the BOR to function, as previously described. Clearing the SBOREN disables the BOR entirely. The SBOREN bit only operates in this mode; otherwise, it is read as '0'.

Placing BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

Note: Even when the BOR is under software control, the BOR Reset voltage level is still set by the BORV<1:0> Configuration bits; it can not be changed in software.

### 7.4.2 DETECTING BOR

When BOR is enabled, the BOR bit (RCON<1>) is always reset to '1' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR and BOR bits are reset to '0' in the software, immediately after any POR event. If the BOR bit is '1' while POR is '0', it can be reliably assumed that a BOR event has occurred.

**Note:** Even when the device exits from Deep Sleep mode, both the POR and BOR are set.

#### 7.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, BOR remains under hardware control and operates as previously described. However, whenever the device enters Sleep mode, BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

| U-0          | U-0                        | U-0                                    | U-0              | U-0                                | U-0                   | U-0             | R/W-0  |  |  |  |  |

|--------------|----------------------------|----------------------------------------|------------------|------------------------------------|-----------------------|-----------------|--------|--|--|--|--|

|              | —                          |                                        | —                | —                                  | —                     | —               | HLVDIF |  |  |  |  |

| bit 15       |                            |                                        |                  |                                    |                       |                 | bit 8  |  |  |  |  |

|              |                            |                                        |                  |                                    |                       |                 |        |  |  |  |  |

| U-0          | U-0                        | U-0                                    | U-0              | U-0                                | R/W-0                 | R/W-0           | U-0    |  |  |  |  |

|              |                            |                                        |                  |                                    | U2ERIF <sup>(1)</sup> | U1ERIF          |        |  |  |  |  |

| bit 7        |                            |                                        |                  |                                    |                       |                 | bit 0  |  |  |  |  |

|              |                            |                                        |                  |                                    |                       |                 |        |  |  |  |  |

| Legend:      |                            |                                        |                  |                                    |                       |                 |        |  |  |  |  |

| R = Readal   | ble bit                    | W = Writable                           | bit              | U = Unimplemented bit, read as '0' |                       |                 |        |  |  |  |  |

| -n = Value a | at POR                     | '1' = Bit is set                       |                  | '0' = Bit is clea                  | ared                  | x = Bit is unkn | iown   |  |  |  |  |

|              |                            |                                        |                  |                                    |                       |                 |        |  |  |  |  |

| bit 15-9     | Unimplemen                 | ted: Read as '                         | 0'               |                                    |                       |                 |        |  |  |  |  |

| bit 8        | HLVDIF: High               | n/Low-Voltage [                        | Detect Interrupt | t Flag Status bit                  | t                     |                 |        |  |  |  |  |

|              |                            | request has occ                        |                  |                                    |                       |                 |        |  |  |  |  |

|              | 0 = Interrupt i            | request has not                        | t occurred       |                                    |                       |                 |        |  |  |  |  |

| bit 7-3      | Unimplemen                 | ted: Read as '                         | 0'               |                                    |                       |                 |        |  |  |  |  |

| bit 2        | U2ERIF: UAF                | RT2 Error Interr                       | upt Flag Status  | s bit <sup>(1)</sup>               |                       |                 |        |  |  |  |  |

|              |                            | request has occ                        |                  |                                    |                       |                 |        |  |  |  |  |

|              | 0 = Interrupt i            | 0 = Interrupt request has not occurred |                  |                                    |                       |                 |        |  |  |  |  |

| bit 1        | U1ERIF: UAF                | RT1 Error Interr                       | upt Flag Status  | s bit                              |                       |                 |        |  |  |  |  |

|              |                            | request has occ                        |                  |                                    |                       |                 |        |  |  |  |  |

|              |                            | request has not                        |                  |                                    |                       |                 |        |  |  |  |  |

| bit 0        | Unimplemented: Read as '0' |                                        |                  |                                    |                       |                 |        |  |  |  |  |

#### REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

Note 1: This bit is unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

#### REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0                                   | U-0   | U-0              | U-0              | U-0               | U-0                                | U-0                | U-0     |  |

|---------------------------------------|-------|------------------|------------------|-------------------|------------------------------------|--------------------|---------|--|

| _                                     | —     | _                | —                | —                 | —                                  | —                  | —       |  |

| bit 15                                |       |                  |                  |                   |                                    |                    | bit 8   |  |

|                                       |       |                  |                  |                   |                                    |                    |         |  |

| U-0                                   | U-0   | U-0              | U-0              | U-0               | U-0                                | U-0                | R/W-0   |  |

| —                                     | —     | —                | —                | —                 | —                                  | —                  | ULPWUIF |  |

| bit 7                                 |       |                  |                  |                   |                                    |                    | bit 0   |  |

|                                       |       |                  |                  |                   |                                    |                    |         |  |

| Legend:                               |       |                  |                  |                   |                                    |                    |         |  |

| R = Readable                          | e bit | W = Writable     | W = Writable bit |                   | U = Unimplemented bit, read as '0' |                    |         |  |

| -n = Value at POR '1' = B             |       | '1' = Bit is set |                  | '0' = Bit is clea | ared                               | x = Bit is unknown |         |  |

| R = Readable bit<br>-n = Value at POR |       |                  |                  |                   |                                    |                    | nown    |  |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

| R/W-0        | U-0            | R/W-0            | U-0             | U-0                                | U-0         | U-0                | R/W-0   |  |  |

|--------------|----------------|------------------|-----------------|------------------------------------|-------------|--------------------|---------|--|--|

| ULPEN        |                | ULPSIDL          | _               | —                                  | _           |                    | ULPSINK |  |  |

| bit 15       |                |                  |                 |                                    |             |                    | bit 8   |  |  |

|              |                |                  |                 |                                    |             |                    |         |  |  |

| U-0          | U-0            | U-0              | U-0             | U-0                                | U-0         | U-0                | U-0     |  |  |

|              |                | —                | —               |                                    | —           |                    |         |  |  |

| bit 7        |                |                  |                 |                                    |             |                    | bit 0   |  |  |

| l            |                |                  |                 |                                    |             |                    | 1       |  |  |

| Legend:      |                |                  |                 |                                    |             |                    |         |  |  |

| R = Readat   | ole bit        | W = Writable     | bit             | U = Unimplemented bit, read as '0' |             |                    |         |  |  |

| -n = Value a | at POR         | '1' = Bit is set |                 | '0' = Bit is clea                  | ared        | x = Bit is unknown |         |  |  |

|              |                |                  |                 |                                    |             |                    |         |  |  |

| bit 15       | ULPEN: ULP     | WU Module En     | able bit        |                                    |             |                    |         |  |  |

|              | 1 = Module is  |                  |                 |                                    |             |                    |         |  |  |

|              | 0 = Module is  | disabled         |                 |                                    |             |                    |         |  |  |

| bit 14       | Unimplemen     | ted: Read as '   | כ'              |                                    |             |                    |         |  |  |

| bit 13       | ULPSIDL: UL    | PWU Stop in I    | dle Select bit  |                                    |             |                    |         |  |  |

|              |                |                  |                 | ne device enters                   | s Idle mode |                    |         |  |  |

|              | 0 = Continues  | s module opera   | tion in Idle mo | de                                 |             |                    |         |  |  |

| bit 12-9     | Unimplemen     | ted: Read as '   | כ'              |                                    |             |                    |         |  |  |

| bit 8        | ULPSINK: UL    | _PWU Current     | Sink Enable bi  | t                                  |             |                    |         |  |  |

|              | 1 = Current si | ink is enabled   |                 |                                    |             |                    |         |  |  |

|              | 0 = Current si | ink is disabled  |                 |                                    |             |                    |         |  |  |

| bit 7-0      | Unimplemen     | ted: Read as '   | כ'              |                                    |             |                    |         |  |  |

|              |                |                  |                 |                                    |             |                    |         |  |  |

#### REGISTER 10-1: ULPWCON: ULPWU CONTROL REGISTER

| U-0       | U-0                            | U-0                                          | U-0            | U-0               | U-0    | U-0                | U-0     |  |  |  |  |

|-----------|--------------------------------|----------------------------------------------|----------------|-------------------|--------|--------------------|---------|--|--|--|--|

| _         |                                | <u> </u>                                     | —              | <u> </u>          | —      | <u> </u>           |         |  |  |  |  |

| pit 15    |                                |                                              |                |                   |        |                    | bit 8   |  |  |  |  |

|           |                                |                                              |                |                   |        |                    |         |  |  |  |  |

| U-0       | R/W-0                          | R/W-0                                        | R/W-0          | R/W-0             | R/W-0  | R/W-0              | R/W-0   |  |  |  |  |

|           | T4OUTPS3                       | T4OUTPS2                                     | T4OUTPS1       | T4OUTPS0          | TMR4ON | T4CKPS1            | T4CKPS0 |  |  |  |  |

| oit 7     |                                |                                              |                |                   |        |                    | bit C   |  |  |  |  |

|           |                                |                                              |                |                   |        |                    |         |  |  |  |  |

| egend:    |                                |                                              |                |                   |        |                    |         |  |  |  |  |

| R = Reada |                                | W = Writable                                 | bit            | U = Unimplem      |        |                    | as '0'  |  |  |  |  |

| n = Value | at POR                         | '1' = Bit is set                             |                | '0' = Bit is clea | ared   | x = Bit is unknown |         |  |  |  |  |

| oit 15-7  |                                | ted. Deed oo W                               | <b>,</b>       |                   |        |                    |         |  |  |  |  |

|           | -                              | ted: Read as '                               |                | <b>_</b>          |        |                    |         |  |  |  |  |

| oit 6-3   |                                | <b>0&gt;:</b> Timer4 Ou                      | tput Postscale | Select bits       |        |                    |         |  |  |  |  |

|           | 1111 = 1:16  <br>1110 = 1:15   |                                              |                |                   |        |                    |         |  |  |  |  |

|           | •                              | OSISCAIE                                     |                |                   |        |                    |         |  |  |  |  |

|           | •                              |                                              |                |                   |        |                    |         |  |  |  |  |

|           | •                              | •                                            |                |                   |        |                    |         |  |  |  |  |

|           |                                | 0001 = 1:2 Postscale<br>0000 = 1:1 Postscale |                |                   |        |                    |         |  |  |  |  |

| oit 2     | TMR4ON: Tir                    | ner4 On bit                                  |                |                   |        |                    |         |  |  |  |  |

|           | 1 = Timer4 is<br>0 = Timer4 is |                                              |                |                   |        |                    |         |  |  |  |  |

| oit 1-0   | T4CKPS<1:0                     | >: Timer4 Cloc                               | k Prescale Sel | ect bits          |        |                    |         |  |  |  |  |

|           | 10 = Prescaler is  16          |                                              |                |                   |        |                    |         |  |  |  |  |

|           | 01 = Prescaler is 4            |                                              |                |                   |        |                    |         |  |  |  |  |

|           |                                | -                                            |                |                   |        |                    |         |  |  |  |  |

## REGISTER 15-1: T4CON: TIMER4 CONTROL REGISTER

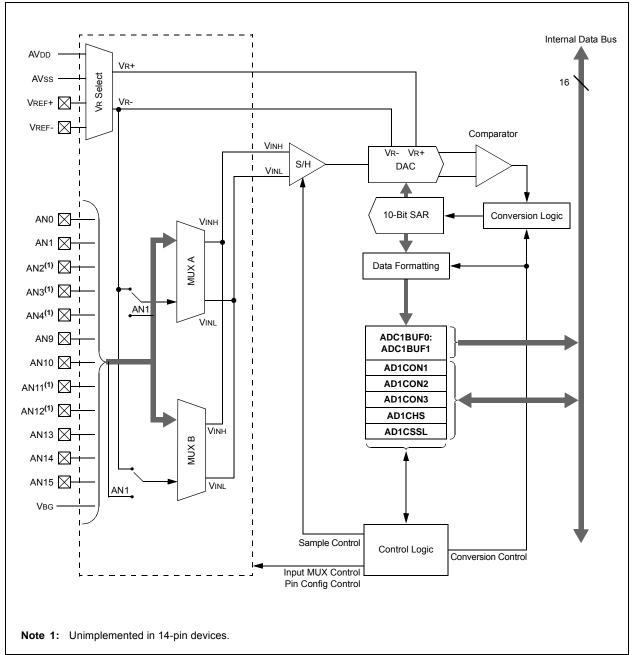

#### FIGURE 19-1: 10-BIT HIGH-SPEED A/D CONVERTER BLOCK DIAGRAM

| R/W-0        | U-0                                                                                                                                                                                | U-0                                                                                                                     | U-0                                | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|------------------|-----------------|--------|--|

| CH0NB        | —                                                                                                                                                                                  | —                                                                                                                       | _                                  | CH0SB3            | CH0SB2           | CH0SB1          | CH0SB0 |  |

| bit 15       |                                                                                                                                                                                    |                                                                                                                         |                                    |                   |                  |                 | bit 8  |  |

|              |                                                                                                                                                                                    |                                                                                                                         |                                    |                   |                  |                 |        |  |

| R/W-0        | U-0                                                                                                                                                                                | U-0                                                                                                                     | U-0                                | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |

| CH0NA        |                                                                                                                                                                                    |                                                                                                                         |                                    | CH0SA3            | CH0SA2           | CH0SA1          | CH0SA0 |  |

| bit 7        |                                                                                                                                                                                    |                                                                                                                         |                                    |                   |                  |                 | bit C  |  |

| Legend:      |                                                                                                                                                                                    |                                                                                                                         |                                    |                   |                  |                 |        |  |

| R = Readab   | le bit                                                                                                                                                                             | W = Writable                                                                                                            | bit                                | U = Unimplem      | nented bit, read | 1 as '0'        |        |  |

| -n = Value a | It POR                                                                                                                                                                             | '1' = Bit is set                                                                                                        | t                                  | '0' = Bit is clea | ared             | x = Bit is unkr | iown   |  |

|              | 0111 = Low<br>0110 = Inter                                                                                                                                                         | 4<br>3<br>2(1)<br>1(1)<br>0<br>er guardband ra<br>er guardband ra<br>rnal band gap re<br>erved; do not us<br>(1)<br>(1) | iil (0.215 * VDI<br>eference (VBG) | )<br>)            |                  |                 |        |  |

| bit 7        | 0001 = AN1<br>0000 = AN0<br>CH0NA: Channel 0 Negative Input Select for MUX A Multiplexer Setting bit<br>1 = Channel 0 negative input is AN1<br>0 = Channel 0 negative input is VR- |                                                                                                                         |                                    |                   |                  |                 |        |  |

| bit 6-4      | Unimplemented: Read as '0'                                                                                                                                                         |                                                                                                                         |                                    |                   |                  |                 |        |  |

|              | Unimpleme                                                                                                                                                                          | nted: Read as '                                                                                                         | 0'                                 |                   |                  |                 |        |  |

### REGISTER 19-4: AD1CHS: A/D INPUT SELECT REGISTER

Note 1: Unimplemented on 14-pin devices; do not use.

#### REGISTER 20-1: CMxCON: COMPARATOR x CONTROL REGISTER

| R/W-0      | R/W-0                                | R/W-0                                                                                                                                                                                  | R/W-0             | U-0              | U-0              | R/W-0                               | R-0            |  |  |

|------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|-------------------------------------|----------------|--|--|

| CON        | COE                                  | CPOL                                                                                                                                                                                   | CLPWR             |                  | _                | CEVT                                | COUT           |  |  |

| bit 15     |                                      |                                                                                                                                                                                        | •                 |                  | •                |                                     | bit            |  |  |

|            |                                      |                                                                                                                                                                                        |                   |                  |                  |                                     |                |  |  |

| R/W-0      | R/W-0                                | U-0                                                                                                                                                                                    | R/W-0             | U-0              | U-0              | R/W-0                               | R/W-0          |  |  |

| EVPOL1     | <sup>(1)</sup> EVPOL0 <sup>(1)</sup> |                                                                                                                                                                                        | CREF              |                  |                  | CCH1                                | CCH0           |  |  |

| bit 7      |                                      |                                                                                                                                                                                        |                   |                  |                  |                                     | bit            |  |  |

| Legend:    |                                      |                                                                                                                                                                                        |                   |                  |                  |                                     |                |  |  |

| R = Reada  | abla bit                             | W = Writable                                                                                                                                                                           | hit               |                  | montod bit roo   | d aa '0'                            |                |  |  |

|            |                                      |                                                                                                                                                                                        |                   |                  | nented bit, rea  |                                     |                |  |  |

| -n = Value | atPOR                                | '1' = Bit is se                                                                                                                                                                        | [                 | '0' = Bit is cle | ared             | x = Bit is unkn                     | iown           |  |  |

| bit 15     | CON: Compa                           | arator Enable b                                                                                                                                                                        | it                |                  |                  |                                     |                |  |  |

|            | •                                    | ator is enabled                                                                                                                                                                        |                   |                  |                  |                                     |                |  |  |

|            |                                      | ator is disabled                                                                                                                                                                       |                   |                  |                  |                                     |                |  |  |

| bit 14     | COE: Compa                           | arator Output E                                                                                                                                                                        | nable bit         |                  |                  |                                     |                |  |  |

|            |                                      |                                                                                                                                                                                        | resent on the C   | kOUT pin         |                  |                                     |                |  |  |

|            | -                                    | ator output is in                                                                                                                                                                      | -                 |                  |                  |                                     |                |  |  |

| bit 13     |                                      | •                                                                                                                                                                                      | Polarity Select b | bit              |                  |                                     |                |  |  |

|            |                                      | ator output is in                                                                                                                                                                      |                   |                  |                  |                                     |                |  |  |

| bit 12     | -                                    | <ul> <li>0 = Comparator output is not inverted</li> <li>CLPWR: Comparator Low-Power Mode Select bit</li> </ul>                                                                         |                   |                  |                  |                                     |                |  |  |

|            |                                      | •                                                                                                                                                                                      | Low-Power mo      |                  |                  |                                     |                |  |  |

|            |                                      |                                                                                                                                                                                        | perate in Low-Po  |                  |                  |                                     |                |  |  |

| bit 11-10  | Unimplemer                           | Unimplemented: Read as '0'                                                                                                                                                             |                   |                  |                  |                                     |                |  |  |

| bit 9      | CEVT: Comp                           | arator Event bi                                                                                                                                                                        | t                 |                  |                  |                                     |                |  |  |

|            | 1 = Compara                          | ator event defir                                                                                                                                                                       | ned by EVPOL<     | 1:0> has occu    | ırred; subsequ   | ent triggers and                    | interrupts a   |  |  |

|            |                                      | until the bit is o                                                                                                                                                                     |                   |                  |                  |                                     |                |  |  |

|            | -                                    | ator event has                                                                                                                                                                         |                   |                  |                  |                                     |                |  |  |

| bit 8      |                                      | parator Output                                                                                                                                                                         | bit               |                  |                  |                                     |                |  |  |

|            | <u>When CPOL</u><br>1 = VIN+ > V     |                                                                                                                                                                                        |                   |                  |                  |                                     |                |  |  |

|            | 0 = VIN + < V                        |                                                                                                                                                                                        |                   |                  |                  |                                     |                |  |  |

|            | When CPOL                            |                                                                                                                                                                                        |                   |                  |                  |                                     |                |  |  |

|            | 1 = VIN+ < V                         |                                                                                                                                                                                        |                   |                  |                  |                                     |                |  |  |

|            | 0 = VIN + > V                        |                                                                                                                                                                                        |                   |                  |                  |                                     |                |  |  |

| bit 7-6    |                                      |                                                                                                                                                                                        | t/Interrupt Polar |                  |                  |                                     |                |  |  |

|            |                                      | rigger/event/interrupt is generated on any change of the comparator output (while CEVT = 0) rigger/event/interrupt is generated on the high-to-low transition of the comparator output |                   |                  |                  |                                     |                |  |  |

|            |                                      |                                                                                                                                                                                        |                   |                  |                  | f the comparato<br>of the comparato |                |  |  |

|            |                                      |                                                                                                                                                                                        | t generation is o |                  | Ign transition o |                                     | output         |  |  |

| bit 5      |                                      | nted: Read as                                                                                                                                                                          | •                 |                  |                  |                                     |                |  |  |

| bit 4      | -                                    |                                                                                                                                                                                        | ice Select bits ( | non-invertina ii | nput)            |                                     |                |  |  |

|            |                                      |                                                                                                                                                                                        | nects to the inte | -                |                  |                                     |                |  |  |

|            |                                      |                                                                                                                                                                                        | nects to the CxI  |                  | J                |                                     |                |  |  |

| Note 1:    | If EVPOL<1:0> is                     | s set to a value                                                                                                                                                                       | other than '00'.  | the first interr | upt generated    | will occur on an                    | y transition c |  |  |

|            | COUT, regardles                      |                                                                                                                                                                                        |                   |                  |                  |                                     |                |  |  |

|            | bits setting.                        |                                                                                                                                                                                        |                   |                  |                  |                                     |                |  |  |

2: Unimplemented on 14-pin (PIC24FXXKL100/200) devices.

## 25.0 INSTRUCTION SET SUMMARY

**Note:** This chapter is a brief summary of the PIC24F Instruction Set Architecture (ISA) and is not intended to be a comprehensive reference source.

The PIC24F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

Table 25-1 lists the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 25-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value, 'f'

- The destination, which could either be the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register, 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the Table Read and Table Write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all of the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all Table Reads and Table Writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

| Assembly<br>Mnemonic |        | Assembly Syntax  | Description                                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|------------------|----------------------------------------------|---------------|----------------|--------------------------|

| GOTO                 | GOTO   | Expr             | Go to Address                                | 2             | 2              | None                     |

|                      | GOTO   | Wn               | Go to Indirect                               | 1             | 2              | None                     |

| INC                  | INC    | f                | f = f + 1                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | f,WREG           | WREG = f + 1                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | Ws,Wd            | Wd = Ws + 1                                  | 1             | 1              | C, DC, N, OV, Z          |

| INC2                 | INC2   | f                | f = f + 2                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | f,WREG           | WREG = f + 2                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | Ws,Wd            | Wd = Ws + 2                                  | 1             | 1              | C, DC, N, OV, Z          |

| IOR                  | IOR    | f                | f = f .IOR. WREG                             | 1             | 1              | N, Z                     |

|                      | IOR    | f,WREG           | WREG = f .IOR. WREG                          | 1             | 1              | N, Z                     |

|                      | IOR    | #lit10,Wn        | Wd = lit10 .IOR. Wd                          | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,Ws,Wd         | Wd = Wb .IOR. Ws                             | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,#lit5,Wd      | Wd = Wb .IOR. lit5                           | 1             | 1              | N, Z                     |

| LNK                  | LNK    | #lit14           | Link Frame Pointer                           | 1             | 1              | None                     |

| LSR                  | LSR    | f                | f = Logical Right Shift f                    | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | f,WREG           | WREG = Logical Right Shift f                 | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Ws,Wd            | Wd = Logical Right Shift Ws                  | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Wb,Wns,Wnd       | Wnd = Logical Right Shift Wb by Wns          | 1             | 1              | N, Z                     |

|                      | LSR    | Wb,#lit5,Wnd     | Wnd = Logical Right Shift Wb by lit5         | 1             | 1              | N, Z                     |

| MOV                  | MOV    | f,Wn             | Move f to Wn                                 | 1             | 1              | None                     |

|                      | MOV    | [Wns+Slit10],Wnd | Move [Wns+Slit10] to Wnd                     | 1             | 1              | None                     |

|                      | MOV    | f                | Move f to f                                  | 1             | 1              | N, Z                     |

|                      | MOV    | f,WREG           | Move f to WREG                               | 1             | 1              | None                     |

|                      | MOV    | #lit16,Wn        | Move 16-bit Literal to Wn                    | 1             | 1              | None                     |

|                      | MOV.b  | #lit8,Wn         | Move 8-bit Literal to Wn                     | 1             | 1              | None                     |

|                      | MOV    | Wn,f             | Move Wn to f                                 | 1             | 1              | None                     |

|                      | MOV    | Wns,[Wns+Slit10] | Move Wns to [Wns+Slit10]                     | 1             | 1              | None                     |

|                      | MOV    | Wso,Wdo          | Move Ws to Wd                                | 1             | 1              | None                     |

|                      | MOV    | WREG, f          | Move WREG to f                               | 1             | 1              | None                     |

|                      | MOV.D  | Wns,Wd           | Move Double from W(ns):W(ns+1) to Wd         | 1             | 2              | None                     |

|                      | MOV.D  | Ws,Wnd           | Move Double from Ws to W(nd+1):W(nd)         | 1             | 2              | None                     |

| MUL                  | MUL.SS | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Signed(Ws)       | 1             | 1              | None                     |

|                      | MUL.SU | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(Ws)     | 1             | 1              | None                     |

|                      | MUL.US | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Unsigned(Wb) * Signed(Ws)     | 1             | 1              | None                     |

|                      | MUL.UU | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(Ws)   | 1             | 1              | None                     |

|                      | MUL.SU | Wb,#lit5,Wnd     | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(lit5)   | 1             | 1              | None                     |

|                      | MUL.UU | Wb,#lit5,Wnd     | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(lit5) | 1             | 1              | None                     |

|                      | MUL    | f                | W3:W2 = f * WREG                             | 1             | 1              | None                     |

| NEG                  | NEG    | f                | $f = \overline{f} + 1$                       | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG    | f,WREG           | WREG = $\overline{f}$ + 1                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG    | Ws,Wd            | $Wd = \overline{Ws} + 1$                     | 1             | 1              | C, DC, N, OV, Z          |

| NOP                  | NOP    | wa, wa           | No Operation                                 | 1             | 1              | None                     |

| 1101                 | NOP    |                  | No Operation                                 | 1             | 1              | None                     |

| POP                  | POP    | f                | Pop f from Top-of-Stack (TOS)                | 1             | 1              | None                     |

| 1.01                 | POP    | Wdo              | Pop from Top-of-Stack (TOS) to Wdo           | 1             | 1              | None                     |

|                      | POP.D  | Wdo              | Pop from Top-of-Stack (TOS) to Wdb           | 1             | 2              | None                     |

|                      | POP.S  | WILU             | Pop Shadow Registers                         | 1             | 1              | All                      |

| סוופע                |        | f                | Push f to Top-of-Stack (TOS)                 | 1             | 1              | None                     |

| PUSH                 | PUSH   |                  | , ,                                          |               |                |                          |

|                      | PUSH   | Wso              | Push Wso to Top-of-Stack (TOS)               | 1             | 1              | None                     |

|                      | PUSH.D | Wns              | Push W(ns):W(ns+1) to Top-of-Stack (TOS)     | 1             | 2              | None                     |

### TABLE 25-2: INSTRUCTION SET OVERVIEW (CONTINUED)

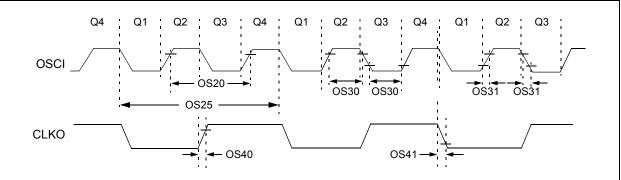

#### TABLE 26-18: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               |                                                                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |                    |                          |                                      |

|--------------------|---------------|-------------------------------------------------------------------------|------------------------------------------------------|--------------------|--------------------|--------------------------|--------------------------------------|

| Param<br>No.       | Sym           | Characteristic                                                          | Min                                                  | Typ <sup>(1)</sup> | Max                | Units                    | Conditions                           |

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks allowed<br>only in EC mode) | DC<br>4                                              | _                  | 32<br>8            | MHz<br>MHz               | EC<br>ECPLL                          |

|                    |               | Oscillator Frequency                                                    | 0.2<br>4<br>4<br>31                                  |                    | 4<br>25<br>8<br>33 | MHz<br>MHz<br>MHz<br>kHz | XT<br>HS<br>HSPLL<br>SOSC            |

| OS20               | Tosc          | Tosc = 1/Fosc                                                           | —                                                    | _                  |                    | —                        | See Parameter OS10 for<br>Fosc value |

| OS25               | TCY           | Instruction Cycle Time <sup>(2)</sup>                                   | 62.5                                                 | _                  | DC                 | ns                       |                                      |

| OS30               | TosL,<br>TosH | External Clock in (OSCI)<br>High or Low Time                            | 0.45 x Tosc                                          | —                  | _                  | ns                       | EC                                   |

| OS31               | TosR,<br>TosF | External Clock in (OSCI)<br>Rise or Fall Time                           | —                                                    | —                  | 20                 | ns                       | EC                                   |

| OS40               | TckR          | CLKO Rise Time <sup>(3)</sup>                                           | —                                                    | 6                  | 10                 | ns                       |                                      |

| OS41               | TckF          | CLKO Fall Time <sup>(3)</sup>                                           | —                                                    | 6                  | 10                 | ns                       |                                      |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Instruction cycle period (TCY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

**3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 TCY) and high for the Q3-Q4 period (1/2 TCY).

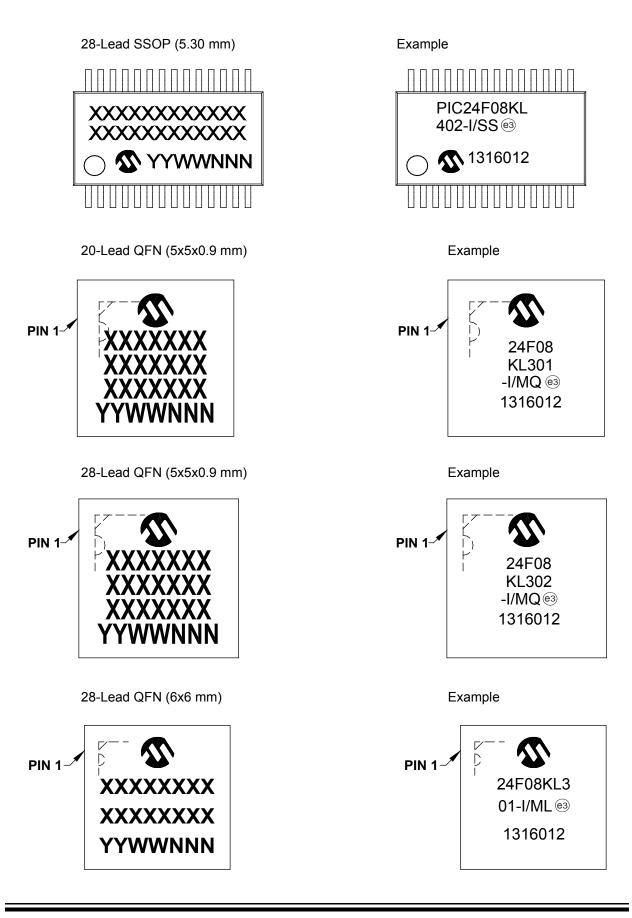

20-Lead SOIC (7.50 mm)

Example

28-Lead SOIC (7.50 mm)

14-Lead TSSOP (4.4 mm)

20-Lead SSOP (5.30 mm)

Example

Example

Example

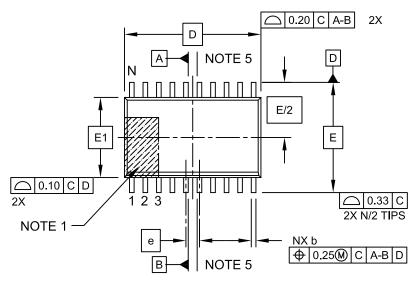

### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

TOP VIEW

VIEW A-A

Microchip Technology Drawing C04-094C Sheet 1 of 2

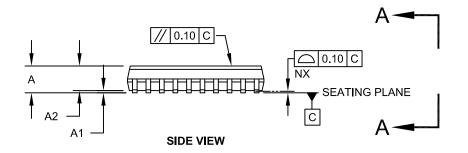

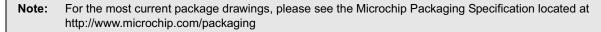

## 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

|                        | Units            | MILLIMETERS |          |      |  |

|------------------------|------------------|-------------|----------|------|--|

|                        | Dimension Limits | MIN         | NOM      | MAX  |  |

| Number of Pins         | N                |             | 28       |      |  |

| Pitch                  | e                |             | 0.65 BSC |      |  |

| Overall Height         | A                | 0.80        | 0.90     | 1.00 |  |

| Standoff               | A1               | 0.00        | 0.02     | 0.05 |  |

| Contact Thickness      | A3               |             | 0.20 REF |      |  |

| Overall Width          | E                | 6.00 BSC    |          |      |  |

| Exposed Pad Width      | E2               | 3.65        | 3.70     | 4.20 |  |

| Overall Length         | D                |             | 6.00 BSC |      |  |

| Exposed Pad Length     | D2               | 3.65        | 3.70     | 4.20 |  |

| Contact Width          | b                | 0.23        | 0.30     | 0.35 |  |

| Contact Length         | L                | 0.50        | 0.55     | 0.70 |  |

| Contact-to-Exposed Pad | К                | 0.20        | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

NOTES:

NOTES:

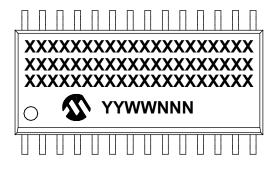

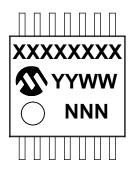

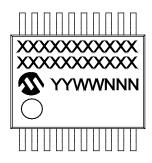

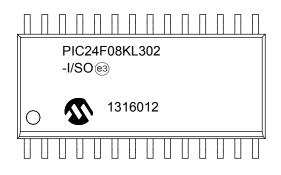

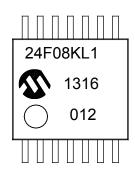

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.