# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 18                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

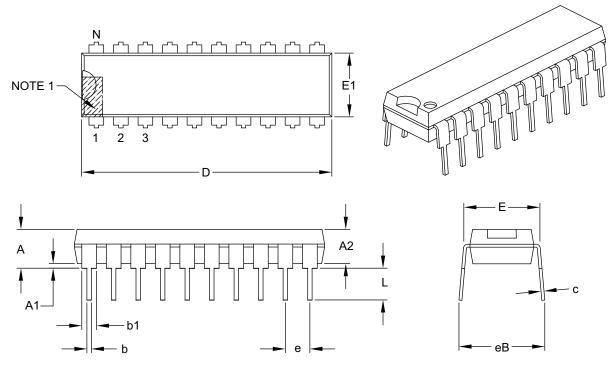

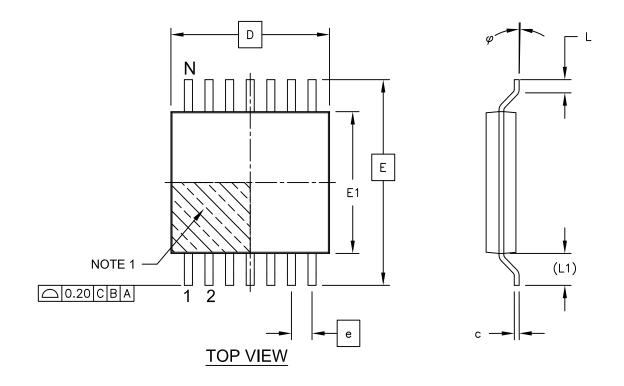

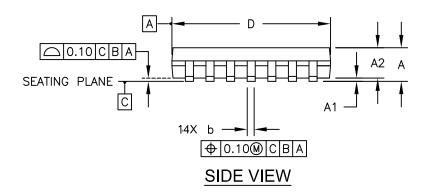

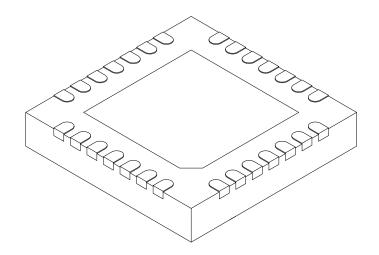

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl401t-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 3.0 CPU

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the CPU, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"CPU"** (DS39703).

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16<sup>th</sup> Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K word boundary of either program memory or data EEPROM memory, defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (i.e., A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by a 16-bit integer signed and unsigned division. All divide operations require 19 cycles to complete, but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme, with up to eight sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is illustrated in Figure 3-1.

## 3.1 Programmer's Model

Figure 3-2 displays the programmer's model for the PIC24F. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions.

Table 3-1 provides a description of each register. All registers associated with the programmer's model are memory mapped.

## 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing it is not recommended.

All of the Table Write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

## 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. For more information, refer to **Section 5.5 "Programming Operations"**.

## 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

| // C example using MPLAB C30                                                                  |                                                                                     |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| <pre>intattribute ((space(auto_psv))) progAddr = &amp;progAddr<br/>unsigned int offset;</pre> | // Global variable located in Pgm Memory $% \mathcal{T}_{\mathcal{T}}$              |

| //Set up pointer to the first memory location to be written                                   |                                                                                     |

| <pre>TBLPAG =builtin_tblpage(&amp;progAddr); offset = &amp;progAddr &amp; 0xFFFF;</pre>       | // Initialize PM Page Boundary SFR<br>// Initialize lower word of address           |

| <pre>builtin_tblwtl(offset, 0x0000);</pre>                                                    | <pre>// Set base address of erase block // with dummy latch write</pre>             |

| NVMCON = $0 \times 4058$ ;                                                                    | // Initialize NVMCON                                                                |

| <pre>asm("DISI #5");</pre>                                                                    | <pre>// Block all interrupts for next 5 // instructions</pre>                       |

| builtin_write_NVM();                                                                          | <pre>// Instructions // C30 function to perform unlock // sequence and set WR</pre> |

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| MOV #0x4004, W0 ;                                                     |       |

|-----------------------------------------------------------------------|-------|

|                                                                       |       |

| MOV W0, NVMCON ; Initialize NVMCON                                    |       |

| ; Set up a pointer to the first program memory location to be written |       |

| ; program memory selected, and writes enabled                         |       |

| MOV #0x0000, W0 ;                                                     |       |

| MOV W0, TBLPAG ; Initialize PM Page Boundary SFR                      |       |

| MOV #0x6000, W0 ; An example program memory addre                     | SS    |

| ; Perform the TBLWT instructions to write the latches                 |       |

| ; 0th_program_word                                                    |       |

| MOV #LOW_WORD_0, W2 ;                                                 |       |

| MOV #HIGH_BYTE_0, W3 ;                                                |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      | latch |

| TBLWTH W3, [W0++] ; Write PM high byte into program                   | latch |

| ; lst_program_word                                                    |       |

| MOV #LOW_WORD_1, W2 ;                                                 |       |

| MOV #HIGH_BYTE_1, W3 ;                                                |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      | latch |

| TBLWTH W3, [W0++] ; Write PM high byte into program                   | latch |

| ; 2nd_program_word                                                    |       |

| MOV #LOW_WORD_2, W2 ;                                                 |       |

| MOV #HIGH_BYTE_2, W3 ;                                                |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      | latch |

| TBLWTH W3, [W0++] ; Write PM high byte into program                   | latch |

| •                                                                     |       |

| •                                                                     |       |

| · ·                                                                   |       |

| ; 32nd_program_word                                                   |       |

| MOV #LOW_WORD_31, W2 ;                                                |       |

| MOV #HIGH_BYTE_31, W3 ;                                               |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      |       |

| TBLWTH W3, [W0]   ; Write PM high byte into program                   | latch |

### 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

### 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

### 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSC bits in the Flash Configuration Word (FOSCSEL); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

## 7.4 Brown-out Reset (BOR)

PIC24F16KL402 family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above the threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the power-up timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the BOR Reset does not automatically enable the PWRT.

## 7.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<13>). Setting SBOREN enables the BOR to function, as previously described. Clearing the SBOREN disables the BOR entirely. The SBOREN bit only operates in this mode; otherwise, it is read as '0'.

Placing BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

Note: Even when the BOR is under software control, the BOR Reset voltage level is still set by the BORV<1:0> Configuration bits; it can not be changed in software.

### 10.4 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted, synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption. Meanwhile, the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

### 10.5 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing, with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMD Control registers.

Both bits have similar functions in enabling or disabling its associated module. Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect, and read values will be invalid. Many peripheral modules have a corresponding PMD bit.

In contrast, disabling a module by clearing its XXXEN bit, disables its functionality, but leaves its registers available to be read and written to. Power consumption is reduced, but not by as much as when the PMD bits are used.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature disables the module while in Idle mode, allowing further reduction of power consumption during Idle mode. This enhances power savings for extremely critical power applications.

### REGISTER 17-3: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|--------------|-----|-----|-----|-----|-----|-----|-----|

| —            | —   | —   | —   | —   | —   | —   | —   |

| bit 15 bit 8 |     |     |     |     |     |     |     |

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | CKP   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

| Legend:   |                                                                          |                                                                   |                                                         |                                                       |  |  |  |

|-----------|--------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------|--|--|--|

| R = Read  | lable bit                                                                | W = Writable bit                                                  | U = Unimplemented bit                                   | , read as '0'                                         |  |  |  |

| -n = Valu | n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |                                                                   |                                                         |                                                       |  |  |  |

|           |                                                                          |                                                                   |                                                         |                                                       |  |  |  |

| bit 15-8  | Unimple                                                                  | mented: Read as '0'                                               |                                                         |                                                       |  |  |  |

| bit 7     | WCOL: \                                                                  | Nrite Collision Detect bit                                        |                                                         |                                                       |  |  |  |

|           |                                                                          | 0                                                                 | while it is still transmitting the                      | e previous word (must be cleared                      |  |  |  |

|           | in sc<br>0 = No c                                                        | ftware)                                                           |                                                         |                                                       |  |  |  |

| bit 6     |                                                                          | MSSPx Receive Overflow In                                         | diaatar hit(1)                                          |                                                       |  |  |  |

| DILO      | SPI Slav                                                                 |                                                                   |                                                         |                                                       |  |  |  |

|           |                                                                          |                                                                   | SPxBUF register is still holding                        | the previous data. In case of over-                   |  |  |  |

|           |                                                                          |                                                                   |                                                         | ave mode. The user must read the                      |  |  |  |

|           |                                                                          |                                                                   | ng data, to avoid setting overflo                       | ow (must be cleared in software).                     |  |  |  |

|           | 0 = No o                                                                 |                                                                   |                                                         |                                                       |  |  |  |

| bit 5     |                                                                          | MSSPx Enable bit <sup>(2)</sup>                                   |                                                         |                                                       |  |  |  |

|           |                                                                          | bles serial port and configures<br>bles serial port and configure | s SCKx, SDOx, SDIx and $\overline{SSx}$                 | as serial port pins                                   |  |  |  |

| bit 4     |                                                                          | ock Polarity Select bit                                           |                                                         |                                                       |  |  |  |

| DIL 4     |                                                                          | state for clock is a high level                                   |                                                         |                                                       |  |  |  |

|           |                                                                          | state for clock is a low level                                    |                                                         |                                                       |  |  |  |

| bit 3-0   | SSPM<3                                                                   | :0>: MSSPx Mode Select bit                                        | <sub>S</sub> (3)                                        |                                                       |  |  |  |

|           | 1010 = \$                                                                | SPI Master mode, Clock = Fo                                       | osc/(2 * ([SSPxADD] + 1)) <sup>(4)</sup>                |                                                       |  |  |  |

|           | 0101 = 5                                                                 | SPI Slave mode, Clock = SCk                                       | (x pin; SSx pin control is disabl                       | ed, $\overline{\text{SSx}}$ can be used as an I/O pin |  |  |  |

|           |                                                                          |                                                                   | <pre>Kx pin; SSx pin control is enab ABA subset/0</pre> | led                                                   |  |  |  |

|           |                                                                          | SPI Master mode, Clock = TN<br>SPI Master mode, Clock = Fc        | •                                                       |                                                       |  |  |  |

|           |                                                                          | SPI Master mode, Clock = Fo                                       |                                                         |                                                       |  |  |  |

|           |                                                                          | SPI Master mode, Clock = Fo                                       |                                                         |                                                       |  |  |  |

| Note 1:   | In Master mo                                                             | de the overflow bit is not se                                     | t since each new reception (ar                          | nd transmission) is initiated by                      |  |  |  |

|           |                                                                          | SSPxBUF register.                                                 |                                                         |                                                       |  |  |  |

| •         | -<br>\\\/h======h=h=                                                     | -                                                                 | why according used as instant on a star                 |                                                       |  |  |  |

- 2: When enabled, these pins must be properly configured as input or output.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C mode only.

- 4: SSPxADD value of 0 is not supported when the Baud Rate Generator is used in SPI mode.

# REGISTER 17-4: SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

| U-0        | U-0                                                                   | U-0                                     | U-0                | U-0                    | U-0                  | U-0                  | U-0                  |

|------------|-----------------------------------------------------------------------|-----------------------------------------|--------------------|------------------------|----------------------|----------------------|----------------------|

| —          | _                                                                     | —                                       |                    | —                      | —                    | —                    | —                    |

| bit 15     |                                                                       |                                         |                    |                        |                      |                      | bit 8                |

|            |                                                                       |                                         |                    |                        |                      |                      |                      |

| R/W-0      | R/W-0                                                                 | R/W-0                                   | R/W-0              | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| WCOL       | SSPOV                                                                 | SSPEN <sup>(1)</sup>                    | CKP                | SSPM3 <sup>(2)</sup>   | SSPM2 <sup>(2)</sup> | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |

| bit 7      |                                                                       |                                         |                    |                        |                      |                      | bit 0                |

|            |                                                                       |                                         |                    |                        |                      |                      |                      |

| Legend:    |                                                                       |                                         |                    |                        |                      |                      |                      |

| R = Read   |                                                                       | W = Writable bi                         | t                  | -                      | ented bit, read      |                      |                      |

| -n = Value | e at POR                                                              | '1' = Bit is set                        |                    | '0' = Bit is clea      | ared                 | x = Bit is unkn      | own                  |

|            |                                                                       |                                         |                    |                        |                      |                      |                      |

| bit 15-8   | -                                                                     | ted: Read as '0'                        |                    |                        |                      |                      |                      |

| bit 7      |                                                                       | e Collision Detect                      | bit                |                        |                      |                      |                      |

|            | $\frac{\text{In Master Tra}}{1 = A \text{ write}}$                    | i <u>nsmit mode:</u><br>to the SSPxBUF  | register wa        | s attempted wh         | ile the $l^2$ C co   | nditions were r      | not valid for a      |

|            |                                                                       | sion to be started                      |                    |                        |                      |                      |                      |

|            | 0 = No collis                                                         | ion                                     |                    |                        |                      |                      |                      |

|            | In Slave Tran                                                         |                                         |                    |                        |                      | .,                   |                      |

|            | 1 = The SSP<br>0 = No collisi                                         | xBUF register is w<br>ion               | ritten while it is | s still transmitting   | the previous wo      | rd (must be clea     | red in software)     |

|            |                                                                       | ode (Master or SI                       | ave modes):        |                        |                      |                      |                      |

|            | This is a "don                                                        |                                         |                    |                        |                      |                      |                      |

| bit 6      | SSPOV: MSS                                                            | SPx Receive Over                        | flow Indicator     | bit                    |                      |                      |                      |

|            | In Receive m                                                          |                                         |                    |                        |                      |                      |                      |

|            | 1 = A byte is<br>0 = No overf                                         | received while the<br>low               | SSPxBUF reg        | ister is still holding | g the previous by    | /te (must be clea    | ired in software)    |

|            | In Transmit m                                                         |                                         |                    |                        |                      |                      |                      |

|            |                                                                       | n't care" bit in Trar                   | smit mode.         |                        |                      |                      |                      |

| bit 5      | SSPEN: MSS                                                            | SPx Enable bit <sup>(1)</sup>           |                    |                        |                      |                      |                      |

|            |                                                                       | the serial port and the serial port and |                    |                        |                      | serial port pins     |                      |

| bit 4      |                                                                       | Release Control bi                      | -                  | lese pills as i/O      | port pins            |                      |                      |

| DIL 4      | In Slave mod                                                          |                                         | ι                  |                        |                      |                      |                      |

|            | 1 = Releases                                                          |                                         |                    |                        |                      |                      |                      |

|            | 0 = Holds clo                                                         | ck low (clock strei                     | ch); used to e     | ensure data setu       | ıp time              |                      |                      |

|            | In Master mo                                                          |                                         |                    |                        |                      |                      |                      |

|            | Unused in thi                                                         |                                         | (2)                |                        |                      |                      |                      |

| bit 3-0    |                                                                       | MSSPx Mode Se                           |                    |                        |                      |                      |                      |

|            |                                                                       | lave mode, 10-bit<br>lave mode, 7-bit a |                    |                        |                      |                      |                      |

|            |                                                                       | irmware Controlle                       |                    |                        |                      | labica               |                      |

|            | 1000 = I <sup>2</sup> C N                                             | laster mode, Cloc                       | k = Fosc/(2 *      |                        | 1)) <sup>(3)</sup>   |                      |                      |

|            |                                                                       | lave mode, 10-bit<br>lave mode, 7-bit a |                    |                        |                      |                      |                      |

|            | $\mathbf{U} \mathbf{T} \mathbf{U} = \mathbf{L} \mathbf{C} \mathbf{S}$ | nave moue, 7-bit a                      | auuress            |                        |                      |                      |                      |

| Note 1:    |                                                                       | d, the SDAx and S                       | -                  | -                      | -                    |                      |                      |

| 2:         | Bit combination                                                       | ons not specifically                    | y listed here a    | are either reserv      | ed or implemen       | ted in SPI mode      | e only.              |

SSPxADD values of 0, 1 or 2 are not supported when the Baud Rate Generator is used with I<sup>2</sup>C mode.

## REGISTER 17-7: SSPxCON3: MSSPx CONTROL REGISTER 3 (I<sup>2</sup>C<sup>™</sup> MODE)

| bit 7 Au<br>bit 6 Pi<br>bit 6 Pi<br>bit 5 Si<br>bit 4 Bi<br>$\frac{ 2 }{1}$<br>bit 3 Si<br>bit 2 Si                                                                                                                                                                                                                        | R<br><b>CKTIM:</b> Ack<br>= Indicates<br>= Not an Acc<br><b>CIE:</b> Stop C<br>= Enables in<br>= Stop dete<br><b>CIE:</b> Start C<br>= Enables in<br>= Start dete<br><b>DEN:</b> Buffen<br><u>C Master m</u><br>nis bit is igno                 | cknowledge sec<br>ondition Interru<br>nterrupt on det<br>ction interrupts<br>condition Interru<br>nterrupt on det<br>ection interrupts<br>r Overwrite Ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | o'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup>                | '0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition<br>1)<br>tart or Restart o | set on the 8 <sup>th</sup><br>ing edge of the                             | x = Bit is unkr                                  |                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------|------------------------|

| R-0ACKTIM(2)bit 7Legend:R = Readable bit-n = Value at PObit 15-8Uibit 7Aubit 6PCbit 5SCbit 5SCbit 4Bi $\frac{12}{1}$ bit 3SIbit 3SIbit 2SI                                                                                                                                                                                 | PCIE<br>R<br>R<br>CKTIM: Ack<br>Indicates<br>Not an Ac<br>CIE: Stop C<br>Enables in<br>Stop dete<br>CIE: Start C<br>Enables in<br>Start dete<br>OEN: Buffer<br>CMaster m<br>is bit is igno                                                      | SCIE<br>W = Writable<br>'1' = Bit is set<br>ated: Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge sec<br>ondition Interru<br>nterrupt on det<br>ection interrupts<br>condition Interru<br>nterrupt on det<br>ection interrupts<br>r Overwrite Ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BOEN<br>bit<br>0'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup> | SDAHT<br>U = Unimpler<br>'0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition   | SBCDE<br>nented bit, read<br>ared<br>set on the 8 <sup>th</sup>           | AHEN<br>d as '0'<br>x = Bit is unki              | R/W-0<br>DHEN<br>bit ( |

| ACKTIM(2)bit 7Legend:<br>R = Readable bit<br>-n = Value at PObit 15-8Ui<br>bit 7bit 5Si<br>0bit 6Pi<br>0bit 5Si<br>0bit 4 $\frac{12}{1}$<br>0bit 3Si<br>0bit 3Si<br>0bit 2Si<br>                                                                                                                                           | PCIE<br>R<br>R<br>CKTIM: Ack<br>Indicates<br>Not an Ac<br>CIE: Stop C<br>Enables in<br>Stop dete<br>CIE: Start C<br>Enables in<br>Start dete<br>OEN: Buffer<br>CMaster m<br>is bit is igno                                                      | SCIE<br>W = Writable<br>'1' = Bit is set<br>ated: Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge sec<br>ondition Interru<br>nterrupt on det<br>ection interrupts<br>condition Interru<br>nterrupt on det<br>ection interrupts<br>r Overwrite Ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BOEN<br>bit<br>0'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup> | SDAHT<br>U = Unimpler<br>'0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition   | SBCDE<br>nented bit, read<br>ared<br>set on the 8 <sup>th</sup>           | AHEN<br>d as '0'<br>x = Bit is unki              | DHEN<br>bit (          |

| ACKTIM(2)bit 7Legend:<br>R = Readable bit<br>-n = Value at PObit 15-8Ui<br>bit 7bit 5Si<br>0bit 6Pi<br>0bit 5Si<br>0bit 4 $\frac{12}{1}$<br>0bit 3Si<br>0bit 3Si<br>0bit 2Si<br>                                                                                                                                           | PCIE<br>R<br>R<br>CKTIM: Ack<br>Indicates<br>Not an Ac<br>CIE: Stop C<br>Enables in<br>Stop dete<br>CIE: Start C<br>Enables in<br>Start dete<br>OEN: Buffer<br>CMaster m<br>is bit is igno                                                      | SCIE<br>W = Writable<br>'1' = Bit is set<br>ated: Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge sec<br>ondition Interru<br>nterrupt on det<br>ection interrupts<br>condition Interru<br>nterrupt on det<br>ection interrupts<br>r Overwrite Ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BOEN<br>bit<br>0'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup> | SDAHT<br>U = Unimpler<br>'0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition   | SBCDE<br>nented bit, read<br>ared<br>set on the 8 <sup>th</sup>           | AHEN<br>d as '0'<br>x = Bit is unki              | DHEN<br>bit (          |

| bit 7<br>Legend:<br>R = Readable bit<br>-n = Value at PO<br>bit 15-8 Ui<br>bit 7 A(<br>bit 6 P(<br>1<br>0<br>bit 5 S(<br>1<br>0<br>bit 5 S(<br>1<br>0<br>bit 4 B(<br>1<br>0<br>bit 3 S(<br>0<br>bit 3 S(<br>0<br>bit 2 S(<br>1<br>0<br>0<br>bit 2 S(<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | R<br><b>CKTIM:</b> Ack<br>Indicates<br>Not an Act<br>Indicates<br>Not an Act<br><b>CIE</b> : Stop C<br>Enables in<br>Stop dete<br><b>CIE</b> : Start C<br>Enables in<br>Start dete<br><b>DEN:</b> Buffer<br><u>C Master m</u><br>is bit is igno | W = Writable<br>'1' = Bit is set<br><b>ited:</b> Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge set<br>ondition Interru-<br>nterrupt on det-<br>ction interrupts<br>condition Interru-<br>nterrupt on det-<br>ction interrupts<br>r Overwrite Ena-<br>tode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1</sup>                 | U = Unimpler<br>'0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition            | nented bit, read<br>ared<br>set on the 8 <sup>th</sup><br>ing edge of the | d as '0'<br>x = Bit is unkr<br>falling edge of f | nown                   |

| Legend:<br>R = Readable bit<br>rn = Value at PO<br>bit 15-8 Ui<br>bit 7 AC<br>bit 6 PC<br>bit 5 SC<br>bit 4 BC<br>$\frac{ 2 }{1}$<br>bit 3 SC<br>bit 2 SC<br>1 1<br>0 1<br>0 1<br>0 1<br>0 1<br>0 1<br>0 1<br>0 1                                                                                                          | R<br><b>CKTIM:</b> Ack<br>= Indicates<br>= Not an Acc<br><b>CIE:</b> Stop C<br>= Enables in<br>= Stop dete<br><b>CIE:</b> Start C<br>= Enables in<br>= Start dete<br><b>DEN:</b> Buffen<br><u>C Master m</u><br>nis bit is igno                 | '1' = Bit is set<br><b>ited:</b> Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge sec<br>ondition Interru-<br>nterrupt on det-<br>ection interrupts<br>condition Interru-<br>nterrupt on det-<br>ection interrupts<br>r Overwrite Ena-<br>tode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | o'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup>                | '0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition<br>1)<br>tart or Restart o | ared<br>set on the 8 <sup>th</sup><br>ing edge of the                     | x = Bit is unkr                                  | nown                   |

| R = Readable bit<br>-n = Value at PO<br>bit 15-8 Ui<br>bit 7 Ac<br>bit 6 PC<br>bit 5 SC<br>bit 4 BC<br>$\frac{ 2 }{1}$<br>bit 3 SC<br>bit 2 SC<br>1                                                                                                                                                                        | R<br><b>CKTIM:</b> Ack<br>= Indicates<br>= Not an Acc<br><b>CIE:</b> Stop C<br>= Enables in<br>= Stop dete<br><b>CIE:</b> Start C<br>= Enables in<br>= Start dete<br><b>DEN:</b> Buffen<br><u>C Master m</u><br>nis bit is igno                 | '1' = Bit is set<br><b>ited:</b> Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge sec<br>ondition Interru-<br>nterrupt on det-<br>ection interrupts<br>condition Interru-<br>nterrupt on det-<br>ection interrupts<br>r Overwrite Ena-<br>tode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | o'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup>                | '0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition<br>1)<br>tart or Restart o | ared<br>set on the 8 <sup>th</sup><br>ing edge of the                     | x = Bit is unkr                                  |                        |

| R = Readable bit<br>-n = Value at PO<br>bit 15-8 Ui<br>bit 7 Ac<br>bit 6 PC<br>bit 5 SC<br>bit 4 BC<br>$\frac{ 2 }{1}$<br>bit 3 SC<br>bit 2 SC<br>1                                                                                                                                                                        | R<br><b>CKTIM:</b> Ack<br>= Indicates<br>= Not an Acc<br><b>CIE:</b> Stop C<br>= Enables in<br>= Stop dete<br><b>CIE:</b> Start C<br>= Enables in<br>= Start dete<br><b>DEN:</b> Buffen<br><u>C Master m</u><br>nis bit is igno                 | '1' = Bit is set<br><b>ited:</b> Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge sec<br>ondition Interru-<br>nterrupt on det-<br>ection interrupts<br>condition Interru-<br>nterrupt on det-<br>ection interrupts<br>r Overwrite Ena-<br>tode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | o'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup>                | '0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition<br>1)<br>tart or Restart o | ared<br>set on the 8 <sup>th</sup><br>ing edge of the                     | x = Bit is unkr                                  |                        |

| bit 15-8 Ui<br>bit 15-8 Ui<br>bit 7 A<br>bit 7 A<br>bit 6 P<br>bit 5 S<br>bit 5 S<br>bit 4 B<br>$\frac{ 2 }{1}$<br>bit 3 SI<br>bit 2 SI<br>bit 2 SI                                                                                                                                                                        | R<br><b>CKTIM:</b> Ack<br>= Indicates<br>= Not an Acc<br><b>CIE:</b> Stop C<br>= Enables in<br>= Stop dete<br><b>CIE:</b> Start C<br>= Enables in<br>= Start dete<br><b>DEN:</b> Buffen<br><u>C Master m</u><br>nis bit is igno                 | '1' = Bit is set<br><b>ited:</b> Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge sec<br>ondition Interru-<br>nterrupt on det-<br>ection interrupts<br>condition Interru-<br>nterrupt on det-<br>ection interrupts<br>r Overwrite Ena-<br>tode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | o'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup>                | '0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition<br>1)<br>tart or Restart o | ared<br>set on the 8 <sup>th</sup><br>ing edge of the                     | x = Bit is unkr                                  |                        |

| bit 15-8 Ui<br>bit 7 A<br>bit 7 A<br>bit 6 P<br>bit 6 P<br>bit 5 S<br>bit 4 B<br>bit 4 B<br>$ ^2($<br>1<br>bit 3 SI<br>0<br>bit 2 SI<br>1                                                                                                                                                                                  | nimplemen<br>CKTIM: Ack<br>= Indicates<br>= Not an Ac<br>CIE: Stop C<br>= Enables in<br>= Stop dete<br>CIE: Start C<br>= Enables in<br>= Start dete<br>OEN: Buffer<br><u>C Master m</u><br>nis bit is igno                                      | <b>Ated:</b> Read as the knowledge Time<br>the I <sup>2</sup> C bus is in the chowledge set to the chowledge set | 0'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>pt Enable bit<br>ection of a Sto<br>are disabled <sup>(1</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1</sup>                   | edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition<br>l)<br>tart or Restart o                     | set on the 8 <sup>th</sup><br>ing edge of the                             | falling edge of f                                |                        |