Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

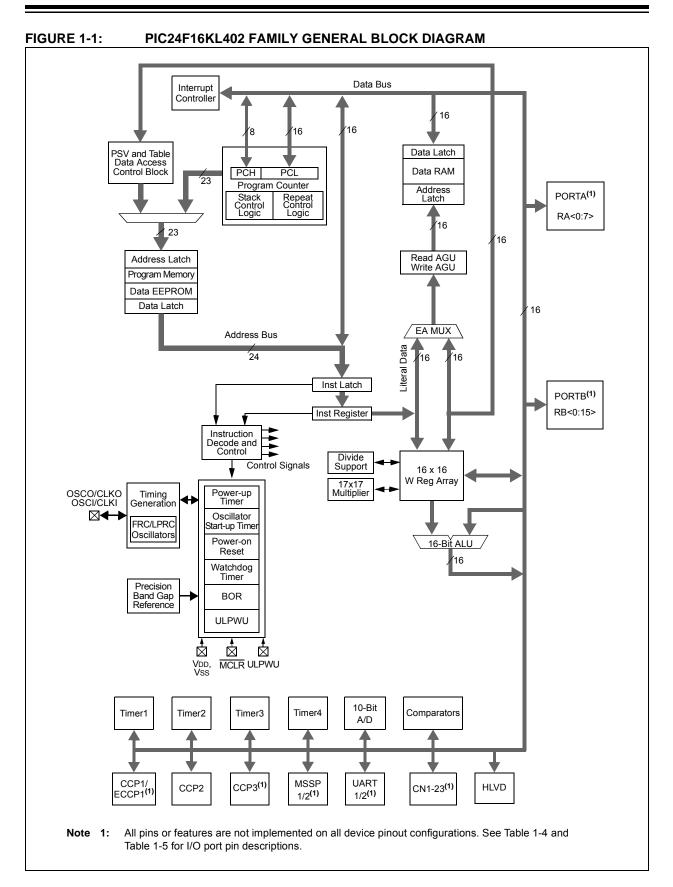

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| 2 0 0 0 0 0 0              |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

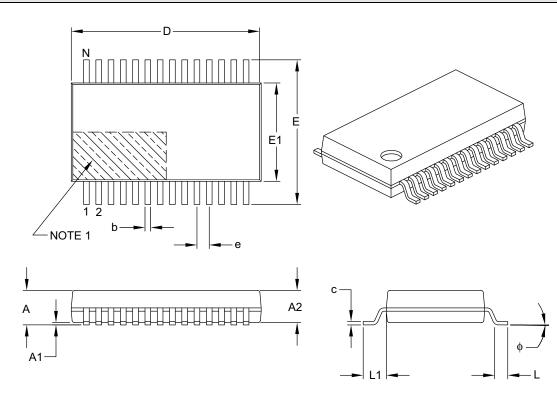

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl402-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

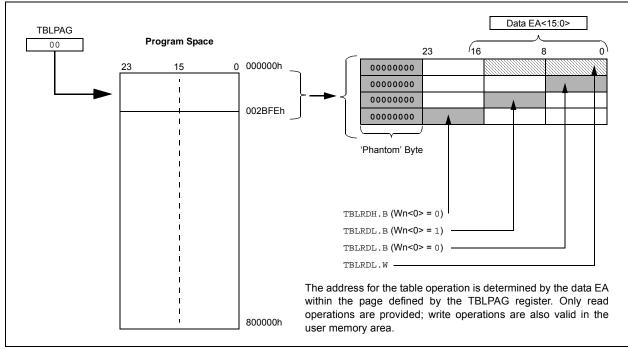

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through data space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

| Note: | The TBLRDH and TBLWTH instructions are |

|-------|----------------------------------------|

|       | not used while accessing data EEPROM   |

|       | memory.                                |

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when the byte select is '1'; the lower byte is selected when it is '0'.

TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

int __attribute__ ((space(auto_psv))) progAddr = &progAddr; // Global variable located in Pgm Memory

unsigned int offset;

unsigned int i;

// Buffer of data to write

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW];

//Set up NVMCON for row programming

NVMCON = 0 \times 4004;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

offset = &progAddr & 0xFFFF;

// Initialize lower word of address

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]);

// Write to address low word

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2i

// Increment address

}

```

### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; | Block all interrupts                  |

|------|-------------|---|---------------------------------------|

|      |             |   | for next 5 instructions               |

| MOV  | #0x55, W0   |   |                                       |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                      |

| MOV  | #0xAA, W1   | ; |                                       |

| MOV  | W1, NVMKEY  | ; | Write the AA key                      |

| BSET | NVMCON, #WR | ; | Start the erase sequence              |

| NOP  |             | ; | 2 NOPs required after setting WR      |

| NOP  |             | ; |                                       |

| BTSC | NVMCON, #15 | ; | Wait for the sequence to be completed |

| BRA  | \$-2        | ; |                                       |

|      |             |   |                                       |

#### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB C30 |                                                 |

|------------------------------|-------------------------------------------------|

| asm("DISI #5");              | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();         | // Perform unlock sequence and set WR           |

#### 6.4.1.1 Data EEPROM Bulk Erase

To erase the entire data EEPROM (bulk erase), the address registers do not need to be configured because this operation affects the entire data EEPROM. The following sequence helps in performing a bulk erase:

- 1. Configure NVMCON to Bulk Erase mode.

- 2. Clear the NVMIF status bit and enable the NVM interrupt (optional).

- 3. Write the key sequence to NVMKEY.

- 4. Set the WR bit to begin the erase cycle.

- 5. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical bulk erase sequence is provided in Example 6-3.

#### 6.4.2 SINGLE-WORD WRITE

To write a single word in the data EEPROM, the following sequence must be followed:

- Erase one data EEPROM word (as mentioned in Section 6.4.1 "Erase Data EEPROM") if PGMONLY bit (NVMCON<12>) is set to '1'.

- 2. Write the data word into the data EEPROM latch.

- 3. Program the data word into the EEPROM:

- Configure the NVMCON register to program one EEPROM word (NVMCON<5:0> = 0001xx).

- Clear the NVMIF status bit and enable the NVM interrupt (optional).

- Write the key sequence to NVMKEY.

- Set the WR bit to begin the erase cycle.

- Either poll the WR bit or wait for the NVM interrupt (NVMIF set).

- To get cleared, wait until NVMIF is set.

A typical single-word write sequence is provided in Example 6-4.

### EXAMPLE 6-3: DATA EEPROM BULK ERASE

// Set up NVMCON to bulk erase the data EEPROM

NVMCON = 0x4050;

// Disable Interrupts For 5 Instructions

asm volatile ("disi #5");

// Issue Unlock Sequence and Start Erase Cycle

\_\_builtin\_write\_NVM();

### EXAMPLE 6-4: SINGLE-WORD WRITE TO DATA EEPROM

| <pre>intattribute ((space(eedata))) eeData = 0x1234;<br/>int newData;<br/>unsigned int offset;</pre>                                                                        | // Global variable located in EEPROM<br>// New data to write to EEPROM                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>// Set up NVMCON to erase one word of data EEPROM NVMCON = 0x4004;</pre>                                                                                               |                                                                                                                                                                         |

| <pre>// Set up a pointer to the EEPROM location to be e TBLPAG =builtin_tblpage(&amp;eeData); offset =builtin_tbloffset(&amp;eeData);builtin_tblwtl(offset, newData);</pre> | erased<br>// Initialize EE Data page pointer<br>// Initizlize lower word of address<br>// Write EEPROM data to write latch                                              |

| <pre>asm volatile ("disi #5");<br/>builtin_write_NVM();<br/>while(NVMCONbits.WR=1);</pre>                                                                                   | <pre>// Disable Interrupts For 5 Instructions // Issue Unlock Sequence &amp; Start Write Cycle // Optional: Poll WR bit to wait for // write sequence to complete</pre> |

### REGISTER 8-1: SR: ALU STATUS REGISTER

| U-0                   | U-0                                                                    | U-0                   | U-0               | U-0                      | U-0               | U-0                | R/W-0             |  |  |  |  |

|-----------------------|------------------------------------------------------------------------|-----------------------|-------------------|--------------------------|-------------------|--------------------|-------------------|--|--|--|--|

| —                     |                                                                        | _                     | —                 | —                        | —                 |                    | DC <sup>(1)</sup> |  |  |  |  |

| bit 15                |                                                                        |                       |                   |                          |                   |                    | bit 8             |  |  |  |  |

|                       |                                                                        |                       |                   |                          |                   |                    |                   |  |  |  |  |

| R/W-0                 | R/W-0                                                                  | R/W-0                 | R-0               | R/W-0                    | R/W-0             | R/W-0              | R/W-0             |  |  |  |  |

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup>                                                  | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup>         | OV <sup>(1)</sup> | Z <sup>(1)</sup>   | C <sup>(1)</sup>  |  |  |  |  |

| bit 7                 |                                                                        |                       |                   | •                        |                   |                    | bit 0             |  |  |  |  |

|                       |                                                                        |                       |                   |                          |                   |                    |                   |  |  |  |  |

| Legend:               |                                                                        |                       |                   |                          |                   |                    |                   |  |  |  |  |

| R = Readab            | le bit                                                                 | W = Writable          | bit               | U = Unimplem             | nented bit, read  | d as '0'           |                   |  |  |  |  |

| -n = Value a          | t POR                                                                  | '1' = Bit is set      |                   | '0' = Bit is cleared     |                   | x = Bit is unknown |                   |  |  |  |  |

|                       |                                                                        |                       |                   |                          |                   |                    |                   |  |  |  |  |

| bit 15-9              | Unimplemen                                                             | ted: Read as 'o       | )'                |                          |                   |                    |                   |  |  |  |  |

| bit 7-5               | IPL<2:0>: CF                                                           | PU Interrupt Price    | ority Level Stat  | us bits <sup>(2,3)</sup> |                   |                    |                   |  |  |  |  |

|                       | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts disabled |                       |                   |                          |                   |                    |                   |  |  |  |  |

|                       |                                                                        | nterrupt Priority     | • • •             |                          |                   |                    |                   |  |  |  |  |

|                       |                                                                        | nterrupt Priority     | ( )               |                          |                   |                    |                   |  |  |  |  |

|                       | 100 = CPU Interrupt Priority Level is 4 (12)                           |                       |                   |                          |                   |                    |                   |  |  |  |  |

|                       | 011 = CPU Interrupt Priority Level is 3 (11)                           |                       |                   |                          |                   |                    |                   |  |  |  |  |

|                       |                                                                        | nterrupt Priority     |                   |                          |                   |                    |                   |  |  |  |  |

|                       |                                                                        | nterrupt Priority     | • • •             |                          |                   |                    |                   |  |  |  |  |

|                       | 0.00 = CPU Interrupt Priority Level is 0 (8)                           |                       |                   |                          |                   |                    |                   |  |  |  |  |

- 000 = CPU Interrupt Priority Level is 0 (8)

- **Note 1:** See Register 3-1 for the description of these bits, which are not dedicated to interrupt control functions.

- **2:** The IPL bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

- 3: The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

Note: Bit 8 and bits 4 through 0 are described in Section 3.0 "CPU".

|                       | R/W-0                                                                              | R/W-0                            | U-0              | R/W-0                     | U-0             | R/W-0                 | U-0    |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------|----------------------------------|------------------|---------------------------|-----------------|-----------------------|--------|--|--|--|--|

| U2TXIF <sup>(1)</sup> | U2RXIF <sup>(1)</sup>                                                              | INT2IF                           |                  | T4IF <sup>(1)</sup>       |                 | CCP3IF <sup>(1)</sup> | _      |  |  |  |  |

| bit 15                |                                                                                    |                                  |                  |                           |                 |                       | bit 8  |  |  |  |  |

|                       |                                                                                    |                                  |                  |                           |                 |                       |        |  |  |  |  |

| U-0                   | U-0                                                                                | U-0                              | R/W-0            | R/W-0                     | R/W-0           | R/W-0                 | R/W-0  |  |  |  |  |

| —                     | —                                                                                  | —                                | INT1IF           | CNIF                      | CMIF            | BCL1IF                | SSP1IF |  |  |  |  |

| bit 7                 |                                                                                    |                                  |                  |                           |                 |                       | bit (  |  |  |  |  |

|                       |                                                                                    |                                  |                  |                           |                 |                       |        |  |  |  |  |

| Legend:               |                                                                                    |                                  |                  |                           |                 |                       |        |  |  |  |  |

| R = Readable          |                                                                                    | W = Writable                     |                  | •                         | nented bit, rea |                       |        |  |  |  |  |

| -n = Value at F       | POR                                                                                | '1' = Bit is set                 |                  | '0' = Bit is clea         | ared            | x = Bit is unkno      | own    |  |  |  |  |

|                       |                                                                                    |                                  |                  | - (1)                     |                 |                       |        |  |  |  |  |

| bit 15                |                                                                                    | T2 Transmitter                   |                  | Status bit <sup>(1)</sup> |                 |                       |        |  |  |  |  |

|                       |                                                                                    | equest has occ                   |                  |                           |                 |                       |        |  |  |  |  |

| L:1 4 4               |                                                                                    | equest has not                   |                  |                           |                 |                       |        |  |  |  |  |

| bit 14                |                                                                                    | RT2 Receiver Ir                  |                  | atus bit                  |                 |                       |        |  |  |  |  |

|                       |                                                                                    | equest has occ                   |                  |                           |                 |                       |        |  |  |  |  |

| bit 13                | 0 = Interrupt request has not occurred                                             |                                  |                  |                           |                 |                       |        |  |  |  |  |

| bit 10                | INT2IF: External Interrupt 2 Flag Status bit<br>1 = Interrupt request has occurred |                                  |                  |                           |                 |                       |        |  |  |  |  |

|                       | 0 = Interrupt request has not occurred                                             |                                  |                  |                           |                 |                       |        |  |  |  |  |

| bit 12                | -                                                                                  | ted: Read as '                   |                  |                           |                 |                       |        |  |  |  |  |

| bit 11                | <b>T4IF:</b> Timer4 Interrupt Flag Status bit <sup>(1)</sup>                       |                                  |                  |                           |                 |                       |        |  |  |  |  |

|                       | 1 = Interrupt request has occurred                                                 |                                  |                  |                           |                 |                       |        |  |  |  |  |

|                       | 0 = Interrupt r                                                                    | equest has not                   | occurred         |                           |                 |                       |        |  |  |  |  |

| bit 10                | Unimplement                                                                        | ted: Read as '                   | כי               |                           |                 |                       |        |  |  |  |  |

| bit 9                 | CCP3IF: Capture/Compare/PWM3 Interrupt Flag Status bit <sup>(1)</sup>              |                                  |                  |                           |                 |                       |        |  |  |  |  |

|                       | 1 = Interrupt request has occurred                                                 |                                  |                  |                           |                 |                       |        |  |  |  |  |

|                       | -                                                                                  | equest has not                   |                  |                           |                 |                       |        |  |  |  |  |

| bit 8-5               | -                                                                                  | ted: Read as '                   |                  |                           |                 |                       |        |  |  |  |  |

| bit 4                 | INT1IF: External Interrupt 1 Flag Status bit                                       |                                  |                  |                           |                 |                       |        |  |  |  |  |

|                       |                                                                                    | equest has occ<br>equest has not |                  |                           |                 |                       |        |  |  |  |  |

| bit 3                 | •                                                                                  | hange Notifica                   |                  | lag Status bit            |                 |                       |        |  |  |  |  |

| DIT 3                 | -                                                                                  | -                                | -                | lay Status bit            |                 |                       |        |  |  |  |  |

|                       | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred       |                                  |                  |                           |                 |                       |        |  |  |  |  |

| bit 2                 | CMIF: Comparator Interrupt Flag Status bit                                         |                                  |                  |                           |                 |                       |        |  |  |  |  |

|                       | 1 = Interrupt request has occurred                                                 |                                  |                  |                           |                 |                       |        |  |  |  |  |

|                       |                                                                                    | equest has not                   |                  |                           |                 |                       |        |  |  |  |  |

| bit 1                 | BCL1IF: MSS                                                                        | SP1 I <sup>2</sup> C™ Bus        | Collision Interr | upt Flag Status           | bit             |                       |        |  |  |  |  |

|                       | 1 = Interrupt r                                                                    | equest has occ                   | curred           |                           |                 |                       |        |  |  |  |  |

|                       | -                                                                                  | equest has not                   |                  |                           |                 |                       |        |  |  |  |  |

| bit 0                 |                                                                                    | SP1 SPI/I <sup>2</sup> C Ev      |                  | ag Status bit             |                 |                       |        |  |  |  |  |

|                       |                                                                                    | equest has occ<br>equest has not |                  |                           |                 |                       |        |  |  |  |  |

|                       |                                                                                    |                                  | aggirrad         |                           |                 |                       |        |  |  |  |  |

### REGISTER 8-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

### REGISTER 9-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REGISTER      | 9-4: REFU                                                                                                                                                                                                                     | CON: REFER                                                                                                                                                                                                                                                                                                                   | KENCE USC                                                                                                                                                                              | ILLATOR CC        | INTROL REC       | 515TER          |               |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|---------------|--|--|--|--|

| bit 15       bit 5         U-0       U-0       U-0       U-0       U-0       U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0         | U-0                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                  | R/W-0             | R/W-0            | R/W-0           | R/W-0         |  |  |  |  |

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ROEN          | —                                                                                                                                                                                                                             | ROSSLP                                                                                                                                                                                                                                                                                                                       | ROSEL                                                                                                                                                                                  | RODIV3            | RODIV2           | RODIV1          | RODIV0        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 15        |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 | bit 8         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 |               |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       0       = Reference oscillator output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference oscillator is disabled in Sleep       0 = Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         111 = Base clock value divid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0           | 0-0                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                    | 0-0               | 0-0              | 0-0             | U-0           |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       1 = Reference oscillator continues to run in Sleep       0 = Reference oscillator continues to run in Sleep         0 = Reference oscillator is disabled in Sleep       0 = Reference oscillator is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         111 = Base clock value divided by 32,768       1100 = Base clock value divided by 4,966         1101 = Base clock value divided by 4,096       1011 = Base clock value divided by 1,024         1000 = Base clock value divided by 1,024       1001 = Base clock value divided by 128         0111 = Base clock value di                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                                                                                                                                                                                                                               | _                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                        | _                 | _                | _               |               |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       0'       Bit 13       ROSSLP: Reference Oscillator Output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference Oscillator Source Select bit       1 = Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock (*1)       0 = System clock is used as the base clock reflects any clock switching of the device         bit 11-8       RODIV-3:0-: Reference Oscillator Divisor Select bits       1111 = Base clock value divided by 32,768         1110 = Base clock value divided by 10:       100 = Base clock value divided by 10:       100 = Base clock value divided by 2,048         1011 = Base clock value divided by 20:       100 = Base clock value divided by 256       111 = Base clock value divided by 22:         1010 = Base clock value divided by 10:       101 = Base clock value divided by 10:       101 = Base clock value divided by 12:         1000 = Base clock value divided by 10:       111 = Base clock value divided by 22:       100 = Base clock value divided by 22:         1000 = Base clock value divided by 10:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 | DILU          |  |  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       1       ROSSLP: Reference Oscillator Output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference Oscillator Source Select bit       1 = Reference oscillator is used as the base clock '1)         0 = System clock is used as the base clock '10       0 = System clock value divided by 32,768       1111 = Base clock value divided by 4,096         1111 = Base clock value divided by 10,384       100 = Base clock value divided by 1,024       100 = Base clock value divided by 1,024         100 = Base clock value divided by 128       010 = Base clock value divided by 128       010 = Base clock value divided by 128         010 = Base clock value divided by 16       011 = Base clock value divided by 128       010 = Base clock value divided by 128         010 = Base clock value divided by 16       011 = Base clock value divided by 16       011 = Base clock value divided by 128         010 = Base clock value divided by 16       011 = Base clock value divided by 16       011 = Base clock value divided by 18         010 = Base clock value divided by 16       011 = Base clock value divided by 18       010 = Base clock value divided by 18         010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Legend:       |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 |               |  |  |  |  |

| bit 15 <b>ROEN:</b> Reference Oscillator Output Enable bit<br>1 = Reference oscillator is enabled on REFO pin<br>0 = Reference oscillator is disabled<br>bit 14 <b>Unimplemented:</b> Read as '0'<br>bit 13 <b>ROSSLP:</b> Reference Oscillator Output Stop in Sleep bit<br>1 = Reference oscillator continues to run in Sleep<br>0 = Reference oscillator is disabled in Sleep<br>bit 12 <b>ROSEL:</b> Reference Oscillator Source Select bit<br>1 = Primary oscillator is used as the base clock <sup>(1)</sup><br>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br>bit 11-8 <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 22,768<br>1110 = Base clock value divided by 4,192<br>1100 = Base clock value divided by 4,192<br>1100 = Base clock value divided by 1,192<br>1100 = Base clock value divided by 1,024<br>1011 = Base clock value divided by 1,28<br>0110 = Base clock valu | R = Readabl   | le bit                                                                                                                                                                                                                        | W = Writable I                                                                                                                                                                                                                                                                                                               | oit                                                                                                                                                                                    | U = Unimplen      | nented bit, read | d as '0'        |               |  |  |  |  |

| <ul> <li>1 = Reference oscillator is enabled on REFO pin<br/>0 = Reference oscillator is disabled</li> <li>bit 14 Unimplemented: Read as '0'</li> <li>bit 13 ROSSLP: Reference Oscillator Output Stop in Sleep bit<br/>1 = Reference oscillator is disabled in Sleep<br/>0 = Reference oscillator is disabled in Sleep</li> <li>bit 12 ROSEL: Reference Oscillator Source Select bit<br/>1 = Primary oscillator is used as the base clock<sup>(1)</sup><br/>0 = System clock is used as the base clock (1)<br/>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br/>bit 11-8 RODIV-3:0&gt;: Reference Oscillator Divisor Select bits</li> <li>111 = Base clock value divided by 32,768</li> <li>1110 = Base clock value divided by 8,192</li> <li>1100 = Base clock value divided by 4,096</li> <li>1011 = Base clock value divided by 1,024</li> <li>1001 = Base clock value divided by 512</li> <li>1000 = Base clock value divided by 256</li> <li>0111 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 20</li> <li>010 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 20</li> <li>010 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 20</li> <li>010 = Base clock value divided by 2</li> <li>011 = Base clock value divided by 2</li> <li>011 = Base clock</li></ul>                                                                                  | -n = Value at | t POR                                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                        | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |  |  |  |  |

| 1 = Reference oscillator continues to run in Sleep         0 = Reference oscillator is disabled in Sleep         bit 12 <b>ROSEL:</b> Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock; the base clock reflects any clock switching of the device         bit 11-8 <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits         111 = Base clock value divided by 32,768         110 = Base clock value divided by 16,384         100 = Base clock value divided by 4,096         1011 = Base clock value divided by 1,024         1001 = Base clock value divided by 1,024         1001 = Base clock value divided by 128         110 = Base clock value divided by 128         111 = Base clock value divided by 32         100 = Base clock value divided by 32         100 = Base clock value divided by 4,096         111 = Base clock value divided by 2,048         1010 = Base clock value divided by 1,024         1001 = Base clock value divided by 128         111 = Base clock value divided by 32         110 = Base clock value divided by 32         110 = Base clock value divided by 4         111 = Base clock value divided                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               | 1 = Reference<br>0 = Reference                                                                                                                                                                                                | e oscillator is er<br>e oscillator is di                                                                                                                                                                                                                                                                                     | nabled on REF<br>sabled                                                                                                                                                                |                   |                  |                 |               |  |  |  |  |

| 1 = Reference oscillator continues to run in Sleep         0 = Reference oscillator is disabled in Sleep         bit 12 <b>ROSEL:</b> Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock; the base clock reflects any clock switching of the device         bit 11-8 <b>RODIV-3:0&gt;:</b> Reference Oscillator Divisor Select bits         1111 = Base clock value divided by 32,768         1100 = Base clock value divided by 16,384         1101 = Base clock value divided by 4,096         1011 = Base clock value divided by 1,024         1001 = Base clock value divided by 1,024         1001 = Base clock value divided by 1,024         1001 = Base clock value divided by 128         0110 = Base clock value divided by 128         0110 = Base clock value divided by 32         0101 = Base clock value divided by 32         0100 = Base clock value divided by 32         0101 = Base clock value divided by 40         0111 = Base clock value divided by 16         0111 = Base clock v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 13        | -                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        | o in Sleep bit    |                  |                 |               |  |  |  |  |

| bit 12 ROSEL: Reference Oscillator Source Select bit<br>1 = Primary oscillator is used as the base clock <sup>(1)</sup><br>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br>bit 11-8 RODIV<3:0>: Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 32,768<br>1110 = Base clock value divided by 4,096<br>1011 = Base clock value divided by 4,096<br>1011 = Base clock value divided by 2,048<br>1010 = Base clock value divided by 1,024<br>1001 = Base clock value divided by 512<br>1000 = Base clock value divided by 256<br>0111 = Base clock value divided by 128<br>0110 = Base clock value divided by 32<br>1000 = Base clock value divided by 44<br>011 = Base clock value divided by 32<br>0100 = Base clock value divided by 4<br>011 = Base clock value divided by 4<br>010 = Base clock value divided by 266<br>0111 = Base clock value divided by 4<br>0101 = Base clock value divided by 4<br>0101 = Base clock value divided by 4<br>0101 = Base clock value divided by 32<br>0100 = Base clock value divided by 4<br>001 = Base clock value divided by 2<br>000 = Base clock value divided by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 |               |  |  |  |  |

| 1 = Primary oscillator is used as the base clock <sup>(1)</sup><br>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br>bit 11-8 <b>RODIV-3:0&gt;:</b> Reference Oscillator Divisor Select bits 1111 = Base clock value divided by 32,768 1100 = Base clock value divided by 4,096 1011 = Base clock value divided by 4,096 1011 = Base clock value divided by 1,024 1000 = Base clock value divided by 512 1000 = Base clock value divided by 128 0110 = Base clock value divided by 256 0111 = Base clock value divided by 4 000 = Base clock value divided by 4 010 = Base cloc                                                                                                                                                                                                                                                                                                                                                                                                                            |               | 0 = Reference                                                                                                                                                                                                                 | e oscillator is di                                                                                                                                                                                                                                                                                                           | sabled in Slee                                                                                                                                                                         | p                 |                  |                 |               |  |  |  |  |

| 0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br>bit 11-8 RODIV<3:0>: Reference Oscillator Divisor Select bits 1111 = Base clock value divided by 32,768 1100 = Base clock value divided by 16,384 1101 = Base clock value divided by 4,096 1011 = Base clock value divided by 2,048 1010 = Base clock value divided by 1,024 1001 = Base clock value divided by 512 1000 = Base clock value divided by 256 0111 = Base clock value divided by 44 0101 = Base clock value divided by 42 0101 = Base clock value divided by 42 0101 = Base clock value divided by 42 0101 = Base clock value divided by 4 0                                                                                                                                  | bit 12        |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 |               |  |  |  |  |

| bit 11-8 <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 32,768<br>1110 = Base clock value divided by 16,384<br>1101 = Base clock value divided by 8,192<br>1100 = Base clock value divided by 2,048<br>1010 = Base clock value divided by 1,024<br>1001 = Base clock value divided by 512<br>1000 = Base clock value divided by 256<br>0111 = Base clock value divided by 128<br>0110 = Base clock value divided by 32<br>0101 = Base clock value divided by 32<br>0101 = Base clock value divided by 4<br>001 = Base clock value divided by 2<br>0000 = Base clock value divided by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   | ck reflects anv  | clock switching | of the device |  |  |  |  |