Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

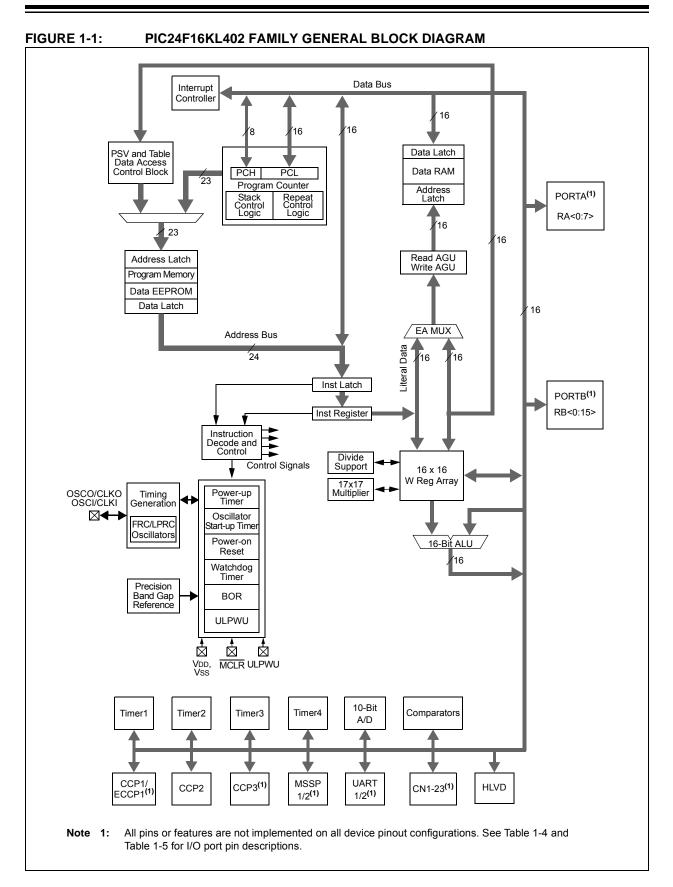

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

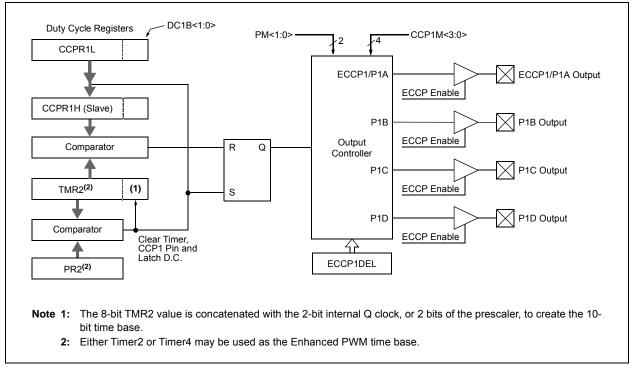

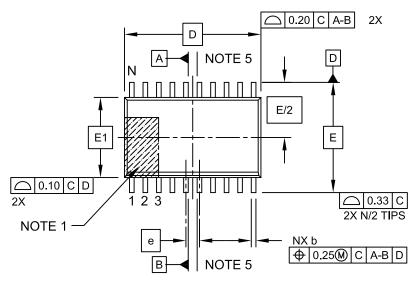

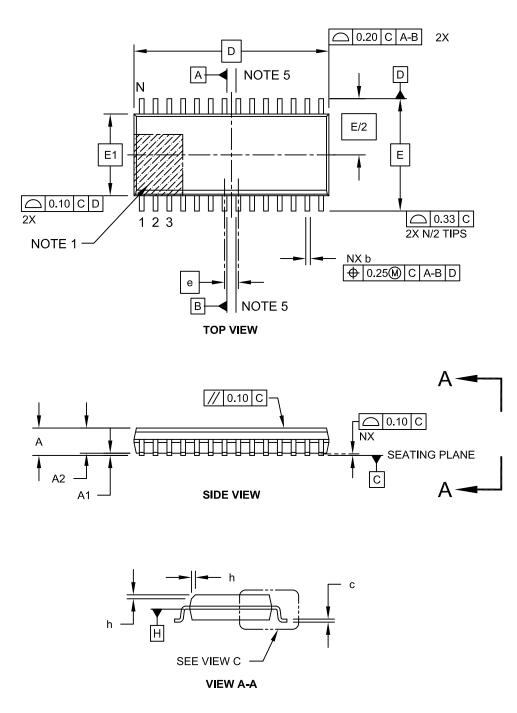

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VFQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (5x5)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl402-i-mq |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-6               | : т  | IMER   | REGIS  | TER N  | IAP    |        |        |        |        |                        |                        |          |          |                  |        |         |         |               |  |

|-------------------------|------|--------|--------|--------|--------|--------|--------|--------|--------|------------------------|------------------------|----------|----------|------------------|--------|---------|---------|---------------|--|

| File Name               | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7                  | Bit 6                  | Bit 5    | Bit 4    | Bit 3            | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |  |

| TMR1                    | 0100 |        |        |        |        |        |        |        |        | Timer1 Reg             | gister                 |          |          |                  |        |         |         | 0000          |  |

| PR1                     | 0102 |        |        |        |        |        |        |        | Tir    | mer1 Period            | Register               |          |          |                  |        |         |         | FFFF          |  |

| T1CON                   | 0104 | TON    | _      | TSIDL  | _      | _      | _      | T1ECS1 | T1ECS0 | _                      | TGATE                  | TCKPS1   | TCKPS0   | —                | TSYNC  | TCS     | _       | 0000          |  |

| TMR2                    | 0106 | _      | _      | _      | _      | _      | _      | _      | _      |                        |                        |          | Timer2 R | egister          |        |         |         | 0000          |  |

| PR2                     | 0108 | _      | _      | _      | _      | _      | _      | _      | _      | Timer2 Period Register |                        |          |          |                  |        |         |         |               |  |

| T2CON                   | 010A | _      | _      | _      | _      | _      | _      | _      | _      | _                      | T2OUTPS3               | T2OUTPS2 | T2OUTPS1 | T2OUTPS0         | TMR2ON | T2CKPS1 | T2CKPS0 | 0000          |  |

| TMR3                    | 010C |        |        |        |        |        |        |        |        | Timer3 Reg             | gister                 |          |          |                  |        |         |         | 0000          |  |

| T3GCON                  | 010E | -      | —      | —      | —      | —      | —      | —      | —      | TMR3GE                 | T3GPOL                 | T3GTM    | T3GSPM   | T3GGO/<br>T3DONE | T3GVAL | T3GSS1  | T3GSS0  | 0000          |  |

| T3CON                   | 0110 | _      | _      | _      | _      | _      | _      | _      | _      | TMR3CS1                | TMR3CS0                | T3CKPS1  | T3CKPS0  | T3OSCEN          | T3SYNC | _       | TMR3ON  | 0000          |  |

| TMR4 <sup>(1)</sup>     | 0112 | _      | _      | _      | _      | _      | —      | _      | _      |                        | •                      | •        | Timer4 R | egister          |        |         |         | 0000          |  |

| PR4 <sup>(1)</sup>      | 0114 | _      | _      | _      | _      | _      | —      | —      | —      | Timer4 Period Register |                        |          |          |                  |        |         |         |               |  |

| T4CON <sup>(1)</sup>    | 0116 | _      | _      | _      | _      | _      | —      | —      | —      | _                      | T4OUTPS3               | T4OUTPS2 | T4OUTPS1 | T4OUTPS0         | TMR40N | T4CKPS1 | T4CKPS0 | 0000          |  |

| CCPTMRS0 <sup>(1)</sup> | 013C | -      | _      | _      | _      | —      | _      | —      | _      | —                      | C3TSEL0 <sup>(1)</sup> | _        | -        | C2TSEL0          | -      | _       | C1TSEL0 | 0000          |  |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

#### TABLE 4-7: CCP/ECCP REGISTER MAP

|                         |      |        | -      |        |        |        |        |       |       | 1                                       |                    |            |            | 1            |           |        |        |               |

|-------------------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-----------------------------------------|--------------------|------------|------------|--------------|-----------|--------|--------|---------------|

| File Name               | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                   | Bit 6              | Bit 5      | Bit 4      | Bit 3        | Bit 2     | Bit 1  | Bit 0  | All<br>Resets |

| CCP1CON                 | 0190 | _      | _      | —      | _      | _      | —      | —     | —     | PM1 <sup>(1)</sup>                      | PM0 <sup>(1)</sup> | DC1B1      | DC1B0      | CCP1M3       | CCP1M2    | CCP1M1 | CCP1M0 | 0000          |

| CCPR1L                  | 0192 | -      | _      | _      | _      | _      | _      | _     | _     |                                         |                    | Capture/Co | ompare/PWN | V1 Register  | Low Byte  |        |        | 0000          |

| CCPR1H                  | 0194 | -      | _      | _      | _      | _      | _      | _     | _     |                                         |                    | Capture/Co | mpare/PWN  | /11 Register | High Byte |        |        | 0000          |

| ECCP1DEL <sup>(1)</sup> | 0196 | -      | _      | _      | _      | _      | _      | _     | _     | PRSEN                                   | PDC6               | PDC5       | PDC4       | PDC3         | PDC2      | PDC1   | PDC0   | 0000          |

| ECCP1AS <sup>(1)</sup>  | 0198 | -      | _      | _      | _      | _      | _      | _     | _     | ECCPASE                                 | ECCPAS2            | ECCPAS1    | ECCPAS0    | PSSAC1       | PSSAC0    | PSSBD1 | PSSBD0 | 0000          |

| PSTR1CON(1)             | 019A | _      | _      | _      | _      | _      | _      | _     | _     | CMPL1                                   | CMPL0              | _          | STRSYNC    | STRD         | STRC      | STRB   | STRA   | 0001          |

| CCP2CON                 | 019C | _      | _      | _      | _      | _      | _      | _     | _     | —                                       | _                  | DC2B1      | DC2B0      | CCP2M3       | CCP2M2    | CCP2M1 | CCP2M0 | 0000          |

| CCPR2L                  | 019E | _      | _      | _      | _      | _      | _      | _     | _     |                                         |                    | Capture/Co | ompare/PWN | M2 Register  | Low Byte  |        |        | 0000          |

| CCPR2H                  | 01A0 | _      | _      | _      | _      | _      | _      | _     | _     |                                         |                    | Capture/Co | ompare/PWN | /12 Register | High Byte |        |        | 0000          |

| CCP3CON <sup>(1)</sup>  | 01A8 | _      | _      | _      | _      | _      | _      | _     | _     | —                                       | _                  | DC3B1      | DC3B0      | CCP3M3       | CCP3M2    | CCP3M1 | CCP3M0 | 0000          |

| CCPR3L <sup>(1)</sup>   | 01AA | _      | _      | _      | _      | _      | _      | _     | _     | Capture/Compare/PWM3 Register Low Byte  |                    |            |            |              |           |        |        |               |

| CCPR3H <sup>(1)</sup>   | 01AC | _      |        | _      | _      | _      | —      | —     | _     | Capture/Compare/PWM3 Register High Byte |                    |            |            |              |           |        |        |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

## TABLE 4-10: PORTA REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 <sup>(1)</sup> | Bit 6  | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|----------------------|--------|----------------------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 02C0 | _      | _      | —      | —      | _      | _      | _     | _     | TRISA7               | TRISA6 | _                    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 00DF          |

| PORTA        | 02C2 |        | —      |        |        |        |        |       | —     | RA7                  | RA6    | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA         | 02C4 |        | —      |        |        |        |        |       | —     | LATA7                | LATA6  | —                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA         | 02C6 | -      | _      | _      | _      | _      | _      | _     | -     | ODA7                 | ODA6   | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These ports and their associated bits are unimplemented on 14-pin and 20-pin devices; read as '0'.

2: PORTA<5> is unavailable when MCLR functionality is enabled (MCLRE Configuration bit = 1).

#### TABLE 4-11: PORTB REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13 <sup>(1)</sup> | Bit 12 <sup>(1)</sup> | Bit 11 <sup>(2)</sup> | Bit 10 <sup>(2)</sup> | Bit 9  | Bit 8  | Bit 7 <sup>(1)</sup> | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3 <sup>(2)</sup> | Bit 2 <sup>(1)</sup> | Bit 1 <sup>(1)</sup> | Bit 0  | All<br>Resets |

|--------------|------|---------|---------|-----------------------|-----------------------|-----------------------|-----------------------|--------|--------|----------------------|----------------------|----------------------|--------|----------------------|----------------------|----------------------|--------|---------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13               | TRISB12               | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7               | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2               | TRISB1               | TRISB0 | FFFF          |

| PORTB        | 02CA | RB15    | RB14    | RB13                  | RB12                  | RB11                  | RB10                  | RB9    | RB8    | RB7                  | RB6                  | RB5                  | RB4    | RB3                  | RB2                  | RB1                  | RB0    | xxxx          |

| LATB         | 02CC | LATB15  | LATB14  | LATB13                | LATB12                | LATB11                | LATB10                | LATB9  | LATB8  | LATB7                | LATB6                | LATB5                | LATB4  | LATB3                | LATB2                | LATB1                | LATB0  | xxxx          |

| ODCB         | 02CE | ODB15   | ODB14   | ODB13                 | ODB12                 | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7                 | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2                 | ODB1                 | ODB0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These ports and their associated bits are unimplemented on 14-pin and 20-pin devices.

2: These ports and their associated bits are unimplemented in 14-pin devices.

## TABLE 4-12: PAD CONFIGURATION REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11                 | Bit 10     | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|------------------------|------------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| PADCFG1      | 02FC | —      | —      | _      | —      | SDO2DIS <sup>(1)</sup> | SCK2DIS(1) | SDO1DIS | SCK1DIS | —     | _     | _     | _     | _     | —     | —     | —     | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12    | Bit 11                | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5 | Bit 4                | Bit 3                | Bit 2                | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|-----------|-----------------------|--------|--------|--------|---------|-------|-------|----------------------|----------------------|----------------------|--------|--------|---------------|

| ADC1BUF0     | 0300 |        |        |        |           |                       |        |        | A/D Bu | uffer 0 |       |       |                      |                      |                      |        |        | xxxx          |

| ADC1BUF1     | 0302 |        |        |        |           |                       |        |        | A/D Bu | uffer 1 |       |       |                      |                      |                      |        |        | xxxx          |

| AD1CON1      | 0320 | ADON   | —      | ADSIDL | —         | _                     | _      | FORM1  | FORM0  | SSRC2   | SSRC1 | SSRC0 | _                    |                      | ASAM                 | SAMP   | DONE   | 0000          |

| AD1CON2      | 0322 | VCFG2  | VCFG1  | VCFG0  | OFFCAL    | —                     | CSCNA  |        | _      | r       |       | SMPI3 | SMPI2                | SMPI1                | SMPI0                | r      | ALTS   | 0000          |

| AD1CON3      | 0324 | ADRC   | EXTSAM | PUMPEN | SAMC4     | SAMC3                 | SAMC2  | SAMC1  | SAMC0  |         |       | ADCS5 | ADCS4                | ADCS3                | ADCS2                | ADCS1  | ADCS0  | 0000          |

| AD1CHS       | 0328 | CH0NB  | —      |        | —         | CH0SB3                | CH0SB2 | CH0SB1 | CH0SB0 | CH0NA   |       | _     | _                    | CH0SA3               | CH0SA2               | CH0SA1 | CH0SA0 | 0000          |

| AD1CSSL      | 0330 | CSSL15 | CSSL14 | CSSL13 | CSSL12(1) | CSSL11 <sup>(1)</sup> | CSSL10 | CSSL9  | CSSL8  | CSSL7   | CSSL6 | _     | CSSL4 <sup>(1)</sup> | CSSL3 <sup>(1)</sup> | CSSL2 <sup>(1)</sup> | CSSL1  | CSSL0  | 0000          |

Legend: — = unimplemented, read as '0', r = reserved bit. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 14-pin devices; read as '0'.

#### TABLE 4-14: ANALOG SELECT REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12                | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2                | Bit 1                | Bit 0                | All<br>Resets       |

|-----------|------|--------|--------|--------|-----------------------|--------|--------|-------|-------|-------|-------|-------|-------|----------|----------------------|----------------------|----------------------|---------------------|

| ANCFG     | 04DE | _      | —      | —      | —                     | _      | _      |       | _     | _     | _     |       |       | _        | —                    |                      | VBGEN                | 0000                |

| ANSA      | 04E0 | -      | _      | -      | —                     | _      | -      | _     | _     | _     | _     | _     | _     | ANSA3    | ANSA2                | ANSA1                | ANSA0                | 000F                |

| ANSB      | 04E2 | ANSB15 | ANSB14 | ANSB13 | ANSB12 <sup>(1)</sup> | —      | _      | _     | _     | —     | —     | _     | ANSB4 | ANSB3(2) | ANSB2 <sup>(1)</sup> | ANSB1 <sup>(1)</sup> | ANSB0 <sup>(1)</sup> | F01F <sup>(3)</sup> |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented in 14-pin devices; read as '0'.

2: These bits are unimplemented in 14-pin and 20-pin devices; read as '0'

3: Reset value for 28-pin devices is shown.

#### TABLE 4-15: COMPARATOR REGISTER MAP

| File<br>Name          | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------------------|------|--------|--------|--------|--------|--------|--------|----------------------|-------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT                | 0630 | CMIDL  | —      | _      |        | _      | _      | C2EVT <sup>(1)</sup> | C1EVT | —      | —      | _     |       | _     | _     | C2OUT | C1OUT | xxxx          |

| CVRCON                | 0632 | _      | _      | _      | _      | _      | _      | _                    | _     | CVREN  | CVROE  | CVRSS | CVR4  | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON                | 0634 | CON    | COE    | CPOL   | CLPWR  | —      | _      | CEVT                 | COUT  | EVPOL1 | EVPOL0 | —     | CREF  | —     | _     | CCH1  | CCH0  | xxxx          |

| CM2CON <sup>(1)</sup> | 0636 | CON    | COE    | CPOL   | CLPWR  | _      | _      | CEVT                 | COUT  | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented in PIC24FXXKL10X/20X devices; read as '0'.

#### TABLE 4-16: SYSTEM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | SBOREN | —      | —      | _      | CM     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 3100          |

| OSCTUN    | 0748 | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 074E | ROEN   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN | -      | HLSIDL | _      | —      | _      | _      | _      | VDIR    | BGVST | IRVST  |       | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on configuration fuses and by type of Reset.

#### TABLE 4-17: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7            | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|---------|--------|--------|-------|-------|------------------|-------|--------|--------|--------|--------|--------|--------|---------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | PGMONLY |        | _      | _     |       | —                | ERASE | NVMOP5 | NVMOP4 | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMKEY    | 0766 | _      | -      | -      | —       | —      |        | _     |       | NVM Key Register |       |        |        |        |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-18: ULTRA LOW-POWER WAKE-UP REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|---------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ULPWCON   | 0768 | ULPEN  | _      | ULPSIDL |        | —      | _      |       | ULPSINK |       | _     |       | _     | _     |       | _     | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-19: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|---------|-------|-------|-------|--------|--------|--------|--------|------------|

| PMD1      | 0770 | _      | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     |       | SSP1MD  | U2MD  | U1MD  |       | —      | _      |        | ADC1MD | 0000       |

| PMD2      | 0772 | _      | —      | —      | _      | —      | —      | _     | -     | _       | _     | —     | _     | —      | CCP3MD | CCP2MD | CCP1MD | 0000       |

| PMD3      | 0774 | _      | _      | _      |        |        | CMPMD  | _     | -     | —       | _     | _     |       | —      | _      | SSP2MD | —      | 0000       |

| PMD4      | 0776 |        | _      | _      | _      | _      | _      | -     | —     | ULPWUMD |       | _     | EEMD  | REFOMD | —      | HLVDMD | _      | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS30001037C-page 42

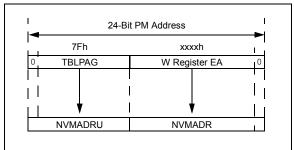

# 6.3 NVM Address Register

As with Flash program memory, the NVM Address Registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space; instead, they directly capture the EA<23:0> of the last Table Write instruction that has been executed and selects the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", is unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

#### FIGURE 6-1: DATA EEPROM ADDRESSING WITH TBLPAG AND NVM ADDRESS REGISTERS

# 6.4 Data EEPROM Operations

The EEPROM block is accessed using Table Read and Table Write operations, similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- Bulk erase the entire data EEPROM

- Write one word

- Read one word

| Note: | Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | The C30 C compiler includes library<br>procedures to automatically perform the<br>Table Read and Table Write operations,<br>manage the Table Pointer and write<br>buffers, and unlock and initiate memory<br>write sequences. This eliminates the need<br>to create assembler macros or time<br>critical routines in C for each application. |

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the C30 compiler libraries.

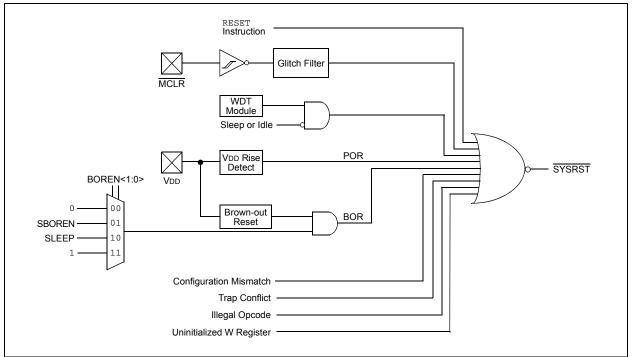

# 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Resets, refer to the "dsPIC33/PIC24 Family Reference Manual", "Reset with Programmable Brown-out Reset" (DS39728).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- · UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on a Power-on Reset (POR) and unchanged by all other Resets.

**Note:** Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A POR will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer (WDT) and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value, after a device Reset, will be meaningful.

# FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

### 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

## 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSC bits in the Flash Configuration Word (FOSCSEL); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

# 7.4 Brown-out Reset (BOR)

PIC24F16KL402 family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above the threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the power-up timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the BOR Reset does not automatically enable the PWRT.

# 7.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<13>). Setting SBOREN enables the BOR to function, as previously described. Clearing the SBOREN disables the BOR entirely. The SBOREN bit only operates in this mode; otherwise, it is read as '0'.

Placing BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

Note: Even when the BOR is under software control, the BOR Reset voltage level is still set by the BORV<1:0> Configuration bits; it can not be changed in software.

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7   | CLKLOCK: Clock Selection Lock Enable bit                                                 |

|---------|------------------------------------------------------------------------------------------|

|         | <u>If FSCM is Enabled (FCKSM1 = 1):</u>                                                  |

|         | 1 = Clock and PLL selections are locked                                                  |

|         | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit |

|         | If FSCM is Disabled (FCKSM1 = 0):                                                        |

|         | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.  |

| bit 6   | Unimplemented: Read as '0'                                                               |

| bit 5   | LOCK: PLL Lock Status bit <sup>(2)</sup>                                                 |

|         | 1 = PLL module is in lock or the PLL module start-up timer is satisfied                  |

|         | 0 = PLL module is out of lock, the PLL start-up timer is running or PLL is disabled      |

| bit 4   | Unimplemented: Read as '0'                                                               |

| bit 3   | CF: Clock Fail Detect bit                                                                |

|         | 1 = FSCM has detected a clock failure                                                    |

|         | 0 = No clock failure has been detected                                                   |

| bit 2   | SOSCDRV: Secondary Oscillator Drive Strength bit <sup>(3)</sup>                          |

|         | 1 = High-power SOSC circuit is selected                                                  |

|         | 0 = Low/high-power select is done via the SOSCSRC Configuration bit                      |

| bit 1   | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                    |

|         | 1 = Enables secondary oscillator                                                         |

|         | 0 = Disables secondary oscillator                                                        |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                      |

|         | 1 = Initiates an oscillator switch to the clock source specified by the NOSC<2:0> bits   |

|         | 0 = Oscillator switch is complete                                                        |

| Note 1: | Reset values for these bits are determined by the FNOSC<2:0> Configuration bits.         |

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- **3:** When SOSC is selected to run from a digital clock input rather than an external crystal (SOSCSRC = 0), this bit has no effect.

| ROI         DOZE2         DOZE1         DOZE0         DOZEN <sup>(1)</sup> RCDIV2         RCDIV1         RCD           bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ′W-1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0                   bit 15       Recadable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit         1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts clear the DOZEN bit         bit 14-12       DOZE         DOZE         110 = 1:64       101 = 1:32         100 = 1:16       111 = 1:32         100 = 1:1       DOZE Colspan="2">DOZE Enable bit <sup>(1)</sup> 1 = DOZE       DOZE Enable bit <sup>(1)</sup> 1 = DOZE       COCON:11:12) = 111 or 001:         101 = 1:2       OOI: State (divide-by-64)         101 = 250 kHz (divide-by-64)       OOI: State (divide-by-64)         101 = 250 kHz (divide-by-20)       OOI: 111 F 3125 kHz (divide-by-20)         101 = 250 kHz (divide-by-21)       OII: 2         101 = 20       OIII = 1MHz (divide-by-20)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DIV0  |

| -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 8 |

| -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.0   |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>bit 14-12 DOZE-2:0>: CPU-to-Peripheral Clock Ratio Select bits<br>111 = 1:128<br>100 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:3<br>010 = 1:16<br>011 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: DOZE Enable bit <sup>(1)</sup><br>1 = DOZE-2:0> bits specify the CPU-to-peripheral clock ratio<br>0 = CPU and the peripheral clock ratio are set to 1:1<br>bit 10-8 RCDIV-2:0>: FRC Postscaler Select bits<br>When COSC-2:0> (OSCCON<14:12) = 111 or 001:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-4)<br>011 = 4 MHz (divide-by-4)<br>011 = 4 MHz (divide-by-2) (offault)<br>00 = 8 MHz (divide-by-2) (offault)<br>00 = 8 MHz (divide-by-2) (00Fault)<br>110 = 156 kHz (divide-by-32)<br>110 = 156 kHz (divide-by-32)<br>110 = 156 kHz (divide-by-32)<br>111 = 1.95 kHz (divide-by-32)<br>111 = 1.95 kHz (divide-by-32)<br>111 = 1.95 kHz (divide-by-32)<br>112 = 1.05 kHz (divide-by-32)<br>113 = 1.95 kHz (divide-by-32)<br>114 = 1.95 kHz (divide-by-32)<br>115 = 1.95 kHz (divide-by-32)<br>116 = 7.81 kHz (divide-by-32)<br>117 = 1.95 kHz (divide-by-4)<br>118 = 1.95 kHz (divide-by-32)<br>119 = 31.25 kHz (divide-by-32)<br>110 = 1.55 kHz (divide-by-4)<br>111 = 1.95 kHz (divide-by-32)<br>112 = 1.95 kHz (divide-by-32)<br>113 = 1.95 kHz (divide-by-4)<br>114 = 1.95 kHz (divide-by-4)<br>115 = 1.55 kHz (divide-by-4)<br>116 = 1.55 kHz (divide-by-4)<br>117 = 1.95 kHz (divide-by-4)<br>118 = 1.95 kHz (divide-by-4)<br>119 = 1.55 kHz (divide-by-4)<br>110 = 1.55 kHz (divide-by-4)<br>111 = 1.95 kHz (divide-by-4)<br>112 = 1.95 kHz (divide-by-4)<br>113 = 1.95 kHz (divide-by-4)<br>114 = 1.95 kHz (divide-by-4)<br>115 = 1.55 kHz (divide-by-4)<br>116 = 1.55 kHz (divide-by-4)<br>117 = 1.55 kHz (divide-by-4)<br>118 = 1.55 kHz (divide-by-4)<br>119 = 1.55 kHz (divide-by-4)<br>110 = 1.55 kHz (divide-by-4)<br>111 = 1.95 kHz (divide-by-4)<br>111 = 1.95 kHz (divi       |       |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<br>.n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 15ROI: Recover on Interrupt bit<br>.1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>.1 = Interrupts have no effect on the DOZEN bitbit 14-12DOZE-2:0>: CPU-to-Peripheral Clock Ratio Select bits111 = 1:128<br>.100 = 1:6<br>.011 = 1:8<br>.000 = 1:16<br>.001 = 1:2<br>.000 = 1:1bit 11DOZEN: DOZE Enable bit(1)<br>.000 = 1:1bit 11DOZEN: DOZE Enable bit(1)<br>.000 = 1:1bit 10-RCDIV<2:0>: FRC Postscaler Select bitsWhen COSC-2:0> (DSCCON<14:12) = 111 or .001;<br>.111 = 31.25 kHz (divide-by-26)<br>.100 = 125 kHz (divide-by-4)<br>.001 = 25 kHz (divide-by-4)001 = 2 MHz (divide-by-16)<br>.001 = 4 MHz (divide-by-16)<br>.001 = 4 MHz (divide-by-256)<br>.100 = 2.8 kHz (divide-by-26)<br>.100 = 31.25 kHz (divide-by-26)<br>.100 = 31.25 kHz (divide-by-32)<br>.100 = 31.25 kHz (divide-by-32)<br>.100 = 31.25 kHz (divide-by-4)<br>.101 = 25 kHz (divide-by-32)<br>.100 = 31.25 kHz (divide-by-4)<br>.101 = 15.62 kHz (divide-by-4)<br>.101 = 125 kHz (divide-by-4)<br>.111 = 1.95 kHz (divide-by-32)<br>.100 = 31.25 kHz (divide-by-4)<br>.111 = 1.25 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit ( |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1         0 = Interrupts have no effect on the DOZEN bit       DOZE-2:0>: CPU-to-Peripheral Clock Ratio Select bits         111 = 1:128       100 = 1:64         100 = 1:16       111 = 1:2         010 = 1:12       000 = 1:16         011 = 1:2       000 = 1:1         bit 10       DOZEE-2:0> bits specify the CPU-to-peripheral clock ratio         0 = CPU and the peripheral clock ratio are set to 1:1       bit 10-8         RCDIV<2:0>: FRC Postscaler Select bits         When COSC-2:0> (OSCCON<14:12) = 111 or 001:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>bit 14-12 DDZE<2:0>: CPU-to-Peripheral Clock Ratio Select bits<br>111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: DOZE Enable bit <sup>(1)</sup><br>1 = DOZE<2:0> bits specify the CPU-to-peripheral clock ratio<br>0 = CPU and the peripheral clock ratio are set to 1:1<br>bit 10-8 RCDIV<2:0>: FRC Postscaler Select bits<br>When COSC<2:0> (OSCCON<14:12) = 111 or 001:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-4)<br>011 = 1 MHz (divide-by-4)<br>011 = 1 MHz (divide-by-4)<br>011 = 2 MHz (divide-by-4)<br>011 = 1 MHz (divide-by-2)<br>100 = 500 kHz (divide-by-2)<br>100 = 4 MHz (divide-by-4)<br>011 = 1 MHz (divide-by-2)<br>100 = 4 MHz (divide-by-2)<br>100 = 50 KHz (divide-by-2)<br>100 = 50 KHz (divide-by-2)<br>100 = 50 KHz (divide-by-2)<br>101 = 7.81 kHz (divide-by-2)<br>102 = 7.81 kHz (divide-by-2)<br>104 = 4 MHz (divide-by-2)<br>105 = 7.81 kHz (divide-by-2)<br>105 = 7.81 kHz (divide-by-2)<br>106 = 7.81 kHz (divide-by-2)<br>107 = 7.81 kHz (divide-by-2)<br>108 = 7.81 kHz (divide-by-2)<br>109 = 3.125 kHz (divide-by-32)<br>100 = 3.125 kHz (divide-by-4)<br>101 = 1.5.62 kHz (divide-by-4)<br>102 = 3.125 kHz (divide-by-4)<br>103 = 3.125 kHz (divide-by-4)<br>104 = 3.125 kHz (divide-by-4)<br>105 = 3.125 kHz (divide-by-4)<br>105 = 3.125 kHz (divide-by-4)<br>105 = 3.125 kHz (divide-by-4)<br>105 = 3.125 kHz (divide-by-4)<br>106 = 3.125 kHz (divide-by-4)<br>107 = 3.125 kHz (divide-by-4)<br>108 = 3.125 kHz (divide-by-4)<br>109 = 3.125 kHz (divide-by-4)<br>100 = 3.125 kHz (divide-by-4)<br>101 = 1.5.5 kHz (divide-by-4)<br>102 = 3.125 kHz (divide-by-4)<br>103 = 3.5 kHz (divide-by-4)<br>104 = 3.5 kHz (divide- |       |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| bit 11<br>DOZEN: DOZE Enable bit <sup>(1)</sup><br>1 = DOZE<2:0> bits specify the CPU-to-peripheral clock ratio<br>0 = CPU and the peripheral clock ratio are set to 1:1<br>bit 10-8<br>RCDIV<2:0>: FRC Postscaler Select bits<br>When COSC<2:0> (OSCCON<14:12) = 111 or 001:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-3)<br>010 = 2 MHz (divide-by-3)<br>010 = 2 MHz (divide-by-4)<br>011 = 1 MHz (divide-by-2) (default)<br>000 = 8 MHz (divide-by-1)<br>When COSC<2:0> (OSCCON<14:12>) = 110:<br>111 = 1.95 kHz (divide-by-26)<br>110 = 7.81 kHz (divide-by-32)<br>100 = 31.25 kHz (divide-by-36)<br>011 = 62.5 kHz (divide-by-4)<br>010 = 125 kHz (divide-by-4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| 0 = CPU and the peripheral clock ratio are set to 1:1 bit 10-8 RCDIV-2:0>: FRC Postscaler Select bits When COSC<2:0> (OSCCON<14:12) = 111 or 001: 111 = 31.25 kHz (divide-by-256) 110 = 125 kHz (divide-by-256) 100 = 500 kHz (divide-by-32) 100 = 500 kHz (divide-by-4) 011 = 1 MHz (divide-by-4) 011 = 4 MHz (divide-by-4) 001 = 4 MHz (divide-by-2) (default) 000 = 8 MHz (divide-by-1) When COSC<2:0> (OSCCON<14:12>) = 110: 111 = 1.95 kHz (divide-by-256) 100 = 7.81 kHz (divide-by-32) 100 = 31.25 kHz (divide-by-36) 011 = 62.5 kHz (divide-by-8) 010 = 125 kHz (divide-by-4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| When $COSC < 2:0 > (OSCCON < 14:12) = 111 \text{ or } 001:$ 111 = 31.25 kHz (divide-by-256)         100 = 125 kHz (divide-by-64)         101 = 250 kHz (divide-by-32)         100 = 500 kHz (divide-by-16)         011 = 1 MHz (divide-by-8)         010 = 2 MHz (divide-by-4)         001 = 4 MHz (divide-by-2) (default)         000 = 8 MHz (divide-by-1)         When $COSC < 2:0 > (OSCCON < 14:12 >) = 110:$ 111 = 1.95 kHz (divide-by-256)         110 = 7.81 kHz (divide-by-32)         100 = 31.25 kHz (divide-by-32)         100 = 31.25 kHz (divide-by-16)         011 = 62.5 kHz (divide-by-8)         010 = 125 kHz (divide-by-4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| 000 = 500  kHz (divide-by-1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

#### REGISTER 9-2: CLKDIV: CLOCK DIVIDER REGISTER

Note 1: This bit is automatically cleared when the ROI bit is set and an interrupt occurs.

REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0                | U-0                            | R/W-0                            | U-0              | U-0               | U-0              | R/W-0                 | R/W-0                 |

|----------------------|--------------------------------|----------------------------------|------------------|-------------------|------------------|-----------------------|-----------------------|

| TON                  | _                              | TSIDL                            | _                | _                 | _                | T1ECS1 <sup>(1)</sup> | T1ECS0 <sup>(1)</sup> |

| bit 15               |                                | I                                |                  |                   |                  |                       | bit 8                 |

|                      |                                |                                  |                  |                   |                  |                       |                       |

| U-0                  | R/W-0                          | R/W-0                            | R/W-0            | U-0               | R/W-0            | R/W-0                 | U-0                   |

| _                    | TGATE                          | TCKPS1                           | TCKPS0           | —                 | TSYNC            | TCS                   | —                     |

| bit 7                |                                |                                  |                  |                   |                  |                       | bit (                 |

| Legend:              |                                |                                  |                  |                   |                  |                       |                       |

| R = Readabl          | e bit                          | W = Writable                     | bit              | U = Unimplerr     | nented bit. read | d as '0'              |                       |

| -n = Value at        | POR                            | '1' = Bit is set                 |                  | '0' = Bit is clea |                  | x = Bit is unkr       | iown                  |

|                      |                                |                                  |                  |                   |                  |                       |                       |

| bit 15               | TON: Timer1                    | On bit                           |                  |                   |                  |                       |                       |

|                      | 1 = Starts 16-                 |                                  |                  |                   |                  |                       |                       |

|                      | 0 = Stops 16-                  | bit Timer1                       |                  |                   |                  |                       |                       |

| bit 14               | Unimplement                    | ted: Read as '                   | )'               |                   |                  |                       |                       |

| bit 13               |                                | 1 Stop in Idle N                 |                  |                   |                  |                       |                       |

|                      |                                |                                  |                  | device enters Idl | e mode           |                       |                       |

| L:1 10 10            |                                | module opera                     |                  | de                |                  |                       |                       |

| bit 12-10<br>bit 9-8 | -                              | ted: Read as '<br>: Timer1 Exten |                  | La at hita(1)     |                  |                       |                       |

| DIL 9-0              | 11 = Reserve                   |                                  |                  | lect bits ?       |                  |                       |                       |

|                      |                                | ises the LPRC                    | as the clock s   | ource             |                  |                       |                       |

|                      |                                | ises the extern                  |                  |                   |                  |                       |                       |

|                      | 00 <b>= Timer1</b> u           | ises the Secon                   | dary Oscillato   | r (SOSC) as the   | clock source     |                       |                       |

| bit 7                | Unimplement                    | ted: Read as '                   | י'               |                   |                  |                       |                       |

| bit 6                | TGATE: Time                    | r1 Gated Time                    | Accumulation     | Enable bit        |                  |                       |                       |

|                      | When TCS =                     | -                                |                  |                   |                  |                       |                       |

|                      | This bit is igno<br>When TCS = |                                  |                  |                   |                  |                       |                       |

|                      |                                | <u>u.</u><br>ne accumulatio      | n is enabled     |                   |                  |                       |                       |

|                      |                                | ne accumulatio                   |                  |                   |                  |                       |                       |

| bit 5-4              | TCKPS<1:0>                     | : Timer1 Input                   | Clock Prescal    | e Select bits     |                  |                       |                       |

|                      | 11 <b>= 1:256</b>              |                                  |                  |                   |                  |                       |                       |

|                      | 10 = 1:64                      |                                  |                  |                   |                  |                       |                       |

|                      | 01 = 1:8<br>00 = 1:1           |                                  |                  |                   |                  |                       |                       |

| bit 3                |                                | ted: Read as '                   | )'               |                   |                  |                       |                       |

| bit 2                | -                              |                                  |                  | hronization Sele  | ect bit          |                       |                       |

|                      | When TCS =                     |                                  | , ,              |                   |                  |                       |                       |

|                      | 1 = Synchron                   | nizes external (                 |                  |                   |                  |                       |                       |

|                      |                                | t synchronize e                  | external clock i | input             |                  |                       |                       |

|                      | When TCS =                     |                                  |                  |                   |                  |                       |                       |

| hit 1                | This bit is igno               | Clock Source S                   | Soloct bit       |                   |                  |                       |                       |

| bit 1                |                                | ock source is s                  |                  | ECS<1.05          |                  |                       |                       |