Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VFQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl402t-i-mq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-4: PIC24F16KL40X/30X FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|            |                                  | Pin N         | umber                             |               |            |                  |                                           |

|------------|----------------------------------|---------------|-----------------------------------|---------------|------------|------------------|-------------------------------------------|

| Function   | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | I/O        | Buffer           | Description                               |

| PGEC1      | 5                                | 2             | 5                                 | 2             | I/O        | ST               | ICSP™ Clock 1                             |

| PCED1      | 4                                | 1             | 4                                 | 1             | I/O        | ST               | ICSP Data 1                               |

| PGEC2      | 2                                | 19            | 22                                | 19            | I/O        | ST               | ICSP Clock 2                              |

| PGED2      | 3                                | 20            | 21                                | 18            | I/O        | ST               | ICSP Data 2                               |

| PGEC3      | 10                               | 7             | 15                                | 12            | I/O        | ST               | ICSP Clock 3                              |

| PGED3      | 9                                | 6             | 14                                | 11            | I/O        | ST               | ICSP Data 3                               |

| RA0        | 2                                | 19            | 2                                 | 27            | I/O        | ST               | PORTA Pins                                |

| RA1        | 3                                | 20            | 3                                 | 28            | I/O        | ST               |                                           |

| RA2        | 7                                | 4             | 9                                 | 6             | I/O        | ST               |                                           |

| RA3        | 8                                | 5             | 10                                | 7             | I/O        | ST               |                                           |

| RA4        | 10                               | 7             | 12                                | 9             | I/O        | ST               |                                           |

| RA5        | 1                                | 18            | 1                                 | 26            | I          | ST               | -                                         |

| RA6        | 14                               | 11            | 20                                | 17            | I/O        | ST               |                                           |

| RA7        |                                  | _             | 19                                | 16            | I/O        | ST               | 202723                                    |

| RB0        | 4                                | 1             | 4                                 | 1             | 1/0        | ST               | PORTB Pins                                |

| RB1        | 5                                | 2             | 5                                 | 2             | 1/0        | ST               |                                           |

| RB2        | 6                                | 3             | 6<br>7                            | 3             | I/O<br>I/O | ST<br>ST         |                                           |

| RB3        | 9                                | -             | 11                                | 8             | 1/0        | ST               |                                           |

| RB4<br>RB5 | —<br>—                           | 6             | 14                                | 11            | 1/0        | ST               | -                                         |

| RB6        |                                  |               | 15                                | 12            | 1/0        | ST               |                                           |

| RB7        | 11                               | 8             | 16                                | 13            | 1/0        | ST               |                                           |

| RB8        | 12                               | 9             | 17                                | 14            | I/O        | ST               |                                           |

| RB9        | 13                               | 10            | 18                                | 15            | I/O        | ST               |                                           |

| RB10       | _                                | _             | 21                                | 18            | I/O        | ST               |                                           |

| RB11       | _                                | _             | 22                                | 19            | I/O        | ST               |                                           |

| RB12       | 15                               | 12            | 23                                | 20            | I/O        | ST               |                                           |

| RB13       | 16                               | 13            | 24                                | 21            | I/O        | ST               |                                           |

| RB14       | 17                               | 14            | 25                                | 22            | I/O        | ST               |                                           |

| RB15       | 18                               | 15            | 26                                | 23            | I/O        | ST               |                                           |

| REFO       | 18                               | 15            | 26                                | 23            | 0          | _                | Reference Clock Output                    |

| SCK1       | 15                               | 12            | 22                                | 19            | I/O        | ST               | MSSP1 SPI Serial Input/Output Clock       |

| SCK2       | 18                               | 15            | 14                                | 11            | I/O        | ST               | MSSP2 SPI Serial Input/Output Clock       |

| SCL1       | 12                               | 9             | 17                                | 14            | I/O        | I <sup>2</sup> C | MSSP1 I <sup>2</sup> C Clock Input/Output |

| SCL2       | 18                               | 15            | 7                                 | 4             | I/O        | I <sup>2</sup> C | MSSP2 I <sup>2</sup> C Clock Input/Output |

| SCLKI      | 10                               | 7             | 12                                | 9             | I          | ST               | Digital Secondary Clock Input             |

| SDA1       | 13                               | 10            | 18                                | 15            | I/O        | I <sup>2</sup> C | MSSP1 I <sup>2</sup> C Data Input/Output  |

| SDA2       | 2                                | 19            | 2                                 | 27            | I/O        | I <sup>2</sup> C | MSSP2 I <sup>2</sup> C Data Input/Output  |

| SDI1       | 17                               | 14            | 21                                | 18            | I          | ST               | MSSP1 SPI Serial Data Input               |

| SDI2       | 2                                | 19            | 19                                | 16            | I          | ST               | MSSP2 SPI Serial Data Input               |

| SD01       | 16                               | 13            | 24                                | 21            | 0          | _                | MSSP1 SPI Serial Data Output              |

| SDO2       | 3                                | 20            | 15                                | 12            | 0          |                  | MSSP2 SPI Serial Data Output              |

**Legend:** TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer I<sup>2</sup>C = I<sup>2</sup>C™/SMBus input buffer

### TABLE 4-10: PORTA REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 <sup>(1)</sup> | Bit 6  | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|----------------------|--------|----------------------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 02C0 | 1      | _      | -      | _      | -      | _      | -     | -     | TRISA7               | TRISA6 | _                    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 00DF          |

| PORTA        | 02C2 | -      | _      | _      | _      | _      | _      | _     | _     | RA7                  | RA6    | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA         | 02C4 | -      | _      | _      | _      | _      | _      | _     | _     | LATA7                | LATA6  | _                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA         | 02C6 | -      | _      | ı      | _      | ı      | _      | ı     | ı     | ODA7                 | ODA6   | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These ports and their associated bits are unimplemented on 14-pin and 20-pin devices; read as '0'.

2: PORTA<5> is unavailable when  $\overline{MCLR}$  functionality is enabled (MCLRE Configuration bit = 1).

### TABLE 4-11: PORTB REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13 <sup>(1)</sup> | Bit 12 <sup>(1)</sup> | Bit 11 <sup>(2)</sup> | Bit 10 <sup>(2)</sup> | Bit 9  | Bit 8  | Bit 7 <sup>(1)</sup> | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3 <sup>(2)</sup> | Bit 2 <sup>(1)</sup> | Bit 1 <sup>(1)</sup> | Bit 0  | All<br>Resets |

|--------------|------|---------|---------|-----------------------|-----------------------|-----------------------|-----------------------|--------|--------|----------------------|----------------------|----------------------|--------|----------------------|----------------------|----------------------|--------|---------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13               | TRISB12               | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7               | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2               | TRISB1               | TRISB0 | FFFF          |

| PORTB        | 02CA | RB15    | RB14    | RB13                  | RB12                  | RB11                  | RB10                  | RB9    | RB8    | RB7                  | RB6                  | RB5                  | RB4    | RB3                  | RB2                  | RB1                  | RB0    | xxxx          |

| LATB         | 02CC | LATB15  | LATB14  | LATB13                | LATB12                | LATB11                | LATB10                | LATB9  | LATB8  | LATB7                | LATB6                | LATB5                | LATB4  | LATB3                | LATB2                | LATB1                | LATB0  | xxxx          |

| ODCB         | 02CE | ODB15   | ODB14   | ODB13                 | ODB12                 | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7                 | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2                 | ODB1                 | ODB0   | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These ports and their associated bits are unimplemented on 14-pin and 20-pin devices.

2: These ports and their associated bits are unimplemented in 14-pin devices.

### TABLE 4-12: PAD CONFIGURATION REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11                 | Bit 10                 | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|------------------------|------------------------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| PADCFG1      | 02FC | 1      | _      | _      | 1      | SDO2DIS <sup>(1)</sup> | SCK2DIS <sup>(1)</sup> | SDO1DIS | SCK1DIS | _     | _     | _     |       | _     | -     | _     | _     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

#### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|---------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY | _   | _   | _   | _     |

| bit 15     |       |       |         |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _     | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:           | HC = Hardware Clearable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit            | SO = Settable Only bit             |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 15 **WR:** Write Control bit (program or erase)

1 = Initiates a data EEPROM erase or write cycle (can be set but not cleared in software)

0 = Write cycle is complete (cleared automatically by hardware)

bit 14 WREN: Write Enable bit (erase or program)

1 = Enables an erase or program operation

0 = No operation allowed (device clears this bit on completion of the write/erase operation)

bit 13 WRERR: Flash Error Flag bit

1 = A write operation is prematurely terminated (any  $\overline{MCLR}$  or WDT Reset during programming operation)

0 = The write operation completed successfully

bit 12 **PGMONLY:** Program Only Enable bit

1 = Write operation is executed without erasing target address(es) first

0 = Automatic erase-before-write; write operations are preceded automatically by an erase of target address(es)

bit 11-7 **Unimplemented:** Read as '0'

bit 6 **ERASE**: Erase Operation Select bit

1 = Performs an erase operation when WR is set

0 = Performs a write operation when WR is set

bit 5-0 **NVMOP<5:0>:** Programming Operation Command Byte bits<sup>(1)</sup>

Erase Operations (when ERASE bit is '1'):

011010 = Erases 8 words

011001 = Erases 4 words

011000 = Erases 1 word

0100xx = Erases entire data EEPROM

Programming Operations (when ERASE bit is '0'):

001xxx = Writes 1 word

Note 1: These NVMOP configurations are unimplemented on PIC24F04KL10X and PIC24F08KL20X devices.

### REGISTER 8-17: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

|--------|-------|-------|-------|-----|---------|---------|---------|

| _      | T1IP2 | T1IP1 | T1IP0 |     | CCP1IP2 | CCP1IP1 | CCP1IP0 |

| bit 15 |       |       |       |     |         |         | bit 8   |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|-----|-----|-----|-----|---------|---------|---------|

| _     | _   | _   | _   | _   | INT0IP2 | INT0IP1 | INT0IP0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 T1IP<2:0>: Timer1 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 CCP1IP<2:0>: Capture/Compare/PWM1 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

-

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 **INT0IP<2:0>:** External Interrupt 0 Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

### REGISTER 8-18: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

|--------|-------|-------|-------|-----|---------|---------|---------|

| _      | T2IP2 | T2IP1 | T2IP0 | _   | CCP2IP2 | CCP2IP1 | CCP2IP0 |

| bit 15 |       |       |       |     |         |         | bit 8   |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 **T2IP<2:0>:** Timer2 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 **CCP2IP<2:0>:** Capture/Compare/PWM2 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

-

\_

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7-0 **Unimplemented:** Read as '0'

### REGISTER 9-2: CLKDIV: CLOCK DIVIDER REGISTER

| R/W-0  | R/W-0 | R/W-1 | R/W-1 | R/W-0                | R/W-0  | R/W-0  | R/W-1  |

|--------|-------|-------|-------|----------------------|--------|--------|--------|

| ROI    | DOZE2 | DOZE1 | DOZE0 | DOZEN <sup>(1)</sup> | RCDIV2 | RCDIV1 | RCDIV0 |

| bit 15 |       |       |       |                      |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   |     |     | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 ROI: Recover on Interrupt bit

1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1

0 = Interrupts have no effect on the DOZEN bit

bit 14-12 DOZE<2:0>: CPU-to-Peripheral Clock Ratio Select bits

111 = 1:128

110 = 1:64

101 = 1:32

100 = 1:16

011 = 1:8

010 = 1:4

001 = 1:2

000 = 1:1

bit 11 **DOZEN:** DOZE Enable bit<sup>(1)</sup>

1 = DOZE<2:0> bits specify the CPU-to-peripheral clock ratio

0 = CPU and the peripheral clock ratio are set to 1:1

bit 10-8 RCDIV<2:0>: FRC Postscaler Select bits

When COSC<2:0> (OSCCON<14:12) = 111 or 001:

111 = 31.25 kHz (divide-by-256)

110 = 125 kHz (divide-by-64)

101 = 250 kHz (divide-by-32)

100 = 500 kHz (divide-by-16)

011 = 1 MHz (divide-by-8)

010 = 2 MHz (divide-by-4)

001 = 4 MHz (divide-by-2) (default)

000 = 8 MHz (divide-by-1)

When COSC<2:0> (OSCCON<14:12>) = 110:

111 = 1.95 kHz (divide-by-256)

110 = 7.81 kHz (divide-by-64)

101 = 15.62 kHz (divide-by-32)

100 = 31.25 kHz (divide-by-16)

011 = 62.5 kHz (divide-by-8)

010 = 125 kHz (divide-by-4)

001 = 250 kHz (divide-by-2) (default)

000 = 500 kHz (divide-by-1)

bit 7-0 Unimplemented: Read as '0'

Note 1: This bit is automatically cleared when the ROI bit is set and an interrupt occurs.

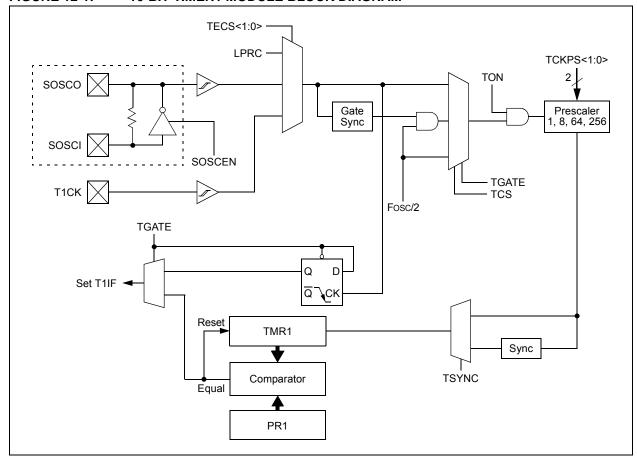

### 12.0 TIMER1

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can operate as a free-running, interval timer/counter, or serve as the time counter for a software-based Real-Time Clock (RTC). Timer1 is only reset on initial VDD power-on events. This allows the timer to continue operating as an RTC clock source through other types of device Reset.

Timer1 can operate in three modes:

- · 16-Bit Timer

- · 16-Bit Synchronous Counter

- · 16-Bit Asynchronous Counter

Timer1 also supports these features:

- · Timer Gate Operation

- · Selectable Prescaler Settings

- · Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 illustrates a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- Set the TON bit (= 1).

- Select the timer prescaler ratio using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- Load the timer period value into the PR1 register.

- If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### REGISTER 14-1: T3CON: TIMER3 CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   | R/W-0                      | R/W-0 | R/W-0   | R/W-0 R/W-0 |         | R/W-0 U-0 |       |

|---------|----------------------------|-------|---------|-------------|---------|-----------|-------|

| TMR3CS1 | S1 TMR3CS0 T3CKPS1 T3CKPS0 |       | T3OSCEN | T3SYNC      | 3SYNC — |           |       |

| bit 7   |                            |       |         |             |         |           | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-6 TMR3CS<1:0>: Timer3 Clock Source Select bits

11 = Low-Power RC Oscillator (LPRC)

10 = External clock source (selected by T3CON<3>)

01 = Instruction clock (Fosc/2) 00 = System clock (Fosc)<sup>(1)</sup>

bit 5-4 T3CKPS<1:0>: Timer3 Input Clock Prescale Select bits

11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value

bit 3 T3OSCEN: Timer3 Oscillator Enable bit

1 = SOSC (Secondary Oscillator) is used as a clock source

0 = T3CK digital input pin is used as a clock source

bit 2 T3SYNC: Timer3 External Clock Input Synchronization Control bit

When TMR3CS<1:0> = 1x:

1 = Does not synchronize the external clock input

0 = Synchronizes the external clock input(2)

0 = Synchronizes the external clock input<sup>(2)</sup>

When TMR3CS<1:0> = 0x:

This bit is ignored; Timer3 uses the internal clock.

bit 1 **Unimplemented:** Read as '0'

bit 0 TMR3ON: Timer3 On bit

1 = Enables Timer3

0 = Stops Timer3

Note 1: The Fosc clock source should not be selected if the timer will be used with the ECCP capture or compare features.

2: This option must be selected when the timer will be used with ECCP/CCP.

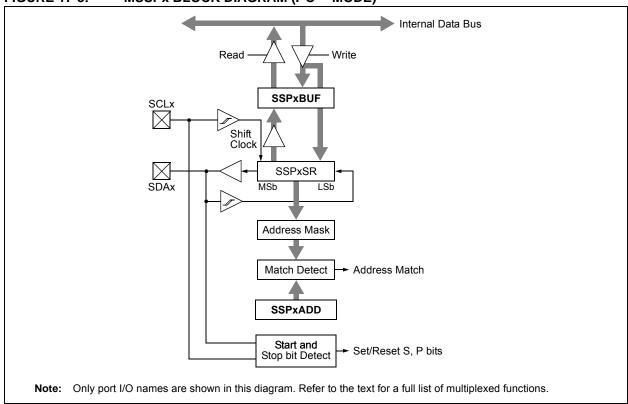

FIGURE 17-3: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

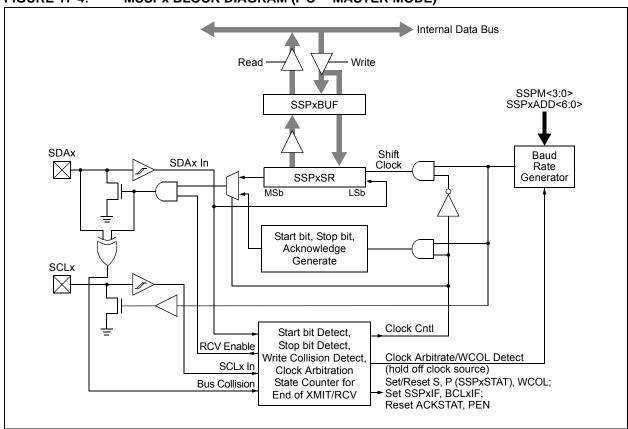

FIGURE 17-4: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C™ MASTER MODE)

### REGISTER 17-5: SSPxCON2: MSSPx CONTROL REGISTER 2 (I<sup>2</sup>C™ MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0   | R/W-0                | R/W-0                | R/W-0               | R/W-0              | R/W-0               | R/W-0              |

|-------|---------|----------------------|----------------------|---------------------|--------------------|---------------------|--------------------|

| GCEN  | ACKSTAT | ACKDT <sup>(1)</sup> | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup> | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7 |         |                      |                      |                     |                    |                     | bit 0              |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7 GCEN: General Call Enable bit (Slave mode only)

1 = Enables interrupt when a general call address (0000h) is received in the SSPxSR

0 = General call address is disabled

bit 6 ACKSTAT: Acknowledge Status bit (Master Transmit mode only)

1 = Acknowledge was not received from slave0 = Acknowledge was received from slave

bit 5 ACKDT: Acknowledge Data bit (Master Receive mode only)<sup>(1)</sup>

1 = No Acknowledge0 = Acknowledge

bit 4 ACKEN: Acknowledge Sequence Enable bit (Master mode only)(2)

1 = Initiates Acknowledge sequence on SDAx and SCLx pins, and transmits ACKDT data bit; automatically cleared by hardware

0 = Acknowledge sequence is Idle

bit 3 RCEN: Receive Enable bit (Master Receive mode only)(2)

1 = Enables Receive mode for I<sup>2</sup>C

0 = Receive is Idle

bit 2 **PEN:** Stop Condition Enable bit (Master mode only)<sup>(2)</sup>

1 = Initiates Stop condition on SDAx and SCLx pins; automatically cleared by hardware

0 = Stop condition is Idle

bit 1 RSEN: Repeated Start Condition Enable bit (Master mode only)(2)

1 = Initiates Repeated Start condition on SDAx and SCLx pins; automatically cleared by hardware

0 = Repeated Start condition is Idle

bit 0 SEN: Start Condition Enable bit<sup>(2)</sup>

Master Mode:

1 = Initiates Start condition on SDAx and SCLx pins; automatically cleared by hardware

0 = Start condition is Idle

Slave Mode:

1 = Clock stretching is enabled for both slave transmit and slave receive (stretch is enabled)

0 = Clock stretching is disabled

**Note 1:** The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

2: If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

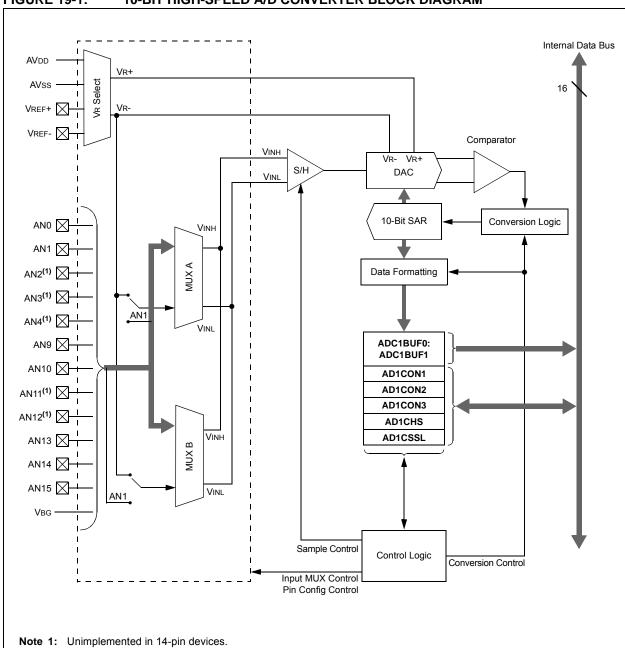

FIGURE 19-1: 10-BIT HIGH-SPEED A/D CONVERTER BLOCK DIAGRAM

#### **HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER** REGISTER 22-1:

| R/W-0  | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| HLVDEN | _   | HLSIDL | _   | _   | _   | _   | _     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-----|--------|--------|--------|--------|

| VDIR  | BGVST | IRVST | _   | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 |

| bit 7 |       |       |     |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown

bit 15 HLVDEN: High/Low-Voltage Detect Power Enable bit

> 1 = HLVD is enabled 0 = HLVD is disabled

bit 14 Unimplemented: Read as '0'

bit 13 HLSIDL: HLVD Stop in Idle Mode bit

1 = Discontinues module operation when the device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7 VDIR: Voltage Change Direction Select bit

1 = Event occurs when the voltage equals or exceeds the trip point (HLVDL<3:0>)

0 = Event occurs when the voltage equals or falls below the trip point (HLVDL<3:0>)

bit 6 **BGVST:** Band Gap Voltage Stable Flag bit

1 = Indicates that the band gap voltage is stable

0 = Indicates that the band gap voltage is unstable

bit 5 **IRVST:** Internal Reference Voltage Stable Flag bit

1 = Indicates that the internal reference voltage is stable and the High-Voltage Detect logic generates

the interrupt flag at the specified voltage range

0 = Indicates that the internal reference voltage is unstable and the High-Voltage Detect logic will not generate the interrupt flag at the specified voltage range, and the HLVD interrupt should not be

enabled

bit 4 Unimplemented: Read as '0'

bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits

1111 = External analog input is used (input comes from the HLVDIN pin)

1110 = Trip Point 14<sup>(1)</sup>

1101 = Trip Point 13<sup>(1)</sup>

1100 = Trip Point 12<sup>(1)</sup>

0000 = Trip Point 0<sup>(1)</sup>

Note 1: For the actual trip point, see Section 26.0 "Electrical Characteristics".

### 25.0 INSTRUCTION SET SUMMARY

Note:

This chapter is a brief summary of the PIC24F Instruction Set Architecture (ISA) and is not intended to be a comprehensive reference source.

The PIC24F instruction set adds many enhancements to the previous PIC® MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- · Control operations

Table 25-1 lists the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 25-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value, 'f'

- The destination, which could either be the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register, 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the Table Read and Table Write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all of the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all Table Reads and Table Writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

TABLE 26-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)(2)

| DC CHARACTERISTICS | DC CHARACTERISTICS     |       |       |      | Standard Operating Conditions: 1.8V to 3.6V Operating temperature -40°C $\leq$ TA $\leq$ +85°C for Industrial -40°C $\leq$ TA $\leq$ +125°C for Extended |                   |  |  |  |  |

|--------------------|------------------------|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|

| Parameter No.      | Typical <sup>(1)</sup> | Max   | Units |      |                                                                                                                                                          | Conditions        |  |  |  |  |

| IDD Current        |                        |       |       |      |                                                                                                                                                          |                   |  |  |  |  |

| DC20               | 0.154                  | 0.350 | mA    | 1.8V | +85V°C                                                                                                                                                   |                   |  |  |  |  |

|                    | 0.301                  | 0.630 | IIIA  | 3.3V | +65V C                                                                                                                                                   | 0.5 MIPS,         |  |  |  |  |

|                    | _                      | .500  | mA    | 1.8V | +125°C                                                                                                                                                   | Fosc = 1 MHz      |  |  |  |  |

|                    | _                      | .800  | IIIA  | 3.3V | +125 C                                                                                                                                                   |                   |  |  |  |  |

| DC22               | 0.300                  | _     | mA    | 1.8V | +85°C                                                                                                                                                    | 1 MIPS,           |  |  |  |  |

|                    | 0.585                  | _     | IIIA  | 3.3V | +65 C                                                                                                                                                    | Fosc = 2 MHz      |  |  |  |  |

| DC24               | 7.76                   | 12.0  | mA    | 3.3V | +85°C                                                                                                                                                    | 16 MIPS,          |  |  |  |  |

|                    | _                      | 18.0  | IIIA  | 3.3V | +125°C                                                                                                                                                   | Fosc = 32 MHz     |  |  |  |  |

| DC26               | 1.44                   | _     | mA    | 1.8V | +85°C                                                                                                                                                    | FRC (4 MIPS),     |  |  |  |  |

|                    | 2.71                   | _     | IIIA  | 3.3V | +65 C                                                                                                                                                    | Fosc = 8 MHz      |  |  |  |  |

| DC30               | 4.00                   | 28.0  |       | 1.8V | +85°C                                                                                                                                                    |                   |  |  |  |  |

|                    | 9.00                   | 55.0  | μA    | 3.3V | +05 C                                                                                                                                                    | LPRC (15.5 KIPS), |  |  |  |  |

|                    | _                      | 45.0  |       | 1.8V | +125°C                                                                                                                                                   | Fosc = 31 kHz     |  |  |  |  |

|                    |                        | 90.0  | μA    | 3.3V | 1125 C                                                                                                                                                   |                   |  |  |  |  |

**Note 1:** Data in the Typical column is at 3.3V, +25°C, unless otherwise stated.

TABLE 26-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)(2)

| DC CHARACTERISTI     | cs                     |       | Standard Operating Conditions: 1.8V to 3.6V Operating temperature -40°C $\leq$ TA $\leq$ +85°C for Industrial -40°C $\leq$ TA $\leq$ +125°C for Extended |      |        |                   |  |  |  |  |  |  |

|----------------------|------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|-------------------|--|--|--|--|--|--|

| Parameter No.        | Typical <sup>(1)</sup> | Max   | Units                                                                                                                                                    |      |        | Conditions        |  |  |  |  |  |  |

| Idle Current (IIDLE) | Idle Current (IIDLE)   |       |                                                                                                                                                          |      |        |                   |  |  |  |  |  |  |

| DC40                 | 0.035                  | 0.080 | - mA                                                                                                                                                     | 1.8V | +85°C  |                   |  |  |  |  |  |  |

|                      | 0.077                  | 0.150 | IIIA                                                                                                                                                     | 3.3V | +65 C  | 0.5 MIPS,         |  |  |  |  |  |  |

|                      | _                      | 0.160 | A                                                                                                                                                        | 1.8V | 1405°C | Fosc = 1 MHz      |  |  |  |  |  |  |

|                      | _                      | 0.300 | mA                                                                                                                                                       | 3.3V | +125°C |                   |  |  |  |  |  |  |

| DC42                 | 0.076                  | _     | m A                                                                                                                                                      | 1.8V | 10E°C  | 1 MIPS,           |  |  |  |  |  |  |

|                      | 0.146                  | _     | - mA                                                                                                                                                     | 3.3V | +85°C  | Fosc = 2 MHz      |  |  |  |  |  |  |

| DC44                 | 2.52                   | 3.20  | mA                                                                                                                                                       | 3.3V | +85°C  | 16 MIPS,          |  |  |  |  |  |  |

|                      | _                      | 5.00  | mA                                                                                                                                                       | 3.3V | +125°C | Fosc = 32 MHz     |  |  |  |  |  |  |

| DC46                 | 0.45                   | _     | mA                                                                                                                                                       | 1.8V | +85°C  | FRC (4 MIPS),     |  |  |  |  |  |  |

|                      | 0.76                   | _     | mA                                                                                                                                                       | 3.3V | +65 C  | Fosc = 8 MHz      |  |  |  |  |  |  |

| DC50                 | 0.87                   | 18.0  | μA                                                                                                                                                       | 1.8V | 10E°C  |                   |  |  |  |  |  |  |

|                      | 1.55                   | 40.0  | μΑ                                                                                                                                                       | 3.3V | +85°C  | LPRC (15.5 KIPS), |  |  |  |  |  |  |

|                      | _                      | 27.0  | μA                                                                                                                                                       | 1.8V | +125°C | Fosc = 31 kHz     |  |  |  |  |  |  |

|                      | _                      | 50.0  | μA                                                                                                                                                       | 3.3V | +125 C |                   |  |  |  |  |  |  |

**Note 1:** Data in the Typical column is at 3.3V, +25°C, unless otherwise stated.

<sup>2:</sup> IDD is measured with all peripherals disabled. All I/Os are configured as outputs and set low; PMDx bits are set to '1' and WDT, etc., are all disabled.

<sup>2:</sup> IIDLE is measured with all I/Os configured as outputs and set low; PMDx bits are set to '1' and WDT, etc., are all disabled.

TABLE 26-11: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |     |                     |     | r <b>d Opera</b><br>ng tempe | _   | -40°C ≤ | ditions: 1.8V to 3.6V $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |            |  |  |

|--------------------|-----|---------------------|-----|------------------------------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Param<br>No.       | Sym | Characteristic      | Min | Typ <sup>(1)</sup>           | Max | Units   | Conditions                                                                                                                                                                 |            |  |  |

|                    | Vol | Output Low Voltage  |     |                              |     |         |                                                                                                                                                                            |            |  |  |

| DO10               |     | All I/O Pins        | _   | _                            | 0.4 | V       | IOL = 4.0 mA                                                                                                                                                               | VDD = 3.6V |  |  |

|                    |     |                     | _   | _                            | 0.4 | V       | IOL = 3.5 mA                                                                                                                                                               | VDD = 2.0V |  |  |

| DO16               |     | OSC2/CLKO           | _   | _                            | 0.4 | V       | IOL = 1.2 mA                                                                                                                                                               | VDD = 3.6V |  |  |

|                    |     |                     | _   | _                            | 0.4 | V       | IOL = 0.4 mA                                                                                                                                                               | VDD = 2.0V |  |  |

|                    | Vон | Output High Voltage |     |                              |     |         |                                                                                                                                                                            |            |  |  |

| DO20               |     | All I/O Pins        | 3   | _                            | _   | V       | IOH = -3.0 mA                                                                                                                                                              | VDD = 3.6V |  |  |

|                    |     |                     | 1.6 | _                            | _   | V       | Iон = -1.0 mA                                                                                                                                                              | VDD = 2.0V |  |  |

| DO26               |     | OSC2/CLKO           | 3   | _                            | _   | V       | Iон = -1.0 mA                                                                                                                                                              | VDD = 3.6V |  |  |

|                    |     |                     | 1.6 | _                            | _   | V       | IOH = -0.5 mA                                                                                                                                                              | VDD = 2.0V |  |  |

**Note 1:** Data in "Typ" column is at +25°C unless otherwise stated.

TABLE 26-12: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |       |                                   | Standard Operating Conditions: 1.8V to 3.6V<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |    |     |            |                                               |

|--------------------|-------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|------------|-----------------------------------------------|

| Param<br>No.       | Sym   | Characteristic                    | Min Typ <sup>(1)</sup> Max Units Condition                                                                                                                                                                                |    |     | Conditions |                                               |

|                    |       | Program Flash Memory              |                                                                                                                                                                                                                           |    |     |            |                                               |

| D130               | ЕР    | Cell Endurance                    | 10,000 <sup>(2)</sup>                                                                                                                                                                                                     | _  | _   | E/W        |                                               |

| D131               | VPR   | VDD for Read                      | VMIN                                                                                                                                                                                                                      | _  | 3.6 | V          | VMIN = Minimum operating voltage              |

| D133A              | Tıw   | Self-Timed Write Cycle<br>Time    | _                                                                                                                                                                                                                         | 2  | _   | ms         |                                               |

| D134               | TRETD | Characteristic Retention          | 40                                                                                                                                                                                                                        | _  | _   | Year       | Provided no other specifications are violated |

| D135               | IDDP  | Supply Current During Programming | _                                                                                                                                                                                                                         | 10 | _   | mA         |                                               |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: Self-write and block erase.

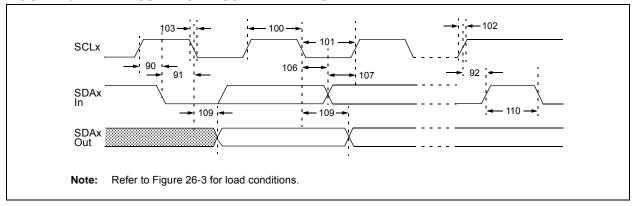

FIGURE 26-14: MSSPx I<sup>2</sup>C™ BUS DATA TIMING

TABLE 26-34: I<sup>2</sup>C™ BUS DATA REQUIREMENTS (MASTER MODE)

| Param.<br>No. | Symbol  | Characteristic                |              | Min              | Max  | Units | Conditions                                |  |

|---------------|---------|-------------------------------|--------------|------------------|------|-------|-------------------------------------------|--|

| 100           | THIGH   | Clock High Time               | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

|               |         |                               | 400 kHz mode | 2(Tosc)(BRG + 1) | _    |       |                                           |  |

| 101           | TLOW    | Clock Low Time                | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

|               |         |                               | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

| 102           | TR      | SDAx and SCLx<br>Rise Time    | 100 kHz mode | _                | 1000 | ns    | CB is specified to be from 10 to 400 pF   |  |

|               |         |                               | 400 kHz mode | 20 + 0.1 CB      | 300  | ns    |                                           |  |

| 103           | TF      | SDAx and SCLx<br>Fall Time    | 100 kHz mode | _                | 300  | ns    | CB is specified to be from 10 to 400 pF   |  |

|               |         |                               | 400 kHz mode | 20 + 0.1 CB      | 300  | ns    |                                           |  |

| 90            | Tsu:sta | Start Condition<br>Setup Time | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     | Only relevant for Repeate Start condition |  |

|               |         |                               | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

| 91            | THD:STA | Start Condition<br>Hold Time  | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     | After this period, the first              |  |

|               |         |                               | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     | clock pulse is generated                  |  |

| 106           | THD:DAT | Data Input<br>Hold Time       | 100 kHz mode | 0                | _    | ns    |                                           |  |

|               |         |                               | 400 kHz mode | 0                | 0.9  | μS    |                                           |  |

| 107           | Tsu:dat | Data Input<br>Setup Time      | 100 kHz mode | 250              | _    | ns    | (Note 1)                                  |  |

|               |         |                               | 400 kHz mode | 100              | _    | ns    |                                           |  |

| 92            | Tsu:sto | Stop Condition<br>Setup Time  | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

|               |         |                               | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

| 109           | Таа     | Output Valid from Clock       | 100 kHz mode |                  | 3500 | ns    |                                           |  |

|               |         |                               | 400 kHz mode | _                | 1000 | ns    |                                           |  |

| 110           | TBUF    | Bus Free Time                 | 100 kHz mode | 4.7              | _    | μS    | Time the bus must be free                 |  |

|               |         |                               | 400 kHz mode | 1.3              |      | μS    | before a new transmission can start       |  |

| D102          | Св      | Bus Capacitive Loading        |              |                  | 400  | pF    |                                           |  |

Note 1: A Fast mode I²C bus device can be used in a Standard mode I²C bus system, but Parameter 107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCLx signal. If such a device does stretch the LOW period of the SCLx signal, it must output the next data bit to the SDAx line, Parameter 102 + Parameter 107 = 1000 + 250 = 1250 ns (for 100 kHz mode), before the SCLx line is released.

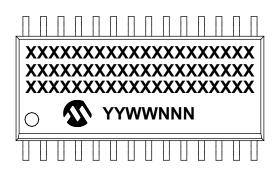

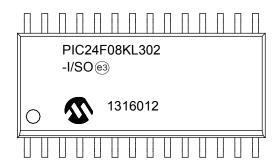

20-Lead SOIC (7.50 mm)

Example

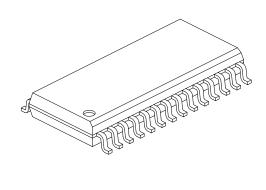

28-Lead SOIC (7.50 mm)

Example

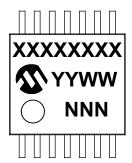

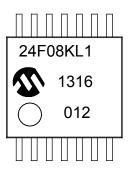

14-Lead TSSOP (4.4 mm)

Example

20-Lead SSOP (5.30 mm)

Example

### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2

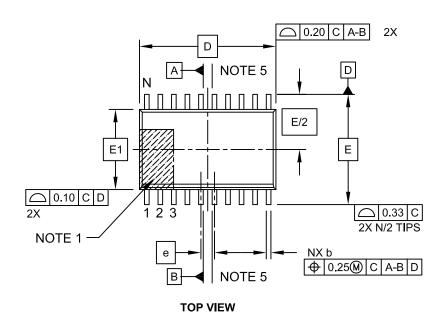

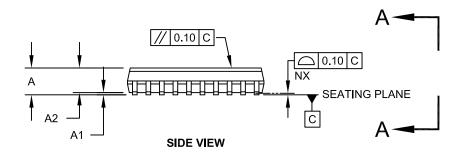

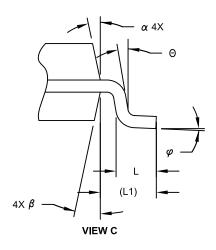

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |

|--------------------------|-------------|-----------|-----|------|--|

| Dimensior                | Limits      | MIN       | NOM | MAX  |  |

| Number of Pins           | N           | 28        |     |      |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |

| Overall Height           | Α           | -         | -   | 2.65 |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |

| Overall Width            | Е           | 10.30 BSC |     |      |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |

| Overall Length           | D           | 17.90 BSC |     |      |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |

| Foot Length              | L           | 0.40      | -   | 1.27 |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |

| Foot Angle               | φ           | 0°        | -   | 8°   |  |

| Lead Thickness           | С           | 0.18      | -   | 0.33 |  |

| Lead Width               | b           | 0.31      | -   | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -   | 15°  |  |

#### Notes

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

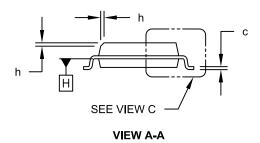

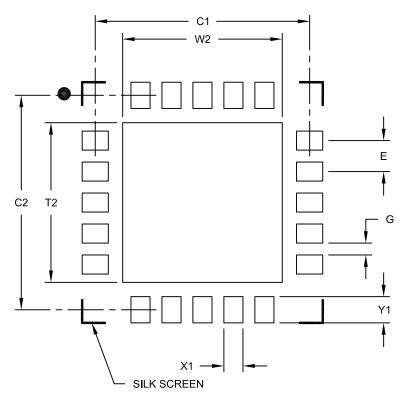

20-Lead Plastic Quad Flat, No Lead Package (MQ) - 5x5 mm Body [QFN] With 0.40mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimension Limits           |             | MIN      | NOM  | MAX  |

| Contact Pitch              | Е           | 0.65 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 3.35 |

| Optional Center Pad Length | T2          |          |      | 3.35 |

| Contact Pad Spacing        | C1          |          | 4.50 |      |

| Contact Pad Spacing        | C2          |          | 4.50 |      |

| Contact Pad Width (X20)    | X1          |          |      | 0.40 |

| Contact Pad Length (X20)   | Y1          |          |      | 0.55 |

| Distance Between Pads      | G           | 0.20     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2139A