#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08kl402t-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

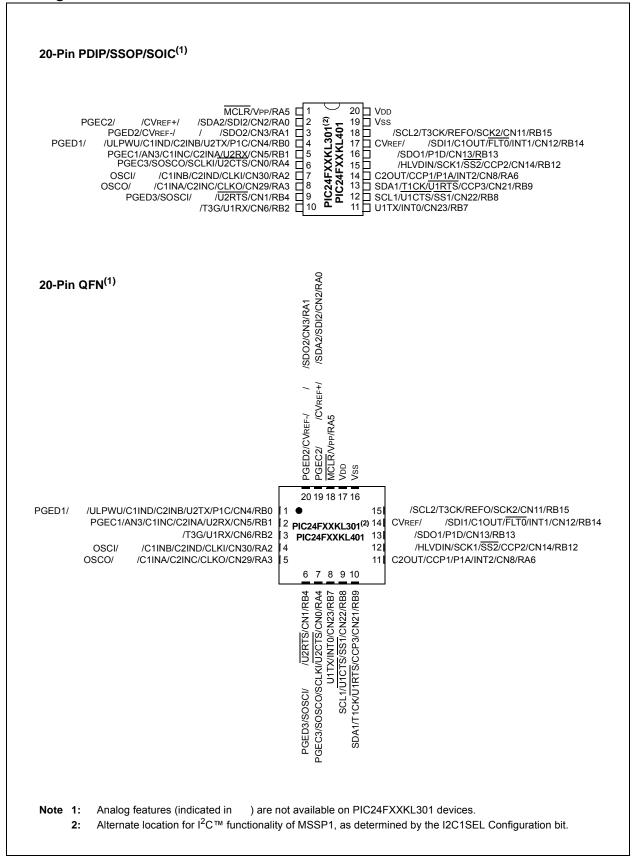

#### Pin Diagrams: PIC24FXXKL301/401

#### 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

#### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic shift right source register by one or more bits. |

| SL          | Shift left source register by one or more bits.             |

| LSR         | Logical shift right source register by one or more bits.    |

### 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and bussing. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 **Program Address Space**

The program address memory space of the PIC24F16KL402 family is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24F16KL402 family of devices are shown in Figure 4-1.

### FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24F16KL402 FAMILY DEVICES

|                            | PIC24F04KLXXX                                                                                                                                       | PIC24F08KL2XX                                                                                              | PIC24F08KL3XX                                                                                              |       | PIC24F08KL4XX                                                                                              | PIC24F16KLXXX                                                                                     |                                                                                    |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                            | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash<br>Program Memory<br>(1408 instructions) | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash |       | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table | 000000h<br>00002h<br>00004h<br>0000FEh<br>000100h<br>000104h<br>0001FEh<br>000200h |

| User Memory Space          |                                                                                                                                                     | Program Memory<br>(2816 instructions)                                                                      | <br>Program Memory<br>(2816 instructions)                                                                  | -     | Program Memory<br>(2816 instructions)                                                                      | <br>Flash<br>Program Memory<br>(5632 instructions)                                                | - 000AFEh                                                                          |

| User Me                    | Unimplemented<br>Read '0'                                                                                                                           | Unimplemented<br>Read '0'                                                                                  | Unimplemented<br>Read '0'                                                                                  |       | Unimplemented<br>Read '0'                                                                                  | Unimplemented                                                                                     | 002BFEh                                                                            |

|                            |                                                                                                                                                     |                                                                                                            | <br>Data EEPROM<br>(256 bytes)                                                                             | -<br> | Data EEPROM<br>(512 bytes)                                                                                 | <br>Read '0'<br>Data EEPROM<br>(512 bytes)                                                        | <ul> <li>7FFE00h</li> <li>7FFF00h</li> <li>7FFFFFh</li> <li>800000h</li> </ul>     |

| Ī                          | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | 800800h                                                                            |

| ace                        | Unique ID                                                                                                                                           | Unique ID                                                                                                  | Unique ID                                                                                                  |       | Unique ID                                                                                                  | Unique ID                                                                                         | 800802h<br>800808h                                                                 |

| lory Sp                    | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | 80080Ah                                                                            |

| Mem                        | Device Config Registers                                                                                                                             | Device Config Registers                                                                                    | Device Config Registers                                                                                    |       | Device Config Registers                                                                                    | Device Config Registers                                                                           | F80000h<br>F8000Eh                                                                 |

| Configuration Memory Space | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | F80010h<br>FEFFFEh                                                                 |

|                            | DEVID (2)                                                                                                                                           | DEVID (2)                                                                                                  | DEVID (2)                                                                                                  |       | DEVID (2)                                                                                                  | DEVID (2)                                                                                         | FF0000h<br>FFFFFFh                                                                 |

Note: Memory areas are not displayed to scale.

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

|              | чυ.  |        |                      | 1 001                |                      |                     |            |                       |            |       |            |            |            |         |                       |                       |          |               |

|--------------|------|--------|----------------------|----------------------|----------------------|---------------------|------------|-----------------------|------------|-------|------------|------------|------------|---------|-----------------------|-----------------------|----------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14               | Bit 13               | Bit 12               | Bit 11              | Bit 10     | Bit 9                 | Bit 8      | Bit 7 | Bit 6      | Bit 5      | Bit 4      | Bit 3   | Bit 2                 | Bit 1                 | Bit 0    | All<br>Resets |

| INTCON1      | 0080 | NSTDIS | —                    | —                    | —                    | —                   | —          | —                     | —          | _     | —          | —          | MATHERR    | ADDRERR | STKERR                | OSCFAIL               | —        | 0000          |

| INTCON2      | 0082 | ALTIVT | DISI                 | _                    | —                    | —                   | _          | _                     | —          | _     | _          | _          | _          | _       | INT2EP                | INT1EP                | INT0EP   | 0000          |

| IFS0         | 0084 | NVMIF  | _                    | AD1IF                | U1TXIF               | U1RXIF              | _          | _                     | T3IF       | T2IF  | CCP2IF     | _          | _          | T1IF    | CCP1IF                | _                     | INT0IF   | 0000          |

| IFS1         | 0086 | U2TXIF | U2RXIF               | INT2IF               | _                    | T4IF <sup>(1)</sup> | _          | CCP3IF <sup>(1)</sup> | _          | _     | _          | _          | INT1IF     | CNIF    | CMIF                  | BCL1IF                | SSP1IF   | 0000          |

| IFS2         | 8800 |        | _                    | _                    | _                    |                     | _          | _                     | _          | _     | _          | T3GIF      | _          | _       | _                     | _                     | _        | 0000          |

| IFS3         | 008A | —      | _                    | _                    | —                    | —                   | _          | _                     | —          | _     | _          | —          | _          | _       | BCL2IF <sup>(1)</sup> | SSP2IF <sup>(1)</sup> | —        | 0000          |

| IFS4         | 008C | —      | _                    | _                    | —                    | _                   | _          | _                     | HLVDIF     | _     | _          | _          | _          | _       | U2ERIF                | U1ERIF                | _        | 0000          |

| IFS5         | 008E | —      | _                    | _                    | —                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | _                     | _                     | ULPWUIF  | 0000          |

| IEC0         | 0094 | NVMIE  | _                    | AD1IE                | U1TXIE               | U1RXIE              | _          | _                     | T3IE       | T2IE  | CCP2IE     | _          | _          | T1IE    | CCP1IE                | _                     | INT0IE   | 0000          |

| IEC1         | 0096 | U2TXIE | U2RXIE               | INT2IE               | —                    | T4IE <sup>(1)</sup> | _          | CCP3IE <sup>(1)</sup> | _          | _     | _          | _          | INT1IE     | CNIE    | CMIE                  | BCL1IE                | SSP1IE   | 0000          |

| IEC2         | 0098 | _      | _                    | -                    | —                    | _                   | _          | _                     | _          |       | _          | T3GIE      | _          | _       | _                     | _                     | -        | 0000          |

| IEC3         | 009A | _      | _                    |                      | —                    | _                   | _          | _                     | _          |       | _          | _          | -          | _       | BCL2IE <sup>(1)</sup> | SSP2IE <sup>(1)</sup> |          | 0000          |

| IEC4         | 009C | _      | _                    |                      | —                    | _                   | _          | _                     | HLVDIE     |       | _          | _          | -          | _       | U2ERIE                | U1ERIE                |          | 0000          |

| IEC5         | 009E | _      | _                    |                      | —                    | _                   | _          | _                     | _          |       | _          | _          | -          | _       | _                     | _                     | ULPWUIE  | 0000          |

| IPC0         | 00A4 | —      | T1IP2                | T1IP1                | T1IP0                | _                   | CCP1IP2    | CCP1IP1               | CCP1IP0    | _     | _          | _          | _          | _       | INT0IP2               | INT0IP1               | INT0IP0  | 4404          |

| IPC1         | 00A6 | _      | T2IP2                | T2IP1                | T2IP0                | _                   | CCP2IP2    | CCP2IP1               | CCP2IP0    |       | _          | _          | -          | _       | _                     | _                     | -        | 4400          |

| IPC2         | 00A8 | _      | U1RXIP2              | U1RXIP1              | U1RXIP0              | _                   | _          | _                     | _          |       | _          | _          | -          | _       | T3IP2                 | T3IP1                 | T3IP0    | 4004          |

| IPC3         | 00AA | _      | NVMIP2               | NVMIP1               | NVMIP0               | _                   | _          | _                     | _          |       | AD1IP2     | AD1IP1     | AD1IP0     | _       | U1TXIP2               | U1TXIP1               | U1TXIP0  | 4044          |

| IPC4         | 00AC | _      | CNIP2                | CNIP1                | CNIP0                | _                   | CMIP2      | CMIP1                 | CMIP0      |       | BCL1IP2    | BCL1IP1    | BCL1IP0    | _       | SSP1IP2               | SSP1IP1               | SS1IP0   | 4444          |

| IPC5         | 00AE | _      | _                    | -                    | —                    | _                   | _          | _                     | _          |       | _          | _          | _          | _       | INT1IP2               | INT1IP1               | INT1IP0  | 0004          |

| IPC6         | 00B0 | _      | T4IP2 <sup>(1)</sup> | T4IP1 <sup>(1)</sup> | T4IP0 <sup>(1)</sup> | _                   | _          | _                     | _          |       | CCP3IP2(1) | CCP3IP1(1) | CCP3IP0(1) | _       | —                     | —                     |          | 4040          |

| IPC7         | 00B2 | _      | U2TXIP2              | U2TXIP1              | U2TXIP0              | _                   | U2RXIP2    | U2RXIP1               | U2RXIP0    |       | INT2IP2    | INT2IP1    | INT2IP0    | _       | _                     | _                     |          | 4440          |

| IPC9         | 00B6 | _      | _                    | -                    | —                    | _                   | _          | —                     | _          |       | T3GIP2     | T3GIP1     | T3GIP0     | _       | _                     | _                     |          | 0040          |

| IPC12        | 00BC | _      | _                    | _                    | —                    | _                   | BCL2IP2(1) | BCL2IP1(1)            | BCL2IP0(1) |       | SSP2IP2(1) | SSP2IP1(1) | SSP2IP0(1) | _       | _                     | _                     |          | 0440          |

| IPC16        | 00C4 | _      | _                    | _                    | _                    | _                   | U2ERIP2    | U2ERIP1               | U2ERIP0    | _     | U1ERIP2    | U1ERIP1    | U1ERIP0    | _       | _                     | —                     | _        | 0440          |

| IPC18        | 00C8 | _      | _                    | _                    | _                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | HLVDIP2               | HLVDIP1               | HLVDIP0  | 0004          |

| IPC20        | 00CC | _      | _                    | _                    | _                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | ULPWUIP2              | ULPWUIP1              | ULPWUIP0 | 0004          |

| INTTREG      | 00E0 | CPUIRQ | r                    | VHOLD                | _                    | ILR3                | ILR2       | ILR1                  | ILR0       | _     | VECNUM6    | VECNUM5    | VECNUM4    | VECNUM3 | VECNUM2               | VECNUM1               | VECNUM0  | 0000          |

Legend: Note 1:

Legend: — = unimplemented, read as '0', r = reserved. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

| TABLE 4-6               | : т  | IMER   | REGIS  | TER N  | IAP    |        |        |        |        |                        |                        |          |              |                  |        |         |         |               |

|-------------------------|------|--------|--------|--------|--------|--------|--------|--------|--------|------------------------|------------------------|----------|--------------|------------------|--------|---------|---------|---------------|

| File Name               | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7                  | Bit 6                  | Bit 5    | Bit 4        | Bit 3            | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

| TMR1                    | 0100 |        |        |        |        |        |        |        |        | Timer1 Reg             | gister                 |          |              |                  |        |         |         | 0000          |

| PR1                     | 0102 |        |        |        |        |        |        |        | Tir    | mer1 Period            | er1 Period Register    |          |              |                  |        | FFFF    |         |               |

| T1CON                   | 0104 | TON    | _      | TSIDL  | _      | _      | _      | T1ECS1 | T1ECS0 | _                      | TGATE                  | TCKPS1   | TCKPS0       | _                | TSYNC  | TCS     | _       | 0000          |

| TMR2                    | 0106 | _      | _      | _      | _      | _      | _      | _      | _      |                        |                        |          | Timer2 R     | egister          |        |         |         | 0000          |

| PR2                     | 0108 | _      | _      | _      | _      | _      | _      | _      | _      | Timer2 Period Register |                        |          |              |                  | OOFF   |         |         |               |

| T2CON                   | 010A | _      | _      | _      | _      | _      | _      | _      | _      | _                      | T2OUTPS3               | T2OUTPS2 | T2OUTPS1     | T2OUTPS0         | TMR2ON | T2CKPS1 | T2CKPS0 | 0000          |

| TMR3                    | 010C |        |        |        |        |        |        |        |        | Timer3 Reg             | gister                 |          |              |                  |        |         |         | 0000          |

| T3GCON                  | 010E | -      | —      | —      | —      | —      | —      | —      | —      | TMR3GE                 | T3GPOL                 | T3GTM    | T3GSPM       | T3GGO/<br>T3DONE | T3GVAL | T3GSS1  | T3GSS0  | 0000          |

| T3CON                   | 0110 | _      | _      | _      | _      | _      | _      | _      | _      | TMR3CS1                | TMR3CS0                | T3CKPS1  | T3CKPS0      | T3OSCEN          | T3SYNC | _       | TMR3ON  | 0000          |

| TMR4 <sup>(1)</sup>     | 0112 | _      | _      | _      | _      | _      | —      | _      | _      |                        | •                      | •        | Timer4 R     | egister          |        |         |         | 0000          |

| PR4 <sup>(1)</sup>      | 0114 | _      | _      | _      | _      | _      | —      | —      | _      |                        |                        |          | Timer4 Perio | d Register       |        |         |         | 00FF          |

| T4CON <sup>(1)</sup>    | 0116 | _      | _      | _      | _      | _      | —      | —      | _      | _                      | T4OUTPS3               | T4OUTPS2 | T4OUTPS1     | T4OUTPS0         | TMR40N | T4CKPS1 | T4CKPS0 | 0000          |

| CCPTMRS0 <sup>(1)</sup> | 013C | -      | _      | _      | _      | —      | _      | —      | _      | _                      | C3TSEL0 <sup>(1)</sup> | _        | -            | C2TSEL0          | -      | _       | C1TSEL0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

#### TABLE 4-7: CCP/ECCP REGISTER MAP

|                         |      |        | -      |        |        |        |        |       |       | 1                                         |                    |            |            |              |           |        |        |               |

|-------------------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------------------------------------------|--------------------|------------|------------|--------------|-----------|--------|--------|---------------|

| File Name               | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                     | Bit 6              | Bit 5      | Bit 4      | Bit 3        | Bit 2     | Bit 1  | Bit 0  | All<br>Resets |

| CCP1CON                 | 0190 | _      | _      | —      | _      | _      | —      | —     | —     | PM1 <sup>(1)</sup>                        | PM0 <sup>(1)</sup> | DC1B1      | DC1B0      | CCP1M3       | CCP1M2    | CCP1M1 | CCP1M0 | 0000          |

| CCPR1L                  | 0192 | -      | _      | _      | _      | _      | _      | _     | _     |                                           |                    | Capture/Co | ompare/PWN | V1 Register  | Low Byte  |        |        | 0000          |

| CCPR1H                  | 0194 | -      | _      | _      | _      | _      | _      | _     | _     | Capture/Compare/PWM1 Register High Byte   |                    |            |            |              | 0000      |        |        |               |

| ECCP1DEL <sup>(1)</sup> | 0196 | -      | _      | _      | _      | _      | _      | _     | _     | PRSEN                                     | PDC6               | PDC5       | PDC4       | PDC3         | PDC2      | PDC1   | PDC0   | 0000          |

| ECCP1AS <sup>(1)</sup>  | 0198 | -      | _      | _      | _      | _      | _      | _     | _     | ECCPASE                                   | ECCPAS2            | ECCPAS1    | ECCPAS0    | PSSAC1       | PSSAC0    | PSSBD1 | PSSBD0 | 0000          |

| PSTR1CON(1)             | 019A | _      | _      | _      | _      | _      | _      | _     | _     | CMPL1                                     | CMPL0              | —          | STRSYNC    | STRD         | STRC      | STRB   | STRA   | 0001          |

| CCP2CON                 | 019C | _      | _      | _      | _      | _      | _      | _     | _     | _                                         | _                  | DC2B1      | DC2B0      | CCP2M3       | CCP2M2    | CCP2M1 | CCP2M0 | 0000          |

| CCPR2L                  | 019E | _      | _      | _      | _      | _      | _      | _     | _     |                                           |                    | Capture/Co | ompare/PWN | M2 Register  | Low Byte  |        |        | 0000          |

| CCPR2H                  | 01A0 | _      | _      | _      | _      | _      | _      | _     | _     | Capture/Compare/PWM2 Register High Byte 0 |                    |            |            |              | 0000      |        |        |               |

| CCP3CON <sup>(1)</sup>  | 01A8 | _      | _      | _      | _      | _      | _      | _     | _     | _                                         | _                  | DC3B1      | DC3B0      | CCP3M3       | CCP3M2    | CCP3M1 | CCP3M0 | 0000          |

| CCPR3L <sup>(1)</sup>   | 01AA | _      | _      | _      | _      | _      | _      | _     | _     | Capture/Compare/PWM3 Register Low Byte 0  |                    |            |            |              | 0000      |        |        |               |

| CCPR3H <sup>(1)</sup>   | 01AC | _      |        | _      | _      | _      | —      | —     | _     |                                           |                    | Capture/Co | ompare/PWN | /13 Register | High Byte |        |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

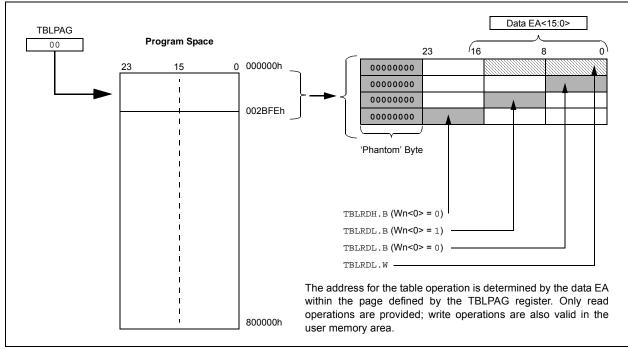

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through data space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

| Note: | The TBLRDH and TBLWTH instructions are |

|-------|----------------------------------------|

|       | not used while accessing data EEPROM   |

|       | memory.                                |

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when the byte select is '1'; the lower byte is selected when it is '0'.

TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

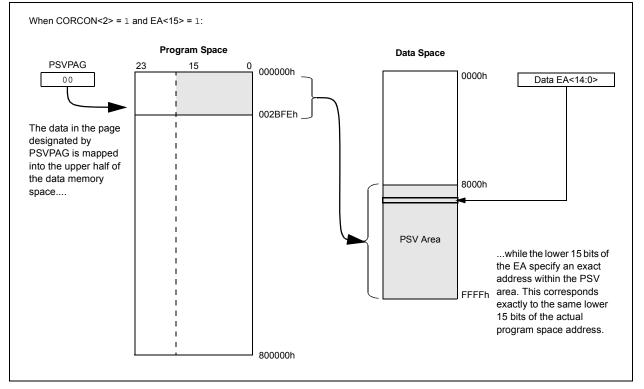

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into a 16K word page of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the MSb of the data space EA is '1' and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address (PSVPAG) register. This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location, used as data, should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

### Note: PSV access is temporarily disabled during Table Reads/Writes.

For operations that use PSV and are executed outside of a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle, in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles, in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

#### FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

### 6.0 DATA EEPROM MEMORY

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information on Data       |

|       | EEPROM, refer to the "dsPIC33/PIC24        |

|       | Family Reference Manual", "Data            |

|       | EEPROM" (DS39720).                         |

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFFFh. For PIC24FXXKL4XX devices, the size of the data EEPROM is 256 words (7FFE00h to 7FFFFh). For PIC24FXXKL3XX devices, the size of the data EEPROM is 128 words (7FFF0h to 7FFFFh). The data EEPROM is not implemented in PIC24F08KL20X or PIC24F04KL10X devices.

The data EEPROM is organized as 16-bit wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

#### 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle, and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

#### 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

| //Disable Interrupts For 5 instr | uctions |

|----------------------------------|---------|

| asm volatile("disi #5");         |         |

| //Issue Unlock Sequence          |         |

| asm volatile ("mov #0x55, W0     | \n"     |

| "mov W0, NVMKEY                  | \n"     |

| "mov #0xAA, W1                   | \n"     |

| "mov W1, NVMKEY                  | \n");   |

| // Perform Write/Erase operation | S       |

| asm volatile ("bset NVMCON, #WR  | \n"     |

| "nop                             | \n"     |

| "nop                             | \n");   |

#### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

|                       | R/W-0                 | R/W-0                            | U-0              | R/W-0                     | U-0               | R/W-0                 | U-0    |

|-----------------------|-----------------------|----------------------------------|------------------|---------------------------|-------------------|-----------------------|--------|

| U2TXIF <sup>(1)</sup> | U2RXIF <sup>(1)</sup> | INT2IF                           |                  | T4IF <sup>(1)</sup>       |                   | CCP3IF <sup>(1)</sup> | _      |

| bit 15                |                       |                                  |                  |                           |                   |                       | bit 8  |

|                       |                       |                                  |                  |                           |                   |                       |        |

| U-0                   | U-0                   | U-0                              | R/W-0            | R/W-0                     | R/W-0             | R/W-0                 | R/W-0  |

| —                     | —                     | —                                | INT1IF           | CNIF                      | CMIF              | BCL1IF                | SSP1IF |

| bit 7                 |                       |                                  |                  |                           |                   |                       | bit (  |

|                       |                       |                                  |                  |                           |                   |                       |        |

| Legend:               |                       |                                  |                  |                           |                   |                       |        |

| R = Readable          |                       | W = Writable                     |                  | •                         | nented bit, rea   |                       |        |

| -n = Value at F       | POR                   | '1' = Bit is set                 |                  | '0' = Bit is clea         | ared              | x = Bit is unkno      | own    |

|                       |                       |                                  |                  | - (1)                     |                   |                       |        |

| bit 15                |                       | T2 Transmitter                   |                  | Status bit <sup>(1)</sup> |                   |                       |        |

|                       |                       | equest has occ                   |                  |                           |                   |                       |        |

| L:1 4 4               |                       | equest has not                   |                  |                           |                   |                       |        |

| bit 14                |                       | RT2 Receiver Ir                  |                  | atus bit                  |                   |                       |        |

|                       |                       | equest has occ<br>equest has not |                  |                           |                   |                       |        |

| bit 13                | •                     | nal Interrupt 2                  |                  |                           |                   |                       |        |

| bit 10                |                       | equest has occ                   | -                |                           |                   |                       |        |

|                       |                       | equest has not                   |                  |                           |                   |                       |        |

| bit 12                | -                     | ted: Read as '                   |                  |                           |                   |                       |        |

| bit 11                | -                     | Interrupt Flag S                 |                  |                           |                   |                       |        |

|                       | 1 = Interrupt r       | equest has occ                   | curred           |                           |                   |                       |        |

|                       | 0 = Interrupt r       | equest has not                   | occurred         |                           |                   |                       |        |

| bit 10                | Unimplement           | ted: Read as '                   | כי               |                           |                   |                       |        |

| bit 9                 | CCP3IF: Capt          | ture/Compare/I                   | PWM3 Interrup    | ot Flag Status b          | it <sup>(1)</sup> |                       |        |

|                       |                       | equest has occ                   |                  |                           |                   |                       |        |

|                       | -                     | equest has not                   |                  |                           |                   |                       |        |

| bit 8-5               | -                     | ted: Read as '                   |                  |                           |                   |                       |        |

| bit 4                 |                       | nal Interrupt 1                  | •                |                           |                   |                       |        |

|                       |                       | equest has occ<br>equest has not |                  |                           |                   |                       |        |

| bit 3                 | •                     | hange Notifica                   |                  | lag Status bit            |                   |                       |        |

| DIT 3                 | -                     | equest has occ                   | -                | lay Status bit            |                   |                       |        |

|                       |                       | equest has oct                   |                  |                           |                   |                       |        |

| bit 2                 | -                     | arator Interrupt                 |                  |                           |                   |                       |        |

|                       |                       | equest has occ                   | -                |                           |                   |                       |        |

|                       |                       | equest has not                   |                  |                           |                   |                       |        |

| bit 1                 | BCL1IF: MSS           | SP1 I <sup>2</sup> C™ Bus        | Collision Interr | upt Flag Status           | bit               |                       |        |

|                       | 1 = Interrupt r       | equest has occ                   | curred           |                           |                   |                       |        |

|                       | -                     | equest has not                   |                  |                           |                   |                       |        |

| bit 0                 |                       | SP1 SPI/I <sup>2</sup> C Ev      |                  | ag Status bit             |                   |                       |        |

|                       |                       | equest has occ<br>equest has not |                  |                           |                   |                       |        |

|                       |                       |                                  | acourred         |                           |                   |                       |        |

#### REGISTER 8-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

#### REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

|        | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 | —      | —   | —   | —   | —   | —   | —   | —     |

|        | bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-------|-----|-----|-----|-----|-------|

| —     | —   | T3GIF | —   |     |     |     | —     |

| bit 7 |     |       |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-6 | Unimplemented: Read as '0'                            |

|----------|-------------------------------------------------------|

| bit 5    | T3GIF: Timer3 External Gate Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                    |

|          | 0 = Interrupt request has not occurred                |

|          |                                                       |

bit 4-0 Unimplemented: Read as '0'

#### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                 | U-0   |

|-------|-----|-----|-----|-----|-----------------------|-----------------------|-------|

| _     | —   | —   | —   | —   | BCL2IF <sup>(1)</sup> | SSP2IF <sup>(1)</sup> | _     |

| bit 7 |     |     |     |     |                       |                       | bit 0 |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

- bit 2 BCL2IF: MSSP2 I<sup>2</sup>C<sup>™</sup> Bus Collision Interrupt Flag Status bit<sup>(1)</sup> 1 = Interrupt request has occurred 0 = Interrupt request has not occurred bit 1 SSP2IF: MSSP2 SPI/I<sup>2</sup>C Event Interrupt Flag Status bit<sup>(1)</sup> 1 = Interrupt request has occurred 0 = Interrupt request has not occurred bit 0 Unimplemented: Bood os <sup>(0)</sup>

- bit 0 Unimplemented: Read as '0'

- Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

#### REGISTER 8-19: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0          | R/W-1                                                            | R/W-0                                                   | R/W-0            | U-0                                     | U-0   | U-0   | U-0   |  |  |  |

|--------------|------------------------------------------------------------------|---------------------------------------------------------|------------------|-----------------------------------------|-------|-------|-------|--|--|--|

| _            | U1RXIP2                                                          | U1RXIP1                                                 | U1RXIP0          |                                         | _     | _     |       |  |  |  |

| bit 15       |                                                                  |                                                         | L                |                                         | l     |       | bit 8 |  |  |  |

|              |                                                                  |                                                         |                  |                                         |       |       |       |  |  |  |

| U-0          | U-0                                                              | U-0                                                     | U-0              | U-0                                     | R/W-1 | R/W-0 | R/W-0 |  |  |  |

| _            | —                                                                | —                                                       | —                | _                                       | T3IP2 | T3IP1 | T3IP0 |  |  |  |

| bit 7        |                                                                  |                                                         | •                |                                         |       |       | bit 0 |  |  |  |

|              |                                                                  |                                                         |                  |                                         |       |       |       |  |  |  |

| Legend:      |                                                                  |                                                         |                  |                                         |       |       |       |  |  |  |

| R = Readab   | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                         |                  |                                         |       |       |       |  |  |  |

| -n = Value a | t POR                                                            | '1' = Bit is set                                        |                  | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |  |

| bit 14-12    |                                                                  | >: UART1 Rece<br>pt is Priority 7 (<br>pt is Priority 1 | •                |                                         |       |       |       |  |  |  |

|              | 000 = Interru                                                    | pt source is dis                                        |                  |                                         |       |       |       |  |  |  |

| bit 11-3     | •                                                                | ted: Read as '                                          |                  |                                         |       |       |       |  |  |  |

| bit 2-0      | T3IP<2:0>: ⊺                                                     | imer3 Interrupt                                         | Priority bits    |                                         |       |       |       |  |  |  |

|              | 111 = Interru<br>•<br>•                                          | pt is Priority 7(                                       | highest priority | interrupt)                              |       |       |       |  |  |  |

|              | •                                                                |                                                         |                  |                                         |       |       |       |  |  |  |

#### REGISTER 8-25: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0          | U-0           | U-0                 | U-0              | U-0               | U-0              | U-0             | U-0   |

|--------------|---------------|---------------------|------------------|-------------------|------------------|-----------------|-------|

| _            | —             | —                   | _                | —                 | —                | —               | —     |

| bit 15       |               |                     |                  |                   |                  |                 | bit 8 |

|              |               |                     |                  |                   |                  |                 |       |

| U-0          | R/W-1         | R/W-0               | R/W-0            | U-0               | U-0              | U-0             | U-0   |

| —            | T3GIP2        | T3GIP1              | T3GIP0           | —                 | —                | —               | —     |

| bit 7        |               |                     |                  |                   |                  |                 | bit 0 |

|              |               |                     |                  |                   |                  |                 |       |

| Legend:      |               |                     |                  |                   |                  |                 |       |

| R = Readab   | le bit        | W = Writable        | bit              | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value a | It POR        | '1' = Bit is set    |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|              |               |                     |                  |                   |                  |                 |       |

| bit 15-7     | Unimplemen    | ted: Read as 'd     | )'               |                   |                  |                 |       |

| bit 6-4      | T3GIP<2:0>:   | Timer3 Externa      | al Gate Interru  | pt Priority bits  |                  |                 |       |

|              | 111 = Interru | pt is Priority 7 (I | highest priority | y interrupt)      |                  |                 |       |

|              | •             |                     |                  |                   |                  |                 |       |

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

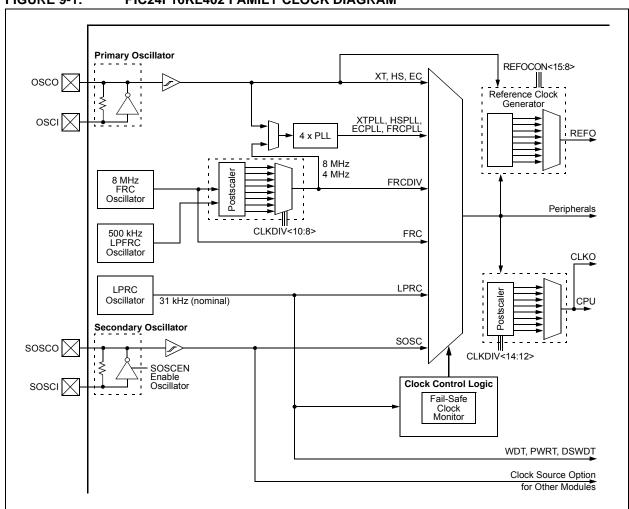

### 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Oscillator Configuration, refer to the "dsPIC33/PIC24 Family Reference Manual", "Oscillator with 500 kHz Low-Power FRC" (DS39726).

The oscillator system for the PIC24F16KL402 family of devices has the following features:

- A total of five external and internal oscillator options as clock sources, providing 11 different clock modes.

- On-chip, 4x Phase Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources.

- Software-controllable switching between various clock sources.

- Software-controllable postscaler for selective clocking of CPU for system power savings.

- System frequency range declaration bits for EC mode. When using an external clock source, the current consumption is reduced by setting the declaration bits to the expected frequency range.

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown.

A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: PIC24F16KL402 FAMILY CLOCK DIAGRAM

| U-0          | U-0                                                                           | U-0                           | U-0            | U-0               | U-0           | U-0             | U-0         |  |  |  |  |

|--------------|-------------------------------------------------------------------------------|-------------------------------|----------------|-------------------|---------------|-----------------|-------------|--|--|--|--|

|              | —                                                                             | —                             |                | —                 | _             | —               |             |  |  |  |  |

| bit 15       | •                                                                             |                               |                |                   |               |                 | bit         |  |  |  |  |

|              |                                                                               |                               |                |                   |               |                 |             |  |  |  |  |

| R/W-0        | R/W-0                                                                         | R-0                           | R-0            | R-0               | R-0           | R-0             | R-0         |  |  |  |  |

| SMP          | CKE <sup>(1)</sup>                                                            | D/A                           | Р              | S                 | R/W           | UA              | BF          |  |  |  |  |

| bit 7        |                                                                               |                               |                |                   |               |                 | bit         |  |  |  |  |

|              |                                                                               |                               |                |                   |               |                 |             |  |  |  |  |

| Legend:      |                                                                               |                               |                |                   |               |                 |             |  |  |  |  |

| R = Readab   |                                                                               | W = Writable                  |                | U = Unimplen      |               |                 |             |  |  |  |  |

| -n = Value a | t POR                                                                         | '1' = Bit is set              |                | '0' = Bit is clea | ared          | x = Bit is unkn | own         |  |  |  |  |

| bit 15-8     | Unimplome                                                                     | nted: Read as '               | o'             |                   |               |                 |             |  |  |  |  |

| bit 7        | -                                                                             |                               | 0              |                   |               |                 |             |  |  |  |  |

|              | SMP: Sample bit<br>SPI Master mode:                                           |                               |                |                   |               |                 |             |  |  |  |  |

|              | 1 = Input data is sampled at the end of data output time                      |                               |                |                   |               |                 |             |  |  |  |  |

|              | 0 = Input data is sampled at the middle of data output time                   |                               |                |                   |               |                 |             |  |  |  |  |

|              | <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode. |                               |                |                   |               |                 |             |  |  |  |  |

|              |                                                                               |                               |                | Slave mode.       |               |                 |             |  |  |  |  |

| bit 6        |                                                                               | ock Select bit <sup>(1)</sup> |                |                   |               |                 |             |  |  |  |  |

|              |                                                                               |                               |                | to active clock   |               |                 |             |  |  |  |  |

| bit 5        | D/A: Data/Ad                                                                  | ddress bit                    |                |                   |               |                 |             |  |  |  |  |

|              | Used in I <sup>2</sup> C <sup>⊤</sup>                                         | <sup>™</sup> mode only.       |                |                   |               |                 |             |  |  |  |  |

| bit 4        | P: Stop bit                                                                   |                               |                |                   |               |                 |             |  |  |  |  |

|              | Used in I <sup>2</sup> C r                                                    | mode only. This               | bit is cleared | when the MSSF     | x module is d | isabled; SSPEN  | is cleared. |  |  |  |  |

| bit 3        | S: Start bit                                                                  |                               |                |                   |               |                 |             |  |  |  |  |

|              | Used in I <sup>2</sup> C r                                                    | mode only.                    |                |                   |               |                 |             |  |  |  |  |

| bit 2        | R/W: Read/V                                                                   | Vrite Informatio              | n bit          |                   |               |                 |             |  |  |  |  |

|              | Used in I <sup>2</sup> C r                                                    | mode only.                    |                |                   |               |                 |             |  |  |  |  |

| bit 1        | UA: Update Address bit                                                        |                               |                |                   |               |                 |             |  |  |  |  |

|              | Used in I <sup>2</sup> C r                                                    | -                             |                |                   |               |                 |             |  |  |  |  |

| bit 0        | BF: Buffer Fi                                                                 |                               |                |                   |               |                 |             |  |  |  |  |

|              |                                                                               | is complete, SS               |                |                   |               |                 |             |  |  |  |  |

|              | 0 = Receive                                                                   | is not complete               | , SSPxBUF is   | empty             |               |                 |             |  |  |  |  |

| Note 1: ⊺    | he polarity of th                                                             | e clock state is              | set by the CK  | P bit (SSPxCON    | V1<4>).       |                 |             |  |  |  |  |

### REGISTER 17-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

#### 18.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UART:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write data byte to lower byte of UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0 and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately, because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

#### 18.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UART (as described in **Section 18.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

### 18.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UART for the desired mode.

- 2. Set UTXEN and UTXBRK sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

#### 18.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UART (as described in Section 18.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UART.

- 3. A receive interrupt will be generated when one or more data characters have been received as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

#### 18.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-to-Send (UxCTS) and Request-to-Send (UxRTS) are the two hardware-controlled pins that are associated with the UART module. These two pins allow the UART to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

### 18.7 Infrared Support

The UART module provides two types of infrared UART support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 18.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UART module is enabled; it can be used to support the IrDA codec chip.

### 18.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UART has full implementation of the IrDA encoder and decoder as part of the UART module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

| R/W-0        | U-0                                       | R/W-0                                                                                         | R/W-0                           | R/W-0                            | U-0                                 | R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup> |  |  |

|--------------|-------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------|----------------------------------|-------------------------------------|----------------------|----------------------|--|--|

| UARTEN       |                                           | USIDL                                                                                         | IREN <sup>(1)</sup>             | RTSMD                            |                                     | UEN1                 | UEN0                 |  |  |

| bit 15       |                                           |                                                                                               |                                 |                                  |                                     |                      | bit 8                |  |  |

|              |                                           |                                                                                               |                                 |                                  |                                     |                      |                      |  |  |

| R/C-0, HC    |                                           | R/W-0, HC                                                                                     | R/W-0                           | R/W-0                            | R/W-0                               | R/W-0                | R/W-0                |  |  |

| WAKE         | LPBACK                                    | ABAUD                                                                                         | RXINV                           | BRGH                             | PDSEL1                              | PDSEL0               | STSEL                |  |  |

| bit 7        |                                           |                                                                                               |                                 |                                  |                                     |                      | bit 0                |  |  |

| 1            |                                           |                                                                                               | L :4                            |                                  |                                     | L                    |                      |  |  |

| Legend:      | bla bit                                   | C = Clearable<br>W = Writable t                                                               |                                 |                                  | re Clearable bit                    |                      |                      |  |  |

| R = Readat   |                                           |                                                                                               | DIC                             | •                                | nented bit, read                    |                      |                      |  |  |

| -n = Value a |                                           | '1' = Bit is set                                                                              |                                 | '0' = Bit is clea                | areo                                | x = Bit is unkn      | own                  |  |  |

| bit 15       |                                           | ARTx Enable bit                                                                               |                                 |                                  |                                     |                      |                      |  |  |

| DIUTS        |                                           | s enabled; all U/                                                                             | NPTy nine are                   | controlled by I                  |                                     | ed by LIENZ1.0       |                      |  |  |

|              |                                           | s disabled; all U                                                                             |                                 |                                  |                                     |                      |                      |  |  |

| bit 14       | -                                         | ted: Read as '0                                                                               | ,                               |                                  |                                     |                      |                      |  |  |