Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

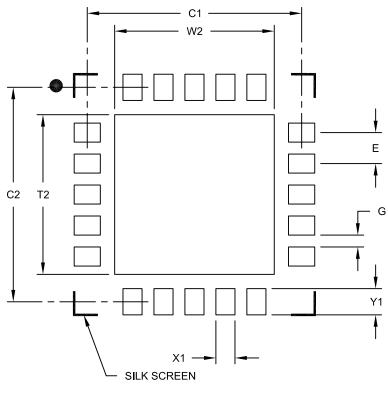

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 20-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16kl401-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-3: DEVICE FEATURES FOR THE PIC24F16KL20X/10X DEVICE |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| TABLE 1-5. DEVICE FEATOR                            |                    |                        |                                                             |               |

|-----------------------------------------------------|--------------------|------------------------|-------------------------------------------------------------|---------------|

| Features                                            | PIC24F08KL201      | PIC24F04KL101          | PIC24F08KL200                                               | PIC24F04KL100 |

| Operating Frequency                                 |                    | DC – 3                 | 2 MHz                                                       |               |

| Program Memory (bytes)                              | 8K                 | 4K                     | 8K                                                          | 4K            |

| Program Memory (instructions)                       | 2816               | 1408                   | 2816                                                        | 1408          |

| Data Memory (bytes)                                 | 512                | 512                    | 512                                                         | 512           |

| Data EEPROM Memory (bytes)                          |                    | —                      | —                                                           | —             |

| Interrupt Sources<br>(soft vectors/NMI traps)       | 27 (23/4)          | 26 (22/4)              | 27 (23/4)                                                   | 26 (22/4)     |

| I/O Ports                                           | PORTA<br>PORTB<15: |                        | PORT/<br>PORTB<15                                           |               |

| Total I/O Pins                                      | 1                  | 7                      | 1                                                           | 2             |

| Timers (8/16-bit)                                   | 1/2                | 1/2                    | 1/2                                                         | 1/2           |

| Capture/Compare/PWM modules:                        |                    |                        |                                                             |               |

| Total                                               | 2                  | 2                      | 2                                                           | 2             |

| Enhanced CCP                                        | 0                  | 0                      | 0                                                           | 0             |

| Input Change Notification Interrupt                 | 17                 | 17                     | 11                                                          | 11            |

| Serial Communications:                              |                    |                        |                                                             |               |

| UART                                                | 1                  | 1                      | 1                                                           | 1             |

| MSSP                                                | 1                  | 1                      | 1                                                           | 1             |

| 10-Bit Analog-to-Digital Module<br>(input channels) | 12                 |                        | 7                                                           |               |

| Analog Comparators                                  | 1                  | 1                      | 1                                                           | 1             |

| Resets (and delays)                                 |                    |                        | , MCLR, WDT, Illega<br>aps, Configuration W<br>T, PLL Lock) |               |

| Instruction Set                                     | 76 Base            | Instructions, Multiple | Addressing Mode \                                           | /ariations    |

| Packages                                            | 20-Pin PDIP/SS     | SOP/SOIC/QFN           | 14-Pin PD                                                   | IP/TSSOP      |

|                                                     |                    |                        |                                                             |               |

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro® Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

| TABLE 4-6               | : Т  | IMER   | REGIS  | TER N  | IAP    |        |        |        |        |                        |                        |          |              |                  |        |         |         |               |

|-------------------------|------|--------|--------|--------|--------|--------|--------|--------|--------|------------------------|------------------------|----------|--------------|------------------|--------|---------|---------|---------------|

| File Name               | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7                  | Bit 6                  | Bit 5    | Bit 4        | Bit 3            | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

| TMR1                    | 0100 |        |        |        |        |        |        |        |        | Timer1 Reg             | gister                 |          |              |                  |        |         |         | 0000          |

| PR1                     | 0102 |        |        |        |        |        |        |        | Tir    | mer1 Period            | Register               |          |              |                  |        |         |         | FFFF          |

| T1CON                   | 0104 | TON    | _      | TSIDL  | _      | _      | _      | T1ECS1 | T1ECS0 | _                      | TGATE                  | TCKPS1   | TCKPS0       | —                | TSYNC  | TCS     | _       | 0000          |

| TMR2                    | 0106 | _      | _      | _      | _      | _      | _      | _      | _      | Timer2 Register        |                        |          |              |                  |        |         | 0000    |               |

| PR2                     | 0108 | _      | _      | _      | _      | _      | _      | _      | _      | Timer2 Period Register |                        |          |              |                  |        |         | OOFF    |               |

| T2CON                   | 010A | _      | _      | _      | _      | _      | _      | _      | _      | _                      | T2OUTPS3               | T2OUTPS2 | T2OUTPS1     | T2OUTPS0         | TMR2ON | T2CKPS1 | T2CKPS0 | 0000          |

| TMR3                    | 010C |        |        |        |        |        |        |        |        | Timer3 Reg             | gister                 |          |              |                  |        |         |         | 0000          |

| T3GCON                  | 010E | -      | —      | —      | —      | —      | —      | —      | —      | TMR3GE                 | T3GPOL                 | T3GTM    | T3GSPM       | T3GGO/<br>T3DONE | T3GVAL | T3GSS1  | T3GSS0  | 0000          |

| T3CON                   | 0110 | _      | _      | _      | _      | _      | _      | _      | _      | TMR3CS1                | TMR3CS0                | T3CKPS1  | T3CKPS0      | T3OSCEN          | T3SYNC | _       | TMR3ON  | 0000          |

| TMR4 <sup>(1)</sup>     | 0112 | _      | _      | _      | _      | _      | —      | _      | _      |                        | •                      | •        | Timer4 R     | egister          |        |         |         | 0000          |

| PR4 <sup>(1)</sup>      | 0114 | _      | _      | _      | _      | _      | —      | —      | _      |                        |                        |          | Timer4 Perio | d Register       |        |         |         | 00FF          |

| T4CON <sup>(1)</sup>    | 0116 | _      | _      | _      | _      | _      | —      | —      | _      | _                      | T4OUTPS3               | T4OUTPS2 | T4OUTPS1     | T4OUTPS0         | TMR40N | T4CKPS1 | T4CKPS0 | 0000          |

| CCPTMRS0 <sup>(1)</sup> | 013C | -      | _      | _      | _      | —      | _      | —      | _      | —                      | C3TSEL0 <sup>(1)</sup> | _        | -            | C2TSEL0          | -      | _       | C1TSEL0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

#### TABLE 4-7: CCP/ECCP REGISTER MAP

| File Name               | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                   | Bit 6              | Bit 5      | Bit 4      | Bit 3        | Bit 2     | Bit 1  | Bit 0  | All<br>Resets |

|-------------------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-----------------------------------------|--------------------|------------|------------|--------------|-----------|--------|--------|---------------|

| CCP1CON                 | 0190 | _      | _      | —      | _      | _      | —      | —     | _     | PM1 <sup>(1)</sup>                      | PM0 <sup>(1)</sup> | DC1B1      | DC1B0      | CCP1M3       | CCP1M2    | CCP1M1 | CCP1M0 | 0000          |

| CCPR1L                  | 0192 | -      | _      | _      | _      | _      | _      | _     | _     | Capture/Compare/PWM1 Register Low Byte  |                    |            |            |              |           |        | 0000   |               |

| CCPR1H                  | 0194 | -      | _      | _      | _      | _      | _      | _     | _     | Capture/Compare/PWM1 Register High Byte |                    |            |            |              |           |        | 0000   |               |

| ECCP1DEL <sup>(1)</sup> | 0196 | -      | _      | _      | _      | _      | _      | _     | _     | PRSEN                                   | PDC6               | PDC5       | PDC4       | PDC3         | PDC2      | PDC1   | PDC0   | 0000          |

| ECCP1AS <sup>(1)</sup>  | 0198 | -      | _      | _      | _      | _      | _      | _     | _     | ECCPASE                                 | ECCPAS2            | ECCPAS1    | ECCPAS0    | PSSAC1       | PSSAC0    | PSSBD1 | PSSBD0 | 0000          |

| PSTR1CON(1)             | 019A | _      | _      | _      | _      | _      | _      | _     | _     | CMPL1                                   | CMPL0              | —          | STRSYNC    | STRD         | STRC      | STRB   | STRA   | 0001          |

| CCP2CON                 | 019C | _      | _      | _      | _      | _      | _      | _     | _     | —                                       | _                  | DC2B1      | DC2B0      | CCP2M3       | CCP2M2    | CCP2M1 | CCP2M0 | 0000          |

| CCPR2L                  | 019E | _      | _      | _      | _      | _      | _      | _     | _     |                                         |                    | Capture/Co | ompare/PWN | M2 Register  | Low Byte  |        |        | 0000          |

| CCPR2H                  | 01A0 | _      | _      | _      | _      | _      | _      | _     | _     |                                         |                    | Capture/Co | ompare/PWN | /12 Register | High Byte |        |        | 0000          |

| CCP3CON <sup>(1)</sup>  | 01A8 | _      | _      | _      | _      | _      | _      | _     | _     | —                                       | _                  | DC3B1      | DC3B0      | CCP3M3       | CCP3M2    | CCP3M1 | CCP3M0 | 0000          |

| CCPR3L <sup>(1)</sup>   | 01AA | _      | _      | _      | _      | _      | _      | _     | _     |                                         |                    | Capture/Co | ompare/PWN | VI3 Register | Low Byte  |        |        | 0000          |

| CCPR3H <sup>(1)</sup>   | 01AC | _      |        | _      | _      | _      | —      | —     | _     |                                         |                    | Capture/Co | ompare/PWN | /13 Register | High Byte |        |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits and/or registers are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

### FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLE

|          | Reset – GOTO Address<br>Reserved<br>Oscillator Fail Trap Vector<br>Address Error Trap Vector<br>Stack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>                 | 000002h<br>000004h<br>0000014h<br>000007Ch<br>00007Ch |                                                        |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|

|          | Oscillator Fail Trap Vector<br>Address Error Trap Vector<br>Stack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>—<br>—<br>Interrupt Vector 52<br>Interrupt Vector 53 | 000014h<br>00007Ch                                    |                                                        |

|          | Address Error Trap Vector<br>Stack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>—<br>—<br>Interrupt Vector 52<br>Interrupt Vector 53                                | 00007Ch                                               |                                                        |

| <b>x</b> | Stack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>—<br>—<br>Interrupt Vector 52<br>Interrupt Vector 53                                                             | 00007Ch                                               |                                                        |

|          | Math Error Trap Vector<br>Reserved<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>—<br>—<br>—<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                   | 00007Ch                                               |                                                        |

|          | Reserved<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>—<br>—<br>—<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                             | 00007Ch                                               |                                                        |

|          | Reserved<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>—<br>—<br>—<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                             | 00007Ch                                               |                                                        |

|          | Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>—<br>—<br>—<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                         | 00007Ch                                               |                                                        |

|          | Interrupt Vector 0<br>Interrupt Vector 1<br>—<br>—<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                          | 00007Ch                                               |                                                        |

|          | Interrupt Vector 1<br>—<br>—<br>—<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                                           | 00007Ch                                               |                                                        |

|          | Interrupt Vector 52                                                                                                                                                                                                                       |                                                       |                                                        |

|          | Interrupt Vector 53                                                                                                                                                                                                                       |                                                       | · · · · · · · · · · · · · · · · ·                      |

|          |                                                                                                                                                                                                                                           | 00007Eh                                               | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

|          | Interrupt Vector 54<br>—                                                                                                                                                                                                                  |                                                       |                                                        |

|          | _                                                                                                                                                                                                                                         | 000080h                                               |                                                        |

|          |                                                                                                                                                                                                                                           |                                                       |                                                        |

|          | _                                                                                                                                                                                                                                         |                                                       |                                                        |

|          | —                                                                                                                                                                                                                                         |                                                       |                                                        |

|          | Interrupt Vector 116                                                                                                                                                                                                                      | 0000FCh                                               |                                                        |

|          | Interrupt Vector 117                                                                                                                                                                                                                      | 0000FEh                                               |                                                        |

|          | Reserved                                                                                                                                                                                                                                  | 000100h                                               |                                                        |

|          | Reserved                                                                                                                                                                                                                                  | 000102h                                               |                                                        |

|          | Reserved                                                                                                                                                                                                                                  |                                                       |                                                        |

|          | Oscillator Fail Trap Vector                                                                                                                                                                                                               |                                                       |                                                        |

|          | Address Error Trap Vector                                                                                                                                                                                                                 |                                                       |                                                        |

|          | Stack Error Trap Vector                                                                                                                                                                                                                   |                                                       |                                                        |

|          | Math Error Trap Vector                                                                                                                                                                                                                    |                                                       |                                                        |

|          | Reserved                                                                                                                                                                                                                                  |                                                       |                                                        |

|          | Reserved                                                                                                                                                                                                                                  |                                                       |                                                        |

|          | Reserved                                                                                                                                                                                                                                  |                                                       |                                                        |

|          | Interrupt Vector 0                                                                                                                                                                                                                        | 000114h                                               |                                                        |

|          | Interrupt Vector 1                                                                                                                                                                                                                        |                                                       |                                                        |

|          | —                                                                                                                                                                                                                                         |                                                       | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|          |                                                                                                                                                                                                                                           |                                                       | , ,                                                    |

|          | _                                                                                                                                                                                                                                         |                                                       |                                                        |

|          | Interrupt Vector 52                                                                                                                                                                                                                       | 00017Ch                                               |                                                        |

|          | Interrupt Vector 53                                                                                                                                                                                                                       | 00017Eh                                               |                                                        |

|          | Interrupt Vector 54                                                                                                                                                                                                                       | 000180h                                               |                                                        |

|          | —                                                                                                                                                                                                                                         |                                                       |                                                        |

|          | —                                                                                                                                                                                                                                         |                                                       |                                                        |

| ¥        | —                                                                                                                                                                                                                                         |                                                       |                                                        |

|          | Interrupt Vector 116                                                                                                                                                                                                                      |                                                       |                                                        |

|          | Interrupt Vector 117                                                                                                                                                                                                                      | 0001FEh                                               |                                                        |

|          | Start of Code                                                                                                                                                                                                                             | 000200h                                               |                                                        |

|          |                                                                                                                                                                                                                                           | -                                                     |                                                        |

|          |                                                                                                                                                                                                                                           |                                                       |                                                        |

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|-------|-----|-----|---------|---------|--------|---------|-------|

| —     | —   | —   | MATHERR | ADDRERR | STKERR | OSCFAIL | —     |

| bit 7 |     |     |         |         |        |         | bit 0 |

| Legend:           |            |                                                                                                                |                                    |                    |  |  |  |  |

|-------------------|------------|----------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Reada         | ble bit    | W = Writable bit                                                                                               | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value        | at POR     | '1' = Bit is set                                                                                               | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 15            | 1 = Interr | Interrupt Nesting Disable bit<br>upt nesting is disabled<br>upt nesting is enabled                             |                                    |                    |  |  |  |  |

| bit 14-5<br>bit 4 | MATHER     | mented: Read as '0'<br>R: Arithmetic Error Trap Status<br>flow trap has occurred<br>flow trap has not occurred | bit                                |                    |  |  |  |  |

| bit 3             | 1 = Addre  | R: Address Error Trap Status b<br>ess error trap has occurred<br>ess error trap has not occurred               | it                                 |                    |  |  |  |  |

| bit 2             | STKERR     | : Stack Error Trap Status bit                                                                                  |                                    |                    |  |  |  |  |

|       | <ol> <li>1 = Stack error trap has occurred</li> <li>0 = Stack error trap has not occurred</li> </ol>            |

|-------|-----------------------------------------------------------------------------------------------------------------|

| bit 1 | OSCFAIL: Oscillator Failure Trap Status bit                                                                     |

|       | <ul><li>1 = Oscillator failure trap has occurred</li><li>0 = Oscillator failure trap has not occurred</li></ul> |

| bit 0 | Unimplemented: Read as '0'                                                                                      |

**—**

| U-0                 | R/W-1                                                                 | R/W-0                                                                                                                | R/W-0                         | U-0              | U-0              | U-0             | U-0     |

|---------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|------------------|-----------------|---------|

|                     | NVMIP2                                                                | NVMIP1                                                                                                               | NVMIP0                        |                  | _                | _               |         |

| bit 15              |                                                                       |                                                                                                                      | ÷                             |                  | ÷                |                 | bit 8   |

| U-0                 | R/W-1                                                                 | R/W-0                                                                                                                | R/W-0                         | U-0              | R/W-1            | R/W-0           | R/W-0   |

| _                   | AD1IP2                                                                | AD1IP1                                                                                                               | AD1IP0                        | _                | U1TXIP2          | U1TXIP1         | U1TXIP0 |

| bit 7               |                                                                       | 1                                                                                                                    |                               |                  |                  |                 | bit (   |

| Legend:             |                                                                       |                                                                                                                      |                               |                  |                  |                 |         |

| R = Readab          | le bit                                                                | W = Writable                                                                                                         | bit                           | U = Unimplei     | mented bit, read | d as '0'        |         |

| -n = Value a        | t POR                                                                 | '1' = Bit is set                                                                                                     |                               | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |

| bit 11-7<br>bit 6-4 | •<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>AD1IP<2:0>: | pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>A/D Conversic<br>pt is Priority 7 ( | abled<br>0'<br>n Complete Int | terrupt Priority | bits             |                 |         |

|                     | •<br>•<br>001 = Interru<br>000 = Interru                              | pt is Priority 1<br>pt source is dis                                                                                 | abled                         | interrupt)       |                  |                 |         |

| bit 3               | -                                                                     | ted: Read as '                                                                                                       |                               |                  |                  |                 |         |

| bit 2-0             | 111 = Interru<br>•<br>•                                               | >: UART1 Trans<br>pt is Priority 7 (                                                                                 | -                             | -                |                  |                 |         |

|                     |                                                                       | pt is Priority 1<br>pt source is dis                                                                                 | abled                         |                  |                  |                 |         |

#### REGISTER 8-20: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

### REGISTER 8-30: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| R-0           | r-0                                     | R/W-0                                                                         | U-0                           | R-0                              | R-0                                                                           | R-0                                    | R-0            |  |  |  |

|---------------|-----------------------------------------|-------------------------------------------------------------------------------|-------------------------------|----------------------------------|-------------------------------------------------------------------------------|----------------------------------------|----------------|--|--|--|

| CPUIRQ        | r                                       | VHOLD                                                                         | —                             | ILR3                             | ILR2                                                                          | ILR1                                   | ILR0           |  |  |  |

| bit 15        |                                         |                                                                               |                               | •                                |                                                                               | ·                                      | bit 8          |  |  |  |

|               |                                         |                                                                               |                               |                                  |                                                                               |                                        |                |  |  |  |

| U-0           |                                         | R-0                                                                           |                               |                                  |                                                                               |                                        |                |  |  |  |

|               | VECNUM6                                 | VECNUM5                                                                       | VECNUM4                       | VECNUM3                          | VECNUM2                                                                       | VECNUM1                                | VECNUM0        |  |  |  |

| bit 7         |                                         |                                                                               |                               |                                  |                                                                               |                                        | bit (          |  |  |  |

| Legend:       |                                         | r = Reserved                                                                  | bit                           |                                  |                                                                               |                                        |                |  |  |  |

| R = Readable  | e bit                                   | W = Writable                                                                  | bit                           | U = Unimpler                     | nented bit, read                                                              | as '0'                                 |                |  |  |  |

| -n = Value at | POR                                     | '1' = Bit is set                                                              |                               | '0' = Bit is cle                 |                                                                               | x = Bit is unkr                        | nown           |  |  |  |

| bit 14        | 0 = No interr                           | vhen the CPU p<br>upt request is le<br>aintain as '0'                         |                               |                                  | errupt priority)                                                              |                                        |                |  |  |  |

| bit 14        | Reserved: M                             |                                                                               |                               | 0                                |                                                                               |                                        |                |  |  |  |

| bit 13        | VHOLD: Vector Hold bit                  |                                                                               |                               |                                  |                                                                               |                                        |                |  |  |  |

|               | 1 = VECNUN<br>current in<br>0 = VECNUN  | //<6:0> will cor<br>nterrupt<br>//<6:0> will con                              | tain the value                | e of the highe<br>of the last Ac | rupt is Stored in<br>st priority pend<br>knowledged inte<br>ther interrupts a | ling interrupt, i<br>errupt (last inte | instead of the |  |  |  |

| bit 12        | Unimplemen                              | ted: Read as '                                                                | )'                            |                                  |                                                                               |                                        |                |  |  |  |

| bit 11-8      | 1111 = CPU<br>•<br>•<br>•<br>0001 = CPU | w CPU Interrup<br>Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit | y Level is 15<br>y Level is 1 | el bits                          |                                                                               |                                        |                |  |  |  |

| bit 7         | Unimplemen                              | ted: Read as '                                                                | )'                            |                                  |                                                                               |                                        |                |  |  |  |

| bit 6-0       | VECNUM<6:                               | 0>: Vector Num                                                                | ber of Pendin                 | g Interrupt bits                 | 5                                                                             |                                        |                |  |  |  |

|               | 0111111 = Ir<br>•<br>•                  | nterrupt vector p                                                             | pending is Nu                 | mber 135                         |                                                                               |                                        |                |  |  |  |

|               |                                         | nterrupt vector p<br>nterrupt vector p                                        |                               |                                  |                                                                               |                                        |                |  |  |  |

NOTES:

REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0          | U-0                                                                                         | R/W-0                             | U-0            | U-0                  | U-0              | R/W-0                 | R/W-0                 |  |

|----------------|---------------------------------------------------------------------------------------------|-----------------------------------|----------------|----------------------|------------------|-----------------------|-----------------------|--|

| TON            | _                                                                                           | TSIDL                             | _              | _                    |                  | T1ECS1 <sup>(1)</sup> | T1ECS0 <sup>(1)</sup> |  |

| bit 15         |                                                                                             |                                   |                |                      |                  |                       | bit 8                 |  |

|                |                                                                                             |                                   |                |                      |                  |                       |                       |  |

| U-0            | R/W-0                                                                                       | R/W-0                             | R/W-0          | U-0                  | R/W-0            | R/W-0                 | U-0                   |  |

| —              | TGATE                                                                                       | TCKPS1                            | TCKPS0         | —                    | TSYNC            | TCS                   | —                     |  |

| bit 7          |                                                                                             |                                   |                |                      |                  |                       | bit (                 |  |

| Legend:        |                                                                                             |                                   |                |                      |                  |                       |                       |  |

| R = Readable   | e bit                                                                                       | W = Writable                      | bit            | U = Unimplem         | nented bit, read | d as '0'              |                       |  |

| -n = Value at  |                                                                                             | '1' = Bit is set                  |                | '0' = Bit is clea    |                  | x = Bit is unkr       | lown                  |  |

|                |                                                                                             |                                   |                | 0 21110 0.00         |                  |                       |                       |  |

| bit 15         | TON: Timer1                                                                                 | On bit                            |                |                      |                  |                       |                       |  |

|                | 1 = Starts 16-                                                                              | -bit Timer1                       |                |                      |                  |                       |                       |  |

|                | 0 = Stops 16-                                                                               | -bit Timer1                       |                |                      |                  |                       |                       |  |

| bit 14         | Unimplement                                                                                 | ted: Read as '                    | כי             |                      |                  |                       |                       |  |

| bit 13         | TSIDL: Timer                                                                                | 1 Stop in Idle N                  | lode bit       |                      |                  |                       |                       |  |

|                |                                                                                             |                                   |                | device enters Idl    | le mode          |                       |                       |  |

|                |                                                                                             | s module opera                    |                | de                   |                  |                       |                       |  |

| bit 12-10      | Unimplemented: Read as '0'<br>T1ECS <1:0>: Timer1 Extended Clock Select bits <sup>(1)</sup> |                                   |                |                      |                  |                       |                       |  |

| bit 9-8        |                                                                                             |                                   | ded Clock Sel  | lect bits(")         |                  |                       |                       |  |

|                | 11 = Reserve                                                                                | d; do not use<br>uses the LPRC    | as the clock s | ource                |                  |                       |                       |  |

|                |                                                                                             | uses the extern                   |                |                      |                  |                       |                       |  |

|                |                                                                                             |                                   |                | r (SOSC) as the      | e clock source   |                       |                       |  |

| bit 7          | Unimplement                                                                                 | ted: Read as '                    | )'             |                      |                  |                       |                       |  |

| bit 6          | TGATE: Time                                                                                 | r1 Gated Time                     | Accumulation   | Enable bit           |                  |                       |                       |  |

|                | When TCS =                                                                                  |                                   |                |                      |                  |                       |                       |  |

|                | This bit is igno                                                                            |                                   |                |                      |                  |                       |                       |  |

|                | <u>When TCS =</u> $1 = Catod times$                                                         | <u>0:</u><br>ne accumulatio       | n is onablad   |                      |                  |                       |                       |  |

|                |                                                                                             | ne accumulatio                    |                |                      |                  |                       |                       |  |

| bit 5-4        |                                                                                             | : Timer1 Input                    |                | e Select bits        |                  |                       |                       |  |

|                | 11 <b>= 1:256</b>                                                                           |                                   |                |                      |                  |                       |                       |  |

|                | 10 <b>= 1:64</b>                                                                            |                                   |                |                      |                  |                       |                       |  |

|                | 01 = 1:8                                                                                    |                                   |                |                      |                  |                       |                       |  |

| 1.1.0          | 00 = 1:1                                                                                    |                                   | . 1            |                      |                  |                       |                       |  |

| bit 3          | -                                                                                           | ted: Read as '                    |                | here a in a tion Cal | a at hit         |                       |                       |  |

| bit 2          |                                                                                             |                                   | ock input Sync | hronization Sele     |                  |                       |                       |  |

|                | <u>When TCS =</u><br>1 = Synchroi                                                           | <u>⊥.</u><br>nizes external (     | clock input    |                      |                  |                       |                       |  |

|                |                                                                                             | t synchronize e                   |                | input                |                  |                       |                       |  |

|                | When TCS =                                                                                  | <u>0:</u>                         |                |                      |                  |                       |                       |  |

|                | This bit is igno                                                                            | ored.                             |                |                      |                  |                       |                       |  |

|                |                                                                                             |                                   |                |                      |                  |                       |                       |  |

| bit 1          |                                                                                             | Clock Source S                    |                |                      |                  |                       |                       |  |

| bit 1          | 1 = Timer1 cl                                                                               |                                   |                | ECS<1:0>             |                  |                       |                       |  |

| bit 1<br>bit 0 | 1 = Timer1 cl<br>0 = Internal c                                                             | Clock Source S<br>ock source is s | elected by T1  | ECS<1:0>             |                  |                       |                       |  |

| U-0                                | U-0                            | U-0            | U-0            | U-0               | U-0             | U-0      | U-0     |

|------------------------------------|--------------------------------|----------------|----------------|-------------------|-----------------|----------|---------|

| _                                  |                                |                |                |                   |                 |          |         |

| bit 15                             |                                |                |                |                   |                 |          | bita    |

|                                    |                                |                |                |                   |                 |          |         |

| U-0                                | R/W-0                          | R/W-0          | R/W-0          | R/W-0             | R/W-0           | R/W-0    | R/W-0   |

| _                                  | T2OUTPS3                       | T2OUTPS2       | T2OUTPS1       | T2OUTPS0          | TMR2ON          | T2CKPS1  | T2CKPS0 |

| bit 7                              |                                |                |                |                   |                 |          | bit (   |

| Legend:                            |                                |                |                |                   |                 |          |         |

| R = Readable                       | e bit                          | W = Writable   | bit            | U = Unimplem      | ented bit, read | l as '0' |         |

| -n = Value at POR '1' = Bit is set |                                |                |                | '0' = Bit is clea | x = Bit is unkr | nown     |         |

| bit 15-7                           | Unimplement                    | ted: Read as ' | י.             |                   |                 |          |         |

|                                    | -                              |                |                |                   |                 |          |         |

| bit 6-3                            | 11111 = 1:16 F                 | 0>: Timer2 Ou  | ipul Posiscale | Select bits       |                 |          |         |

|                                    | 1111 = 1.16 F                  |                |                |                   |                 |          |         |

|                                    | •                              | 0000000        |                |                   |                 |          |         |

|                                    | •                              |                |                |                   |                 |          |         |

|                                    | •<br>0001 = 1:2 Pc             |                |                |                   |                 |          |         |

|                                    | 0001 = 1.2 PC<br>0000 = 1.1 PC |                |                |                   |                 |          |         |

| bit 2                              | TMR2ON: Tin                    |                |                |                   |                 |          |         |

| 5.11 -                             | 1 = Timer2 is                  |                |                |                   |                 |          |         |

|                                    | 0 = Timer2 is                  |                |                |                   |                 |          |         |

| bit 1-0                            | T2CKPS<1:0                     | >: Timer2 Cloc | k Prescale Sel | ect bits          |                 |          |         |

|                                    | 10 = Prescale                  | er is 16       |                |                   |                 |          |         |

|                                    | 01 = Prescale                  | er is 4        |                |                   |                 |          |         |

|                                    | 00 = Prescale                  |                |                |                   |                 |          |         |

### REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

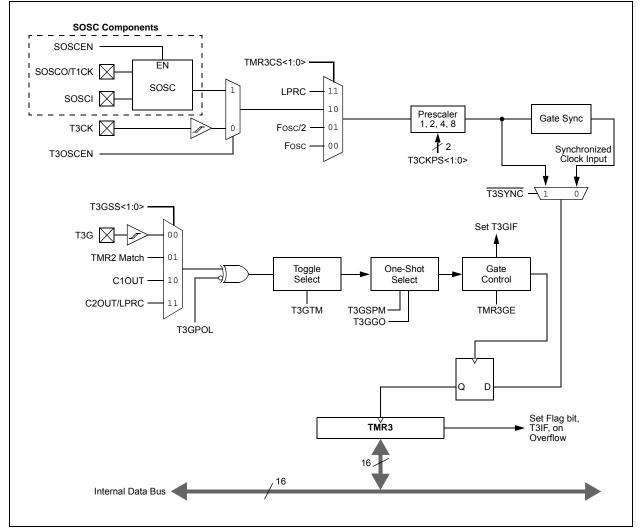

### 14.0 TIMER3 MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704).

The Timer3 timer/counter modules incorporate these features:

- Software-selectable operation as a 16-bit timer or counter

- One 16-bit readable and writable Timer Value register

- Selectable clock source (internal or external) with device clock, SOSC or LPRC oscillator options

- · Interrupt-on-overflow

- Multiple timer gating options, including:

- User-selectable gate sources and polarity

- Gate/toggle operation

- Single Pulse (One-Shot) mode

- Module Reset on ECCP Special Event Trigger

The Timer3 module is controlled through the T3CON register (Register 14-1). A simplified block diagram of the Timer3 module is shown in Figure 14-1.

The Fosc clock source should not be used with the ECCP capture/compare features. If the timer will be used with the capture or compare features, always select one of the other timer clocking options.

### FIGURE 14-1: TIMER3 BLOCK DIAGRAM

### REGISTER 17-7: SSPxCON3: MSSPx CONTROL REGISTER 3 (I<sup>2</sup>C<sup>™</sup> MODE)

| U-0                   | U-0                         | U-0                                   | U-0             | U-0               | U-0                        | U-0                | U-0             |

|-----------------------|-----------------------------|---------------------------------------|-----------------|-------------------|----------------------------|--------------------|-----------------|

| _                     | —                           | _                                     |                 | _                 | —                          | —                  | —               |

| bit 15                |                             | ·                                     |                 | ·                 |                            | ·                  | bit 8           |

|                       |                             |                                       |                 |                   |                            |                    |                 |

| R-0                   | R/W-0                       | R/W-0                                 | R/W-0           | R/W-0 R/W-0       |                            | R/W-0              | R/W-0           |

| ACKTIM <sup>(2)</sup> | PCIE                        | SCIE                                  | BOEN            | SDAHT             | SBCDE                      | AHEN               | DHEN            |

| bit 7                 |                             |                                       |                 |                   |                            |                    | bit             |

|                       |                             |                                       |                 |                   |                            |                    |                 |

| Legend:               |                             |                                       |                 |                   |                            |                    |                 |

| R = Readable          |                             | W = Writable                          | bit             | -                 | nented bit, rea            |                    |                 |

| -n = Value at         | POR                         | '1' = Bit is set                      |                 | '0' = Bit is cle  | ared                       | x = Bit is unk     | nown            |

| bit 15-8              | Unimplemen                  | ited: Read as '(                      | ۰'              |                   |                            |                    |                 |

| bit 7                 | -                           | knowledge Time                        |                 |                   |                            |                    |                 |

|                       |                             | the I <sup>2</sup> C bus is in        |                 | dae sequence.     | set on the 8 <sup>th</sup> | falling edge of t  | the SCI x cloc  |

|                       |                             | cknowledge sec                        |                 |                   |                            |                    |                 |

| bit 6                 | PCIE: Stop C                | ondition Interru                      | pt Enable bit   |                   |                            |                    |                 |

|                       |                             | nterrupt on dete                      |                 |                   |                            |                    |                 |

|                       | •                           | ection interrupts                     |                 | )                 |                            |                    |                 |

| bit 5                 |                             | ondition Interru                      | •               |                   |                            |                    |                 |

|                       |                             | nterrupt on dete                      |                 |                   | conditions                 |                    |                 |

| bit 4                 |                             | r Overwrite Ena                       |                 |                   |                            |                    |                 |

|                       | I <sup>2</sup> C Master m   |                                       |                 |                   |                            |                    |                 |

|                       | This bit is ign             |                                       |                 |                   |                            |                    |                 |

|                       | I <sup>2</sup> C Slave mo   |                                       | 1 <u>1017</u>   |                   |                            | <i></i>            |                 |

|                       |                             | F is updated an<br>SPOV bit only if   |                 | enerated for a re | eceived addres             | s/data byte, igr   | noring the stat |

|                       |                             | F is only update                      |                 | )<br>V is clear   |                            |                    |                 |

| bit 3                 | SDAHT: SDA                  | x Hold Time Se                        | election bit    |                   |                            |                    |                 |

|                       |                             | of 300 ns hold                        |                 |                   |                            |                    |                 |

|                       |                             | of 100 ns hold                        |                 | 0                 | e e                        |                    |                 |

| bit 2                 | SBCDE: Slav                 | /e Mode Bus Co                        | ollision Detect | Enable bit (Sla   | ve mode only)              |                    |                 |

|                       |                             | slave bus collisi                     | •               |                   |                            |                    |                 |

| L 11 A                |                             | s collision interr                    | •               |                   |                            |                    |                 |

| bit 1                 |                             | ess Hold Enable                       | -               | • •               | a received edg             | trace bytes the    | CKD bit of th   |

|                       |                             | g the 8th falling<br>N1 register will |                 |                   |                            | iress byte, the    |                 |

|                       |                             | holding is disat                      |                 |                   |                            |                    |                 |

| bit 0                 | DHEN: Data                  | Hold Enable bit                       | (Slave mode     | only)             |                            |                    |                 |

|                       |                             | g the 8th falling                     | •               |                   | data byte; slave           | e hardware clea    | ars the CKP b   |

|                       |                             | SPxCON1 regist                        |                 | s held low        |                            |                    |                 |

|                       | v = vata noi                | ding is disabled                      |                 |                   |                            |                    |                 |

|                       | iis bit has no ef<br>abled. | fect in Slave mo                      | odes for which  | Start and Stop    | condition dete             | ection is explicit | ly listed as    |

| 0. Th                 |                             |                                       |                 |                   |                            |                    |                 |

2: The ACKTIM status bit is active only when the AHEN bit or DHEN bit is set.

### EQUATION 19-1: A/D CONVERSION CLOCK PERIOD<sup>(1)</sup>

$$ADCS = \frac{TAD}{TCY} - 1$$

$TAD = TCY \bullet (ADCS + 1)$

**Note 1:** Based on TCY = 2 \* TOSC; Doze mode and PLL are disabled.

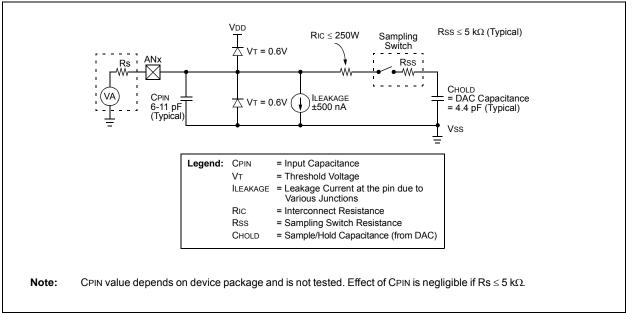

### FIGURE 19-2: 10-BIT A/D CONVERTER ANALOG INPUT MODEL

| R/P-0        | R/P-0                                                                                                                                  | R/P-1                             | R/P-1             | R/P-1             | R/P-0           | R/P-1           | R/P-1   |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------|-------------------|-----------------|-----------------|---------|--|

| FCKSM1       | FCKSM0                                                                                                                                 | SOSCSEL                           | POSCFREQ1         | POSCFREQ0         | OSCIOFNC        | POSCMD1         | POSCMD0 |  |

| bit 7        |                                                                                                                                        |                                   |                   |                   |                 |                 | bit 0   |  |

|              |                                                                                                                                        |                                   |                   |                   |                 |                 |         |  |

| Legend:      |                                                                                                                                        |                                   |                   |                   |                 |                 |         |  |

| R = Readab   | ole bit                                                                                                                                | P = Program                       | nable bit         | U = Unimplem      | ented bit, read | as '0'          |         |  |

| -n = Value a | it POR                                                                                                                                 | '1' = Bit is set                  |                   | '0' = Bit is clea | red             | x = Bit is unkr | nown    |  |

|              |                                                                                                                                        |                                   |                   |                   |                 |                 |         |  |

| bit 7-6      | FCKSM<1:0>                                                                                                                             | Clock Switch                      | ing and Monito    | r Selection Con   | figuration bits |                 |         |  |

|              |                                                                                                                                        | 0                                 | •                 | Clock Monitor is  |                 |                 |         |  |