# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 18                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

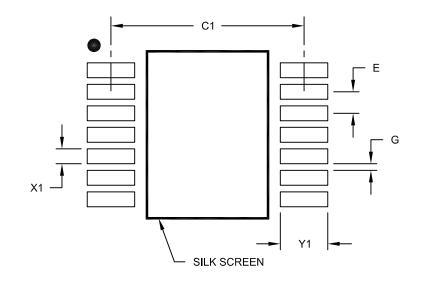

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16kl401t-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

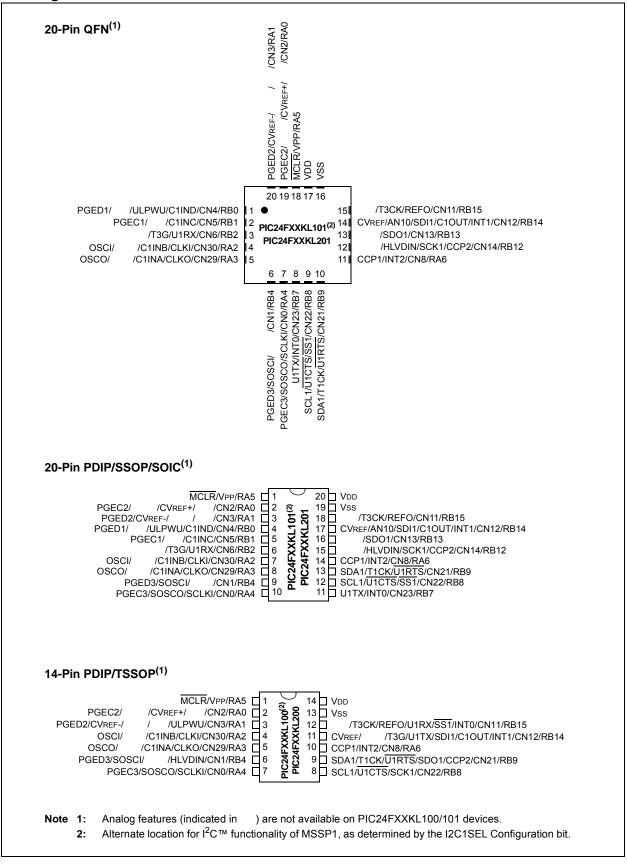

### Pin Diagrams: PIC24FXXKL10X/20X

#### **TABLE 1-5:** PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS

|          |                                  | Pin Numbe     | r                        |     |        |                                                   |

|----------|----------------------------------|---------------|--------------------------|-----|--------|---------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 14-Pin<br>PDIP/<br>TSSOP | I/O | Buffer | Description                                       |

| AN0      | 2                                | 19            | 2                        | I   | ANA    | A/D Analog Inputs. Not available on PIC24F16KL10X |

| AN1      | 3                                | 20            | 3                        | Ι   | ANA    | family devices.                                   |

| AN2      | 4                                | 1             | —                        | Ι   | ANA    |                                                   |

| AN3      | 5                                | 2             | _                        | I   | ANA    |                                                   |

| AN4      | 6                                | 3             | _                        | I   | ANA    |                                                   |

| AN9      | 18                               | 15            | 12                       | I   | ANA    |                                                   |

| AN10     | 17                               | 14            | 11                       | I   | ANA    |                                                   |

| AN11     | 16                               | 13            | _                        | I   | ANA    |                                                   |

| AN12     | 15                               | 12            | _                        | I   | ANA    |                                                   |

| AN13     | 7                                | 4             | 4                        | I   | ANA    | 7                                                 |

| AN14     | 8                                | 5             | 5                        | I   | ANA    | 1                                                 |

| AN15     | 9                                | 6             | 6                        | I   | ANA    | 1                                                 |

| AVdd     | 20                               | 17            | 14                       | I   | ANA    | Positive Supply for Analog modules                |

| AVss     | 19                               | 16            | 13                       | I   | ANA    | Ground Reference for Analog modules               |

| CCP1     | 14                               | 11            | 10                       | I/O | ST     | CCP1 Capture Input/Compare and PWM Output         |

| CCP2     | 15                               | 12            | 9                        | I/O | ST     | CCP2 Capture Input/Compare and PWM Output         |

| C1INA    | 8                                | 5             | 5                        | I   | ANA    | Comparator 1 Input A (+)                          |

| C1INB    | 7                                | 4             | 4                        | I   | ANA    | Comparator 1 Input B (-)                          |

| C1INC    | 5                                | 2             | _                        | I   | ANA    | Comparator 1 Input C (+)                          |

| C1IND    | 4                                | 1             | _                        | I   | ANA    | Comparator 1 Input D (-)                          |

| C1OUT    | 17                               | 14            | 11                       | 0   | _      | Comparator 1 Output                               |

| CLK I    | 7                                | 4             | 9                        | I   | ANA    | Main Clock Input                                  |

| CLKO     | 8                                | 5             | 10                       | 0   | _      | System Clock Output                               |

| CN0      | 10                               | 7             | 7                        | I   | ST     | Interrupt-on-Change Inputs                        |

| CN1      | 9                                | 6             | 6                        | I   | ST     |                                                   |

| CN2      | 2                                | 19            | 2                        | I   | ST     |                                                   |

| CN3      | 3                                | 20            | 3                        | I   | ST     | 7                                                 |

| CN4      | 4                                | 1             | _                        | I   | ST     | 7                                                 |

| CN5      | 5                                | 2             | _                        | Ι   | ST     | ]                                                 |

| CN6      | 6                                | 3             | _                        | I   | ST     | 7                                                 |

| CN8      | 14                               | 11            | 10                       | I   | ST     | 7                                                 |

| CN9      | _                                | _             | —                        | I   | ST     | 7                                                 |

| CN11     | 18                               | 15            | 12                       | I   | ST     | 7                                                 |

| CN12     | 17                               | 14            | 11                       | I   | ST     | 7                                                 |

| CN13     | 16                               | 13            | —                        | I   | ST     | 7                                                 |

| CN14     | 15                               | 12            | _                        | Ι   | ST     | 7                                                 |

| CN21     | 13                               | 10            | 9                        | I   | ST     | 1                                                 |

| CN22     | 12                               | 9             | 8                        | I   | ST     | 1                                                 |

| CN23     | 11                               | 8             | —                        | I   | ST     | 1                                                 |

| CN29     | 8                                | 5             | 5                        | I   | ST     | 1                                                 |

| CN30     | 7                                | 4             | 4                        | 1   | ST     | 1                                                 |

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

### 2.1 Basic Connection Requirements

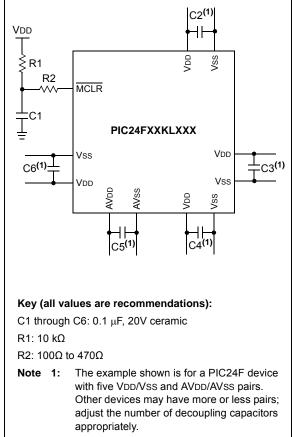

Getting started with the PIC24F16KL402 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.4 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

Note: The AVDD and AVSS pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

### 3.2 CPU Control Registers

### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                    | U-0                  | U-0                                        | U-0            | U-0                            | U-0                          | U-0               | R/W-0          |

|------------------------|----------------------|--------------------------------------------|----------------|--------------------------------|------------------------------|-------------------|----------------|

|                        | _                    | _                                          | _              | _                              | _                            | _                 | DC             |

| bit 15                 |                      | I I                                        |                |                                |                              |                   | bit            |

| R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                       | R-0            | R/W-0                          | R/W-0                        | R/W-0             | R/W-0          |

| IPL2 <sup>(2)</sup>    | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>                        | RA             | N                              | OV                           | Z                 | C              |

| bit 7                  |                      | 20                                         |                |                                | 0.                           | _                 | bit            |

|                        |                      |                                            |                |                                |                              |                   |                |

| Legend:<br>R = Readabl | e hit                | W = Writable b                             | it             | II = I Inimplem                | nented bit, read             | d as 'O'          |                |

| -n = Value at          |                      | '1' = Bit is set                           | iii iii        | '0' = Bit is clea              |                              | x = Bit is unkr   | NOWD           |

|                        |                      |                                            |                |                                |                              |                   |                |

| bit 15-9               | Unimplemen           | ted: Read as '0                            | ,              |                                |                              |                   |                |

| bit 8                  | -                    | f Carry/Borrow b                           |                |                                |                              |                   |                |

|                        |                      | -                                          |                | (for byte-sized da             | ata) or 8 <sup>th</sup> Iow- | order bit (for wo | ord-sized dat  |

|                        | of the res           | sult occurred                              |                |                                |                              |                   |                |

|                        | •                    |                                            |                | rder bit of the res            |                              | ed                |                |

| bit 7-5                | IPL<2:0>: CF         | PU Interrupt Prio                          | rity Level (IP | L) Status bits <sup>(1,2</sup> | 2)                           |                   |                |

|                        |                      |                                            |                | 5); user interrupt             | s disabled                   |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I<br>nterrupt Priority I | •              | ,                              |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

| bit 4                  | <b>RA:</b> REPEAT    | Loop Active bit                            |                |                                |                              |                   |                |

|                        |                      | oop in progress                            |                |                                |                              |                   |                |

|                        |                      | oop not in progr                           | ess            |                                |                              |                   |                |

| bit 3                  | N: ALU Nega          |                                            |                |                                |                              |                   |                |

|                        | 1 = Result wa        | 0                                          | (              | 4:                             |                              |                   |                |

|                        |                      | as non-negative                            | (zero or posi  | tive)                          |                              |                   |                |

| bit 2                  | OV: ALU Ove          |                                            |                |                                |                              |                   |                |

|                        |                      | occurred for sig                           |                | plement) arithm                | etic in this arith           | imetic operation  | n              |

| bit 1                  | <b>Z:</b> ALU Zero   |                                            |                |                                |                              |                   |                |

|                        |                      |                                            | te the 7 hit 4 | nas set it at some             | e time in the n              | aet               |                |

|                        |                      |                                            |                | cts the Z bit, has             |                              |                   | sult)          |

| bit 0                  | C: ALU Carry         |                                            | ,              | ,,                             |                              | ,                 | -7             |

| ~                      |                      |                                            | Significant b  | oit (MSb) of the r             | esult occurred               |                   |                |

|                        |                      |                                            |                | bit (MSb) of the               |                              |                   |                |

| Note 1: Th             | ne IPI. Status hi    | ts are read-only                           | when NSTD      | IS (INTCON1<1                  | 5>) = 1                      |                   |                |

|                        |                      |                                            |                | IPL3 bit (CORC                 |                              | m the CPU I Into  | rrunt Priority |

| <b>2</b> .             |                      |                                            |                |                                |                              |                   | in april nonty |

2: The IPL Status bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

#### TABLE 4-16: SYSTEM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | SBOREN | —      | —      | _      | CM     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 3100          |

| OSCTUN    | 0748 | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 074E | ROEN   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN | -      | HLSIDL | _      | —      | _      | _      | _      | VDIR    | BGVST | IRVST  | -     | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on configuration fuses and by type of Reset.

### TABLE 4-17: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5  | Bit 4   | Bit 3      | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|---------|--------|--------|-------|-------|-------|-------|--------|---------|------------|--------|--------|--------|---------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | PGMONLY |        | _      | _     |       | —     | ERASE | NVMOP5 | NVMOP4  | NVMOP3     | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMKEY    | 0766 | _      | -      | -      | —       | —      |        | _     |       |       |       |        | NVM Key | / Register |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-18: ULTRA LOW-POWER WAKE-UP REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|---------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ULPWCON   | 0768 | ULPEN  | _      | ULPSIDL |        | —      | _      |       | ULPSINK |       | _     |       | _     | _     |       | _     | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-19: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|---------|-------|-------|-------|--------|--------|--------|--------|------------|

| PMD1      | 0770 | _      | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     |       | SSP1MD  | U2MD  | U1MD  |       | —      | _      |        | ADC1MD | 0000       |

| PMD2      | 0772 | _      | —      | —      | _      | —      | —      | _     | -     | _       | _     | —     | _     | —      | CCP3MD | CCP2MD | CCP1MD | 0000       |

| PMD3      | 0774 | _      | _      | _      |        |        | CMPMD  | _     | -     | —       | _     | _     |       | —      | _      | SSP2MD | —      | 0000       |

| PMD4      | 0776 |        | —      | _      | _      | _      | —      | -     | —     | ULPWUMD |       | _     | EEMD  | REFOMD | —      | HLVDMD | _      | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS30001037C-page 42

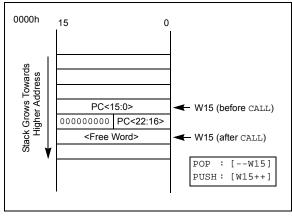

### 4.2.5 SOFTWARE STACK

In addition to its use as a Working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer. The pointer always points to the first available free word and grows from lower to higher addresses. It predecrements for stack pops and post-increments for stack pushes, as shown in Figure 4-4.

Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated, using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation.

Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 0DF6, in RAM, initialize the SPLIM with the value, 0DF4.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the Special Function Register (SFR) space.

**Note:** A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

FIGURE 4-4: CALL STACK FRAME

### 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit wide program space and 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Apart from the normal execution, the PIC24F architecture provides two methods by which the program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space, PSV

Table instructions allow an application to read or write small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. It can only access the least significant word (lsw) of the program word.

### 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit (MSb) of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility Page Address register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike the table operations, this limits remapping operations strictly to the user memory area.

Table 4-20 and Figure 4-5 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> bits refer to a program space word, whereas the D<15:0> bits refer to a data space word.

|                 | <b>D</b> 4 4 4 6 | <b>D</b> 444 A                         | <b>D</b> 4 4 4 4       |                       |                       |                       |                       |

|-----------------|------------------|----------------------------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| R/SO-0, HC      | R/W-0            | R/W-0                                  | R/W-0                  | U-0                   | U-0                   | U-0                   | U-0                   |

| WR              | WREN             | WRERR                                  | PGMONLY                |                       |                       | —                     | —                     |

| bit 15          |                  |                                        |                        |                       |                       |                       | bit 8                 |

|                 |                  |                                        |                        |                       |                       |                       |                       |

| U-0             | R/W-0            | R/W-0                                  | R/W-0                  | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

| —               | ERASE            | NVMOP5 <sup>(1)</sup>                  | NVMOP4 <sup>(1)</sup>  | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7           |                  |                                        |                        |                       |                       |                       | bit 0                 |

|                 |                  |                                        |                        |                       |                       |                       |                       |

| Legend:         |                  | HC = Hardware                          | e Clearable bit        | U = Unimpler          | mented bit, rea       | ad as '0'             |                       |

| R = Readable    | bit              | W = Writable b                         | it                     | SO = Settabl          | e Only bit            |                       |                       |

| -n = Value at I | POR              | '1' = Bit is set                       |                        | '0' = Bit is cle      | ared                  | x = Bit is unk        | nown                  |

|                 |                  |                                        |                        |                       |                       |                       |                       |

| bit 15          | WR: Write Co     | ontrol bit (progra                     | m or erase)            |                       |                       |                       |                       |

|                 |                  | a data EEPROM                          |                        | cvcle (can be s       | et but not clea       | red in software       | e)                    |

|                 |                  | le is complete (                       |                        | •                     |                       |                       | - /                   |

| bit 14          | WREN: Write      | Enable bit (eras                       | e or program)          |                       |                       |                       |                       |

|                 | 1 = Enables a    | in erase or prog                       | ram operation          |                       |                       |                       |                       |

|                 | 0 = No operat    | tion allowed (dev                      | vice clears this t     | oit on completion     | on of the write/      | erase operatio        | on)                   |

| bit 13          | WRERR: Flas      | sh Error Flag bit                      |                        |                       |                       |                       |                       |

|                 | 1 = A write o    | operation is pre                       | maturely termir        | nated (any MC         | LR or WDT             | Reset during          | programming           |

|                 | operation        | /                                      |                        |                       |                       |                       |                       |

|                 |                  | operation comp                         |                        | ліу                   |                       |                       |                       |

| bit 12          |                  | Program Only En                        |                        |                       | <i>.</i>              |                       |                       |

|                 |                  | eration is execute<br>c erase-before-v |                        |                       |                       | tically by an a       | rade of torget        |

|                 | address(e        |                                        | ville, wille oper      | ations are pred       |                       | lucally by all e      | lase of larger        |

| bit 11-7        | •                | ted: Read as '0'                       |                        |                       |                       |                       |                       |

| bit 6           | -                | e Operation Sel                        |                        |                       |                       |                       |                       |

| Sit o           |                  | an erase opera                         |                        | s set                 |                       |                       |                       |

|                 |                  | a write operatio                       |                        |                       |                       |                       |                       |

| bit 5-0         | NVMOP<5:0>       | . Programming                          | Operation Com          | mand Byte bits        | <sub>3</sub> (1)      |                       |                       |

|                 | Erase Operati    | ions (when ERA                         | <u>SE bit is '1'):</u> | -                     |                       |                       |                       |

|                 | 011010 = Era     | ases 8 words                           |                        |                       |                       |                       |                       |

|                 | 011001 = Era     |                                        |                        |                       |                       |                       |                       |

|                 | 011000 = Era     |                                        |                        |                       |                       |                       |                       |

|                 |                  | ases entire data                       |                        | • 'o')•               |                       |                       |                       |

|                 | 001xxx = Wr      | Operations (wh<br>ites 1 word          | EILERASE DIL IS        | <u> </u>              |                       |                       |                       |

|                 |                  |                                        |                        |                       |                       |                       |                       |

#### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

Note 1: These NVMOP configurations are unimplemented on PIC24F04KL10X and PIC24F08KL20X devices.

| R/W-0        | U-0            | R/W-0            | U-0             | U-0               | U-0              | U-0             | R/W-0   |

|--------------|----------------|------------------|-----------------|-------------------|------------------|-----------------|---------|

| ULPEN        |                | ULPSIDL          | _               | —                 | _                |                 | ULPSINK |

| bit 15       |                |                  |                 |                   |                  |                 | bit 8   |

|              |                |                  |                 |                   |                  |                 |         |

| U-0          | U-0            | U-0              | U-0             | U-0               | U-0              | U-0             | U-0     |

|              |                | —                | —               |                   | —                |                 |         |

| bit 7        |                |                  |                 |                   |                  |                 | bit 0   |

| l            |                |                  |                 |                   |                  |                 | 1       |

| Legend:      |                |                  |                 |                   |                  |                 |         |

| R = Readat   | ole bit        | W = Writable     | bit             | U = Unimplem      | nented bit, read | d as '0'        |         |

| -n = Value a | at POR         | '1' = Bit is set |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

|              |                |                  |                 |                   |                  |                 |         |

| bit 15       | ULPEN: ULP     | WU Module En     | able bit        |                   |                  |                 |         |

|              | 1 = Module is  |                  |                 |                   |                  |                 |         |

|              | 0 = Module is  | disabled         |                 |                   |                  |                 |         |

| bit 14       | Unimplemen     | ted: Read as '   | כ'              |                   |                  |                 |         |

| bit 13       | ULPSIDL: UL    | PWU Stop in I    | dle Select bit  |                   |                  |                 |         |

|              |                |                  |                 | ne device enters  | s Idle mode      |                 |         |

|              | 0 = Continues  | s module opera   | tion in Idle mo | de                |                  |                 |         |

| bit 12-9     | Unimplemen     | ted: Read as '   | כ'              |                   |                  |                 |         |

| bit 8        | ULPSINK: UL    | _PWU Current     | Sink Enable bi  | t                 |                  |                 |         |

|              | 1 = Current si | ink is enabled   |                 |                   |                  |                 |         |

|              | 0 = Current si | ink is disabled  |                 |                   |                  |                 |         |

| bit 7-0      | Unimplemen     | ted: Read as '   | כ'              |                   |                  |                 |         |

|              |                |                  |                 |                   |                  |                 |         |

### REGISTER 10-1: ULPWCON: ULPWU CONTROL REGISTER

### REGISTER 16-6: CCPTMRS0: CCP TIMER SELECT CONTROL REGISTER 0<sup>(1)</sup>

| U-0              | U-0          | U-0              | U-0              | U-0               | U-0             | U-0            | U-0     |

|------------------|--------------|------------------|------------------|-------------------|-----------------|----------------|---------|

| —                | —            | —                | —                | _                 | _               | —              | —       |

| bit 15           |              |                  |                  |                   |                 |                | bit 8   |

|                  |              |                  |                  |                   |                 |                |         |

| U-0              | R/W-0        | U-0              | U-0              | R/W-0             | U-0             | U-0            | R/W-0   |

| _                | C3TSEL0      | —                | —                | C2TSEL0           | _               | —              | C1TSEL0 |

| bit 7            |              |                  |                  |                   |                 |                | bit 0   |

|                  |              |                  |                  |                   |                 |                |         |

| Legend:          |              |                  |                  |                   |                 |                |         |

| R = Readable     | e bit        | W = Writable b   | bit              | U = Unimplem      | nented bit, rea | d as '0'       |         |

| -n = Value at    | POR          | '1' = Bit is set |                  | '0' = Bit is clea | ared            | x = Bit is unk | known   |

|                  |              |                  |                  |                   |                 |                |         |

| bit 15-7         | Unimplemen   | ted: Read as '0  | )'               |                   |                 |                |         |

| bit 6            | C3TSEL0: CO  | CP3 Timer Sele   | ction bit        |                   |                 |                |         |

|                  |              | es TMR3/TMR4     |                  |                   |                 |                |         |

|                  |              | es TMR3/TMR2     |                  |                   |                 |                |         |

| bit 5-4          | •            | ted: Read as '0  |                  |                   |                 |                |         |

| bit 3            | C2TSEL0: CO  | CP2 Timer Sele   | ction bit        |                   |                 |                |         |

|                  |              | es TMR3/TMR4     |                  |                   |                 |                |         |

|                  | 0 = CCP2 use | es TMR3/TMR2     |                  |                   |                 |                |         |

|                  | 1.1          | ted: Read as '0  | )'               |                   |                 |                |         |

| bit 2-1          | Unimplemen   | teu. Reau as c   |                  |                   |                 |                |         |

| bit 2-1<br>bit 0 | -            | CP1/ECCP1 Tir    |                  | t                 |                 |                |         |

|                  | C1TSEL0: CO  |                  | ner Selection bi | t                 |                 |                |         |

Note 1: This register is unimplemented on PIC24FXXKL20X/10X devices; maintain as '0'.

| U-0             | U-0           | U-0              | U-0            | R/C-1 <sup>(1)</sup>                | R/C-1 <sup>(1)</sup>  | R/C-1 <sup>(1)</sup> | R/C-1 <sup>(1)</sup> |

|-----------------|---------------|------------------|----------------|-------------------------------------|-----------------------|----------------------|----------------------|

| _               | —             | —                | —              | BSS2                                | BSS1                  | BSS0                 | BWRP                 |

| bit 7           |               |                  |                |                                     |                       |                      | bit 0                |

| <b></b>         |               |                  |                |                                     |                       |                      |                      |

| Legend:         |               |                  |                |                                     |                       |                      |                      |

| R = Readable    | bit           | C = Clearable    | bit            | U = Unimplem                        | nented bit, read      | as '0'               |                      |

| -n = Value at F | POR           | '1' = Bit is set |                | '0' = Bit is clea                   | ared                  | x = Bit is unkn      | own                  |

|                 |               |                  |                |                                     |                       |                      |                      |

| bit 7-4         | Unimplement   | ted: Read as 'd  | )'             |                                     |                       |                      |                      |

| bit 3-1         | BSS<2:0>: Bo  | oot Segment P    | rogram Flash ( | Code Protection                     | n bits <sup>(1)</sup> |                      |                      |

|                 |               |                  |                | ory space is Ge<br>rts at 0200h, er |                       | t                    |                      |

|                 |               |                  |                | rts at 0200h, er                    |                       |                      |                      |

|                 | 100 = Reserv  | 0.0              |                |                                     |                       |                      |                      |

|                 | 011 = Reserv  | 0                | ament starts a | t 0200h, ends a                     |                       |                      |                      |

|                 |               |                  |                | t 0200h, ends a                     |                       |                      |                      |

|                 | 000 = Reserv  |                  | 0              |                                     |                       |                      |                      |

| bit 0           | BWRP: Boot    | Segment Progr    | am Flash Write | e Protection bit                    | (1)                   |                      |                      |

|                 | •             | ment may be w    |                |                                     |                       |                      |                      |

|                 | 0 = Boot Segr | ment is write-pr | otected        |                                     |                       |                      |                      |

### REGISTER 23-1: FBS: BOOT SEGMENT CONFIGURATION REGISTER

- **Note 1:** Code protection bits can only be programmed by clearing them. They can be reset to their default factory state ('1'), but only by performing a bulk erase and reprogramming the entire device.

- **2:** This selection is available only on PIC24F16KL40X devices.

### REGISTER 23-2: FGS: GENERAL SEGMENT CONFIGURATION REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/C-1 <sup>(1)</sup> | R/C-1 <sup>(1)</sup> |

|--------|-----|-----|-----|-----|-----|----------------------|----------------------|

| —      | —   | —   | —   | —   | _   | GSS0                 | GWRP                 |

| bit 7  |     |     |     |     |     |                      | bit 0                |

|        |     |     |     |     |     |                      |                      |

| Logond |     |     |     |     |     |                      |                      |

| Legend:           |                   |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | C = Clearable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-2 | Unimplemented: Read as '0' |  |

|---------|----------------------------|--|

|         |                            |  |

bit 1 **GSS0:** General Segment Code Flash Code Protection bit<sup>(1)</sup>

- 1 = No protection

- 0 = Standard security is enabled

- bit 0 **GWRP:** General Segment Code Flash Write Protection bit<sup>(1)</sup>

- 1 = General Segment may be written

- 0 = General Segment is write-protected

**Note 1:** Code protection bits can only be programmed by clearing them. They can be reset to their default factory state ('1'), but only by performing a bulk erase and reprogramming the entire device.

### REGISTER 23-5: FWDT: WATCHDOG TIMER CONFIGURATION REGISTER

| R/P-1         | R/P-1                                                                                                                                                                                   | R/P-0                    | R/P-1         | R/P-1             | R/P-1            | R/P-1           | R/P-1          |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|-------------------|------------------|-----------------|----------------|--|--|

| FWDTEN1       | WINDIS                                                                                                                                                                                  | FWDTEN0                  | FWPSA         | WDTPS3            | WDTPS2           | WDTPS1          | WDTPS0         |  |  |

| bit 7         |                                                                                                                                                                                         |                          |               |                   |                  |                 | bit 0          |  |  |

| Legend:       |                                                                                                                                                                                         |                          |               |                   |                  |                 |                |  |  |

| R = Readable  | e bit                                                                                                                                                                                   | P = Programm             | able bit      | U = Unimplem      | nented bit, read | 1 as '0'        |                |  |  |

| -n = Value at |                                                                                                                                                                                         | '1' = Bit is set         |               | '0' = Bit is clea |                  | x = Bit is unkr | iown           |  |  |

| bit 7,5       |                                                                                                                                                                                         | <b>0&gt;:</b> Watchdog T | imer Enable h | nite              |                  |                 |                |  |  |

| 5117,5        |                                                                                                                                                                                         | enabled in hard          |               | 10                |                  |                 |                |  |  |

|               |                                                                                                                                                                                         | controlled with t        |               | bit setting       |                  |                 |                |  |  |

|               |                                                                                                                                                                                         | enabled only wh          |               |                   |                  | ep, SWDTEN b    | it is disabled |  |  |

|               |                                                                                                                                                                                         | disabled in hard         |               |                   | d                |                 |                |  |  |

| bit 6         |                                                                                                                                                                                         | dowed Watchdo            | •             |                   |                  |                 |                |  |  |

|               | 1 = Standard WDT is selected; windowed WDT is disabled                                                                                                                                  |                          |               |                   |                  |                 |                |  |  |

|               | 0 = Windowed WDT is enabled; note that executing a CLRWDT instruction while the WDT is disabled<br>in hardware and software (FWDTEN<1:0> = 00 and SWDTEN (RCON<5> = 0) will not cause a |                          |               |                   |                  |                 |                |  |  |

|               | device R                                                                                                                                                                                |                          | e (i weiter)  |                   |                  |                 |                |  |  |

| bit 4         | FWPSA: WD                                                                                                                                                                               | T Prescaler bit          |               |                   |                  |                 |                |  |  |

|               | 1 = WDT pre                                                                                                                                                                             | scaler ratio of 1:       | 128           |                   |                  |                 |                |  |  |

|               | 0 = WDT pre                                                                                                                                                                             | scaler ratio of 1:       | 32            |                   |                  |                 |                |  |  |

| bit 3-0       | WDTPS<3:0>: Watchdog Timer Postscale Select bits                                                                                                                                        |                          |               |                   |                  |                 |                |  |  |

|               | 1111 = 1:32,768                                                                                                                                                                         |                          |               |                   |                  |                 |                |  |  |

|               | 1110 = 1:16,                                                                                                                                                                            |                          |               |                   |                  |                 |                |  |  |

|               | 1101 = 1:8,1<br>1100 = 1:4,0                                                                                                                                                            |                          |               |                   |                  |                 |                |  |  |

|               | 1011 = 1:2,0                                                                                                                                                                            |                          |               |                   |                  |                 |                |  |  |

|               | 1011 = 1.2,040<br>1010 = 1:1,024                                                                                                                                                        |                          |               |                   |                  |                 |                |  |  |

|               | 1001 = 1:512                                                                                                                                                                            |                          |               |                   |                  |                 |                |  |  |

|               | 1000 = 1:256                                                                                                                                                                            |                          |               |                   |                  |                 |                |  |  |

|               | 0111 = 1:128<br>0110 = 1:64                                                                                                                                                             | 5                        |               |                   |                  |                 |                |  |  |

|               | 0101 = 1:32                                                                                                                                                                             |                          |               |                   |                  |                 |                |  |  |

|               | 0100 = 1:16                                                                                                                                                                             |                          |               |                   |                  |                 |                |  |  |

|               | 0011 = 1:8                                                                                                                                                                              |                          |               |                   |                  |                 |                |  |  |

|               | 0010 = 1:4                                                                                                                                                                              |                          |               |                   |                  |                 |                |  |  |

|               | 0001 <b>= 1:2</b>                                                                                                                                                                       |                          |               |                   |                  |                 |                |  |  |

### TABLE 25-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Assembly<br>Mnemonic | Assembly Syntax |              | Description                             | # of<br>Words | # of<br>Cycles                                                                | Status Flags<br>Affected |

|----------------------|-----------------|--------------|-----------------------------------------|---------------|-------------------------------------------------------------------------------|--------------------------|

| PWRSAV               | PWRSAV          | #lit1        | Go into Sleep or Idle mode              | 1             | 1                                                                             | WDTO, Sleep              |

| RCALL                | RCALL           | Expr         | Relative Call                           | 1             | 2                                                                             | None                     |

|                      | RCALL           | Wn           | Computed Call                           | 1             | 2                                                                             | None                     |

| REPEAT               | REPEAT          | #lit14       | Repeat Next Instruction lit14 + 1 times | 1             | 1                                                                             | None                     |

|                      | REPEAT          | Wn           | Repeat Next Instruction (Wn) + 1 times  | 1             | 1                                                                             | None                     |

| RESET                | RESET           |              | Software Device Reset                   | 1             | 1                                                                             | None                     |

| RETFIE               | RETFIE          |              | Return from Interrupt                   | 1             | 3 (2)                                                                         | None                     |

| RETLW                | RETLW           | #lit10,Wn    | Return with Literal in Wn               | 1             | 3 (2)                                                                         | None                     |

| RETURN               | RETURN          |              | Return from Subroutine                  | 1             | 3 (2)                                                                         | None                     |

| RLC                  | RLC             | f            | f = Rotate Left through Carry f         | 1             | 1                                                                             | C, N, Z                  |

|                      | RLC             | f,WREG       | WREG = Rotate Left through Carry f      | 1             | 1                                                                             | C, N, Z                  |

|                      | RLC             | Ws,Wd        | Wd = Rotate Left through Carry Ws       | 1             | 1                                                                             | C, N, Z                  |

| RLNC                 | RLNC            | f            | f = Rotate Left (No Carry) f            | 1             | 1                                                                             | N, Z                     |

|                      | RLNC            | f,WREG       | WREG = Rotate Left (No Carry) f         | 1             | 1                                                                             | N, Z                     |

|                      | RLNC            | Ws,Wd        | Wd = Rotate Left (No Carry) Ws          | 1             | 1                                                                             | N, Z                     |

| RRC                  | RRC             | f            | f = Rotate Right through Carry f        | 1             | 1                                                                             | C, N, Z                  |

|                      | RRC             | f,WREG       | WREG = Rotate Right through Carry f     | 1             | 1                                                                             | C, N, Z                  |

|                      | RRC             | Ws,Wd        | Wd = Rotate Right through Carry Ws      | 1             | 1                                                                             | C, N, Z                  |

| RRNC                 | RRNC            | f            | f = Rotate Right (No Carry) f           | 1             | 1                                                                             | N, Z                     |

|                      | RRNC            | f,WREG       | WREG = Rotate Right (No Carry) f        | 1             | 1                                                                             | N, Z                     |

|                      | RRNC            | Ws,Wd        | Wd = Rotate Right (No Carry) Ws         | 1             | 1                                                                             | N, Z                     |

| SE                   | SE              | Ws,Wnd       | Wnd = Sign-Extended Ws                  | 1             | 1                                                                             | C, N, Z                  |

| SETM                 | SETM            | f            | f = FFFFh                               | 1             | 1                                                                             | None                     |

|                      | SETM            | WREG         | WREG = FFFFh                            | 1             | 1         1           1         1           1         1           1         1 | None                     |

|                      | SETM            | Ws           | Ws = FFFFh                              | 1             | 1                                                                             | None                     |

| SL                   | SL              | f            | f = Left Shift f                        |               |                                                                               | C, N, OV, Z              |

|                      | SL              | f,WREG       | WREG = Left Shift f                     | 1             | 1                                                                             | C, N, OV, Z              |

|                      | SL              | Ws,Wd        | Wd = Left Shift Ws                      | 1             | 1                                                                             | C, N, OV, Z              |

|                      | SL              | Wb,Wns,Wnd   | Wnd = Left Shift Wb by Wns              | 1             | 1                                                                             | N, Z                     |

|                      | SL              | Wb,#lit5,Wnd | Wnd = Left Shift Wb by lit5             | 1             | 1                                                                             | N, Z                     |

| SUB                  | SUB             | f            | f = f – WREG                            | 1             | 1                                                                             | C, DC, N, OV,            |

|                      | SUB             | f,WREG       | WREG = f – WREG                         | 1             | 1                                                                             | C, DC, N, OV,            |

|                      | SUB             | #lit10,Wn    | Wn = Wn - lit10                         | 1             | 1                                                                             | C, DC, N, OV, 2          |

|                      | SUB             | Wb,Ws,Wd     | Wd = Wb – Ws                            | 1             | 1                                                                             | C, DC, N, OV,            |

|                      | SUB             | Wb,#lit5,Wd  | Wd = Wb – lit5                          | 1             | 1                                                                             | C, DC, N, OV,            |

| SUBB                 | SUBB            | f            | $f = f - WREG - (\overline{C})$         | 1             | 1                                                                             | C, DC, N, OV, 2          |

| SUBB                 |                 |              | $WREG = f - WREG - (\overline{C})$      | 1             | 1                                                                             |                          |

|                      | SUBB            | f,WREG       |                                         |               |                                                                               | C, DC, N, OV, 2          |

|                      | SUBB            | #lit10,Wn    | Wn = Wn – lit10 – (C)                   | 1             | 1                                                                             | C, DC, N, OV,            |

|                      | SUBB            | Wb,Ws,Wd     | Wd = Wb - Ws - (C)                      | 1             | 1                                                                             | C, DC, N, OV, 2          |

|                      | SUBB            | Wb,#lit5,Wd  | Wd = Wb - lit5 - (C)                    | 1             | 1                                                                             | C, DC, N, OV,            |

| SUBR                 | SUBR            | f            | f = WREG – f                            | 1             | 1                                                                             | C, DC, N, OV,            |

|                      | SUBR            | f,WREG       | WREG = WREG – f                         | 1             | 1                                                                             | C, DC, N, OV,            |

|                      | SUBR            | Wb,Ws,Wd     | Wd = Ws – Wb                            | 1             | 1                                                                             | C, DC, N, OV,            |

|                      | SUBR            | Wb,#lit5,Wd  | Wd = lit5 - Wb                          | 1             | 1                                                                             | C, DC, N, OV,            |

| SUBBR                | SUBBR           | f            | $f = WREG - f - (\overline{C})$         | 1             | 1                                                                             | C, DC, N, OV, 2          |

|                      | SUBBR           | f,WREG       | WREG = WREG – f – $(\overline{C})$      | 1             | 1                                                                             | C, DC, N, OV,            |

|                      | SUBBR           | Wb,Ws,Wd     | $Wd = Ws - Wb - (\overline{C})$         | 1             | 1                                                                             | C, DC, N, OV,            |

|                      | SUBBR           | Wb,#lit5,Wd  | $Wd = lit5 - Wb - (\overline{C})$       | 1             | 1                                                                             | C, DC, N, OV,            |

| SWAP                 | SWAP.b          | Wn           | Wn = Nibble Swap Wn                     | 1             | 1                                                                             | None                     |

|                      | SWAP            | Wn           | Wn = Byte Swap Wn                       | 1             | 1                                                                             | None                     |

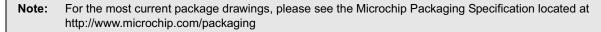

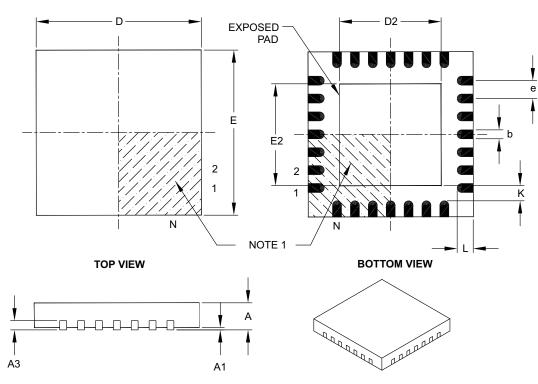

#### TABLE 26-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                  | Symbol | Min | Тур         | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| Operating Junction Temperature Range                                                                                                                                                    | ТJ     | -40 | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                     | TA     | -40 | _           | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$PI/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     |     | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                       | PDMAX  | (   | TJ — TA)/θ. | IA   | W    |

### TABLE 26-2: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур  | Max | Unit | Notes |

|------------------------------------------|--------|------|-----|------|-------|

| Package Thermal Resistance, 20-Pin PDIP  | θJA    | 62.4 | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP | θJA    | 60   |     | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SSOP  | θJA    | 108  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP  | θJA    | 71   | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SOIC  | θJA    | 75   | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC  | θJA    | 80.2 | -   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin QFN   | θJA    | 43   | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN   | θJA    | 32   | _   | °C/W | 1     |

| Package Thermal Resistance, 14-Pin PDIP  | θJA    | 62.4 | -   | °C/W | 1     |

| Package Thermal Resistance, 14-Pin TSSOP | θJA    | 108  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

#### TABLE 26-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CH         | ARACTER | $ \begin{array}{ll} \mbox{Standard Operating Conditions: } 1.8V \ to \ 3.6V \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \ for \ Industrial \\ -40^\circ C \leq TA \leq +125^\circ C \ for \ Extended \\ \end{array} $ |      |                    |      |       |                                   |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|-------|-----------------------------------|

| Para<br>m No. | Symbol  | Characteristic                                                                                                                                                                                                                                   | Min  | Typ <sup>(1)</sup> | Max  | Units | Conditions                        |

| DC10          | Vdd     | Supply Voltage                                                                                                                                                                                                                                   | 1.8  | —                  | 3.6  | V     |                                   |

| DC12          | Vdr     | RAM Data Retention<br>Voltage <sup>(2)</sup>                                                                                                                                                                                                     | 1.5  | —                  | —    | V     |                                   |