Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

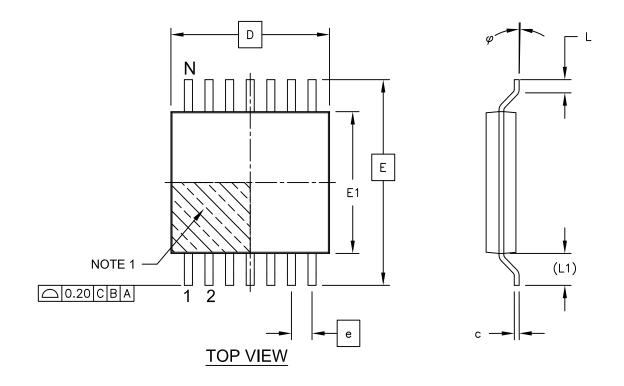

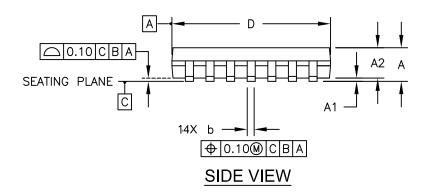

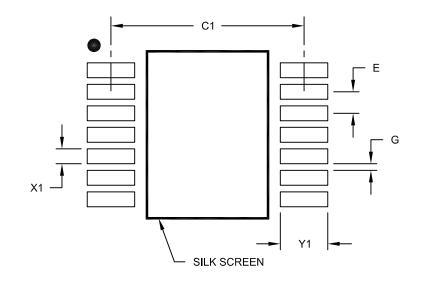

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VFQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (5x5)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16kl402-e-mq |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2 Other Special Features

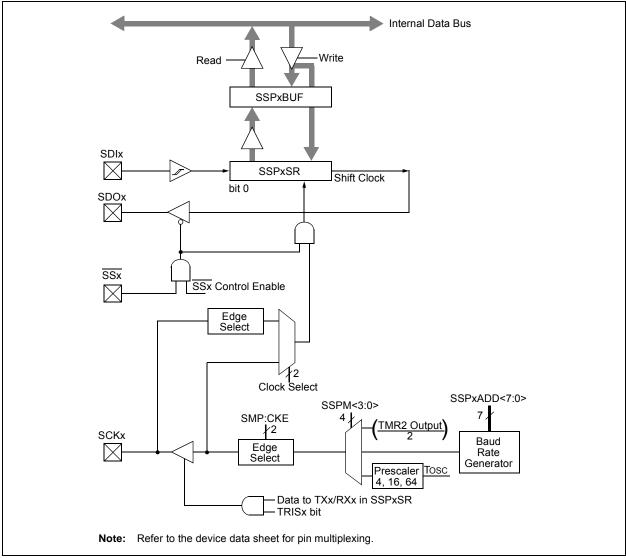

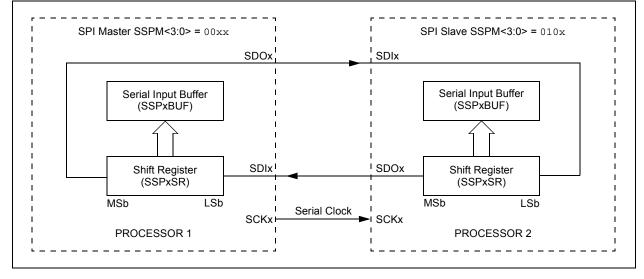

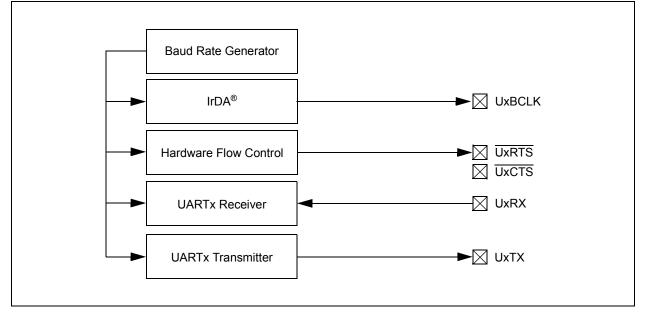

- Communications: The PIC24F16KL402 family incorporates multiple serial communication peripherals to handle a range of application requirements. The MSSP module implements both SPI and I<sup>2</sup>C™ protocols, and supports both Master and Slave modes of operation for each. Devices also include one of two UARTs with built-in IrDA<sup>®</sup> encoders/decoders.

- Analog Features: Select members of the PIC24F16KL402 family include a 10-bit A/D Converter module. The A/D module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, as well as faster sampling speeds.

The comparator modules are configurable for a wide range of operations and can be used as either a single or double comparator module.

## 1.3 Details on Individual Family Members

Devices in the PIC24F16KL402 family are available in 14-pin, 20-pin and 28-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The PIC24F16KL402 family may be thought of as four different device groups, each offering a slightly different set of features. These differ from each other in multiple ways:

- · The size of the Flash program memory

- The presence and size of data EEPROM

- The presence of an A/D Converter and the number of external analog channels available

- · The number of analog comparators

- The number of general purpose timers

- The number and type of CCP modules (i.e., CCP vs. ECCP)

- The number of serial communications modules (both MSSPs and UARTs)

The general differences between the different sub-families are shown in Table 1-1. The feature sets for specific devices are summarized in Table 1-2 and Table 1-3.

A list of the individual pin features available on the PIC24F16KL402 family devices, sorted by function, is provided in Table 1-4 (for PIC24FXXKL40X/30X devices) and Table 1-5 (for PIC24FXXKL20X/10X devices). Note that these tables show the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

| Device Group  | Program<br>Memory<br>(bytes) | Data<br>EEPROM<br>(bytes) | Timers<br>(8/16-bit) | CCP and<br>ECCP | Serial<br>(MSSP/<br>UART) | A/D<br>(channels) | Comparators |

|---------------|------------------------------|---------------------------|----------------------|-----------------|---------------------------|-------------------|-------------|

| PIC24FXXKL10X | 4K                           | _                         | 1/2                  | 2/0             | 1/1                       | _                 | 1           |

| PIC24FXXKL20X | 8K                           | —                         | 1/2                  | 2/0             | 1/1                       | 7 or 12           | 1           |

| PIC24FXXKL30X | 8K                           | 256                       | 2/2                  | 2/1             | 2/2                       | —                 | 2           |

| PIC24FXXKL40X | 8K or 16K                    | 512                       | 2/2                  | 2/1             | 2/2                       | 12                | 2           |

#### TABLE 1-1:FEATURE COMPARISON FOR PIC24F16KL402 FAMILY GROUPS

# 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                    | U-0                  | U-0                                        | U-0            | U-0                            | U-0                          | U-0               | R/W-0          |

|------------------------|----------------------|--------------------------------------------|----------------|--------------------------------|------------------------------|-------------------|----------------|

|                        | _                    | _                                          | _              | _                              | _                            | _                 | DC             |

| bit 15                 |                      | I I                                        |                |                                |                              |                   | bit            |

| R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                       | R-0            | R/W-0                          | R/W-0                        | R/W-0             | R/W-0          |

| IPL2 <sup>(2)</sup>    | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>                        | RA             | N                              | OV                           | Z                 | C              |

| bit 7                  |                      | 20                                         |                |                                | 0.                           | _                 | bit            |

|                        |                      |                                            |                |                                |                              |                   |                |

| Legend:<br>R = Readabl | e hit                | W = Writable b                             | it             | II = I Inimplem                | nented bit, read             | d as 'O'          |                |

| -n = Value at          |                      | '1' = Bit is set                           | iii iii        | '0' = Bit is clea              |                              | x = Bit is unkr   | NOWD           |

|                        |                      |                                            |                |                                |                              |                   |                |

| bit 15-9               | Unimplemen           | ted: Read as '0                            | ,              |                                |                              |                   |                |

| bit 8                  | -                    | f Carry/Borrow b                           |                |                                |                              |                   |                |

|                        |                      | -                                          |                | (for byte-sized da             | ata) or 8 <sup>th</sup> Iow- | order bit (for wo | ord-sized dat  |

|                        | of the res           | sult occurred                              |                |                                |                              |                   |                |

|                        | •                    |                                            |                | rder bit of the res            |                              | ed                |                |

| bit 7-5                | IPL<2:0>: CF         | PU Interrupt Prio                          | rity Level (IP | L) Status bits <sup>(1,2</sup> | 2)                           |                   |                |

|                        |                      |                                            |                | 5); user interrupt             | s disabled                   |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I<br>nterrupt Priority I | •              | ,                              |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

|                        |                      | nterrupt Priority I                        |                |                                |                              |                   |                |

| bit 4                  | <b>RA:</b> REPEAT    | Loop Active bit                            |                |                                |                              |                   |                |

|                        |                      | oop in progress                            |                |                                |                              |                   |                |

|                        |                      | oop not in progr                           | ess            |                                |                              |                   |                |

| bit 3                  | N: ALU Nega          |                                            |                |                                |                              |                   |                |

|                        | 1 = Result wa        | 0                                          | (              | 4:                             |                              |                   |                |

|                        |                      | as non-negative                            | (zero or posi  | tive)                          |                              |                   |                |

| bit 2                  | OV: ALU Ove          |                                            |                |                                |                              |                   |                |

|                        |                      | occurred for sig                           |                | plement) arithm                | etic in this arith           | imetic operation  | n              |

| bit 1                  | <b>Z:</b> ALU Zero   |                                            |                |                                |                              |                   |                |

|                        |                      |                                            | te the 7 hit 4 | nas set it at some             | e time in the n              | aet               |                |

|                        |                      |                                            |                | cts the Z bit, has             |                              |                   | sult)          |

| bit 0                  | C: ALU Carry         |                                            | ,              | ,,                             |                              | ,                 | -7             |

| ~                      |                      |                                            | Significant b  | oit (MSb) of the r             | esult occurred               |                   |                |

|                        |                      |                                            |                | bit (MSb) of the               |                              |                   |                |

| Note 1: Th             | ne IPI. Status hi    | ts are read-only                           | when NSTD      | IS (INTCON1<1                  | 5>) = 1                      |                   |                |

|                        |                      |                                            |                | IPL3 bit (CORC                 |                              | m the CPU I Into  | rrunt Priority |

| <b>2</b> .             |                      |                                            |                |                                |                              |                   | in april nonty |

2: The IPL Status bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

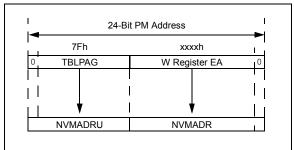

## 6.3 NVM Address Register

As with Flash program memory, the NVM Address Registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space; instead, they directly capture the EA<23:0> of the last Table Write instruction that has been executed and selects the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", is unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

#### FIGURE 6-1: DATA EEPROM ADDRESSING WITH TBLPAG AND NVM ADDRESS REGISTERS

## 6.4 Data EEPROM Operations

The EEPROM block is accessed using Table Read and Table Write operations, similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- Bulk erase the entire data EEPROM

- Write one word

- Read one word

| Note: | Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | The C30 C compiler includes library<br>procedures to automatically perform the<br>Table Read and Table Write operations,<br>manage the Table Pointer and write<br>buffers, and unlock and initiate memory<br>write sequences. This eliminates the need<br>to create assembler macros or time<br>critical routines in C for each application. |

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the C30 compiler libraries.

## 7.4.2 DETECTING BOR

When BOR is enabled, the BOR bit (RCON<1>) is always reset to '1' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR and BOR bits are reset to '0' in the software, immediately after any POR event. If the BOR bit is '1' while POR is '0', it can be reliably assumed that a BOR event has occurred.

**Note:** Even when the device exits from Deep Sleep mode, both the POR and BOR are set.

#### 7.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, BOR remains under hardware control and operates as previously described. However, whenever the device enters Sleep mode, BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

# 8.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Interrupt Controller, refer to the "dsPIC33/PIC24 Family Reference Manual", "Interrupts" (DS39707).

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. It has the following features:

- Up to eight processor exceptions and software traps

- · Seven user-selectable priority levels

- · Interrupt Vector Table (IVT) with up to 118 vectors

- Unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

## 8.1 Interrupt Vector Table (IVT)

The IVT is shown in Figure 8-1. The IVT resides in the program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of eight non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

PIC24F16KL402 family devices implement 32 non-maskable traps and unique interrupts; these are summarized in Table 8-1 and Table 8-2.

#### 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE (AIVT)

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

## 8.2 Reset Sequence

A device Reset is not a true exception, because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset, which forces the Program Counter (PC) to zero. The microcontroller then begins program execution at location, 000000h. The user programs a GOTO instruction at the Reset address, which redirects the program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| U-0          | U-0             | U-0              | U-0              | U-0                  | U-0                   | U-0             | R/W-0  |

|--------------|-----------------|------------------|------------------|----------------------|-----------------------|-----------------|--------|

|              | —               |                  | —                | —                    | —                     | —               | HLVDIF |

| bit 15       |                 |                  |                  |                      |                       |                 | bit 8  |

|              |                 |                  |                  |                      |                       |                 |        |

| U-0          | U-0             | U-0              | U-0              | U-0                  | R/W-0                 | R/W-0           | U-0    |

|              |                 |                  |                  |                      | U2ERIF <sup>(1)</sup> | U1ERIF          |        |

| bit 7        |                 |                  |                  |                      |                       |                 | bit 0  |

|              |                 |                  |                  |                      |                       |                 |        |

| Legend:      |                 |                  |                  |                      |                       |                 |        |

| R = Readal   | ble bit         | W = Writable     | bit              | U = Unimplem         | nented bit, read      | l as '0'        |        |

| -n = Value a | at POR          | '1' = Bit is set |                  | '0' = Bit is clea    | ared                  | x = Bit is unkn | iown   |

|              |                 |                  |                  |                      |                       |                 |        |

| bit 15-9     | Unimplemen      | ted: Read as '   | 0'               |                      |                       |                 |        |

| bit 8        | HLVDIF: High    | n/Low-Voltage [  | Detect Interrupt | t Flag Status bit    | t                     |                 |        |

|              |                 | request has occ  |                  |                      |                       |                 |        |

|              | 0 = Interrupt i | request has not  | t occurred       |                      |                       |                 |        |

| bit 7-3      | Unimplemen      | ted: Read as '   | 0'               |                      |                       |                 |        |

| bit 2        | U2ERIF: UAF     | RT2 Error Interr | upt Flag Status  | s bit <sup>(1)</sup> |                       |                 |        |

|              |                 | request has occ  |                  |                      |                       |                 |        |

|              | 0 = Interrupt i | request has not  | t occurred       |                      |                       |                 |        |

| bit 1        | U1ERIF: UAF     | RT1 Error Interr | upt Flag Status  | s bit                |                       |                 |        |

|              |                 | request has occ  |                  |                      |                       |                 |        |

|              |                 | request has not  |                  |                      |                       |                 |        |

| bit 0        | Unimplemen      | ted: Read as '   | 0'               |                      |                       |                 |        |

#### REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

Note 1: This bit is unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

## REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0                                                    | U-0   | U-0          | U-0 | U-0          | U-0              | U-0      | U-0     |

|--------------------------------------------------------|-------|--------------|-----|--------------|------------------|----------|---------|

| _                                                      | —     | _            | —   | —            | —                | —        | —       |

| bit 15                                                 |       |              |     |              |                  |          | bit 8   |

|                                                        |       |              |     |              |                  |          |         |

| U-0                                                    | U-0   | U-0          | U-0 | U-0          | U-0              | U-0      | R/W-0   |

| —                                                      | —     | —            | —   | —            | —                | —        | ULPWUIF |

| bit 7                                                  |       |              |     |              |                  |          | bit 0   |

|                                                        |       |              |     |              |                  |          |         |

| Legend:                                                |       |              |     |              |                  |          |         |

| R = Readable                                           | e bit | W = Writable | bit | U = Unimplem | nented bit, read | l as '0' |         |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleare |       |              |     | ared         | x = Bit is unkr  | nown     |         |

|                                                        |       |              |     |              |                  |          | nown    |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7   | CLKLOCK: Clock Selection Lock Enable bit                                                 |

|---------|------------------------------------------------------------------------------------------|

|         | <u>If FSCM is Enabled (FCKSM1 = 1):</u>                                                  |

|         | 1 = Clock and PLL selections are locked                                                  |

|         | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit |

|         | If FSCM is Disabled (FCKSM1 = 0):                                                        |

|         | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.  |

| bit 6   | Unimplemented: Read as '0'                                                               |

| bit 5   | LOCK: PLL Lock Status bit <sup>(2)</sup>                                                 |

|         | 1 = PLL module is in lock or the PLL module start-up timer is satisfied                  |

|         | 0 = PLL module is out of lock, the PLL start-up timer is running or PLL is disabled      |

| bit 4   | Unimplemented: Read as '0'                                                               |

| bit 3   | CF: Clock Fail Detect bit                                                                |

|         | 1 = FSCM has detected a clock failure                                                    |

|         | 0 = No clock failure has been detected                                                   |

| bit 2   | SOSCDRV: Secondary Oscillator Drive Strength bit <sup>(3)</sup>                          |

|         | 1 = High-power SOSC circuit is selected                                                  |

|         | 0 = Low/high-power select is done via the SOSCSRC Configuration bit                      |

| bit 1   | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                    |

|         | 1 = Enables secondary oscillator                                                         |

|         | 0 = Disables secondary oscillator                                                        |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                      |

|         | 1 = Initiates an oscillator switch to the clock source specified by the NOSC<2:0> bits   |

|         | 0 = Oscillator switch is complete                                                        |

| Note 1: | Reset values for these bits are determined by the FNOSC<2:0> Configuration bits.         |

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- **3:** When SOSC is selected to run from a digital clock input rather than an external crystal (SOSCSRC = 0), this bit has no effect.

## 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

Note: The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 23.0** "**Special Features**" for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically, as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM, with LPRC as a clock source, are enabled) or SOSC (if SOSCEN remains enabled).

Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

#### REGISTER 9-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REGISTER      | 9-4: REFU                                                                                                                                                                                                                     | CON: REFER                                                                                                                                                                                                                                                                                                                   | KENCE USC                                                                                                                                                                              | ILLATOR CC        | INTROL REC       | 515TER          |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|---------------|

| bit 15       bit 5         U-0       U-0       U-0       U-0       U-0       U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0         | U-0                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                  | R/W-0             | R/W-0            | R/W-0           | R/W-0         |

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ROEN          | —                                                                                                                                                                                                                             | ROSSLP                                                                                                                                                                                                                                                                                                                       | ROSEL                                                                                                                                                                                  | RODIV3            | RODIV2           | RODIV1          | RODIV0        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 15        |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 | bit 8         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 |               |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       0       = Reference oscillator output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference oscillator is disabled in Sleep       0 = Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )       0 = System clock is used as the base clock ( <sup>11</sup> )         111 = Base clock value divid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0           | 0-0                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                    | 0-0               | 0-0              | 0-0             | U-0           |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       1 = Reference oscillator continues to run in Sleep       0 = Reference oscillator continues to run in Sleep         0 = Reference oscillator is disabled in Sleep       0 = Reference oscillator is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)       0 = System clock is used as the base clock (*1)         111 = Base clock value divided by 32,768       1100 = Base clock value divided by 4,966         1101 = Base clock value divided by 4,096       1011 = Base clock value divided by 1,024         1000 = Base clock value divided by 1,024       1001 = Base clock value divided by 128         0111 = Base clock value di                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                                                                                                                                                                                                                               | _                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                        | _                 | _                | _               |               |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       0'       Bit 13       ROSSLP: Reference Oscillator Output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference Oscillator Source Select bit       1 = Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock (*1)       0 = System clock is used as the base clock reflects any clock switching of the device         bit 11-8       RODIV-3:0>: Reference Oscillator Divisor Select bits       1111 = Base clock value divided by 32,768         1110 = Base clock value divided by 10:       100 = Base clock value divided by 10:       100 = Base clock value divided by 2,048         1011 = Base clock value divided by 20:       100 = Base clock value divided by 256       111 = Base clock value divided by 22:         0100 = Base clock value divided by 10:       011 = Base clock value divided by 10:       011 = Base clock value divided by 12:         0100 = Base clock value divided by 10:       011 = Base clock value divided by 10:       011 = Base clock value divided by 20:         0100 = Base clock value divided by 10:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 | DILU          |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       1       ROSSLP: Reference Oscillator Output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference Oscillator Source Select bit       1 = Reference oscillator is used as the base clock '1)         0 = System clock is used as the base clock '10       0 = System clock value divided by 32,768       1111 = Base clock value divided by 4,096         1111 = Base clock value divided by 10,384       100 = Base clock value divided by 1,024       100 = Base clock value divided by 1,024         100 = Base clock value divided by 128       010 = Base clock value divided by 128       010 = Base clock value divided by 128         010 = Base clock value divided by 16       011 = Base clock value divided by 128       010 = Base clock value divided by 128         010 = Base clock value divided by 16       011 = Base clock value divided by 16       011 = Base clock value divided by 128         010 = Base clock value divided by 16       011 = Base clock value divided by 18       010 = Base clock value divided by 18         010 = Base clock value divided by 16       011 = Base clock value divided by 16       011 = Base clock value divided by 18         010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Legend:       |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        |                   |                  |                 |               |

| bit 15 <b>ROEN:</b> Reference Oscillator Output Enable bit<br>1 = Reference oscillator is enabled on REFO pin<br>0 = Reference oscillator is disabled<br>bit 14 <b>Unimplemented:</b> Read as '0'<br>bit 13 <b>ROSSLP:</b> Reference Oscillator Output Stop in Sleep bit<br>1 = Reference oscillator continues to run in Sleep<br>0 = Reference oscillator is disabled in Sleep<br>bit 12 <b>ROSEL:</b> Reference Oscillator Source Select bit<br>1 = Primary oscillator is used as the base clock <sup>(1)</sup><br>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br>bit 11-8 <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 22,768<br>1110 = Base clock value divided by 4,192<br>1100 = Base clock value divided by 4,192<br>1100 = Base clock value divided by 1,192<br>1100 = Base clock value divided by 1,024<br>1011 = Base clock value divided by 1,28<br>0110 = Base clock value divided by 2,208<br>0110 = Base clock value divided by 1,28<br>0110 = Base clock value divided by 2,208<br>0110 = Base clock | R = Readabl   | le bit                                                                                                                                                                                                                        | W = Writable I                                                                                                                                                                                                                                                                                                               | oit                                                                                                                                                                                    | U = Unimplen      | nented bit, read | d as '0'        |               |

| <ul> <li>1 = Reference oscillator is enabled on REFO pin<br/>0 = Reference oscillator is disabled</li> <li>bit 14 Unimplemented: Read as '0'</li> <li>bit 13 ROSSLP: Reference Oscillator Output Stop in Sleep bit<br/>1 = Reference oscillator is disabled in Sleep<br/>0 = Reference oscillator is disabled in Sleep</li> <li>bit 12 ROSEL: Reference Oscillator Source Select bit<br/>1 = Primary oscillator is used as the base clock<sup>(1)</sup><br/>0 = System clock is used as the base clock (1)<br/>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br/>bit 11-8 RODIV-3:0&gt;: Reference Oscillator Divisor Select bits</li> <li>111 = Base clock value divided by 32,768</li> <li>1110 = Base clock value divided by 8,192</li> <li>1100 = Base clock value divided by 4,096</li> <li>1011 = Base clock value divided by 1,024</li> <li>1001 = Base clock value divided by 512</li> <li>1000 = Base clock value divided by 256</li> <li>0111 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 260</li> <li>011 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 28</li> <li>010 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 26</li> <li>010 = Base clock value divided by 40</li> <li>011 = Base clock value divided by 26</li> <li>010 = Base clock value divided by 26</li> <li>010 = Base clock value divided by 20</li> <li>010 = Bas</li></ul>                                                                                  | -n = Value at | t POR                                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                        | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |

| 1 = Reference oscillator continues to run in Sleep         0 = Reference oscillator is disabled in Sleep         bit 12 <b>ROSEL:</b> Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock; the base clock reflects any clock switching of the device         bit 11-8 <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits         111 = Base clock value divided by 32,768         110 = Base clock value divided by 16,384         100 = Base clock value divided by 4,096         1011 = Base clock value divided by 1,024         1001 = Base clock value divided by 1,024         1001 = Base clock value divided by 128         110 = Base clock value divided by 128         111 = Base clock value divided by 32         100 = Base clock value divided by 4         101 = Base clock value divided by 128         110 = Base clock value divided by 32         110 = Base clock value divided by 32         110 = Base clock value divided by 16         111 = Base clock value divided by 16 </td <td></td> <td>1 = Reference<br/>0 = Reference</td> <td>e oscillator is er<br/>e oscillator is di</td> <td>nabled on REF<br/>sabled</td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               | 1 = Reference<br>0 = Reference                                                                                                                                                                                                | e oscillator is er<br>e oscillator is di                                                                                                                                                                                                                                                                                     | nabled on REF<br>sabled                                                                                                                                                                |                   |                  |                 |               |

| 1 = Reference oscillator continues to run in Sleep         0 = Reference oscillator is disabled in Sleep         bit 12 <b>ROSEL:</b> Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock; the base clock reflects any clock switching of the device         bit 11-8 <b>RODIV-3:0&gt;:</b> Reference Oscillator Divisor Select bits         1111 = Base clock value divided by 32,768         1100 = Base clock value divided by 16,384         1101 = Base clock value divided by 4,096         1011 = Base clock value divided by 1,024         1001 = Base clock value divided by 1,024         1001 = Base clock value divided by 1,024         1001 = Base clock value divided by 128         0110 = Base clock value divided by 128         0110 = Base clock value divided by 32         0101 = Base clock value divided by 32         0100 = Base clock value divided by 32         0101 = Base clock value divided by 40         011 = Base clock value divided by 16         0111 = Base clock va                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 13        | -                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        | o in Sleep bit    |                  |                 |               |

| bit 12 ROSEL: Reference Oscillator Source Select bit<br>1 = Primary oscillator is used as the base clock <sup>(1)</sup><br>0 = System clock is used as the base clock; the base clock reflects any clock switching of the device<br>bit 11-8 RODIV<3:0>: Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 32,768<br>1110 = Base clock value divided by 4,096<br>1011 = Base clock value divided by 4,096<br>1011 = Base clock value divided by 2,048<br>1010 = Base clock value divided by 1,024<br>1001 = Base clock value divided by 512<br>1000 = Base clock value divided by 256<br>0111 = Base clock value divided by 128<br>0110 = Base clock value divided by 32<br>1000 = Base clock value divided by 44<br>011 = Base clock value divided by 32<br>0100 = Base clock value divided by 4<br>011 = Base clock value divided by 4<br>010 = Base clock value divided by 266<br>0111 = Base clock value divided by 4<br>0101 = Base clock value divided by 4<br>0101 = Base clock value divided by 4<br>0101 = Base clock value divided by 32<br>0100 = Base clock value divided by 4<br>001 = Base clock value divided by 2<br>000 = Base clock value divided by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                                                      | -                 |                  |                 |               |