# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 28-SPDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16kl402-e-sp |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24F04KL100 PIC24F04KL101

- PIC24F08KL200

- PIC24F08KL201PIC24F08KL302

- PIC24F08KL301

PIC24F08KL401

- PIC24F16KL401

- PIC24F08KL402 PIC24F16KL402

The PIC24F16KL402 family adds an entire range of economical, low pin count and low-power devices to Microchip's portfolio of 16-bit microcontrollers. Aimed at applications that require low-power consumption but more computational ability than an 8-bit platform can provide, these devices offer a range of tailored peripheral sets that allow the designer to optimize both price point and features with no sacrifice of functionality.

### 1.1 Core Features

#### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> digital signal controllers. The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 64 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32-bit by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as C

- Operational performance up to 16 MIPS

#### 1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24F16KL402 family incorporate a range of features that can significantly reduce power consumption during operation. Key features include:

• **On-the-Fly Clock Switching:** The device clock can be changed under software control to the Timer1 source, or the internal, Low-Power RC (LPRC) oscillator during operation, allowing the user to incorporate power-saving ideas into their software designs.

- **Doze Mode Operation:** When timing-sensitive applications, such as serial communications, require the uninterrupted operation of peripherals, the CPU clock speed can be selectively reduced, allowing incremental power savings without missing a beat.

- Instruction-Based Power-Saving Modes: The microcontroller can suspend all operations, or selectively shut down its core while leaving its peripherals active, with a single instruction in software.

### 1.1.3 OSCILLATOR OPTIONS AND FEATURES

The PIC24F16KL402 family offers five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes using crystals or ceramic resonators.

- Two External Clock modes offering the option of a divide-by-2 clock output.

- Two Fast Internal Oscillators (FRCs): One with a nominal 8 MHz output and the other with a nominal 500 kHz output. These outputs can also be divided under software control to provide clock speed as low as 31 kHz or 2 kHz.

- A Phase Locked Loop (PLL) frequency multiplier, available to the External Oscillator modes and the 8 MHz FRC Oscillator, which allows clock speeds of up to 32 MHz.

- A separate Internal RC Oscillator (LPRC) with a fixed 31 kHz output, which provides a low-power option for timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

### 1.1.4 EASY MIGRATION

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, or even jumping from 20-pin or 28-pin devices to 44-pin/48-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow, from the relatively simple, to the powerful and complex.

| TABLE 1-3: DEVICE FEATURES FOR THE PIC24F16KL20X/10X DEVICE |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| TABLE 1-5. DEVICE FEATOR                            |                                      |                        |                                                             |               |

|-----------------------------------------------------|--------------------------------------|------------------------|-------------------------------------------------------------|---------------|

| Features                                            | PIC24F08KL201                        | PIC24F04KL101          | PIC24F08KL200                                               | PIC24F04KL100 |

| Operating Frequency                                 |                                      | DC – 3                 | 2 MHz                                                       |               |

| Program Memory (bytes)                              | 8K                                   | 4K                     | 8K                                                          | 4K            |

| Program Memory (instructions)                       | 2816                                 | 1408                   | 2816                                                        | 1408          |

| Data Memory (bytes)                                 | 512                                  | 512                    | 512                                                         | 512           |

| Data EEPROM Memory (bytes)                          |                                      | —                      | —                                                           | —             |

| Interrupt Sources<br>(soft vectors/NMI traps)       | 27 (23/4)                            | 26 (22/4)              | 27 (23/4)                                                   | 26 (22/4)     |

| I/O Ports                                           | PORTA<6:0><br>PORTB<15:12,9:7,4,2:0> |                        | PORT/<br>PORTB<15                                           |               |

| Total I/O Pins                                      | 1                                    | 7                      | 1                                                           | 2             |

| Timers (8/16-bit)                                   | 1/2                                  | 1/2                    | 1/2                                                         | 1/2           |

| Capture/Compare/PWM modules:                        |                                      |                        |                                                             |               |

| Total                                               | 2                                    | 2                      | 2                                                           | 2             |

| Enhanced CCP                                        | 0                                    | 0                      | 0                                                           | 0             |

| Input Change Notification Interrupt                 | 17                                   | 17                     | 11                                                          | 11            |

| Serial Communications:                              |                                      |                        |                                                             |               |

| UART                                                | 1                                    | 1                      | 1                                                           | 1             |

| MSSP                                                | 1                                    | 1                      | 1                                                           | 1             |

| 10-Bit Analog-to-Digital Module<br>(input channels) | 12                                   |                        | 7                                                           |               |

| Analog Comparators                                  | 1                                    | 1                      | 1                                                           | 1             |

| Resets (and delays)                                 |                                      |                        | , MCLR, WDT, Illega<br>aps, Configuration W<br>T, PLL Lock) |               |

| Instruction Set                                     | 76 Base                              | Instructions, Multiple | Addressing Mode \                                           | /ariations    |

| Packages                                            | 20-Pin PDIP/SS                       | SOP/SOIC/QFN           | 14-Pin PD                                                   | IP/TSSOP      |

|                                                     |                                      |                        |                                                             |               |

|          |                                  | Pin Number    | •                        |     |        |                                                                               |

|----------|----------------------------------|---------------|--------------------------|-----|--------|-------------------------------------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 14-Pin<br>PDIP/<br>TSSOP | I/O | Buffer | Description                                                                   |

| CVREF    | 17                               | 14            | 11                       | Ι   | ANA    | Comparator Voltage Reference Output                                           |

| CVREF+   | 2                                | 19            | 2                        | I   | ANA    | Comparator Reference Positive Input Voltage                                   |

| CVREF-   | 3                                | 20            | 3                        | I   | ANA    | Comparator Reference Negative Input Voltage                                   |

| HLVDIN   | 15                               | 12            | 6                        | I   | ST     | High/Low-Voltage Detect Input                                                 |

| INT0     | 11                               | 8             | 12                       | I   | ST     | Interrupt 0 Input                                                             |

| INT1     | 17                               | 14            | 11                       | I   | ST     | Interrupt 1 Input                                                             |

| INT2     | 14                               | 11            | 10                       | I   | ST     | Interrupt 2 Input                                                             |

| MCLR     | 1                                | 18            | 1                        | I   | ST     | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |

| OSCI     | 7                                | 4             | 4                        | I   | ANA    | Main Oscillator Input                                                         |

| OSCO     | 8                                | 5             | 5                        | 0   | ANA    | Main Oscillator Output                                                        |

| PGEC1    | 5                                | 2             | _                        | I/O | ST     | ICSP™ Clock 1                                                                 |

| PCED1    | 4                                | 1             | _                        | I/O | ST     | ICSP Data 1                                                                   |

| PGEC2    | 2                                | 19            | 2                        | I/O | ST     | ICSP Clock 2                                                                  |

| PGED2    | 3                                | 20            | 3                        | I/O | ST     | ICSP Data 2                                                                   |

| PGEC3    | 10                               | 7             | 7                        | I/O | ST     | ICSP Clock 3                                                                  |

| PGED3    | 9                                | 6             | 6                        | I/O | ST     | ICSP Data 3                                                                   |

| RA0      | 2                                | 19            | 2                        | I/O | ST     | PORTA Pins                                                                    |

| RA1      | 3                                | 20            | 3                        | I/O | ST     | 7                                                                             |

| RA2      | 7                                | 4             | 4                        | I/O | ST     | 7                                                                             |

| RA3      | 8                                | 5             | 5                        | I/O | ST     |                                                                               |

| RA4      | 10                               | 7             | 7                        | I/O | ST     | 7                                                                             |

| RA5      | 1                                | 18            | 1                        | I   | ST     | 7                                                                             |

| RA6      | 14                               | 11            | 10                       | I/O | ST     | 7                                                                             |

| RB0      | 4                                | 1             |                          | I/O | ST     | PORTB Pins                                                                    |

| RB1      | 5                                | 2             |                          | I/O | ST     |                                                                               |

| RB2      | 6                                | 3             |                          | I/O | ST     |                                                                               |

| RB4      | 9                                | 6             | 6                        | I/O | ST     |                                                                               |

| RB7      | 11                               | 8             | —                        | I/O | ST     |                                                                               |

| RB8      | 12                               | 9             | 8                        | I/O | ST     | 1                                                                             |

| RB9      | 13                               | 10            | 9                        | I/O | ST     |                                                                               |

| RB12     | 15                               | 12            | _                        | I/O | ST     |                                                                               |

| RB13     | 16                               | 13            | —                        | I/O | ST     | 1                                                                             |

| RB14     | 17                               | 14            | 11                       | I/O | ST     | 1                                                                             |

| RB15     | 18                               | 15            | 12                       | I/O | ST     | 1                                                                             |

| REFO     | 18                               | 15            | 12                       | 0   | —      | Reference Clock Output                                                        |

#### PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS (CONTINUED) **TABLE 1-5:**

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

#### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0               | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| —     | —   | —   | —   | IPL3 <sup>(1)</sup> | PSV   | —   | —     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | <ul><li>1 = Program space is visible in data space</li><li>0 = Program space is not visible in data space</li></ul>           |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

#### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for a 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several Multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing it is not recommended.

All of the Table Write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Enhanced In-Circuit Serial Programming

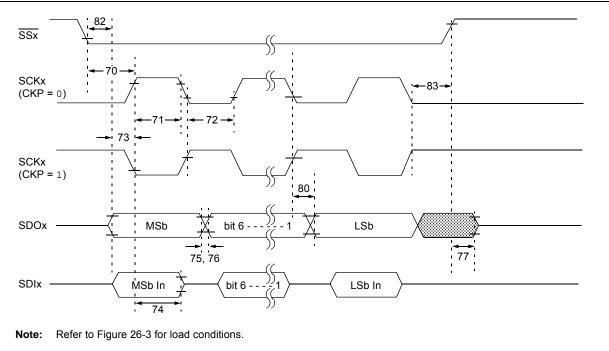

Enhanced ICSP uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

#### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. For more information, refer to **Section 5.5 "Programming Operations"**.

### 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 8.3 Interrupt Control and Status Registers

Depending on the particular device, the PIC24F16KL402 family of devices implements up to 28 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS5

- IEC0 through IEC5

- IPC0 through IPC7, ICP9, IPC12, ICP16, ICP18 and IPC20

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIV table.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence listed in Table 8-2. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. The INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits are in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user may change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit, which together with the IPL<2:0> bits, also indicates the current CPU priority level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All interrupt registers are described in Register 8-3 through Register 8-30, in the following sections.

#### REGISTER 8-17: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0         | R/W-1             | R/W-0                                  | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |

|-------------|-------------------|----------------------------------------|------------------|-------------------|------------------|-----------------|---------|

|             | T1IP2             | T1IP1                                  | T1IP0            | _                 | CCP1IP2          | CCP1IP1         | CCP1IP0 |

| pit 15      |                   |                                        |                  |                   |                  |                 | bit 8   |

| U-0         | U-0               | U-0                                    | U-0              | U-0               | R/W-1            | R/W-0           | R/W-0   |

| 0-0         | 0-0               | 0-0                                    | 0-0              | 0-0               | INT0IP2          | INT0IP1         | INT0IP0 |

| <br>oit 7   |                   |                                        | _                | _                 |                  |                 | bit (   |

|             |                   |                                        |                  |                   |                  |                 |         |

| _egend:     |                   |                                        |                  |                   |                  |                 |         |

| R = Readab  | ole bit           | W = Writable                           | bit              | U = Unimplen      | nented bit, read | l as '0'        |         |

| n = Value a | at POR            | '1' = Bit is set                       |                  | '0' = Bit is cle  | ared             | x = Bit is unkr | iown    |

| bit 15      | Unimpleme         | nted: Read as '                        | 0'               |                   |                  |                 |         |

| bit 14-12   | -                 | Timer1 Interrupt                       |                  |                   |                  |                 |         |

| JIL 14-12   |                   | upt is Priority 7 (                    | -                | (intorrunt)       |                  |                 |         |

|             |                   |                                        | riighest phonty  | interrupt)        |                  |                 |         |

|             | •                 |                                        |                  |                   |                  |                 |         |

|             | •                 |                                        |                  |                   |                  |                 |         |

|             |                   | upt is Priority 1<br>upt source is dis | abled            |                   |                  |                 |         |

| bit 11      | Unimpleme         | nted: Read as '                        | 0'               |                   |                  |                 |         |

| oit 10-8    | CCP1IP<2:0        | D>: Capture/Con                        | npare/PWM1 In    | nterrupt Priority | bits             |                 |         |

|             | 111 = Interr      | upt is Priority 7 (                    | highest priority | interrupt)        |                  |                 |         |

|             | •                 |                                        |                  |                   |                  |                 |         |

|             | •                 |                                        |                  |                   |                  |                 |         |

|             | •<br>001 = Interr | upt is Priority 1                      |                  |                   |                  |                 |         |

|             |                   | upt source is dis                      | abled            |                   |                  |                 |         |

| oit 7-3     | Unimpleme         | nted: Read as '                        | 0'               |                   |                  |                 |         |

| oit 2-0     | -                 | External Interior                      |                  | its               |                  |                 |         |

|             |                   | upt is Priority 7 (                    |                  |                   |                  |                 |         |

|             | •                 |                                        |                  |                   |                  |                 |         |

|             | •                 |                                        |                  |                   |                  |                 |         |

|             | •                 |                                        |                  |                   |                  |                 |         |

|             |                   |                                        |                  |                   |                  |                 |         |

|             |                   | upt is Priority 1<br>upt source is dis | ablod            |                   |                  |                 |         |

#### REGISTER 8-23: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0                                                                       | R/W-1                                                                       | R/W-0                                                   | R/W-0                                      | U-0                             | U-0           | U-0       | U-0   |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------|---------------------------------|---------------|-----------|-------|

| _                                                                         | T4IP2 <sup>(1)</sup>                                                        | T4IP1 <sup>(1)</sup>                                    | T4IP0 <sup>(1)</sup>                       | —                               | _             |           | _     |

| bit 15                                                                    |                                                                             |                                                         |                                            | · · · · ·                       |               |           | bit 8 |

|                                                                           |                                                                             |                                                         |                                            |                                 |               |           |       |

| U-0                                                                       | R/W-1                                                                       | R/W-0                                                   | R/W-0                                      | U-0                             | U-0           | U-0       | U-0   |

|                                                                           | CCP3IP2 <sup>(1)</sup>                                                      | CCP3IP1 <sup>(1)</sup>                                  | CCP3IP0 <sup>(1)</sup>                     | —                               |               | —         | —     |

| bit 7                                                                     |                                                                             |                                                         |                                            |                                 |               |           | bit C |

|                                                                           |                                                                             |                                                         |                                            |                                 |               |           |       |

| Legend:                                                                   |                                                                             |                                                         |                                            |                                 |               |           |       |

| R = Readab                                                                | le bit                                                                      | W = Writable                                            | bit                                        | U = Unimplem                    | ented bit, re | ad as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |                                                                             |                                                         |                                            |                                 |               |           | own   |

|                                                                           |                                                                             |                                                         |                                            |                                 |               |           |       |

| bit 15                                                                    | Unimplemen                                                                  | ted: Read as '                                          | )'                                         |                                 |               |           |       |

| bit 14-12                                                                 | <b>T4IP&lt;2:0&gt;:</b> ⊺i                                                  | mer4 Interrupt                                          | Priority bits <sup>(1)</sup>               |                                 |               |           |       |

|                                                                           | 111 = Interrup                                                              | ot is Priority 7(                                       | highest priority                           | interrupt)                      |               |           |       |

|                                                                           | •                                                                           |                                                         |                                            |                                 |               |           |       |

|                                                                           | •                                                                           |                                                         |                                            |                                 |               |           |       |

|                                                                           | 001 = Interrup                                                              |                                                         |                                            |                                 |               |           |       |

|                                                                           | •                                                                           | ot source is dis                                        |                                            |                                 |               |           |       |

|                                                                           |                                                                             |                                                         | .,                                         |                                 |               |           |       |

| bit 11-7                                                                  | Unimplemen                                                                  |                                                         |                                            | (1)                             |               |           |       |

| bit 11-7<br>bit 6-4                                                       | CCP3IP: Cap                                                                 | ture/Compare/                                           | PWM3 Interrup                              | ot Priority bits <sup>(1)</sup> |               |           |       |

|                                                                           | CCP3IP: Cap                                                                 |                                                         | PWM3 Interrup                              |                                 |               |           |       |

|                                                                           | CCP3IP: Cap                                                                 | ture/Compare/                                           | PWM3 Interrup                              |                                 |               |           |       |

|                                                                           | CCP3IP: Cap                                                                 | ture/Compare/                                           | PWM3 Interrup                              |                                 |               |           |       |

|                                                                           | CCP3IP: Cap<br>111 = Interrup<br>•<br>•<br>•<br>001 = Interrup              | ture/Compare/l<br>ot is Priority 7(<br>ot is Priority 1 | PWM3 Interrup<br>highest priority          |                                 |               |           |       |

|                                                                           | CCP3IP: Cap<br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup | ture/Compare/l<br>ot is Priority 7(                     | PWM3 Interrup<br>highest priority<br>abled |                                 |               |           |       |

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

#### REGISTER 11-1: ANSA: PORTA ANALOG SELECTION REGISTER

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —      | —   |     |     |     |     |     | —     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | ANSA3 | ANSA2 | ANSA1 | ANSA0 |

| bit 7 |     |     |     |       |       |       | bit 0 |

### Legend:

bit 3-0

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

ANSA<3:0>: Analog Select Control bits

1 = Digital input buffer is not active (use for analog input)

0 = Digital input buffer is active

#### REGISTER 11-2: ANSB: PORTB ANALOG SELECTION REGISTER

| R/W-1  | R/W-1  | R/W-1                 | R/W-1                 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|-----------------------|-----------------------|-----|-----|-----|-------|

| ANSB15 | ANSB14 | ANSB13 <sup>(1)</sup> | ANSB12 <sup>(1)</sup> | —   | —   | —   | —     |

| bit 15 |        | •                     |                       |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1                | R/W-1                | R/W-1                | R/W-1                |

|-------|-----|-----|-------|----------------------|----------------------|----------------------|----------------------|

| _     | —   | —   | ANSB4 | ANSB3 <sup>(2)</sup> | ANSB2 <sup>(1)</sup> | ANSB1 <sup>(1)</sup> | ANSB0 <sup>(1)</sup> |

| bit 7 |     |     |       |                      |                      |                      | bit 0                |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-12 | ANSB<15:12>: Analog Select Control bits <sup>(1)</sup><br>1 = Digital input buffer is not active (use for analog input)<br>0 = Digital input buffer is active |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-5  | Unimplemented: Read as '0'                                                                                                                                    |

| bit 4-0   | ANSB<4:0>: Analog Select Control bits <sup>(2)</sup>                                                                                                          |

|           | <ul><li>1 = Digital input buffer is not active (use for analog input)</li><li>0 = Digital input buffer is active</li></ul>                                    |

|           |                                                                                                                                                               |

**Note 1:** ANSB<13:12,2:0> are unimplemented on 14-pin devices.

2: ANSB<3> is unimplemented on 14-pin and 20-pin devices.

### 17.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP)

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive refer-      |

|       | ence source. For more information on       |

|       | MSSP, refer to the "dsPIC33/PIC24          |

|       | Family Reference Manual".                  |

The Master Synchronous Serial Port (MSSP) module is an 8-bit serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, Shift registers, display drivers, A/D Converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The SPI interface supports these modes in hardware:

- Master mode

- Slave mode

- · Daisy-Chaining Operation in Slave mode

- Synchronized Slave operation

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- · Multi-Master mode

- Slave mode with 10-Bit And 7-Bit Addressing and Address Masking

- Byte NACKing

- Selectable Address and Data Hold and Interrupt Masking

### 17.1 I/O Pin Configuration for SPI

In SPI Master mode, the MSSP module will assert control over any pins associated with the SDOx and SCKx outputs. This does not automatically disable other digital functions associated with the pin, and may result in the module driving the digital I/O port inputs. To prevent this, the MSSP module outputs must be disconnected from their output pins while the module is in SPI Master mode. While disabling the module temporarily may be an option, it may not be a practical solution in all applications.

The SDOx and SCKx outputs for the module can be selectively disabled by using the SDOxDIS and SCKxDIS bits in the PADCFG1 register (Register 17-10). Setting the bit disconnects the corresponding output for a particular module from its assigned pin.

NOTES:

| R/W-0        | U-0                                                                                                                                                                                                                            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0   | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------|------------------|-----------------|--------|--|--|--|--|

| CH0NB        | —                                                                                                                                                                                                                              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _     | CH0SB3            | CH0SB2           | CH0SB1          | CH0SB0 |  |  |  |  |

| bit 15       |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                   |                  |                 | bit 8  |  |  |  |  |

|              |                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0   | R/W-0             | R/W-0            |                 |        |  |  |  |  |

| R/W-0        | U-0                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0 |                   |                  |                 |        |  |  |  |  |

| CH0NA        |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | CH0SA3            | CH0SA2           | CH0SA1          | CH0SA0 |  |  |  |  |

| bit 7        |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                   |                  |                 | bit C  |  |  |  |  |

| Legend:      |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                   |                  |                 |        |  |  |  |  |

| R = Readab   | le bit                                                                                                                                                                                                                         | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit   | U = Unimplem      | nented bit, read | 1 as '0'        |        |  |  |  |  |

| -n = Value a | It POR                                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t     | '0' = Bit is clea | ared             | x = Bit is unkr | iown   |  |  |  |  |

|              | 1110 = AN1<br>1101 = AN1<br>1001 = AN1<br>1011 = AN1<br>1010 = AN1<br>1001 = AN9<br>1000 = Upp<br>0111 = Low<br>0110 = Inter<br>0101 = Res<br>0100 = AN4                                                                       | Unimplemented: Read as '0'<br>CH0SB<3:0>: Channel 0 Positive Input Select for MUX B Multiplexer Setting bits<br>1111 = AN15<br>1110 = AN14<br>1101 = AN13<br>1100 = AN12 <sup>(1)</sup><br>1011 = AN11 <sup>(1)</sup><br>1010 = AN10<br>1001 = AN9<br>1000 = Upper guardband rail (0.785 * VDD)<br>0111 = Lower guardband rail (0.215 * VDD)<br>0110 = Internal band gap reference (VBG)<br>0101 = Reserved; do not use<br>0100 = AN4 <sup>(1)</sup><br>0011 = AN3 <sup>(1)</sup> |       |                   |                  |                 |        |  |  |  |  |

| bit 7        | <ul> <li>0001 = AN1</li> <li>0000 = AN0</li> <li>CH0NA: Channel 0 Negative Input Select for MUX A Multiplexer Setting bit</li> <li>1 = Channel 0 negative input is AN1</li> <li>0 = Channel 0 negative input is VR-</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                   |                  |                 |        |  |  |  |  |

| bit 6-4      |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                   |                  |                 |        |  |  |  |  |

|              | Unimpleme                                                                                                                                                                                                                      | Unimplemented: Read as '0'<br>CH0SA<3:0>: Channel 0 Positive Input Select for MUX A Multiplexer Setting bits<br>Bit combinations are identical to those for CH0SB<3:0> (above).                                                                                                                                                                                                                                                                                                   |       |                   |                  |                 |        |  |  |  |  |

### REGISTER 19-4: AD1CHS: A/D INPUT SELECT REGISTER

Note 1: Unimplemented on 14-pin devices; do not use.

#### REGISTER 23-5: FWDT: WATCHDOG TIMER CONFIGURATION REGISTER

| R/P-1         | R/P-1                                                                                                                                                                                   | R/P-0                    | R/P-1         | R/P-1             | R/P-1            | R/P-1           | R/P-1          |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|-------------------|------------------|-----------------|----------------|--|--|--|

| FWDTEN1       | WINDIS                                                                                                                                                                                  | FWDTEN0                  | FWPSA         | WDTPS3            | WDTPS2           | WDTPS1          | WDTPS0         |  |  |  |

| bit 7         |                                                                                                                                                                                         |                          |               |                   |                  |                 | bit 0          |  |  |  |

| Legend:       |                                                                                                                                                                                         |                          |               |                   |                  |                 |                |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                   | P = Programm             | able bit      | U = Unimplem      | nented bit, read | 1 as '0'        |                |  |  |  |

| -n = Value at |                                                                                                                                                                                         | '1' = Bit is set         |               | '0' = Bit is clea |                  | x = Bit is unkr | iown           |  |  |  |

| bit 7,5       |                                                                                                                                                                                         | <b>0&gt;:</b> Watchdog T | imer Enable h | nite              |                  |                 |                |  |  |  |

| 5117,5        |                                                                                                                                                                                         | enabled in hard          |               | 10                |                  |                 |                |  |  |  |

|               |                                                                                                                                                                                         | controlled with t        |               | bit setting       |                  |                 |                |  |  |  |

|               |                                                                                                                                                                                         | enabled only wh          |               |                   |                  | ep, SWDTEN b    | it is disabled |  |  |  |

|               |                                                                                                                                                                                         | disabled in hard         |               |                   | d                |                 |                |  |  |  |

| bit 6         |                                                                                                                                                                                         | dowed Watchdo            | •             |                   |                  |                 |                |  |  |  |

|               | 1 = Standard WDT is selected; windowed WDT is disabled                                                                                                                                  |                          |               |                   |                  |                 |                |  |  |  |

|               | 0 = Windowed WDT is enabled; note that executing a CLRWDT instruction while the WDT is disabled<br>in hardware and software (FWDTEN<1:0> = 00 and SWDTEN (RCON<5> = 0) will not cause a |                          |               |                   |                  |                 |                |  |  |  |

|               | device R                                                                                                                                                                                |                          | e (i weiter)  |                   |                  |                 |                |  |  |  |

| bit 4         | FWPSA: WD                                                                                                                                                                               | T Prescaler bit          |               |                   |                  |                 |                |  |  |  |

|               | 1 = WDT pre                                                                                                                                                                             | scaler ratio of 1:       | 128           |                   |                  |                 |                |  |  |  |

|               | 0 = WDT pre                                                                                                                                                                             | scaler ratio of 1:       | 32            |                   |                  |                 |                |  |  |  |

| bit 3-0       | WDTPS<3:0                                                                                                                                                                               | >: Watchdog Tin          | ner Postscale | Select bits       |                  |                 |                |  |  |  |

|               | 1111 <b>= 1:32</b> ,                                                                                                                                                                    |                          |               |                   |                  |                 |                |  |  |  |

|               | 1110 = 1:16,                                                                                                                                                                            |                          |               |                   |                  |                 |                |  |  |  |

|               | 1101 = 1:8,1<br>1100 = 1:4,0                                                                                                                                                            |                          |               |                   |                  |                 |                |  |  |  |

|               | 1011 = 1:2,0                                                                                                                                                                            |                          |               |                   |                  |                 |                |  |  |  |

|               | 1010 = 1:1,024                                                                                                                                                                          |                          |               |                   |                  |                 |                |  |  |  |

|               | 1001 <b>= 1:512</b>                                                                                                                                                                     |                          |               |                   |                  |                 |                |  |  |  |

|               | 1000 = 1:256                                                                                                                                                                            |                          |               |                   |                  |                 |                |  |  |  |

|               | 0111 = 1:128<br>0110 = 1:64                                                                                                                                                             |                          |               |                   |                  |                 |                |  |  |  |

|               | 0101 = 1:32                                                                                                                                                                             |                          |               |                   |                  |                 |                |  |  |  |

|               | 0100 = 1:16                                                                                                                                                                             |                          |               |                   |                  |                 |                |  |  |  |

|               | 0011 = 1:8                                                                                                                                                                              |                          |               |                   |                  |                 |                |  |  |  |

|               | 0010 = 1:4                                                                                                                                                                              |                          |               |                   |                  |                 |                |  |  |  |

|               | 0001 <b>= 1:2</b>                                                                                                                                                                       |                          |               |                   |                  |                 |                |  |  |  |

| R/P-1               | R/P-1                                 | R/P-1                | R/P-1                                 | R/P-1             | U-0              | R/P-1             | R/P-1                      |

|---------------------|---------------------------------------|----------------------|---------------------------------------|-------------------|------------------|-------------------|----------------------------|

| MCLRE <sup>(1</sup> | ) BORV1 <sup>(2)</sup>                | BORV0 <sup>(2)</sup> | I2C1SEL <sup>(3)</sup>                | PWRTEN            |                  | BOREN1            | BOREN0                     |

| bit 7               |                                       |                      |                                       |                   |                  |                   | bit C                      |

| Logondi             |                                       |                      |                                       |                   |                  |                   |                            |

| Legend:             |                                       |                      |                                       |                   |                  | 1                 |                            |

| R = Reada           |                                       | P = Program          |                                       | •                 | nented bit, read |                   |                            |