#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16kl402-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5.0 FLASH PROGRAM MEMORY

| Note: | This data sheet summarizes the features of this group of PIC24F devices. It is not |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | intended to be a comprehensive reference                                           |  |  |  |  |  |  |  |  |  |

|       | source. For more information on Flash                                              |  |  |  |  |  |  |  |  |  |

|       | Programming, refer to the "dsPIC33/PIC24                                           |  |  |  |  |  |  |  |  |  |

|       | Family Reference Manual", "Program                                                 |  |  |  |  |  |  |  |  |  |

|       | Memory" (DS39715).                                                                 |  |  |  |  |  |  |  |  |  |

The PIC24F16KL402 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 1.8V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24F device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear/Program mode Entry voltage (MCLR/VPP). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed. Run-Time Self Programming (RTSP) is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 32 instructions (96 bytes) at a time, and erase program memory in blocks of 32, 64 and 128 instructions (96,192 and 384 bytes) at a time.

The NVMOP<1:0> (NVMCON<1:0>) bits decide the erase block size.

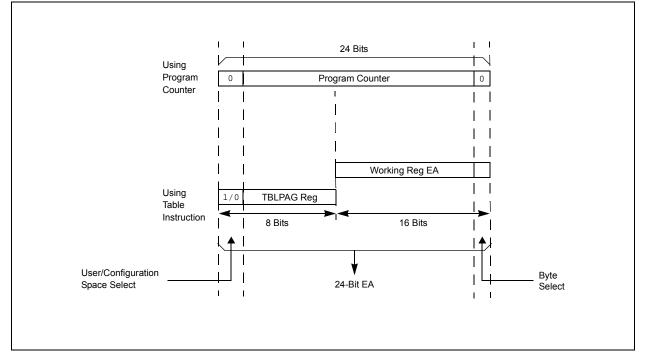

### 5.1 Table Instructions and Flash Programming

Regardless of the method used, Flash memory programming is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as depicted in Figure 5-1.

The TBLRDL and TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### 7.4.2 DETECTING BOR

When BOR is enabled, the BOR bit (RCON<1>) is always reset to '1' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR and BOR bits are reset to '0' in the software, immediately after any POR event. If the BOR bit is '1' while POR is '0', it can be reliably assumed that a BOR event has occurred.

**Note:** Even when the device exits from Deep Sleep mode, both the POR and BOR are set.

### 7.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, BOR remains under hardware control and operates as previously described. However, whenever the device enters Sleep mode, BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|-------|-----|-----|---------|---------|--------|---------|-------|

| —     | —   | —   | MATHERR | ADDRERR | STKERR | OSCFAIL | —     |

| bit 7 |     |     |         |         |        |         | bit 0 |

| Legend:           |            |                                                                                                                |                       |                    |

|-------------------|------------|----------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|

|                   |            | W = Writable bit                                                                                               | U = Unimplemented bit | , read as '0'      |

|                   |            | '1' = Bit is set                                                                                               | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15            | 1 = Interr | Interrupt Nesting Disable bit<br>upt nesting is disabled<br>upt nesting is enabled                             |                       |                    |

| bit 14-5<br>bit 4 | MATHER     | mented: Read as '0'<br>R: Arithmetic Error Trap Status<br>flow trap has occurred<br>flow trap has not occurred | bit                   |                    |

| bit 3             | 1 = Addre  | R: Address Error Trap Status b<br>ess error trap has occurred<br>ess error trap has not occurred               | it                    |                    |

| bit 2             | STKERR     | : Stack Error Trap Status bit                                                                                  |                       |                    |

|       | <ol> <li>1 = Stack error trap has occurred</li> <li>0 = Stack error trap has not occurred</li> </ol>            |

|-------|-----------------------------------------------------------------------------------------------------------------|

| bit 1 | OSCFAIL: Oscillator Failure Trap Status bit                                                                     |

|       | <ul><li>1 = Oscillator failure trap has occurred</li><li>0 = Oscillator failure trap has not occurred</li></ul> |

| bit 0 | Unimplemented: Read as '0'                                                                                      |

### REGISTER 8-25: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0          | U-0           | U-0                 | U-0              | U-0               | U-0              | U-0             | U-0   |

|--------------|---------------|---------------------|------------------|-------------------|------------------|-----------------|-------|

| —            | _             | —                   | —                | —                 | —                | —               | —     |

| bit 15       |               |                     |                  |                   |                  |                 | bit 8 |

|              |               |                     |                  |                   |                  |                 |       |

| U-0          | R/W-1         | R/W-0               | R/W-0            | U-0               | U-0              | U-0             | U-0   |

| _            | T3GIP2        | T3GIP1              | T3GIP0           | —                 | —                | —               | —     |

| bit 7        |               |                     |                  |                   |                  |                 | bit 0 |

|              |               |                     |                  |                   |                  |                 |       |

| Legend:      |               |                     |                  |                   |                  |                 |       |

| R = Readab   | le bit        | W = Writable        | bit              | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value a | t POR         | '1' = Bit is set    |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|              |               |                     |                  |                   |                  |                 |       |

| bit 15-7     | Unimplemen    | ted: Read as 'd     | כי               |                   |                  |                 |       |

| bit 6-4      | T3GIP<2:0>:   | Timer3 Externa      | al Gate Interru  | pt Priority bits  |                  |                 |       |

|              | 111 = Interru | pt is Priority 7 (l | highest priority | / interrupt)      |                  |                 |       |

|              | •             |                     |                  |                   |                  |                 |       |

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

### REGISTER 8-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1                  | R/W-0                  | R/W-0                  |

|--------|-----|-----|-----|-----|------------------------|------------------------|------------------------|

| —      | —   | —   | —   | —   | U2ERIP2 <sup>(1)</sup> | U2ERIP1 <sup>(1)</sup> | U2ERIP0 <sup>(1)</sup> |

| bit 15 |     |     |     |     |                        |                        | bit 8                  |

| U-0   | R/W-1                  | R/W-0                  | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|-------|------------------------|------------------------|------------------------|-----|-----|-----|-------|

| _     | U1ERIP2 <sup>(1)</sup> | U1ERIP1 <sup>(1)</sup> | U1ERIP0 <sup>(1)</sup> |     |     | —   | —     |

| bit 7 |                        |                        |                        |     |     |     | bit 0 |

| Legend:           |                                                                 |                                 |                                |                    |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------|---------------------------------|--------------------------------|--------------------|--|--|--|--|--|--|

| R = Readat        | R = Readable bit W = Writable bit                               |                                 | U = Unimplemented bit,         | read as '0'        |  |  |  |  |  |  |

| -n = Value at POR |                                                                 | '1' = Bit is set                | '0' = Bit is cleared           | x = Bit is unknown |  |  |  |  |  |  |

|                   |                                                                 |                                 |                                |                    |  |  |  |  |  |  |

| bit 15-11         | -                                                               | nented: Read as '0'             |                                |                    |  |  |  |  |  |  |

| bit 10-8          | U2ERIP<2                                                        | 2:0>: UART2 Error Interrupt     | t Priority bits <sup>(1)</sup> |                    |  |  |  |  |  |  |

|                   | 111 = Inte                                                      | errupt is Priority 7 (highest p | priority interrupt)            |                    |  |  |  |  |  |  |

|                   | •                                                               |                                 |                                |                    |  |  |  |  |  |  |

|                   | •                                                               |                                 |                                |                    |  |  |  |  |  |  |

|                   | •                                                               |                                 |                                |                    |  |  |  |  |  |  |

|                   |                                                                 | errupt is Priority 1            |                                |                    |  |  |  |  |  |  |

|                   |                                                                 | errupt source is disabled       |                                |                    |  |  |  |  |  |  |

| bit 7             | -                                                               | nented: Read as '0'             |                                |                    |  |  |  |  |  |  |

| bit 6-4           | U1ERIP<2:0>: UART1 Error Interrupt Priority bits <sup>(1)</sup> |                                 |                                |                    |  |  |  |  |  |  |

|                   | 111 = Interrupt is Priority 7 (highest priority interrupt)      |                                 |                                |                    |  |  |  |  |  |  |

|                   | •                                                               |                                 |                                |                    |  |  |  |  |  |  |

|                   | •                                                               |                                 |                                |                    |  |  |  |  |  |  |

|                   | •                                                               |                                 |                                |                    |  |  |  |  |  |  |

|                   |                                                                 | errupt is Priority 1            |                                |                    |  |  |  |  |  |  |

|                   |                                                                 | errupt source is disabled       |                                |                    |  |  |  |  |  |  |

| bit 3-0           | Unimplen                                                        | nented: Read as '0'             |                                |                    |  |  |  |  |  |  |

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

| R/W-0        | U-0            | R/W-0            | U-0             | U-0                                     | U-0              | U-0      | R/W-0   |

|--------------|----------------|------------------|-----------------|-----------------------------------------|------------------|----------|---------|

| ULPEN        |                | ULPSIDL          | _               | _                                       | _                |          | ULPSINK |

| bit 15       |                |                  |                 |                                         |                  |          | bit 8   |

|              |                |                  |                 |                                         |                  |          |         |

| U-0          | U-0            | U-0              | U-0             | U-0                                     | U-0              | U-0      | U-0     |

|              |                | —                | —               |                                         | —                |          |         |

| bit 7        |                |                  |                 |                                         |                  |          | bit 0   |

| l            |                |                  |                 |                                         |                  |          | 1       |

| Legend:      |                |                  |                 |                                         |                  |          |         |

| R = Readat   | ole bit        | W = Writable     | bit             | U = Unimplem                            | nented bit, read | d as '0' |         |

| -n = Value a | at POR         | '1' = Bit is set |                 | '0' = Bit is cleared x = Bit is unknown |                  |          | nown    |

|              |                |                  |                 |                                         |                  |          |         |

| bit 15       | ULPEN: ULP     | WU Module En     | able bit        |                                         |                  |          |         |

|              | 1 = Module is  |                  |                 |                                         |                  |          |         |

|              | 0 = Module is  | disabled         |                 |                                         |                  |          |         |

| bit 14       | Unimplemen     | ted: Read as '   | כ'              |                                         |                  |          |         |

| bit 13       | ULPSIDL: UL    | PWU Stop in I    | dle Select bit  |                                         |                  |          |         |

|              |                |                  |                 | ne device enters                        | s Idle mode      |          |         |

|              | 0 = Continues  | s module opera   | tion in Idle mo | de                                      |                  |          |         |

| bit 12-9     | Unimplemen     | ted: Read as '   | כ'              |                                         |                  |          |         |

| bit 8        | ULPSINK: UL    | _PWU Current     | Sink Enable bi  | t                                       |                  |          |         |

|              | 1 = Current si | ink is enabled   |                 |                                         |                  |          |         |

|              | 0 = Current si | ink is disabled  |                 |                                         |                  |          |         |

| bit 7-0      | Unimplemen     | ted: Read as '   | כ'              |                                         |                  |          |         |

|              |                |                  |                 |                                         |                  |          |         |

### REGISTER 10-1: ULPWCON: ULPWU CONTROL REGISTER

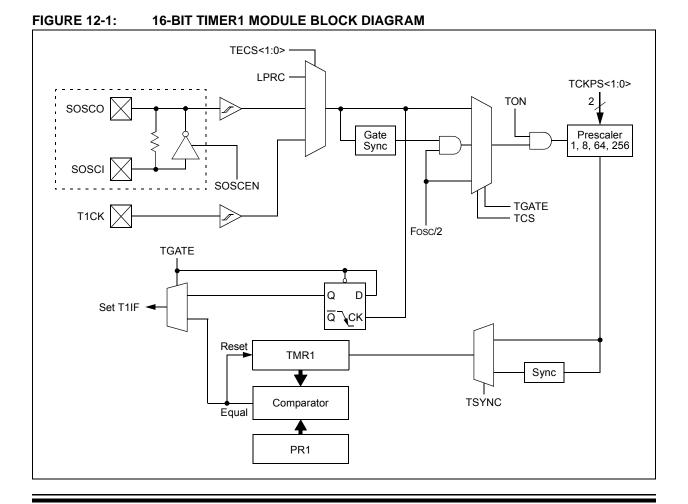

### 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can operate as a free-running, interval timer/counter, or serve as the time counter for a software-based Real-Time Clock (RTC). Timer1 is only reset on initial VDD power-on events. This allows the timer to continue operating as an RTC clock source through other types of device Reset.

Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 illustrates a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0                | U-0                            | R/W-0                            | U-0              | U-0               | U-0              | R/W-0                 | R/W-0                 |

|----------------------|--------------------------------|----------------------------------|------------------|-------------------|------------------|-----------------------|-----------------------|

| TON                  | _                              | TSIDL                            | _                | _                 | _                | T1ECS1 <sup>(1)</sup> | T1ECS0 <sup>(1)</sup> |

| bit 15               |                                | I                                |                  |                   |                  | •                     | bit 8                 |

|                      |                                |                                  |                  |                   |                  |                       |                       |

| U-0                  | R/W-0                          | R/W-0                            | R/W-0            | U-0               | R/W-0            | R/W-0                 | U-0                   |

| _                    | TGATE                          | TCKPS1                           | TCKPS0           | —                 | TSYNC            | TCS                   | —                     |

| bit 7                |                                |                                  |                  |                   |                  |                       | bit (                 |

| Legend:              |                                |                                  |                  |                   |                  |                       |                       |

| R = Readabl          | e bit                          | W = Writable                     | bit              | U = Unimplerr     | nented bit. read | d as '0'              |                       |

| -n = Value at        | POR                            | '1' = Bit is set                 |                  | '0' = Bit is clea |                  | x = Bit is unkr       | iown                  |

|                      |                                |                                  |                  |                   |                  |                       |                       |

| bit 15               | TON: Timer1                    | On bit                           |                  |                   |                  |                       |                       |

|                      | 1 = Starts 16-                 |                                  |                  |                   |                  |                       |                       |

|                      | 0 = Stops 16-                  | bit Timer1                       |                  |                   |                  |                       |                       |

| bit 14               | Unimplement                    | ted: Read as '                   | )'               |                   |                  |                       |                       |

| bit 13               |                                | 1 Stop in Idle N                 |                  |                   |                  |                       |                       |

|                      |                                |                                  |                  | device enters Idl | e mode           |                       |                       |

| h:+ 40 40            |                                | module opera                     |                  | de                |                  |                       |                       |

| bit 12-10<br>bit 9-8 | -                              | ted: Read as '<br>: Timer1 Exten |                  | La at hita(1)     |                  |                       |                       |

| DIL 9-0              | 11 = Reserve                   |                                  |                  | lect bits ?       |                  |                       |                       |

|                      |                                | ises the LPRC                    | as the clock s   | ource             |                  |                       |                       |

|                      |                                | ises the extern                  |                  |                   |                  |                       |                       |

|                      | 00 <b>= Timer1</b> u           | ises the Secon                   | dary Oscillato   | r (SOSC) as the   | clock source     |                       |                       |

| bit 7                | Unimplement                    | ted: Read as '                   | י'               |                   |                  |                       |                       |

| bit 6                | TGATE: Time                    | r1 Gated Time                    | Accumulation     | Enable bit        |                  |                       |                       |

|                      | When TCS =                     | -                                |                  |                   |                  |                       |                       |

|                      | This bit is igno<br>When TCS = |                                  |                  |                   |                  |                       |                       |

|                      |                                | <u>u.</u><br>ne accumulatio      | n is enabled     |                   |                  |                       |                       |

|                      |                                | ne accumulatio                   |                  |                   |                  |                       |                       |

| bit 5-4              | TCKPS<1:0>                     | : Timer1 Input                   | Clock Prescal    | e Select bits     |                  |                       |                       |

|                      | 11 <b>= 1:256</b>              |                                  |                  |                   |                  |                       |                       |

|                      | 10 = 1:64                      |                                  |                  |                   |                  |                       |                       |

|                      | 01 = 1:8<br>00 = 1:1           |                                  |                  |                   |                  |                       |                       |

| bit 3                |                                | ted: Read as '                   | )'               |                   |                  |                       |                       |

| bit 2                | -                              |                                  |                  | hronization Sele  | ect bit          |                       |                       |

|                      | When TCS =                     |                                  | , ,              |                   |                  |                       |                       |

|                      | 1 = Synchron                   | nizes external (                 |                  |                   |                  |                       |                       |

|                      |                                | t synchronize e                  | external clock i | input             |                  |                       |                       |

|                      | When TCS =                     |                                  |                  |                   |                  |                       |                       |

| hit 1                | This bit is igno               | Clock Source S                   | Soloct bit       |                   |                  |                       |                       |

| bit 1                |                                | ock source is s                  |                  | FCS<1.05          |                  |                       |                       |

|                      |                                | clock (Fosc/2)                   |                  |                   |                  |                       |                       |

|                      |                                |                                  |                  |                   |                  |                       |                       |

| bit 0                | Unimplement                    | ted: Read as '                   | כ'               |                   |                  |                       |                       |

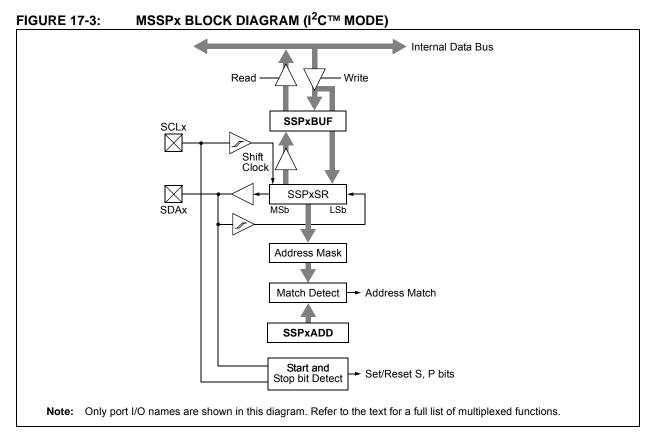

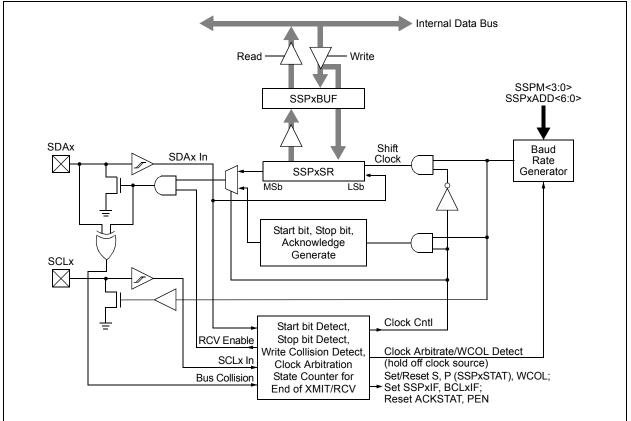

### FIGURE 17-4: MSSPx BLOCK DIAGRAM ( $I^2C^{TM}$ MASTER MODE)

© 2011-2013 Microchip Technology Inc.

NOTES:

### 20.0 COMPARATOR MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator module, refer to the "dsPIC33/PIC24 Family Reference Manual", "Dual Comparator Module" (DS39710).

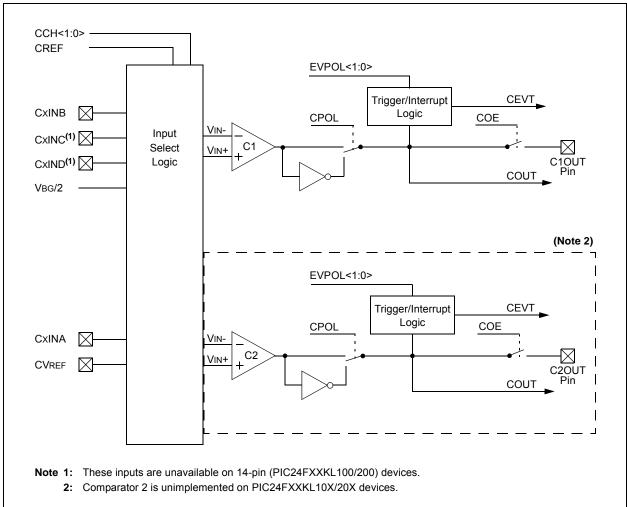

Depending on the particular device, the comparator module provides one or two analog comparators. The inputs to the comparator can be configured to use any one of up to four external analog inputs, as well as a voltage reference input from either the internal band gap reference, divided by 2 (VBG/2), or the comparator voltage reference generator. The comparator outputs may be directly connected to the CxOUT pins. When the respective COE equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module is displayed in Figure 20-1. Diagrams of the possible individual comparator configurations are displayed in Figure 20-2.

Each comparator has its own control register, CMxCON (Register 20-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 20-2).

### FIGURE 20-1: COMPARATOR MODULE BLOCK DIAGRAM

### REGISTER 21-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| U-0           | U-0                                                                                                                                | U-0               | U-0           | U-0                  | U-0             | U-0                | U-0   |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|----------------------|-----------------|--------------------|-------|--|--|--|--|

| _             | —                                                                                                                                  | —                 | —             | _                    | _               | —                  | _     |  |  |  |  |

| bit 15        |                                                                                                                                    |                   |               |                      |                 |                    | bit 8 |  |  |  |  |

| DAMO          |                                                                                                                                    | DAMA              | DAMA          | D 444 0              | DAMA            | DAMA               | DAALO |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                              | R/W-0             | R/W-0         | R/W-0                | R/W-0           | R/W-0              | R/W-0 |  |  |  |  |

| CVREN         | CVROE                                                                                                                              | CVRSS             | CVR4          | CVR3                 | CVR2            | CVR1               | CVR0  |  |  |  |  |

| bit 7         |                                                                                                                                    |                   |               |                      |                 |                    | bit ( |  |  |  |  |

| Legend:       |                                                                                                                                    |                   |               |                      |                 |                    |       |  |  |  |  |

| R = Readabl   | e bit                                                                                                                              | W = Writable      | oit           | U = Unimplen         | nented bit, rea | d as '0'           |       |  |  |  |  |

| -n = Value at | POR                                                                                                                                | '1' = Bit is set  |               | '0' = Bit is cleared |                 | x = Bit is unknown |       |  |  |  |  |

|               |                                                                                                                                    |                   |               |                      |                 |                    |       |  |  |  |  |

| bit 15-8      | Unimpleme                                                                                                                          | nted: Read as '0  | )'            |                      |                 |                    |       |  |  |  |  |

| bit 7         | CVREN: Comparator Voltage Reference Enable bit                                                                                     |                   |               |                      |                 |                    |       |  |  |  |  |

|               | <ol> <li>1 = CVREF circuit is powered on</li> <li>0 = CVREF circuit is powered down</li> </ol>                                     |                   |               |                      |                 |                    |       |  |  |  |  |

| 1.1.0         |                                                                                                                                    | •                 |               | 1.11                 |                 |                    |       |  |  |  |  |

| bit 6         | CVROE: Comparator VREF Output Enable bit                                                                                           |                   |               |                      |                 |                    |       |  |  |  |  |

|               | <ol> <li>CVREF voltage level is output on the CVREF pin</li> <li>CVREF voltage level is disconnected from the CVREF pin</li> </ol> |                   |               |                      |                 |                    |       |  |  |  |  |

| bit 5         |                                                                                                                                    | •                 |               | •                    |                 |                    |       |  |  |  |  |

|               | CVRSS: Comparator VREF Source Selection bit<br>1 = Comparator reference source, CVRSRC = VREF+ – VREF-                             |                   |               |                      |                 |                    |       |  |  |  |  |

|               |                                                                                                                                    | ator reference se |               |                      |                 |                    |       |  |  |  |  |

| bit 4-0       | <b>CVR&lt;4:0&gt;:</b> Comparator VREF Value Selection $0 \le CVR<4:0> \le 31$ bits                                                |                   |               |                      |                 |                    |       |  |  |  |  |

|               | When CVRSS = 1:                                                                                                                    |                   |               |                      |                 |                    |       |  |  |  |  |

|               | CVREF = (VREF-) + (CVR<4:0>/32) • (VREF+ – VREF-)                                                                                  |                   |               |                      |                 |                    |       |  |  |  |  |

|               | When CVRS                                                                                                                          |                   | (00) (A) (    | () (2.2)             |                 |                    |       |  |  |  |  |

|               | UVREF = (AV                                                                                                                        | ′ss) + (CVR<4:0   | >/32) • (AVDD | – AVSS)              |                 |                    |       |  |  |  |  |

### 23.3 Unique ID

A read-only Unique ID value is stored at addresses, 800802h through 800808h. This factory programmed value is unique to each microcontroller produced in the PIC24F16KL402 family. To access this region, use Table Read instructions or Program Space Visibility. To ensure a globally Unique ID across other Microchip microcontroller families, the "Unique ID" value should be further concatenated with the family and Device ID values stored at address, FF0000h.

### REGISTER 23-8: DEVID: DEVICE ID REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   |     | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R      | R      | R      | R      | R      | R      | R      | R      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FAMID7 | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 | FAMID1 | FAMID0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV7  | DEV6 | DEV5 | DEV4 | DEV3 | DEV2 | DEV1 | DEV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-8 **FAMID<7:0>:** Device Family Identifier bits 01001011 = PIC24F16KL402 family

bit 7-0 **DEV<7:0>:** Individual Device Identifier bits 00000001 = PIC24F04KL100

00000010 = PIC24F04KL101

00000101 = PIC24F08KL200 00000110 = PIC24F08KL201

00001010 = PIC24F08KL301 00000000 = PIC24F08KL302

00001110 = PIC24F08KL401 00000100 = PIC24F08KL402 00011110 = PIC24F16KL401 00010100 = PIC24F16KL402

### 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

| Assembly<br>Mnemonic | Assembly Syntax |             | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-----------------|-------------|------------------------------|---------------|----------------|--------------------------|

| TBLRDH               | TBLRDH          | Ws,Wd       | Read Prog<23:16> to Wd<7:0>  | 1             | 2              | None                     |

| TBLRDL               | TBLRDL          | Ws,Wd       | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| TBLWTH               | TBLWTH          | Ws,Wd       | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| TBLWTL               | TBLWTL          | Ws,Wd       | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| ULNK                 | ULNK            |             | Unlink Frame Pointer         | 1             | 1              | None                     |

| XOR                  | XOR             | f           | f = f .XOR. WREG             | 1             | 1              | N, Z                     |

|                      | XOR             | f,WREG      | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |

|                      | XOR             | #lit10,Wn   | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |

|                      | XOR             | Wb,Ws,Wd    | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |

|                      | XOR             | Wb,#lit5,Wd | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |

| ZE                   | ZE              | Ws,Wnd      | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |

### TABLE 25-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Param.<br>No. | Symbol  | Characteris                | tic          | Min         | Max  | Units | Conditions                                 |

|---------------|---------|----------------------------|--------------|-------------|------|-------|--------------------------------------------|

| 100           | Тнідн   | Clock High Time            | 100 kHz mode | 4.0         | —    | μS    | Must operate at a minimum of 1.5 MHz       |

|               |         |                            | 400 kHz mode | 0.6         | —    | μS    | Must operate at a minimum of 10 MHz        |

|               |         |                            | MSSP module  | 1.5         | _    | Тсү   |                                            |

| 101           | TLOW    | Clock Low Time             | 100 kHz mode | 4.7         | —    | μS    | Must operate at a minimum of 1.5 MHz       |

|               |         |                            | 400 kHz mode | 1.3         | —    | μS    | Must operate at a minimum of 10 MHz        |

|               |         |                            | MSSP module  | 1.5         | —    | Тсү   |                                            |

| 102           | TR      | SDAx and SCLx Rise Time    | 100 kHz mode | —           | 1000 | ns    |                                            |

|               |         |                            | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from 10 to 400 pF    |

| 103           | TF      | SDAx and SCLx Fall Time    | 100 kHz mode | —           | 300  | ns    |                                            |

|               |         |                            | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from<br>10 to 400 pF |

| 90            | TSU:STA | Start Condition Setup Time | 100 kHz mode | 4.7         | —    | μS    | Only relevant for Repeated                 |

|               |         |                            | 400 kHz mode | 0.6         | —    | μs    | Start condition                            |

| 91            | THD:STA | Start Condition Hold Time  | 100 kHz mode | 4.0         |      | μS    | After this period, the first clock         |

|               |         |                            | 400 kHz mode | 0.6         | —    | μS    | pulse is generated                         |

| 106           | THD:DAT | Data Input Hold Time       | 100 kHz mode | 0           | —    | ns    |                                            |

|               |         |                            | 400 kHz mode | 0           | 0.9  | μS    |                                            |

| 107           | TSU:DAT | Data Input Setup Time      | 100 kHz mode | 250         | —    | ns    | (Note 2)                                   |

|               |         |                            | 400 kHz mode | 100         | —    | ns    |                                            |

| 92            | Tsu:sto | Stop Condition Setup Time  | 100 kHz mode | 4.7         | —    | μS    |                                            |

|               |         |                            | 400 kHz mode | 0.6         | —    | μS    |                                            |

| 109           | ΤΑΑ     | Output Valid from Clock    | 100 kHz mode | —           | 3500 | ns    | (Note 1)                                   |

|               |         |                            | 400 kHz mode | —           | —    | ns    |                                            |

| 110           | TBUF    | Bus Free Time              | 100 kHz mode | 4.7         | _    | μS    | Time the bus must be free before           |

|               |         |                            | 400 kHz mode | 1.3         | —    | μS    | a new transmission can start               |

| D102          | Св      | Bus Capacitive Loading     |              | _           | 400  | pF    |                                            |

### TABLE 26-32: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS (SLAVE MODE)

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCLx to avoid unintended generation of Start or Stop conditions.

2: A Fast mode I<sup>2</sup>C<sup>™</sup> bus device can be used in a Standard mode I<sup>2</sup>C bus system, but the requirement, Tsu:DAT ≥ 250 ns, must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCLx signal. If such a device does stretch the LOW period of the SCLx signal, it must output the next data bit to the SDAx line, TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCLx line is released.

|              |               |                                                      | Standard Operating te              |         |                                   |       | <b>3.6V (unless otherwise stated)</b><br>85°C for Industrial |  |  |  |  |  |

|--------------|---------------|------------------------------------------------------|------------------------------------|---------|-----------------------------------|-------|--------------------------------------------------------------|--|--|--|--|--|

| Param<br>No. | Symbol        | Characteristic                                       | Min.                               | Тур     | Max.                              | Units | Conditions                                                   |  |  |  |  |  |

|              | Device Supply |                                                      |                                    |         |                                   |       |                                                              |  |  |  |  |  |

| AD01         | AVDD          | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or 1.8 |         | Lesser of:<br>VDD + 0.3<br>or 3.6 | V     |                                                              |  |  |  |  |  |

| AD02         | AVss          | Module Vss Supply                                    | Vss - 0.3                          | _       | Vss + 0.3                         | V     |                                                              |  |  |  |  |  |

|              |               | ·                                                    | Referen                            | ce Inpu | ts                                |       | ·                                                            |  |  |  |  |  |

| AD05         | VREFH         | Reference Voltage High                               | AVss + 1.7                         |         | AVdd                              | V     |                                                              |  |  |  |  |  |

| AD06         | VREFL         | Reference Voltage Low                                | AVss                               |         | AVDD - 1.7                        | V     |                                                              |  |  |  |  |  |

| AD07         | VREF          | Absolute Reference<br>Voltage                        | AVss – 0.3                         | _       | AVDD + 0.3                        | V     |                                                              |  |  |  |  |  |

|              |               |                                                      | Analo                              | g Input |                                   |       | •                                                            |  |  |  |  |  |

| AD10         | VINH-VINL     | Full-Scale Input Span                                | VREFL                              | _       | VREFH                             | V     | (Note 1)                                                     |  |  |  |  |  |

| AD11         | VIN           | Absolute Input Voltage                               | AVss - 0.3                         |         | AVDD + 0.3                        | V     |                                                              |  |  |  |  |  |

| AD12         | VINL          | Absolute VINL Input<br>Voltage                       | AVss – 0.3                         |         | AVDD/2                            | V     |                                                              |  |  |  |  |  |

| AD17         | Rin           | Recommended<br>Impedance of Analog<br>Voltage Source | —                                  | _       | 2.5K                              | Ω     | 10-bit                                                       |  |  |  |  |  |

|              |               |                                                      | A/D A                              | ccuracy | ,                                 |       |                                                              |  |  |  |  |  |

| AD20b        | NR            | Resolution                                           | —                                  | 10      | —                                 | bits  |                                                              |  |  |  |  |  |

| AD21b        | INL           | Integral Nonlinearity                                | _                                  | ±1      | ±2                                | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V               |  |  |  |  |  |

| AD22b        | DNL           | Differential Nonlinearity                            | —                                  | ±1      | ±1.5                              | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V               |  |  |  |  |  |

| AD23b        | Gerr          | Gain Error                                           | —                                  | ±1      | ±3                                | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V               |  |  |  |  |  |

| AD24b        | EOFF          | Offset Error                                         | —                                  | ±1      | ±2                                | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V               |  |  |  |  |  |

| AD25b        |               | Monotonicity                                         | _                                  |         | _                                 |       | (Note 2)                                                     |  |  |  |  |  |

### TABLE 26-35: A/D MODULE SPECIFICATIONS

**Note 1:** Measurements are taken with external VREF+ and VREF- used as the A/D voltage reference.

**2:** The A/D conversion result never decreases with an increase in the input voltage.

### 27.0 PACKAGING INFORMATION

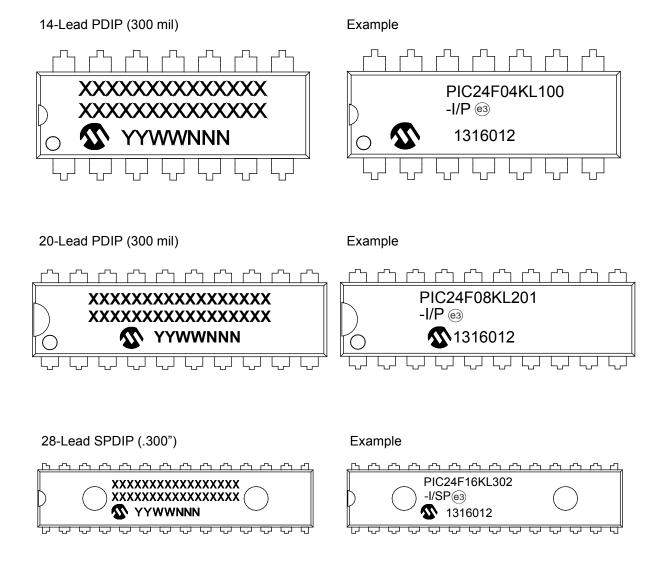

### 27.1 Package Marking Information

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3 | Product-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|---------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:   | will be                           | event the full Microchip part number cannot be marked on one line, it carried over to the next line, thus limiting the number of available ters for customer-specific information.                                                                                                                                                                                          |

© 2011-2013 Microchip Technology Inc.

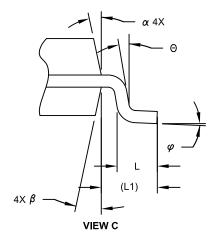

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |           |      |  |

|--------------------------|-------------|-----------|-----------|------|--|

| Dimension                | MIN         | NOM       | MAX       |      |  |

| Number of Pins           | N           |           | 28        |      |  |

| Pitch                    | е           |           | 1.27 BSC  |      |  |

| Overall Height           | A           | -         | -         | 2.65 |  |

| Molded Package Thickness | A2          | 2.05      | -         | -    |  |

| Standoff §               | A1          | 0.10      | -         | 0.30 |  |

| Overall Width            | E           | 10.30 BSC |           |      |  |

| Molded Package Width     | E1          |           | 7.50 BSC  |      |  |

| Overall Length           | D           |           | 17.90 BSC |      |  |

| Chamfer (Optional)       | h           | 0.25      | -         | 0.75 |  |

| Foot Length              | L           | 0.40      | -         | 1.27 |  |

| Footprint                | L1          |           | 1.40 REF  |      |  |

| Lead Angle               | Θ           | 0°        | -         | -    |  |

| Foot Angle               | $\varphi$   | 0°        | -         | 8°   |  |

| Lead Thickness           | С           | 0.18      | -         | 0.33 |  |

| Lead Width               | b           | 0.31      | -         | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°        | -         | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -         | 15°  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-62077-620-9

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.