Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16kl402-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                             | 9   |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers |     |

| 3.0   | СРИ                                                         |     |

| 4.0   | Memory Organization                                         | 31  |

| 5.0   | Flash Program Memory                                        | 47  |

| 6.0   | Data EEPROM Memory                                          | 53  |

| 7.0   | Resets                                                      | 59  |

| 8.0   | Interrupt Controller                                        | 65  |

| 9.0   | Oscillator Configuration                                    |     |

| 10.0  | Power-Saving Features                                       | 105 |

| 11.0  | I/O Ports                                                   | 111 |

| 12.0  | Timer1                                                      | 115 |

| 13.0  | Timer2 Module                                               | 117 |

| 14.0  | Timer3 Module                                               | 119 |

| 15.0  |                                                             |     |

| 16.0  | Capture/Compare/PWM (CCP) and Enhanced CCP Modules          | 125 |

| 17.0  | Master Synchronous Serial Port (MSSP)                       | 135 |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)          | 149 |

| 19.0  | 10-Bit High-Speed A/D Converter                             | 157 |

| 20.0  |                                                             |     |

| 21.0  | Comparator Voltage Reference                                | 171 |

| 22.0  | High/Low-Voltage Detect (HLVD)                              | 173 |

| 23.0  | Special Features                                            | 175 |

| 24.0  | Development Support                                         | 187 |

| 25.0  | Instruction Set Summary                                     | 191 |

| 26.0  |                                                             |     |

| 27.0  | Packaging Information                                       | 225 |

| Appe  | endix A: Revision History                                   | 251 |

| Appe  | endix B: Migrating from PIC18/PIC24 to PIC24F16KL402        | 251 |

| Index | x                                                           | 253 |

| The I | Microchip Web Site                                          | 257 |

| Cust  | omer Change Notification Service                            |     |

| Cust  | omer Support                                                | 257 |

| Prod  | uct Identification System                                   | 259 |

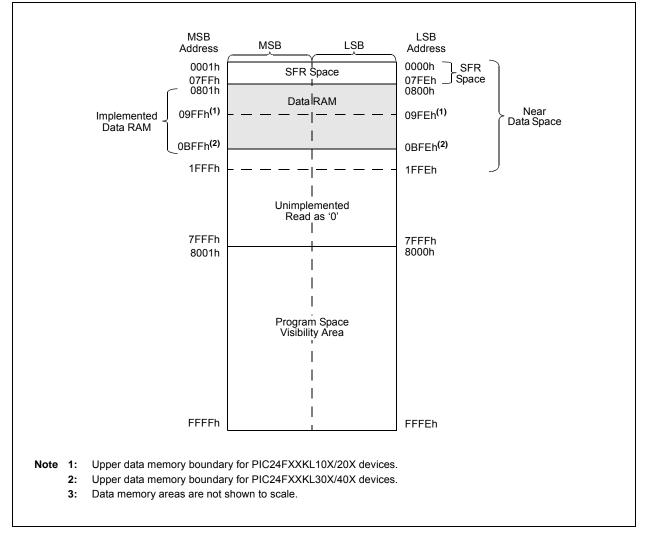

# 4.2 Data Address Space

The PIC24F core has a separate, 16-bit wide data memory space, addressable as a single linear range. The data space is accessed using two Address Generation Units (AGUs); one each for read and write operations. The data space memory map is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV) area (see Section 4.3.3 "Reading Data From Program Memory Using Program Space Visibility"). Depending on the particular device, PIC24F16KL402 family devices implement either 512 or 1024 words of data memory. If an EA points to a location outside of this area, an all zero word or byte will be returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all the data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

## FIGURE 4-3: DATA SPACE MEMORY MAP FOR PIC24F16KL402 FAMILY DEVICES<sup>(3)</sup>

| Start<br>Addr | Bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 14                             | Bit 13                                            | Bit 12                                                           | Bit 11                                                                          | Bit 10                                                                                         | Bit 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit 8                                                                                                                       | Bit 7                                                                                                                                     | Bit 6                                                                                                                                                   | Bit 5                                                                                                                                                                                | Bit 4                                                                                                                                                                | Bit 3                                                                                                                                                                                             | Bit 2                                                                                                                                                                                            | Bit 1                                                                                                                                                                                           | Bit 0                                                                                                                                                             | All<br>Resets                                                                                                                                                                                   |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 0                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 0002          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 1                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 0004          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 2                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 0006          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 3                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 8000          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 4                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 000A          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 5                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 000C          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 6                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 000E          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 7                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 0010          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 8                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 0012          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 9                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 0014          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 10                                                                                                                               |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 0016          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 11                                                                                                                               |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 0018          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 12                                                                                                                               |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 001A          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 13                                                                                                                               |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 001C          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Working                                                                                                                     | Register 14                                                                                                                               |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | 0000                                                                                                                                                                                            |

| 001E          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Vorking Regis                                                                                                               | ter 15                                                                                                                                    |                                                                                                                                                         |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 | _                                                                                                                                                                 | 0800                                                                                                                                                                                            |

| 0020          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                                                   |                                                                  |                                                                                 |                                                                                                | Sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ack Pointer Li                                                                                                              | mit Value Reg                                                                                                                             | gister                                                                                                                                                  |                                                                                                                                                                                      |                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                 |                                                                                                                                                                   | xxxx                                                                                                                                                                                            |