#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

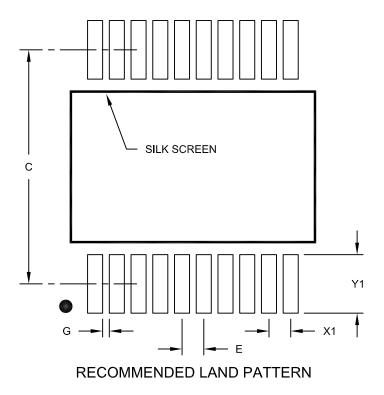

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16kl402-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2 Other Special Features

- Communications: The PIC24F16KL402 family incorporates multiple serial communication peripherals to handle a range of application requirements. The MSSP module implements both SPI and I<sup>2</sup>C™ protocols, and supports both Master and Slave modes of operation for each. Devices also include one of two UARTs with built-in IrDA<sup>®</sup> encoders/decoders.

- Analog Features: Select members of the PIC24F16KL402 family include a 10-bit A/D Converter module. The A/D module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, as well as faster sampling speeds.

The comparator modules are configurable for a wide range of operations and can be used as either a single or double comparator module.

## 1.3 Details on Individual Family Members

Devices in the PIC24F16KL402 family are available in 14-pin, 20-pin and 28-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The PIC24F16KL402 family may be thought of as four different device groups, each offering a slightly different set of features. These differ from each other in multiple ways:

- · The size of the Flash program memory

- The presence and size of data EEPROM

- The presence of an A/D Converter and the number of external analog channels available

- · The number of analog comparators

- The number of general purpose timers

- The number and type of CCP modules (i.e., CCP vs. ECCP)

- The number of serial communications modules (both MSSPs and UARTs)

The general differences between the different sub-families are shown in Table 1-1. The feature sets for specific devices are summarized in Table 1-2 and Table 1-3.

A list of the individual pin features available on the PIC24F16KL402 family devices, sorted by function, is provided in Table 1-4 (for PIC24FXXKL40X/30X devices) and Table 1-5 (for PIC24FXXKL20X/10X devices). Note that these tables show the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

| Device Group  | Program<br>Memory<br>(bytes) | Data<br>EEPROM<br>(bytes) | Timers<br>(8/16-bit) | CCP and<br>ECCP | Serial<br>(MSSP/<br>UART) | A/D<br>(channels) | Comparators |

|---------------|------------------------------|---------------------------|----------------------|-----------------|---------------------------|-------------------|-------------|

| PIC24FXXKL10X | 4K                           | _                         | 1/2                  | 2/0             | 1/1                       | _                 | 1           |

| PIC24FXXKL20X | 8K                           | —                         | 1/2                  | 2/0             | 1/1                       | 7 or 12           | 1           |

| PIC24FXXKL30X | 8K                           | 256                       | 2/2                  | 2/1             | 2/2                       | —                 | 2           |

| PIC24FXXKL40X | 8K or 16K                    | 512                       | 2/2                  | 2/1             | 2/2                       | 12                | 2           |

#### TABLE 1-1:FEATURE COMPARISON FOR PIC24F16KL402 FAMILY GROUPS

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

|              | чυ.  |        |                      | 1 001                |                      |                     |            |                       |            |       |            |            |            |         |                       |                       |          |               |

|--------------|------|--------|----------------------|----------------------|----------------------|---------------------|------------|-----------------------|------------|-------|------------|------------|------------|---------|-----------------------|-----------------------|----------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14               | Bit 13               | Bit 12               | Bit 11              | Bit 10     | Bit 9                 | Bit 8      | Bit 7 | Bit 6      | Bit 5      | Bit 4      | Bit 3   | Bit 2                 | Bit 1                 | Bit 0    | All<br>Resets |

| INTCON1      | 0080 | NSTDIS | —                    | —                    | —                    | —                   | —          | —                     | —          | _     | —          | —          | MATHERR    | ADDRERR | STKERR                | OSCFAIL               | —        | 0000          |

| INTCON2      | 0082 | ALTIVT | DISI                 | _                    | —                    | —                   | _          | _                     | —          | —     | _          | —          | _          | _       | INT2EP                | INT1EP                | INT0EP   | 0000          |

| IFS0         | 0084 | NVMIF  | _                    | AD1IF                | U1TXIF               | U1RXIF              | _          | _                     | T3IF       | T2IF  | CCP2IF     | _          | _          | T1IF    | CCP1IF                | _                     | INT0IF   | 0000          |

| IFS1         | 0086 | U2TXIF | U2RXIF               | INT2IF               | _                    | T4IF <sup>(1)</sup> | _          | CCP3IF <sup>(1)</sup> | _          | _     | _          | _          | INT1IF     | CNIF    | CMIF                  | BCL1IF                | SSP1IF   | 0000          |

| IFS2         | 8800 |        | _                    | _                    | _                    |                     | _          | _                     | _          | _     | _          | T3GIF      | _          | _       | _                     | _                     | _        | 0000          |

| IFS3         | 008A | —      | _                    | _                    | —                    | —                   | _          | _                     | —          | _     | _          | —          | _          | _       | BCL2IF <sup>(1)</sup> | SSP2IF <sup>(1)</sup> | —        | 0000          |

| IFS4         | 008C | —      | _                    | _                    | —                    | _                   | _          | _                     | HLVDIF     | _     | _          | _          | _          | _       | U2ERIF                | U1ERIF                | _        | 0000          |

| IFS5         | 008E | —      | _                    | _                    | —                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | _                     | _                     | ULPWUIF  | 0000          |

| IEC0         | 0094 | NVMIE  | _                    | AD1IE                | U1TXIE               | U1RXIE              | _          | _                     | T3IE       | T2IE  | CCP2IE     | _          | _          | T1IE    | CCP1IE                | _                     | INT0IE   | 0000          |

| IEC1         | 0096 | U2TXIE | U2RXIE               | INT2IE               | —                    | T4IE <sup>(1)</sup> | _          | CCP3IE <sup>(1)</sup> | _          | _     | _          | _          | INT1IE     | CNIE    | CMIE                  | BCL1IE                | SSP1IE   | 0000          |

| IEC2         | 0098 | _      | _                    | -                    | —                    | _                   | _          | _                     | _          |       | _          | T3GIE      | _          | _       | _                     | _                     | -        | 0000          |

| IEC3         | 009A | _      | _                    |                      | —                    | _                   | _          | _                     | _          |       | _          | _          | -          | _       | BCL2IE <sup>(1)</sup> | SSP2IE <sup>(1)</sup> |          | 0000          |

| IEC4         | 009C | _      | _                    |                      | —                    | _                   | _          | _                     | HLVDIE     |       | _          | _          | -          | _       | U2ERIE                | U1ERIE                |          | 0000          |

| IEC5         | 009E | _      | _                    |                      | —                    | _                   | _          | _                     | _          |       | _          | _          | -          | _       | _                     | _                     | ULPWUIE  | 0000          |

| IPC0         | 00A4 | —      | T1IP2                | T1IP1                | T1IP0                | _                   | CCP1IP2    | CCP1IP1               | CCP1IP0    | _     | _          | _          | _          | _       | INT0IP2               | INT0IP1               | INT0IP0  | 4404          |

| IPC1         | 00A6 | _      | T2IP2                | T2IP1                | T2IP0                | _                   | CCP2IP2    | CCP2IP1               | CCP2IP0    |       | _          | _          | -          | _       | _                     | _                     | -        | 4400          |

| IPC2         | 00A8 | _      | U1RXIP2              | U1RXIP1              | U1RXIP0              | _                   | _          | _                     | _          |       | _          | _          | -          | _       | T3IP2                 | T3IP1                 | T3IP0    | 4004          |

| IPC3         | 00AA | _      | NVMIP2               | NVMIP1               | NVMIP0               | _                   | _          | _                     | _          |       | AD1IP2     | AD1IP1     | AD1IP0     | _       | U1TXIP2               | U1TXIP1               | U1TXIP0  | 4044          |

| IPC4         | 00AC | _      | CNIP2                | CNIP1                | CNIP0                | _                   | CMIP2      | CMIP1                 | CMIP0      |       | BCL1IP2    | BCL1IP1    | BCL1IP0    | _       | SSP1IP2               | SSP1IP1               | SS1IP0   | 4444          |

| IPC5         | 00AE | _      | _                    | -                    | —                    | _                   | _          | _                     | _          |       | _          | _          | _          | _       | INT1IP2               | INT1IP1               | INT1IP0  | 0004          |

| IPC6         | 00B0 | _      | T4IP2 <sup>(1)</sup> | T4IP1 <sup>(1)</sup> | T4IP0 <sup>(1)</sup> | _                   | _          | _                     | _          |       | CCP3IP2(1) | CCP3IP1(1) | CCP3IP0(1) | _       | —                     | —                     |          | 4040          |

| IPC7         | 00B2 | _      | U2TXIP2              | U2TXIP1              | U2TXIP0              | _                   | U2RXIP2    | U2RXIP1               | U2RXIP0    |       | INT2IP2    | INT2IP1    | INT2IP0    | _       | _                     | _                     |          | 4440          |

| IPC9         | 00B6 | _      | _                    | -                    | —                    | _                   | _          | —                     | _          |       | T3GIP2     | T3GIP1     | T3GIP0     | _       | _                     | _                     |          | 0040          |

| IPC12        | 00BC | _      | _                    | _                    | —                    | _                   | BCL2IP2(1) | BCL2IP1(1)            | BCL2IP0(1) |       | SSP2IP2(1) | SSP2IP1(1) | SSP2IP0(1) | _       | _                     | _                     |          | 0440          |

| IPC16        | 00C4 | _      | _                    | _                    | _                    | _                   | U2ERIP2    | U2ERIP1               | U2ERIP0    | _     | U1ERIP2    | U1ERIP1    | U1ERIP0    | _       | _                     | —                     | _        | 0440          |

| IPC18        | 00C8 | _      | _                    | _                    | _                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | HLVDIP2               | HLVDIP1               | HLVDIP0  | 0004          |

| IPC20        | 00CC | _      | _                    | _                    | _                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | ULPWUIP2              | ULPWUIP1              | ULPWUIP0 | 0004          |

| INTTREG      | 00E0 | CPUIRQ | r                    | VHOLD                | _                    | ILR3                | ILR2       | ILR1                  | ILR0       | _     | VECNUM6    | VECNUM5    | VECNUM4    | VECNUM3 | VECNUM2               | VECNUM1               | VECNUM0  | 0000          |

Legend: Note 1:

Legend: — = unimplemented, read as '0', r = reserved. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

#### 4.2.5 SOFTWARE STACK

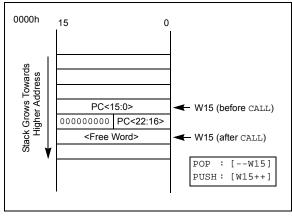

In addition to its use as a Working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer. The pointer always points to the first available free word and grows from lower to higher addresses. It predecrements for stack pops and post-increments for stack pushes, as shown in Figure 4-4.

Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated, using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation.

Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 0DF6, in RAM, initialize the SPLIM with the value, 0DF4.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the Special Function Register (SFR) space.

**Note:** A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

FIGURE 4-4: CALL STACK FRAME

## 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit wide program space and 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Apart from the normal execution, the PIC24F architecture provides two methods by which the program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space, PSV

Table instructions allow an application to read or write small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. It can only access the least significant word (lsw) of the program word.

#### 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit (MSb) of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility Page Address register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike the table operations, this limits remapping operations strictly to the user memory area.

Table 4-20 and Figure 4-5 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> bits refer to a program space word, whereas the D<15:0> bits refer to a data space word.

#### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

| // C example using MPLAB C30                                                                  |                                                                                     |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| <pre>intattribute ((space(auto_psv))) progAddr = &amp;progAddr<br/>unsigned int offset;</pre> | // Global variable located in Pgm Memory $% \mathcal{T}_{\mathcal{T}}$              |

| //Set up pointer to the first memory location to be written                                   |                                                                                     |

| <pre>TBLPAG =builtin_tblpage(&amp;progAddr); offset = &amp;progAddr &amp; 0xFFFF;</pre>       | // Initialize PM Page Boundary SFR<br>// Initialize lower word of address           |

| <pre>builtin_tblwtl(offset, 0x0000);</pre>                                                    | <pre>// Set base address of erase block // with dummy latch write</pre>             |

| NVMCON = $0 \times 4058$ ;                                                                    | // Initialize NVMCON                                                                |

| <pre>asm("DISI #5");</pre>                                                                    | <pre>// Block all interrupts for next 5 // instructions</pre>                       |

| builtin_write_NVM();                                                                          | <pre>// Instructions // C30 function to perform unlock // sequence and set WR</pre> |

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| MOV #0x4004, W0 ;                                                     |       |

|-----------------------------------------------------------------------|-------|

|                                                                       |       |

| MOV W0, NVMCON ; Initialize NVMCON                                    |       |

| ; Set up a pointer to the first program memory location to be written |       |

| ; program memory selected, and writes enabled                         |       |

| MOV #0x0000, W0 ;                                                     |       |

| MOV W0, TBLPAG ; Initialize PM Page Boundary SFR                      |       |

| MOV #0x6000, W0 ; An example program memory addre                     | SS    |

| ; Perform the TBLWT instructions to write the latches                 |       |

| ; 0th_program_word                                                    |       |

| MOV #LOW_WORD_0, W2 ;                                                 |       |

| MOV #HIGH_BYTE_0, W3 ;                                                |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      | latch |

| TBLWTH W3, [W0++] ; Write PM high byte into program                   | latch |

| ; lst_program_word                                                    |       |

| MOV #LOW_WORD_1, W2 ;                                                 |       |

| MOV #HIGH_BYTE_1, W3 ;                                                |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      | latch |

| TBLWTH W3, [W0++] ; Write PM high byte into program                   | latch |

| ; 2nd_program_word                                                    |       |

| MOV #LOW_WORD_2, W2 ;                                                 |       |

| MOV #HIGH_BYTE_2, W3 ;                                                |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      | latch |

| TBLWTH W3, [W0++] ; Write PM high byte into program                   | latch |

| •                                                                     |       |

| •                                                                     |       |

| · ·                                                                   |       |

| ; 32nd_program_word                                                   |       |

| MOV #LOW_WORD_31, W2 ;                                                |       |

| MOV #HIGH_BYTE_31, W3 ;                                               |       |

| TBLWTL W2, [W0] ; Write PM low word into program                      |       |

| TBLWTH W3, [W0]   ; Write PM high byte into program                   | latch |

#### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

int __attribute__ ((space(auto_psv))) progAddr = &progAddr; // Global variable located in Pgm Memory

unsigned int offset;

unsigned int i;

// Buffer of data to write

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW];

//Set up NVMCON for row programming

NVMCON = 0 \times 4004;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

offset = &progAddr & 0xFFFF;

// Initialize lower word of address

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]);

// Write to address low word

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2i

// Increment address

}

```

#### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; | Block all interrupts                  |

|------|-------------|---|---------------------------------------|

|      |             |   | for next 5 instructions               |

| MOV  | #0x55, W0   |   |                                       |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                      |

| MOV  | #0xAA, W1   | ; |                                       |

| MOV  | W1, NVMKEY  | ; | Write the AA key                      |

| BSET | NVMCON, #WR | ; | Start the erase sequence              |

| NOP  |             | ; | 2 NOPs required after setting WR      |

| NOP  |             | ; |                                       |

| BTSC | NVMCON, #15 | ; | Wait for the sequence to be completed |

| BRA  | \$-2        | ; |                                       |

|      |             |   |                                       |

#### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB C30 |                                                 |

|------------------------------|-------------------------------------------------|

| asm("DISI #5");              | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();         | // Perform unlock sequence and set WR           |

#### REGISTER 8-17: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0         | R/W-1                                                                                                         | R/W-0                                  | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|

|             | T1IP2                                                                                                         | T1IP1                                  | T1IP0            | _                 | CCP1IP2          | CCP1IP1         | CCP1IP0 |  |  |  |  |  |

| pit 15      |                                                                                                               |                                        |                  |                   |                  |                 | bit 8   |  |  |  |  |  |

| U-0         | U-0                                                                                                           | U-0                                    | U-0              | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

| 0-0         | 0-0                                                                                                           | 0-0                                    | 0-0              | 0-0               | INT0IP2          | INT0IP1         | INT0IP0 |  |  |  |  |  |

| pit 7       |                                                                                                               |                                        | _                | _                 |                  |                 | bit (   |  |  |  |  |  |

|             |                                                                                                               |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

| _egend:     |                                                                                                               |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

| R = Readab  | ole bit                                                                                                       | W = Writable                           | bit              | U = Unimplen      | nented bit, read | l as '0'        |         |  |  |  |  |  |

| n = Value a | at POR                                                                                                        | '1' = Bit is set                       |                  | '0' = Bit is cle  | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

| bit 15      | Unimpleme                                                                                                     | nted: Read as '                        | 0'               |                   |                  |                 |         |  |  |  |  |  |

| bit 14-12   | -                                                                                                             | Timer1 Interrupt                       |                  |                   |                  |                 |         |  |  |  |  |  |

| JIL 14-12   |                                                                                                               | -                                      | -                | (intorrunt)       |                  |                 |         |  |  |  |  |  |

|             | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul>                                |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

|             | •                                                                                                             |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

|             | •                                                                                                             |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

|             |                                                                                                               | upt is Priority 1<br>upt source is dis | abled            |                   |                  |                 |         |  |  |  |  |  |

| bit 11      | Unimpleme                                                                                                     | nted: Read as '                        | 0'               |                   |                  |                 |         |  |  |  |  |  |

| oit 10-8    | CCP1IP<2:0                                                                                                    | D>: Capture/Con                        | npare/PWM1 In    | nterrupt Priority | bits             |                 |         |  |  |  |  |  |

|             | 111 = Interr                                                                                                  | upt is Priority 7 (                    | highest priority | interrupt)        |                  |                 |         |  |  |  |  |  |

|             | •                                                                                                             | •                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|             | •                                                                                                             |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

|             | •<br>001 = Interr                                                                                             | upt is Priority 1                      |                  |                   |                  |                 |         |  |  |  |  |  |

|             |                                                                                                               | upt source is dis                      | abled            |                   |                  |                 |         |  |  |  |  |  |

| oit 7-3     | Unimpleme                                                                                                     | nted: Read as '                        | 0'               |                   |                  |                 |         |  |  |  |  |  |

| oit 2-0     | -                                                                                                             |                                        |                  | its               |                  |                 |         |  |  |  |  |  |

|             | INTOIP<2:0>: External Interrupt 0 Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

|             | •                                                                                                             |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

|             | •                                                                                                             |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

|             | •                                                                                                             |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

|             |                                                                                                               |                                        |                  |                   |                  |                 |         |  |  |  |  |  |

|             |                                                                                                               | upt is Priority 1<br>upt source is dis | ablod            |                   |                  |                 |         |  |  |  |  |  |

## REGISTER 8-19: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0          | R/W-1                   | R/W-0                                                   | R/W-0            | U-0              | U-0             | U-0             | U-0                |  |  |

|--------------|-------------------------|---------------------------------------------------------|------------------|------------------|-----------------|-----------------|--------------------|--|--|

| _            | U1RXIP2                 | U1RXIP1                                                 | U1RXIP0          |                  | _               | _               |                    |  |  |

| bit 15       |                         |                                                         | L                |                  | l               |                 | bit 8              |  |  |

|              |                         |                                                         |                  |                  |                 |                 |                    |  |  |

| U-0          | U-0                     | U-0                                                     | U-0              | U-0              | R/W-1           | R/W-0           | R/W-0              |  |  |

| _            | —                       | —                                                       | —                | _                | T3IP2           | T3IP1           | T3IP0              |  |  |

| bit 7        |                         |                                                         | •                |                  |                 |                 | bit 0              |  |  |

|              |                         |                                                         |                  |                  |                 |                 |                    |  |  |

| Legend:      |                         |                                                         |                  |                  |                 |                 |                    |  |  |

| R = Readab   | le bit                  | W = Writable                                            | bit              | U = Unimpler     | nented bit, rea | d as '0'        |                    |  |  |

| -n = Value a | t POR                   | '1' = Bit is set                                        |                  | '0' = Bit is cle | ared            | x = Bit is unkr | x = Bit is unknown |  |  |

| bit 14-12    |                         | >: UART1 Rece<br>pt is Priority 7 (<br>pt is Priority 1 | •                |                  |                 |                 |                    |  |  |

|              | 000 = Interru           | pt source is dis                                        |                  |                  |                 |                 |                    |  |  |

| bit 11-3     | •                       | ted: Read as '                                          |                  |                  |                 |                 |                    |  |  |

| bit 2-0      | T3IP<2:0>: ⊺            | imer3 Interrupt                                         | Priority bits    |                  |                 |                 |                    |  |  |

|              | 111 = Interru<br>•<br>• | pt is Priority 7(                                       | highest priority | interrupt)       |                 |                 |                    |  |  |

|              | •                       |                                                         |                  |                  |                 |                 |                    |  |  |

| U-0          | U-0                    | U-0                    | U-0                    | U-0                | R/W-1                  | R/W-0                  | R/W-0                  |

|--------------|------------------------|------------------------|------------------------|--------------------|------------------------|------------------------|------------------------|

|              | —                      |                        |                        | _                  | BCL2IP2 <sup>(1)</sup> | BCL2IP1 <sup>(1)</sup> | BCL2IP0 <sup>(1)</sup> |

| bit 15       |                        |                        |                        |                    |                        |                        | bit 8                  |

|              |                        |                        |                        |                    |                        |                        |                        |

| U-0          | R/W-1                  | R/W-0                  | R/W-0                  | U-0                | U-0                    | U-0                    | U-0                    |

| —            | SSP2IP2 <sup>(1)</sup> | SSP2IP1 <sup>(1)</sup> | SSP2IP0 <sup>(1)</sup> | —                  | —                      | —                      | —                      |

| bit 7        |                        |                        |                        |                    |                        |                        | bit 0                  |

|              |                        |                        |                        |                    |                        |                        |                        |

| Legend:      |                        |                        |                        |                    |                        |                        |                        |

| R = Readab   | le bit                 | W = Writable           | bit                    | U = Unimplem       | nented bit, read       | l as '0'               |                        |

| -n = Value a | t POR                  | '1' = Bit is set       |                        | '0' = Bit is clea  | ared                   | x = Bit is unkn        | own                    |

|              |                        |                        |                        |                    |                        |                        |                        |

| bit 15-11    | •                      | ted: Read as '         |                        |                    |                        |                        |                        |

| bit 10-8     |                        |                        |                        | Interrupt Priori   | ty bits <sup>(1)</sup> |                        |                        |

|              | 111 = Interru          | pt is Priority 7(      | highest priority       | interrupt)         |                        |                        |                        |

|              | •                      |                        |                        |                    |                        |                        |                        |

|              | •                      |                        |                        |                    |                        |                        |                        |

|              | 001 = Interru          |                        |                        |                    |                        |                        |                        |

|              | •                      | pt source is dis       |                        |                    |                        |                        |                        |

| bit 7        | •                      | ted: Read as '         |                        |                    |                        |                        |                        |

| bit 6-4      |                        |                        |                        | rupt Priority bits | <sub>S</sub> (1)       |                        |                        |

|              | 111 = Interru          | ot is Priority 7 (     | highest priority       | interrupt)         |                        |                        |                        |

|              | •                      |                        |                        |                    |                        |                        |                        |

|              | •                      |                        |                        |                    |                        |                        |                        |

|              | 001 = Interru          | •                      |                        |                    |                        |                        |                        |

|              |                        | ot source is dis       |                        |                    |                        |                        |                        |

| bit 3-0      | Unimplemen             | ted: Read as '         | )'                     |                    |                        |                        |                        |

|              |                        |                        |                        |                    |                        |                        |                        |

#### REGISTER 8-26: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

## 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

Note: The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 23.0** "**Special Features**" for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically, as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM, with LPRC as a clock source, are enabled) or SOSC (if SOSCEN remains enabled).

Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

## 10.2.1 SLEEP MODE

Sleep mode includes these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum, provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if any active module has selected the LPRC as its source, including the WDT, Timer1 and Timer3.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features, or peripherals, may continue to operate in Sleep mode. This includes items, such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- On any form of device Reset

- On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

#### 10.2.2 IDLE MODE

Idle mode has these features:

- The CPU will stop executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.5 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is re-applied to the CPU. Instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

## 11.3 Input Change Notification

The Input Change Notification (ICN) function of the I/O ports allows the PIC24F16KL402 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 23 external signals that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the Change Notification (CN) module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately, using the CNPD1 and CNPD2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to VSS by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

**Note:** Pull-ups and pull-downs on Change Notification pins should always be disabled whenever the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE (ASSEMBLY LANGUAGE)

| MOV  | #0xFF00, W0 | ; Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|------|-------------|-------------------------------------------------------------|

| MOV  | W0, TRISB   |                                                             |

| MOV  | #0x00FF, W0 | ; Enable PORTB<15:8> digital input buffers                  |

| MOV  | W0, ANSB    |                                                             |

| NOP  |             | ; Delay 1 cycle                                             |

| BTSS | PORTB, #13  | ; Next Instruction                                          |

|      |             |                                                             |

#### EXAMPLE 11-2: PORT WRITE/READ EXAMPLE (C LANGUAGE)

| TRISB = 0xFF00;          | // Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|--------------------------|--------------------------------------------------------------|

| ANSB = $0 \times 00 FF;$ | // Enable PORTB<15:8> digital input buffers                  |

| NOP();                   | // Delay 1 cycle                                             |

| if(PORTBbits.RB13 == 1)  | // execute following code if PORTB pin 13 is set.            |

| {                        |                                                              |

| }                        |                                                              |

##

| U-0          | U-0                                                                                          | U-0                                | U-0              | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |

|--------------|----------------------------------------------------------------------------------------------|------------------------------------|------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

|              | _                                                                                            |                                    |                  |                       |                       |                       | _                     |  |  |  |

| oit 15       |                                                                                              |                                    |                  |                       |                       |                       | bit                   |  |  |  |

| R/W-0        | R/W-0                                                                                        |                                    |                  |                       |                       | R/W-0                 | R/W-0                 |  |  |  |

| -            |                                                                                              | R/W-0                              | R/W-0            | R/W-0                 | R/W-0                 |                       |                       |  |  |  |

| PM1          | PM0                                                                                          | DC1B1                              | DC1B0            | CCP1M3 <sup>(2)</sup> | CCP1M2 <sup>(2)</sup> | CCP1M1 <sup>(2)</sup> | CCP1M0 <sup>(2)</sup> |  |  |  |

| oit 7        |                                                                                              |                                    |                  |                       |                       |                       | bit                   |  |  |  |

| Legend:      |                                                                                              |                                    |                  |                       |                       |                       |                       |  |  |  |

| R = Readal   | ble bit                                                                                      | W = Writable                       | bit              | U = Unimplen          | nented bit, read      | d as '0'              |                       |  |  |  |

| -n = Value a | at POR                                                                                       | '1' = Bit is set                   |                  | '0' = Bit is clea     | ared                  | x = Bit is unkr       | nown                  |  |  |  |

| oit 15-8     | Unimplemen                                                                                   | ted: Read as '                     | י'               |                       |                       |                       |                       |  |  |  |

| bit 7-6      | -                                                                                            | hanced PWM (                       |                  | ration bits           |                       |                       |                       |  |  |  |

|              |                                                                                              | 2> = 00, 01, 10                    |                  |                       |                       |                       |                       |  |  |  |

|              |                                                                                              | ssigned as a ca                    |                  | ompare output;        | P1B, P1C and          | P1D are assign        | ed as port pir        |  |  |  |

|              | <u>If CCP1M&lt;3:2</u>                                                                       | •                                  |                  |                       |                       | 0                     |                       |  |  |  |

|              |                                                                                              | ge output reve                     | rse: P1B is mo   | dulated; P1C is       | active; P1A a         | nd P1D are ina        | ctive                 |  |  |  |

|              |                                                                                              | dge output: P                      | 1A, P1B are      | modulated wit         | h dead-band           | control; P1C          | and P1D a             |  |  |  |

|              |                                                                                              | d as port pins                     |                  |                       |                       |                       |                       |  |  |  |

|              |                                                                                              | ge output forwa<br>utput: P1A, P1E |                  |                       |                       | are inactive          | 9                     |  |  |  |

| L:L T 4      | -                                                                                            | -                                  |                  |                       |                       |                       |                       |  |  |  |

| bit 5-4      | DC1B<1:0>: PWM Duty Cycle bit 1 and bit 0 for CCP1 Module bits<br>Capture and Compare modes: |                                    |                  |                       |                       |                       |                       |  |  |  |

|              | Unused.                                                                                      | compare mode                       | <u>s</u> :       |                       |                       |                       |                       |  |  |  |

|              | PWM mode:                                                                                    |                                    |                  |                       |                       |                       |                       |  |  |  |

|              |                                                                                              | e the two Leas                     | t Significant bi | ts (bit 1 and bit     | 0) of the 10-b        | it PWM duty cy        | cle. The eid          |  |  |  |

|              |                                                                                              | ant bits (DC1B<                    |                  |                       |                       |                       | , e. e. e. e. g       |  |  |  |

| bit 3-0      | -                                                                                            | ECCP1 Modu                         | -                |                       |                       |                       |                       |  |  |  |

|              | 1111 = PWM mode: P1A and P1C are active-low; P1B and P1D are active-low                      |                                    |                  |                       |                       |                       |                       |  |  |  |

|              | 1110 = PWM mode: P1A and P1C are active-low; P1B and P1D are active-high                     |                                    |                  |                       |                       |                       |                       |  |  |  |

|              |                                                                                              | l mode: P1A an                     |                  |                       |                       |                       |                       |  |  |  |

|              |                                                                                              | I mode: P1A an                     |                  | 0                     |                       | 0                     |                       |  |  |  |

|              |                                                                                              | pare mode: Spe                     |                  |                       |                       |                       |                       |  |  |  |

|              |                                                                                              | oare mode: Ge<br>ts I/O state)     | nerates softwar  | re interrupt on c     | compare match         | (CCPTIF DIUS          | set, CCPT p           |  |  |  |

|              |                                                                                              | pare mode: Initia                  | alizes CCP1 pi   | n hiah: on comp       | pare match. for       | ces CCP1 pin lo       | w (CCP1IF b           |  |  |  |

|              | is set                                                                                       |                                    |                  | <b>J</b> , <b>F F</b> | ,                     | P                     | <b>\</b>              |  |  |  |

|              | 1000 = Com<br>bit is                                                                         | pare mode: Init                    | ializes CCP1 p   | oin low; on com       | pare match, fo        | rces CCP1 pin         | high (CCP1            |  |  |  |

|              |                                                                                              | ure mode: Ever                     | y 16th rising e  | dge                   |                       |                       |                       |  |  |  |

|              | 0110 = Captu                                                                                 | ure mode: Ever                     | y 4th rising ed  |                       |                       |                       |                       |  |  |  |

|              | •                                                                                            | ure mode: Ever                     |                  |                       |                       |                       |                       |  |  |  |

|              |                                                                                              | ure mode: Ever                     | y falling edge   |                       |                       |                       |                       |  |  |  |

|              | 0011 = Rese                                                                                  | rved<br>bare mode: Tog             | ales output on   | match (CCD1)          | E bit is cot)         |                       |                       |  |  |  |

|              | 0010 = Comp<br>0001 = Rese                                                                   |                                    | gies output on   |                       |                       |                       |                       |  |  |  |

|              |                                                                                              | ure/Compare/P                      | WM is disabled   | d (resets CCP1        | module)               |                       |                       |  |  |  |

| Note 1:      | This register is im                                                                          | plemented only                     | y on PIC24FX)    | (KL40X/30X de         | evices. For all o     | other devices, C      | CCP1CON is            |  |  |  |

|              | configured as Reg                                                                            |                                    |                  |                       |                       | ,                     |                       |  |  |  |

| -            | 000414 -0-0- 1                                                                               |                                    |                  |                       |                       |                       |                       |  |  |  |

2: CCP1M<3:0> = 1011 will only reset the timer and not start the A/D conversion on a CCP1 match.

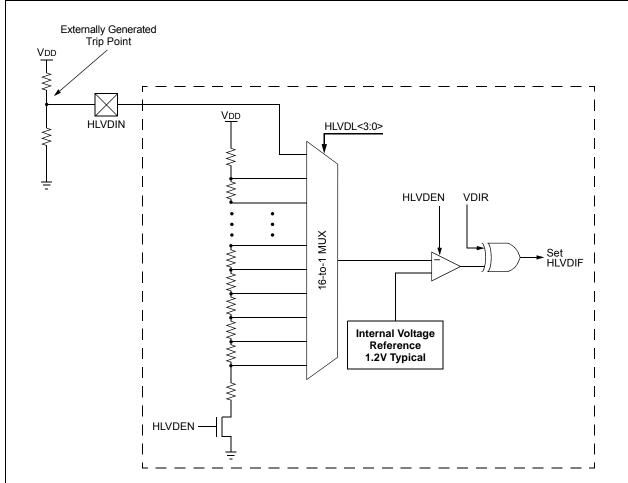

## 22.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the High/Low-Voltage Detect, refer to the "dsPIC33/PIC24 Family Reference Manual", "High-Level Integration with Programmable High/Low-Voltage Detect (HLVD)" (DS39725).

The High/Low-Voltage Detect module (HLVD) is a programmable circuit that allows the user to specify both the device voltage trip point and the direction of change.

An interrupt flag is set if the device experiences an excursion past the trip point in the direction of change. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The HLVD Control register (see Register 22-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

## FIGURE 22-1: HIGH/LOW-VOLTAGE DETECT (HLVD) MODULE BLOCK DIAGRAM

NOTES:

## 24.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 24.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## 25.0 INSTRUCTION SET SUMMARY

**Note:** This chapter is a brief summary of the PIC24F Instruction Set Architecture (ISA) and is not intended to be a comprehensive reference source.

The PIC24F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

Table 25-1 lists the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 25-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value, 'f'

- The destination, which could either be the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register, 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the Table Read and Table Write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all of the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all Table Reads and Table Writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

| DC CHARACTERIS   | TICS                   |       | $\begin{array}{l} \mbox{Standard Operating Conditions: } 1.8V \mbox{ to } 3.6V \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extend} \end{array}$ |            |      | +85°C for Industrial      |  |

|------------------|------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|---------------------------|--|

| Parameter No.    | Typical <sup>(1)</sup> | Max   | Units                                                                                                                                                                                                                                                    | Conditions |      |                           |  |

| Power-Down Curre | nt (IPD)               |       |                                                                                                                                                                                                                                                          |            |      |                           |  |

| DC60             | 0.01                   | 0.20  | μA                                                                                                                                                                                                                                                       | -40°C      |      |                           |  |

|                  | 0.03                   | 0.20  | μA                                                                                                                                                                                                                                                       | +25°C      |      |                           |  |