#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16kl402t-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

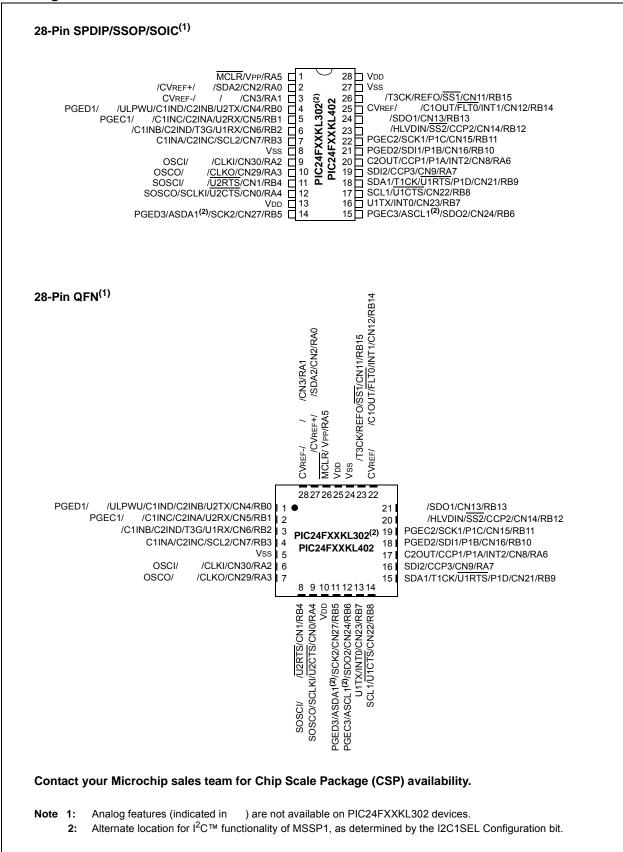

#### Pin Diagrams: PIC24FXXKL302/402

|          |                                  | Pin N         | umber                             |               |     |                   |                                                     |

|----------|----------------------------------|---------------|-----------------------------------|---------------|-----|-------------------|-----------------------------------------------------|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | I/O | Buffer            | Description                                         |

| AN0      | 2                                | 19            | 2                                 | 27            | I   | ANA               | A/D Analog Inputs. Not available on PIC24F16KL30X   |

| AN1      | 3                                | 20            | 3                                 | 28            | I   | ANA               | family devices.                                     |

| AN2      | 4                                | 1             | 4                                 | 1             | I   | ANA               |                                                     |

| AN3      | 5                                | 2             | 5                                 | 2             | I   | ANA               |                                                     |

| AN4      | 6                                | 3             | 6                                 | 3             | Ι   | ANA               |                                                     |

| AN5      | _                                | _             | 7                                 | 4             | Ι   | ANA               |                                                     |

| AN9      | 18                               | 15            | 26                                | 23            | I   | ANA               |                                                     |

| AN10     | 17                               | 14            | 25                                | 22            | Ι   | ANA               |                                                     |

| AN11     | 16                               | 13            | 24                                | 21            | Ι   | ANA               |                                                     |

| AN12     | 15                               | 12            | 23                                | 20            | Ι   | ANA               |                                                     |

| AN13     | 7                                | 4             | 9                                 | 6             | Ι   | ANA               |                                                     |

| AN14     | 8                                | 5             | 10                                | 7             | I   | ANA               |                                                     |

| AN15     | 9                                | 6             | 11                                | 8             | I   | ANA               |                                                     |

| ASCL1    | _                                | _             | 15                                | 12            | I/O | I <sup>2</sup> C™ | Alternate MSSP1 I <sup>2</sup> C Clock Input/Output |

| ASDA1    | _                                | _             | 14                                | 11            | I/O | l <sup>2</sup> C  | Alternate MSSP1 I <sup>2</sup> C Data Input/Output  |

| AVdd     | 20                               | 17            | 28                                | 25            | Ι   | ANA               | Positive Supply for Analog modules                  |

| AVss     | 19                               | 16            | 27                                | 24            | Ι   | ANA               | Ground Reference for Analog modules                 |

| CCP1     | 14                               | 11            | 20                                | 17            | I/O | ST                | CCP1/ECCP1 Capture Input/Compare and PWM<br>Output  |

| CCP2     | 15                               | 12            | 23                                | 20            | I/O | ST                | CCP2 Capture Input/Compare and PWM Output           |

| CCP3     | 13                               | 10            | 19                                | 16            | I/O | ST                | CCP3 Capture Input/Compare and PWM Output           |

| C1INA    | 8                                | 5             | 7                                 | 4             | I   | ANA               | Comparator 1 Input A (+)                            |

| C1INB    | 7                                | 4             | 6                                 | 3             | I   | ANA               | Comparator 1 Input B (-)                            |

| C1INC    | 5                                | 2             | 5                                 | 2             | I   | ANA               | Comparator 1 Input C (+)                            |

| C1IND    | 4                                | 1             | 4                                 | 1             | I   | ANA               | Comparator 1 Input D (-)                            |

| C1OUT    | 17                               | 14            | 25                                | 22            | 0   | _                 | Comparator 1 Output                                 |

| C2INA    | 5                                | 2             | 5                                 | 2             | I   | ANA               | Comparator 2 Input A (+)                            |

| C2INB    | 4                                | 1             | 4                                 | 1             | I   | ANA               | Comparator 2 Input B (-)                            |

| C2INC    | 8                                | 5             | 7                                 | 4             | Ι   | ANA               | Comparator 2 Input C (+)                            |

| C2IND    | 7                                | 4             | 6                                 | 3             | Ι   | ANA               | Comparator 2 Input D (-)                            |

| C2OUT    | 14                               | 11            | 20                                | 17            | 0   |                   | Comparator 2 Output                                 |

| CLK I    | 7                                | 4             | 9                                 | 6             | Ι   | ANA               | Main Clock Input                                    |

| CLKO     | 8                                | 5             | 10                                | 7             | 0   | _                 | System Clock Output                                 |

#### TABLE 1-4: PIC24F16KL40X/30X FAMILY PINOUT DESCRIPTIONS

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

# 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and bussing. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 **Program Address Space**

The program address memory space of the PIC24F16KL402 family is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24F16KL402 family of devices are shown in Figure 4-1.

## FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24F16KL402 FAMILY DEVICES

|                            | PIC24F04KLXXX                                                                                                                                       | PIC24F08KL2XX                                                                                              | PIC24F08KL3XX                                                                                              |       | PIC24F08KL4XX                                                                                              | PIC24F16KLXXX                                                                                     |                                                                                    |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                            | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash<br>Program Memory<br>(1408 instructions) | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash |       | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table | 000000h<br>00002h<br>00004h<br>0000FEh<br>000100h<br>000104h<br>0001FEh<br>000200h |

| User Memory Space          |                                                                                                                                                     | Program Memory<br>(2816 instructions)                                                                      | <br>Program Memory<br>(2816 instructions)                                                                  | -     | Program Memory<br>(2816 instructions)                                                                      | <br>Flash<br>Program Memory<br>(5632 instructions)                                                | - 000AFEh                                                                          |

| User Me                    | Unimplemented<br>Read '0'                                                                                                                           | Unimplemented<br>Read '0'                                                                                  | Unimplemented<br>Read '0'                                                                                  |       | Unimplemented<br>Read '0'                                                                                  | Unimplemented                                                                                     | 002BFEh                                                                            |

|                            |                                                                                                                                                     |                                                                                                            | <br>Data EEPROM<br>(256 bytes)                                                                             | -<br> | Data EEPROM<br>(512 bytes)                                                                                 | <br>Read '0'<br>Data EEPROM<br>(512 bytes)                                                        | <ul> <li>7FFE00h</li> <li>7FFF00h</li> <li>7FFFFFh</li> <li>800000h</li> </ul>     |

| Ī                          | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | 800800h                                                                            |

| ace                        | Unique ID                                                                                                                                           | Unique ID                                                                                                  | Unique ID                                                                                                  |       | Unique ID                                                                                                  | Unique ID                                                                                         | 800802h<br>800808h                                                                 |

| lory Sp                    | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | 80080Ah                                                                            |

| Mem                        | Device Config Registers                                                                                                                             | Device Config Registers                                                                                    | Device Config Registers                                                                                    |       | Device Config Registers                                                                                    | Device Config Registers                                                                           | F80000h<br>F8000Eh                                                                 |

| Configuration Memory Space | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | F80010h<br>FEFFFEh                                                                 |

|                            | DEVID (2)                                                                                                                                           | DEVID (2)                                                                                                  | DEVID (2)                                                                                                  |       | DEVID (2)                                                                                                  | DEVID (2)                                                                                         | FF0000h<br>FFFFFFh                                                                 |

Note: Memory areas are not displayed to scale.

#### TABLE 4-16: SYSTEM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | SBOREN | —      | —      | _      | CM     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 3100          |

| OSCTUN    | 0748 | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 074E | ROEN   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN | -      | HLSIDL | _      | —      | _      | _      | _      | VDIR    | BGVST | IRVST  | -     | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on configuration fuses and by type of Reset.

#### TABLE 4-17: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5  | Bit 4   | Bit 3      | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|---------|--------|--------|-------|-------|-------|-------|--------|---------|------------|--------|--------|--------|---------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | PGMONLY |        | _      | _     |       | —     | ERASE | NVMOP5 | NVMOP4  | NVMOP3     | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMKEY    | 0766 | _      | -      | -      | —       | —      |        | _     |       |       |       |        | NVM Key | / Register |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-18: ULTRA LOW-POWER WAKE-UP REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|---------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ULPWCON   | 0768 | ULPEN  | _      | ULPSIDL |        | —      | _      |       | ULPSINK |       | _     |       | _     | _     |       | _     | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-19: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|---------|-------|-------|-------|--------|--------|--------|--------|------------|

| PMD1      | 0770 | _      | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     |       | SSP1MD  | U2MD  | U1MD  |       | —      | _      |        | ADC1MD | 0000       |

| PMD2      | 0772 | _      | —      | —      | _      | —      | —      | _     | -     | _       | _     | —     | _     | —      | CCP3MD | CCP2MD | CCP1MD | 0000       |

| PMD3      | 0774 | _      | _      | _      |        |        | CMPMD  | _     | -     | —       | _     | _     |       | —      | _      | SSP2MD | —      | 0000       |

| PMD4      | 0776 |        | _      | _      | _      | _      | _      | -     | —     | ULPWUMD |       | _     | EEMD  | REFOMD | —      | HLVDMD | _      | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS30001037C-page 42

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|------------------------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY <sup>(4)</sup> | —   | —   | —   | —     |

| bit 15     |       |       |                        |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:              | SO = Settable Only bit | HC = Hardware Clearab  | le bit           |

|----------------------|------------------------|------------------------|------------------|

| -n = Value at POR    | '1' = Bit is set       | R = Readable bit       | W = Writable bit |

| '0' = Bit is cleared | x = Bit is unknown     | U = Unimplemented bit, | read as '0'      |

| bit 15   | WR: Write Control bit                                                                                                                                                                                                                       |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = Initiates a Flash memory program or erase operation; the operation is self-timed and the bit is cleared by hardware once the operation is complete</li> <li>0 = Program or erase operation is complete and inactive</li> </ul> |

|          |                                                                                                                                                                                                                                             |

| bit 14   | WREN: Write Enable bit                                                                                                                                                                                                                      |

|          | 1 = Enables Flash program/erase operations                                                                                                                                                                                                  |

|          | 0 = Inhibits Flash program/erase operations                                                                                                                                                                                                 |

| bit 13   | WRERR: Write Sequence Error Flag bit                                                                                                                                                                                                        |

|          | <ul> <li>1 = An improper program or erase sequence attempt, or termination, has occurred (bit is set automatically<br/>on any set attempt of the WR bit)</li> </ul>                                                                         |

|          | 0 = The program or erase operation completed normally                                                                                                                                                                                       |

| bit 12   | PGMONLY: Program Only Enable bit <sup>(4)</sup>                                                                                                                                                                                             |

| bit 11-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                  |

| bit 6    | ERASE: Erase/Program Enable bit                                                                                                                                                                                                             |

|          | 1 = Performs the erase operation specified by NVMOP<5:0> on the next WR command                                                                                                                                                             |

|          | 0 = Performs the program operation specified by NVMOP<5:0> on the next WR command                                                                                                                                                           |

| bit 5-0  | NVMOP<5:0>: Programming Operation Command Byte bits <sup>(1)</sup>                                                                                                                                                                          |

|          | Erase Operations (when ERASE bit is '1'):                                                                                                                                                                                                   |

|          | 1010xx = Erases entire boot block (including code-protected boot block) <sup>(2)</sup>                                                                                                                                                      |

|          | 1001xx = Erases entire memory (including boot block, configuration block, general block) <sup>(2)</sup>                                                                                                                                     |

|          | 011010 = Erases 4 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                                       |

|          | 011001 = Erases 2 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                                       |

|          | 011000 = Erases 1 row of Flash memory <sup>(3)</sup><br>0101xx = Erases entire configuration block (except code protection bits)                                                                                                            |

|          | 0101xx = Erases entire comiguration block (except code protection bits)<br>$0100xx = \text{Erases entire data EEPROM^{(4)}}$                                                                                                                |

|          | 0011xx = Erases entire general memory block programming operations                                                                                                                                                                          |

|          | 0001xx = Writes 1 row of Flash memory (when ERASE bit is '0') <sup>(3)</sup>                                                                                                                                                                |

|          |                                                                                                                                                                                                                                             |

|          | All other combinations of the NVMOP<5:0> bits are no operation.                                                                                                                                                                             |

| 2:       | Available in ICSP™ mode only. Refer to the device programming specification.                                                                                                                                                                |

- 3: The address in the Table Pointer decides which rows will be erased.

- 4: This bit is used only while accessing data EEPROM. It is implemented only in devices with data EEPROM.

. .. . \_

.....

# **REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 3

SLEEP: Wake-up from Sleep Flag bit

1 = Device has been in Sleep mode

0 = Device has not been in Sleep mode

bit 2

IDLE: Wake-up from Idle Flag bit

1 = Device has been in Idle mode

0 = Device has not been in Idle mode

0 = Device has not been in Idle mode

bit 1

BOR: Brown-out Reset Flag bit

1 = A Brown-out Reset has occurred (the BOR is also set after a POR)

0 = A Brown-out Reset has not occurred

bit 0

POR: Power-on Reset Flag bit

- 1 = A Power-up Reset has occurred

- 0 = A Power-up Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** The SBOREN bit is forced to '0' when disabled by the Configuration bits, BOREN<1:0> (FPOR<1:0>). When the Configuration bits are set to enable SBOREN, the default Reset state will be '1'.

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | —                       |

| POR (RCON<0>)     | POR                                               | —                       |

#### TABLE 7-1: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits may be set or cleared by the user software.

#### 7.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 7-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. For more information, see **Section 9.0** "Oscillator **Configuration**".

# TABLE 7-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant  |

|------------|---------------------------|

| POR        | FNOSCx Configuration bits |

| BOR        | (FNOSC<10:8>)             |

| MCLR       | COSCx Control bits        |

| WDTO       | (OSCCON<14:12>)           |

| SWR        |                           |

### REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| R/W-0         | U-0                 | R/W-0                              | R/W-0           | R/W-0             | U-0              | U-0             | R/W-0       |

|---------------|---------------------|------------------------------------|-----------------|-------------------|------------------|-----------------|-------------|

| NVMIF         | _                   | AD1IF                              | U1TXIF          | U1RXIF            |                  |                 | T3IF        |

| bit 15        |                     |                                    |                 |                   |                  |                 | bit 8       |

|               | 5444.6              |                                    |                 | 5444              |                  |                 | 5444.6      |

| R/W-0         | R/W-0               | U-0                                | U-0             | R/W-0             | R/W-0            | U-0             | R/W-0       |

| T2IF          | CCP2IF              | —                                  | —               | T1IF              | CCP1IF           | —               | INTOIF      |

| bit 7         |                     |                                    |                 |                   |                  |                 | bit (       |

| Legend:       |                     |                                    |                 |                   |                  |                 |             |

| R = Readable  | e bit               | W = Writable                       | bit             | U = Unimplen      | nented bit, read | d as '0'        |             |

| -n = Value at | POR                 | '1' = Bit is set                   |                 | '0' = Bit is clea | ared             | x = Bit is unkı | nown        |

|               |                     |                                    |                 |                   |                  |                 |             |

| bit 15        | NVMIF: NVM          | I Interrupt Flag                   | Status bit      |                   |                  |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 14        | -                   | ted: Read as '                     |                 |                   |                  |                 |             |

| bit 13        | <b>AD1IF:</b> A/D ( | Conversion Cor                     | nplete Interrup | t Flag Status bit | t                |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

| h:1 40        | -                   | request has no                     |                 | Otatus hit        |                  |                 |             |

| bit 12        |                     | RT1 Transmitter                    |                 | Status bit        |                  |                 |             |

|               |                     | request has no                     |                 |                   |                  |                 |             |

| bit 11        | -                   | RT1 Receiver In                    |                 | tatus bit         |                  |                 |             |

|               |                     | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 10-9      | Unimplemer          | ted: Read as '                     | 0'              |                   |                  |                 |             |

| bit 8         | T3IF: Timer3        | Interrupt Flag                     | Status bit      |                   |                  |                 |             |

|               | •                   | request has oc                     |                 |                   |                  |                 |             |

|               |                     | request has no                     |                 |                   |                  |                 |             |

| bit 7         |                     | Interrupt Flag                     |                 |                   |                  |                 |             |

|               |                     | request has oc<br>request has no   |                 |                   |                  |                 |             |

| bit 6         |                     | -                                  |                 | ot Flag Status b  | it               |                 |             |

|               | •                   | request has oc                     |                 |                   |                  |                 |             |

|               | 0 = Interrupt       | request has no                     | t occurred      |                   |                  |                 |             |

| bit 5-4       | Unimplemer          | ted: Read as '                     | 0'              |                   |                  |                 |             |

| bit 3         | T1IF: Timer1        | Interrupt Flag                     | Status bit      |                   |                  |                 |             |

|               | •                   | request has oc<br>request has no   |                 |                   |                  |                 |             |

| bit 2         | -                   | -                                  |                 | ot Flag Status b  | it (ECCP1 on F   | PIC24FXXKL40    | )X devices) |

|               | 1 = Interrupt       | request has oc                     | curred          | 0                 | Υ.               |                 | ,           |

| L:1 4         | -                   | request has no                     |                 |                   |                  |                 |             |

| bit 1         | -                   | ted: Read as '                     |                 |                   |                  |                 |             |

|               |                     |                                    |                 |                   |                  |                 |             |

| bit 0         |                     | rnal Interrupt 0<br>request has oc | -               |                   |                  |                 |             |

| R/W-0        | U-0           | R/W-0                                                                                     | R/W-0          | R/W-0             | U-0              | U-0            | R/W-0  |  |  |  |

|--------------|---------------|-------------------------------------------------------------------------------------------|----------------|-------------------|------------------|----------------|--------|--|--|--|

| NVMIE        |               | AD1IE                                                                                     | U1TXIE         | U1RXIE            | —                | _              | T3IE   |  |  |  |

| bit 15       |               |                                                                                           |                |                   |                  |                | bit 8  |  |  |  |

|              |               |                                                                                           |                |                   |                  |                |        |  |  |  |

| R/W-0        | R/W-0         | U-0                                                                                       | U-0            | R/W-0             | R/W-0            | U-0            | R/W-0  |  |  |  |

| T2IE         | CCP2IE        | _                                                                                         |                | T1IE              | CCP1IE           | —              | INTOIE |  |  |  |

| bit 7        |               |                                                                                           |                |                   |                  |                | bit C  |  |  |  |

| Legend:      |               |                                                                                           |                |                   |                  |                |        |  |  |  |

| R = Readab   | le bit        | W = Writable t                                                                            | bit            | U = Unimplen      | nented bit, read | l as '0'       |        |  |  |  |

| -n = Value a | t POR         | '1' = Bit is set                                                                          |                | '0' = Bit is clea | ared             | x = Bit is unk | nown   |  |  |  |

| L:4 / C      |               |                                                                                           | - 1-14         |                   |                  |                |        |  |  |  |

| bit 15       |               | /I Interrupt Enabl<br>request is enabl                                                    |                |                   |                  |                |        |  |  |  |

|              |               | request is not er                                                                         |                |                   |                  |                |        |  |  |  |

| bit 14       | Unimpleme     | nted: Read as '0                                                                          | ,              |                   |                  |                |        |  |  |  |

| bit 13       | AD1IE: A/D    | Conversion Com                                                                            | plete Interrup | t Enable bit      |                  |                |        |  |  |  |

|              |               | request is enabl                                                                          |                |                   |                  |                |        |  |  |  |

| L:1 40       | -             | request is not er                                                                         |                | <b>bla b</b> :4   |                  |                |        |  |  |  |

| bit 12       |               | <b>U1TXIE:</b> UART1 Transmitter Interrupt Enable bit<br>1 = Interrupt request is enabled |                |                   |                  |                |        |  |  |  |

|              |               | request is not er                                                                         |                |                   |                  |                |        |  |  |  |

| bit 11       | U1RXIE: UA    | RT1 Receiver In                                                                           | terrupt Enable | e bit             |                  |                |        |  |  |  |

|              |               | request is enabl                                                                          |                |                   |                  |                |        |  |  |  |

|              | -             | request is not er                                                                         |                |                   |                  |                |        |  |  |  |

| bit 10-9     | -             | nted: Read as '0                                                                          |                |                   |                  |                |        |  |  |  |

| bit 8        |               | 3 Interrupt Enable                                                                        |                |                   |                  |                |        |  |  |  |

|              |               | request is enabl<br>request is not er                                                     |                |                   |                  |                |        |  |  |  |

| bit 7        |               | 2 Interrupt Enable                                                                        |                |                   |                  |                |        |  |  |  |

|              |               | request is enabl                                                                          |                |                   |                  |                |        |  |  |  |

|              | 0 = Interrupt | request is not er                                                                         | nabled         |                   |                  |                |        |  |  |  |

| bit 6        |               | pture/Compare/F                                                                           | -              | ot Enable bit     |                  |                |        |  |  |  |

|              |               | request is enabl<br>request is not er                                                     |                |                   |                  |                |        |  |  |  |

| bit 5-4      |               | nted: Read as '0                                                                          |                |                   |                  |                |        |  |  |  |

| bit 3        | -             | Interrupt Enable                                                                          |                |                   |                  |                |        |  |  |  |

| bit 5        |               | request is enabl                                                                          |                |                   |                  |                |        |  |  |  |

|              |               | request is not er                                                                         |                |                   |                  |                |        |  |  |  |

| bit 2        | CCP1IE: Ca    | pture/Compare/F                                                                           | WM1 Interru    | ot Enable bit     |                  |                |        |  |  |  |

|              |               | request is enabl                                                                          |                |                   |                  |                |        |  |  |  |

| L:1 4        |               | request is not er                                                                         |                |                   |                  |                |        |  |  |  |

| bit 1        | -             | nted: Read as '0                                                                          |                |                   |                  |                |        |  |  |  |

| bit 0        |               | rnal Interrupt 0 E<br>request is enabl                                                    |                |                   |                  |                |        |  |  |  |

|              |               | TEQUEST IS ETIDDI                                                                         | 6U             |                   |                  |                |        |  |  |  |

#### REGISTER 8-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0                                                                        | U-0         | U-0                                                                                                | U-0             | U-0           | U-0                   | U-0    | R/W-0  |  |  |  |  |

|----------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------|-----------------|---------------|-----------------------|--------|--------|--|--|--|--|

| _                                                                          | —           | —                                                                                                  | —               | —             | —                     | —      | HLVDIE |  |  |  |  |

| bit 15                                                                     |             |                                                                                                    |                 |               |                       |        | bit 8  |  |  |  |  |

|                                                                            |             |                                                                                                    |                 |               |                       |        |        |  |  |  |  |

| U-0                                                                        | U-0         | U-0                                                                                                | U-0             | U-0           | R/W-0                 | R/W-0  | U-0    |  |  |  |  |

|                                                                            |             | <u> </u>                                                                                           |                 | —             | U2ERIE <sup>(1)</sup> | U1ERIE |        |  |  |  |  |

| bit 7                                                                      |             | bit 0                                                                                              |                 |               |                       |        |        |  |  |  |  |

|                                                                            |             |                                                                                                    |                 |               |                       |        |        |  |  |  |  |

| Legend:                                                                    |             |                                                                                                    |                 |               |                       |        |        |  |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'         |             |                                                                                                    |                 |               |                       |        |        |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |             |                                                                                                    |                 |               |                       |        |        |  |  |  |  |

|                                                                            |             |                                                                                                    |                 |               |                       |        |        |  |  |  |  |

| bit 15-9                                                                   | Unimplemer  | nted: Read as '                                                                                    | 0'              |               |                       |        |        |  |  |  |  |

| bit 8                                                                      | HLVDIE: Hig | h/Low-Voltage                                                                                      | Detect Interrup | ot Enable bit |                       |        |        |  |  |  |  |

|                                                                            |             | request is enat                                                                                    |                 |               |                       |        |        |  |  |  |  |

|                                                                            | •           | request is not e                                                                                   |                 |               |                       |        |        |  |  |  |  |

| bit 7-3                                                                    | Unimplemer  | nted: Read as '                                                                                    | 0'              |               |                       |        |        |  |  |  |  |

| bit 2                                                                      | U2ERIE: UA  | RT2 Error Inter                                                                                    | rupt Enable bit | (1)           |                       |        |        |  |  |  |  |

|                                                                            |             | request is enat                                                                                    |                 |               |                       |        |        |  |  |  |  |

|                                                                            | •           | request is not e                                                                                   |                 |               |                       |        |        |  |  |  |  |

| bit 1                                                                      |             | RT1 Error Inter                                                                                    | •               |               |                       |        |        |  |  |  |  |

|                                                                            |             | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                 |               |                       |        |        |  |  |  |  |

| bit 0                                                                      |             | nted: Read as '                                                                                    |                 |               |                       |        |        |  |  |  |  |

|                                                                            |             |                                                                                                    |                 |               |                       |        |        |  |  |  |  |

Note 1: This bit is unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

#### REGISTER 8-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0                                | U-0       | U-0             | U-0                  | U-0          | U-0                | U-0      | U-0     |

|------------------------------------|-----------|-----------------|----------------------|--------------|--------------------|----------|---------|

| _                                  | —         | —               | _                    | —            | —                  | —        | —       |

| bit 15                             |           |                 |                      | -            |                    |          | bit 8   |

|                                    |           |                 |                      |              |                    |          |         |

| U-0                                | U-0       | U-0             | U-0                  | U-0          | U-0                | U-0      | R/W-0   |

| —                                  | —         | —               | —                    | —            | —                  | —        | ULPWUIE |

| bit 7                              |           |                 |                      |              |                    |          | bit 0   |

|                                    |           |                 |                      |              |                    |          |         |

| Legend:                            |           |                 |                      |              |                    |          |         |

| R = Readable                       | e bit     | W = Writable    | bit                  | U = Unimplem | nented bit, read   | l as '0' |         |

| -n = Value at POR '1' = Bit is set |           |                 | '0' = Bit is cleared |              | x = Bit is unknown |          |         |

| <u>.</u>                           |           |                 |                      |              |                    |          |         |

| bit 15-1                           | Unimpleme | nted: Read as ' | o'                   |              |                    |          |         |

| L:1 0                              |           |                 | A                    |              |                    |          |         |

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable Bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

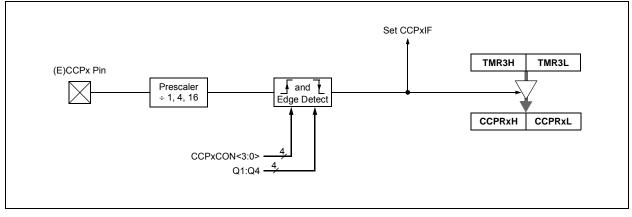

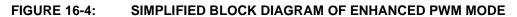

### FIGURE 16-1: GENERIC CAPTURE MODE BLOCK DIAGRAM

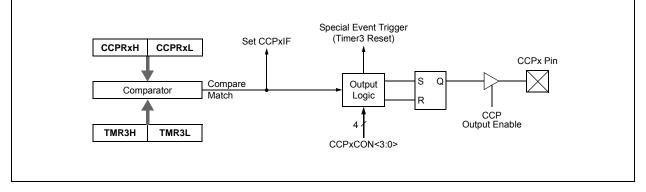

### FIGURE 16-2: GENERIC COMPARE MODE BLOCK DIAGRAM

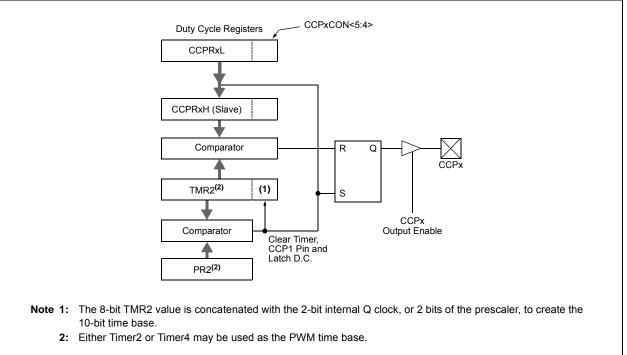

#### FIGURE 16-3: SIMPLIFIED PWM BLOCK DIAGRAM

### REGISTER 16-4: ECCP1DEL: ECCP1 ENHANCED PWM CONTROL REGISTER<sup>(1)</sup>

| U-0           | U-0         | U-0                         | U-0         | U-0                 | U-0              | U-0             | U-0                  |  |  |

|---------------|-------------|-----------------------------|-------------|---------------------|------------------|-----------------|----------------------|--|--|

| _             | —           | —                           | —           | —                   | —                | _               | —                    |  |  |

| bit 15        | •           | •                           |             |                     |                  |                 | bit 8                |  |  |

|               |             |                             |             |                     |                  |                 |                      |  |  |

| R/W-0         | R/W-0       | R/W-0                       | R/W-0       | R/W-0               | R/W-0            | R/W-0           | R/W-0                |  |  |

| PRSEN         | PDC6        | PDC5                        | PDC4        | PDC3 PDC2 PDC1 PDC0 |                  |                 |                      |  |  |

| bit 7         | ·           | •                           |             |                     |                  |                 | bit 0                |  |  |

|               |             |                             |             |                     |                  |                 |                      |  |  |

| Legend:       |             |                             |             |                     |                  |                 |                      |  |  |

| R = Readable  | e bit       | W = Writable I              | oit         | U = Unimplem        | nented bit, read | d as '0'        |                      |  |  |

| -n = Value at | POR         | '1' = Bit is set            |             | '0' = Bit is clea   | ared             | x = Bit is unkn | iown                 |  |  |

|               |             |                             |             |                     |                  |                 |                      |  |  |

| bit 15-8      | Unimplemer  | ted: Read as '0             | )'          |                     |                  |                 |                      |  |  |

| bit 7         | PRSEN: PW   | M Restart Enab              | le bit      |                     |                  |                 |                      |  |  |

|               | 1 = Upon au | to-shutdown, the            | e ECCPASE b | it clears automa    | tically once the | e shutdown eve  | ent goes away;       |  |  |

|               |             | I restarts autom            |             |                     |                  |                 |                      |  |  |

|               | 0 = Upon au | to-shutdown, E0             | CCPASE must | be cleared by s     | software to res  | tart the PWM    |                      |  |  |

|               |             |                             |             |                     |                  |                 |                      |  |  |

| bit 6-0       | PDC<6:0>: F | WM Delay Cou                | nt bits     |                     |                  |                 |                      |  |  |

| bit 6-0       |             | WM Delay Counter of Fcy (Fc |             | between the sc      | heduled time     | when a PWM      | signal <b>should</b> |  |  |

Note 1: This register is implemented only on PIC24FXXKL40X/30X devices.

# REGISTER 17-4: SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

| U-0        | U-0                                                | U-0                                     | U-0                | U-0                    | U-0                  | U-0                  | U-0                  |

|------------|----------------------------------------------------|-----------------------------------------|--------------------|------------------------|----------------------|----------------------|----------------------|

| —          | _                                                  | —                                       |                    | —                      | —                    | —                    | —                    |

| bit 15     |                                                    |                                         |                    |                        |                      |                      | bit 8                |

|            |                                                    |                                         |                    |                        |                      |                      |                      |

| R/W-0      | R/W-0                                              | R/W-0                                   | R/W-0              | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| WCOL       | SSPOV                                              | SSPEN <sup>(1)</sup>                    | CKP                | SSPM3 <sup>(2)</sup>   | SSPM2 <sup>(2)</sup> | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |

| bit 7      |                                                    |                                         |                    |                        |                      |                      | bit 0                |

|            |                                                    |                                         |                    |                        |                      |                      |                      |

| Legend:    |                                                    |                                         |                    |                        |                      |                      |                      |

| R = Read   |                                                    | W = Writable bi                         | t                  | -                      | ented bit, read      |                      |                      |

| -n = Value | e at POR                                           | '1' = Bit is set                        |                    | '0' = Bit is clea      | ared                 | x = Bit is unkn      | own                  |

|            |                                                    |                                         |                    |                        |                      |                      |                      |

| bit 15-8   | -                                                  | ted: Read as '0'                        |                    |                        |                      |                      |                      |

| bit 7      |                                                    | e Collision Detect                      | bit                |                        |                      |                      |                      |

|            | $\frac{\text{In Master Tra}}{1 = A \text{ write}}$ | i <u>nsmit mode:</u><br>to the SSPxBUF  | register wa        | s attempted wh         | ile the $l^2$ C co   | nditions were r      | not valid for a      |

|            |                                                    | sion to be started                      |                    |                        |                      |                      |                      |

|            | 0 = No collis                                      | ion                                     |                    |                        |                      |                      |                      |

|            | In Slave Tran                                      |                                         |                    |                        |                      | .,                   |                      |

|            | 1 = The SSP<br>0 = No collisi                      | xBUF register is w<br>ion               | ritten while it is | s still transmitting   | the previous wo      | rd (must be clea     | red in software)     |

|            |                                                    | ode (Master or SI                       | ave modes):        |                        |                      |                      |                      |

|            | This is a "don                                     |                                         |                    |                        |                      |                      |                      |

| bit 6      | SSPOV: MSS                                         | SPx Receive Over                        | flow Indicator     | bit                    |                      |                      |                      |

|            | In Receive m                                       |                                         |                    |                        |                      |                      |                      |

|            | 1 = A byte is<br>0 = No overf                      | received while the<br>low               | SSPxBUF reg        | ister is still holding | g the previous by    | /te (must be clea    | ired in software)    |

|            | In Transmit m                                      |                                         |                    |                        |                      |                      |                      |

|            |                                                    | n't care" bit in Trar                   | smit mode.         |                        |                      |                      |                      |

| bit 5      | SSPEN: MSS                                         | SPx Enable bit <sup>(1)</sup>           |                    |                        |                      |                      |                      |

|            |                                                    | the serial port and the serial port and |                    |                        |                      | serial port pins     |                      |

| bit 4      |                                                    | Release Control bi                      | -                  | lese pills as i/O      | port pins            |                      |                      |

| DIL 4      | In Slave mod                                       |                                         | ι                  |                        |                      |                      |                      |

|            | 1 = Releases                                       |                                         |                    |                        |                      |                      |                      |

|            | 0 = Holds clo                                      | ck low (clock strei                     | ch); used to e     | ensure data setu       | ıp time              |                      |                      |

|            | In Master mo                                       |                                         |                    |                        |                      |                      |                      |

|            | Unused in thi                                      |                                         | (2)                |                        |                      |                      |                      |

| bit 3-0    |                                                    | MSSPx Mode Se                           |                    |                        |                      |                      |                      |

|            |                                                    | lave mode, 10-bit<br>lave mode, 7-bit a |                    |                        |                      |                      |                      |

|            |                                                    | irmware Controlle                       |                    |                        |                      | labica               |                      |

|            | 1000 = I <sup>2</sup> C N                          | laster mode, Cloc                       | k = Fosc/(2 *      |                        | 1)) <sup>(3)</sup>   |                      |                      |

|            |                                                    | lave mode, 10-bit<br>lave mode, 7-bit a |                    |                        |                      |                      |                      |

|            | $0 \perp 1 = 1 - C S$                              | nave moue, 7-bit a                      | auuress            |                        |                      |                      |                      |

| Note 1:    |                                                    | d, the SDAx and S                       | -                  | -                      | -                    |                      |                      |

| 2:         | Bit combination                                    | ons not specifically                    | y listed here a    | are either reserv      | ed or implemen       | ted in SPI mode      | e only.              |

SSPxADD values of 0, 1 or 2 are not supported when the Baud Rate Generator is used with I<sup>2</sup>C mode.

### REGISTER 19-5: AD1CSSL: A/D INPUT SCAN SELECT REGISTER

| R/W-0            | R/W-0       | R/W-0                              | R/W-0         | R/W-0                   | R/W-0           | R/W-0           |       |

|------------------|-------------|------------------------------------|---------------|-------------------------|-----------------|-----------------|-------|

|                  |             |                                    | CSSL          | <15:8> <sup>(1)</sup>   |                 |                 | R/W-0 |

| bit 15           |             |                                    |               |                         |                 |                 | bit 8 |

|                  |             |                                    |               |                         |                 |                 |       |

| R/W-0            | R/W-0       | U-0                                | R/W-0         | R/W-0                   | R/W-0           | R/W-0           | R/W-0 |

| CSSL<7           | :6>         |                                    |               |                         | CSSL<4:0>(1)    |                 |       |

| bit 7            |             |                                    |               |                         |                 |                 | bit 0 |

|                  |             |                                    |               |                         |                 |                 |       |

| Legend:          |             |                                    |               |                         |                 |                 |       |

| R = Readable bit |             | W = Writable b                     | bit           | U = Unimplem            | ented bit, read | d as '0'        |       |

| -n = Value at PO | R           | '1' = Bit is set                   |               | '0' = Bit is clea       | ared            | x = Bit is unkr | iown  |

|                  |             |                                    |               | (1)                     |                 |                 |       |

|                  |             | A/D Input Pin S                    |               |                         |                 |                 |       |