#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4/M0+                                                       |

| Core Size                  | 32-Bit Dual-Core                                                          |

| Speed                      | 100MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 39                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 12x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

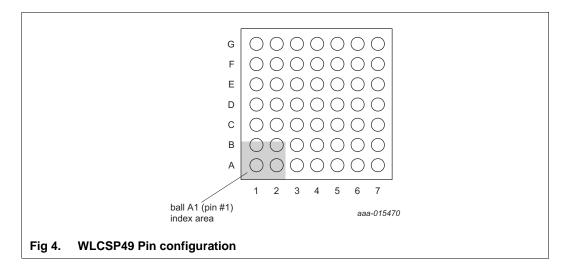

| Package / Case             | 49-UFBGA, WLCSP                                                           |

| Supplier Device Package    | 49-WLCSP (3.44x3.44)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc54114j256uk49z |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

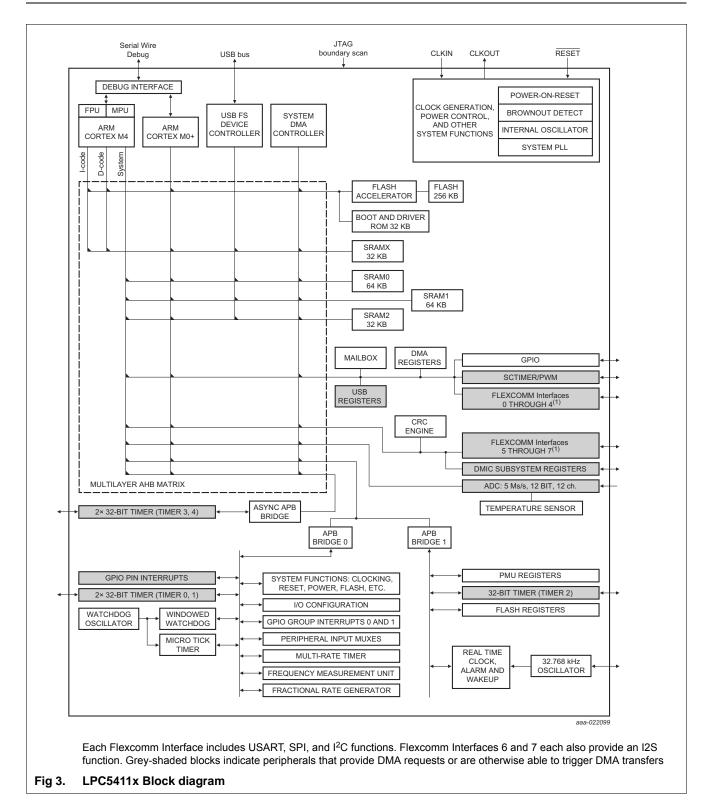

# 5. Block diagram

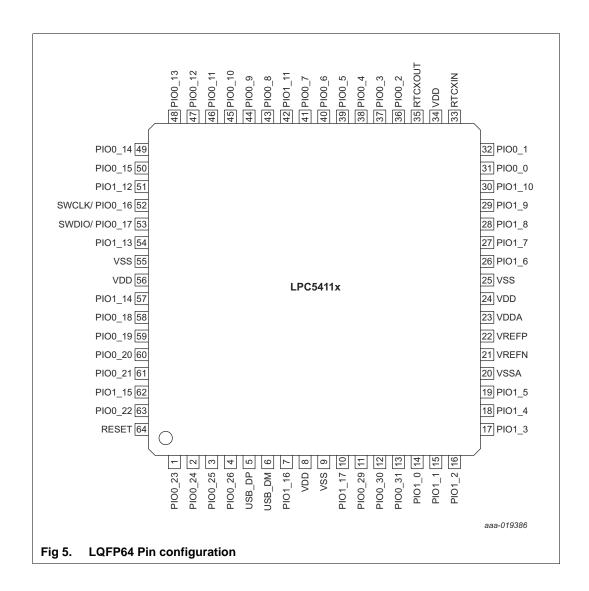

## 6. Pinning information

## 6.1 Pinning

## 6.2 Pin description

On the LPC5411x, digital pins are grouped into two ports. Each digital pin may support up to four different digital functions and one analog function, including General Purpose I/O (GPIO).

| Table 4. |        | scrip  | ,   | •               |      |                                                                                                                                                                                                                          |

|----------|--------|--------|-----|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol   | 49-pin | 64-pin |     | Reset state [1] | Type | Description                                                                                                                                                                                                              |

| PIO0_0   | A6     | 31     | [2] | PU              | I/O  | PIO0_0 — General-purpose digital input/output pin.                                                                                                                                                                       |

|          |        |        |     |                 |      | <b>Remark:</b> In ISP mode, this pin is set to the Flexcomm Interface 0 USART RXD function.                                                                                                                              |

|          |        |        |     |                 | I/O  | FC0_RXD_SDA_MOSI — Flexcomm Interface 0: USART RXD, I2C SDA, SPI MOSI.                                                                                                                                                   |

|          |        |        |     |                 | I/O  | FC3_CTS_SDA_SSEL0 — Flexcomm Interface 3: USART CTS, I2C SDA, SPI SSEL0.                                                                                                                                                 |

|          |        |        |     |                 | I    | CTimer0_CAP0 — 32-bit CTimer0 capture input 0.                                                                                                                                                                           |

|          |        |        |     |                 |      | R — Reserved.                                                                                                                                                                                                            |

|          |        |        |     |                 | 0    | SCT0_OUT3 — SCT0 output 3. PWM output 3.                                                                                                                                                                                 |

| PIO0_1   | B6     | 32     | [2] | PU              | I/O  | PIO0_1 — General-purpose digital input/output pin.                                                                                                                                                                       |

|          |        |        |     |                 |      | <b>Remark:</b> In ISP mode, this pin is set to the Flexcomm Interface 0 USART TXD function.                                                                                                                              |

|          |        |        |     |                 | I/O  | FC0_TXD_SCL_MISO — Flexcomm Interface 0: USART TXD, I2C SCL, SPI MISO.                                                                                                                                                   |

|          |        |        |     |                 | I/O  | FC3_RTS_SCL_SSEL1 — Flexcomm Interface 3: USART RTS, I2C SCL, SPI SSEL1.                                                                                                                                                 |

|          |        |        |     |                 | I    | CTimer0_CAP1 — 32-bit CTimer0 capture input 1.                                                                                                                                                                           |

|          |        |        |     |                 |      | R — Reserved.                                                                                                                                                                                                            |

|          |        |        |     |                 | 0    | SCT0_OUT1 — SCT0 output 1. PWM output 1.                                                                                                                                                                                 |

| PIO0_2   | -      | 36     | [2] | PU              | I/O  | PIO0_2 — General-purpose digital input/output pin.                                                                                                                                                                       |

|          |        |        |     |                 | I/O  | <b>FC0_CTS_SDA_SSEL0</b> — Flexcomm Interface 0: USART CTS, I2C SDA, SPI SSEL0.                                                                                                                                          |

|          |        |        |     |                 | I/O  | FC3_SSEL3 — Flexcomm Interface 3: SPI SSEL3.                                                                                                                                                                             |

|          |        |        |     |                 | I    | CTimer2_CAP1 — 32-bit CTimer2 capture input 1.                                                                                                                                                                           |

| PIO0_3   | -      | 37     | [2] | PU              | I/O  | PIO0_3 — General-purpose digital input/output pin.                                                                                                                                                                       |

|          |        |        |     |                 | I/O  | FC0_RTS_SCL_SSEL1 — Flexcomm Interface 0: USART RTS, I2C SCL, SPI SSEL1.                                                                                                                                                 |

|          |        |        |     |                 | I/O  | FC2_SSEL2 — Flexcomm Interface 2: SPI SSEL2.                                                                                                                                                                             |

|          |        |        |     |                 | 0    | CTimer1_MAT3 — 32-bit CTimer1 match output 3.                                                                                                                                                                            |

| PIO0_4   | C7     | 38     | [2] | PU              | I/O  | PIO0_4 — General-purpose digital input/output pin.                                                                                                                                                                       |

|          |        |        |     |                 |      | <b>Remark:</b> The state of this pin at Reset in conjunction with PIO0_31 and PIO1_6 will determine the boot source for the part or if ISP handler is invoked. See the Boot Process chapter in UM10914 for more details. |

|          |        |        |     |                 | I/O  | FC0_SCK — Flexcomm Interface 0: USART or SPI clock.                                                                                                                                                                      |

|          |        |        |     |                 | I/O  | FC3_SSEL2 — Flexcomm Interface 3: SPI SSEL2.                                                                                                                                                                             |

|          |        |        |     |                 | I    | CTimer0_CAP2 — 32-bit CTimer0 capture input 2.                                                                                                                                                                           |

#### **Pin description** Table 4.

Product data sheet

| Table 4.           |         |                |            |                 |            |                                                                                                                                                                                                                    |

|--------------------|---------|----------------|------------|-----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol             | 49-pin  | 64-pin         |            | Reset state [1] | Type       | Description                                                                                                                                                                                                        |

| PIO0_29/           | •<br>D3 | <b>0</b><br>11 | [4]        | PU              | I/O;       | <b>PIO0_29/ADC0_0</b> — General-purpose digital input/output pin. ADC input channel 0 if the DICIMODE bit is get to 0 in the IOCON register for this pin                                                           |

| ADC0_0             |         |                |            |                 | AI         | if the DIGIMODE bit is set to 0 in the IOCON register for this pin.                                                                                                                                                |

|                    |         |                |            |                 | I/O        | FC1_RXD_SDA_MOSI — Flexcomm Interface 1: USART RXD, I2C SDA, SPI MOSI.                                                                                                                                             |

|                    |         |                |            |                 | 0          | SCT0_OUT2 — SCT0 output 2. PWM output 2.                                                                                                                                                                           |

|                    |         |                |            |                 | 0          | CTimer0_MAT3 — 32-bit CTimer0 match output 3.                                                                                                                                                                      |

|                    |         |                |            |                 |            | R — Reserved.                                                                                                                                                                                                      |

|                    |         |                |            |                 | I          | CTimer0_CAP1 — 32-bit CTimer0 capture input 1.                                                                                                                                                                     |

|                    |         |                |            |                 |            | R — Reserved.                                                                                                                                                                                                      |

|                    |         |                |            |                 | 0          | CTimer0_MAT1 — 32-bit CTimer0 match output 1.                                                                                                                                                                      |

| PIO0_30/<br>ADC0_1 | C1      | 12             | <u>[4]</u> | PU              | I/O;<br>AI | <b>PIO0_30/ADC0_1</b> — General-purpose digital input/output pin. ADC input channel 1 if the DIGIMODE bit is set to 0 in the IOCON register for this pin.                                                          |

|                    |         |                |            |                 | I/O        | FC1_TXD_SCL_MISO — Flexcomm Interface 1: USART TXD, I2C SCL, SPI MISO.                                                                                                                                             |

|                    |         |                |            |                 | 0          | SCT0_OUT3 — SCT0 output 3. PWM output 3.                                                                                                                                                                           |

|                    |         |                |            |                 | 0          | CTimer0_MAT2 — 32-bit CTimer0 match output 2.                                                                                                                                                                      |

|                    |         |                |            |                 |            | R — Reserved.                                                                                                                                                                                                      |

|                    |         |                |            |                 | I          | CTimer0_CAP2 — 32-bit CTimer0 capture input 2.                                                                                                                                                                     |

| PIO0_31/<br>ADC0_2 | C2      | 13             | <u>[4]</u> | PU              | I/O;<br>AI | <b>PIO0_31/ADC0_2</b> — General-purpose digital input/output pin. ADC input channel 2 if the DIGIMODE bit is set to 0 in the IOCON register for this pin.                                                          |

|                    |         |                |            |                 |            | <b>Remark:</b> This pin is also used to invoke ISP mode after device reset. Secondary selection of boot source for ISP mode also uses PIO0_4 and PIO1_6. See the Boot Process chapter in UM10914 for more details. |

|                    |         |                |            |                 | 0          | PDM0_CLK — Clock for PDM interface 0, for digital microphone.                                                                                                                                                      |

|                    |         |                |            |                 | I/O        | FC2_CTS_SDA_SSEL0 — Flexcomm Interface 2: USART CTS, I2C SDA, SPI SSEL0.                                                                                                                                           |

|                    |         |                |            |                 | I          | CTimer2_CAP2 — 32-bit CTimer2 capture input 2.                                                                                                                                                                     |

|                    |         |                |            |                 |            | R — Reserved.                                                                                                                                                                                                      |

|                    |         |                |            |                 | I          | CTimer0_CAP3 — 32-bit CTimer0 capture input 3.                                                                                                                                                                     |

|                    |         |                |            |                 | 0          | CTimer0_MAT3 — 32-bit CTimer0 match output 3.                                                                                                                                                                      |

| PIO1_0/<br>ADC0_3  | C3      | 14             | <u>[4]</u> | PU              | I/O;<br>Al | <b>PIO1_0/ADC0_3</b> — General-purpose digital input/output pin. ADC input channel 3 if the DIGIMODE bit is set to 0 in the IOCON register for this pin.                                                           |

|                    |         |                |            |                 | I          | PDM0_DATA — Data for PDM interface 0, digital microphone input.                                                                                                                                                    |

|                    |         |                |            |                 | I/O        | FC2_RTS_SCL_SSEL1 — Flexcomm Interface 2: USART RTS, I2C SCL, SPI SSEL1.                                                                                                                                           |

|                    |         |                |            |                 | 0          | CTimer3_MAT1 — 32-bit CTimer3 match output 1.                                                                                                                                                                      |

|                    |         |                |            |                 |            | R — Reserved.                                                                                                                                                                                                      |

|                    |         |                |            |                 | I          | CTimer0_CAP0 — 32-bit CTimer0 capture input 0.                                                                                                                                                                     |

| L                  |         | I              | 1          | I               | 1          | =                                                                                                                                                                                                                  |

#### Table 4. Pin description ...continued

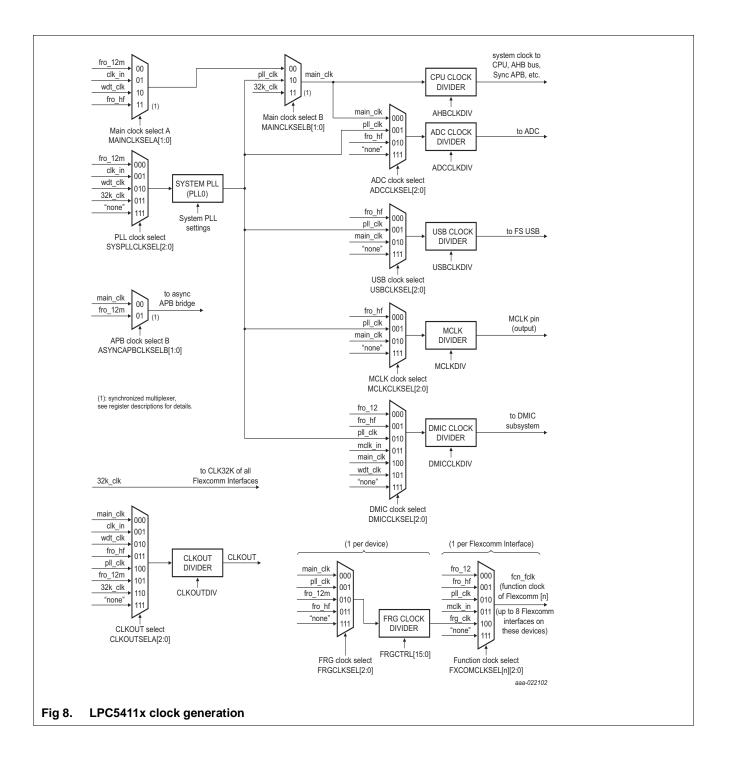

Table 9 describes signals on the clocking diagram.

| Name     | Description                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32k_clk  | The 32 kHz output of the RTC oscillator. The 32 kHz clock must be enabled in the RTCOSCCTRL register.                                                   |

| clk_in   | This is the internal clock that comes from the main CLK_IN pin function. That function must be connected to the pin by selecting it in the IOCON block. |

| frg_clk  | The output of the Fractional Rate Generator.                                                                                                            |

| fro_12m  | The 12 MHz output of the currently selected on-chip FRO oscillator.                                                                                     |

| fro_hf   | The currently selected FRO high speed output. This may be either 96 MHz or 48 MHz.                                                                      |

| main_clk | The main clock used by the CPU and AHB bus, and potentially many others.                                                                                |

| mclk_in  | The MCLK input function, when it is connected to a pin by selecting it in the IOCON block.                                                              |

| pll_clk  | The output of the PLL.                                                                                                                                  |

| wdt_clk  | The output of the watchdog oscillator, which has a selectable target frequency. It must also be enabled in the PDRINCFG0 register.                      |

| "none"   | A tied-off source that should be selected to save power when the output of the related multiplexer is not used.                                         |

Table 7. Clocking diagram signal name descriptions

#### 7.13.3 Brownout detection

The LPC5411x includes a monitor for the voltage level on the  $V_{DD}$  pin. If this voltage falls below a fixed level, the BOD sets a flag that can be polled or cause an interrupt. In addition, a separate threshold levels can be selected to cause chip reset and interrupt.

#### 7.13.4 Safety

The LPC5411x includes a Windowed WatchDog Timer (WWDT), which can be enabled by software after reset. Once enabled, the WWDT remains locked and cannot be modified in any way until a reset occurs.

## 7.14 Code security (Code Read Protection - CRP)

This feature of the LPC5411x allows user to enable different levels of security in the system so that access to the on-chip flash and use of the Serial Wire Debugger (SWD) and In-System Programming (ISP) can be restricted. When needed, CRP is invoked by programming a specific pattern into a dedicated flash location. IAP commands are not affected by the CRP.

In addition, ISP entry can be invoked by pulling a pin on the LPC5411x LOW on reset. This pin is called the ISP entry pin.

There are three levels of Code Read Protection:

- 1. CRP1 disables access to the chip via the SWD and allows partial flash update (excluding flash sector 0) using a limited set of the ISP commands. This mode is useful when CRP is required and flash field updates are needed but all sectors cannot be erased.

- 2. CRP2 disables access to the chip via the SWD and only allows full flash erase and update using a reduced set of the ISP commands.

- CRP3 fully disables any access to the chip via SWD and ISP. It is up to the user's application to provide (if needed) flash update mechanism using IAP calls or a call to reinvoke ISP command to enable a flash update via USART.

| Power mode | Wake-up source                             | Conditions                                                                                                      |  |  |  |  |  |  |

|------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Deep-sleep | Pin interrupts                             | Enable pin interrupts in NVIC and STARTER0 and/or STARTER1 registers.                                           |  |  |  |  |  |  |

|            | BOD interrupt                              | Enable interrupt in NVIC and STARTER0 registers.                                                                |  |  |  |  |  |  |

|            |                                            | Enable interrupt in BODCTRL register.                                                                           |  |  |  |  |  |  |

|            |                                            | <ul> <li>Configure the BOD to keep running in this mode with the power API.</li> </ul>                          |  |  |  |  |  |  |

|            | BOD reset                                  | Enable reset in BODCTRL register.                                                                               |  |  |  |  |  |  |

|            | Watchdog interrupt                         | Enable the watchdog oscillator in the PDRUNCFG0 register.                                                       |  |  |  |  |  |  |

|            |                                            | <ul> <li>Enable the watchdog interrupt in NVIC and STARTER0 registers.</li> </ul>                               |  |  |  |  |  |  |

|            |                                            | <ul> <li>Enable the watchdog in the WWDT MOD register and feed.</li> </ul>                                      |  |  |  |  |  |  |

|            |                                            | <ul> <li>Enable interrupt in WWDT MOD register.</li> </ul>                                                      |  |  |  |  |  |  |

|            |                                            | <ul> <li>Configure the WDTOSC to keep running in this mode with the power API.</li> </ul>                       |  |  |  |  |  |  |

|            | Watchdog reset                             | <ul> <li>Enable the watchdog oscillator in the PDRUNCFG0 register.</li> </ul>                                   |  |  |  |  |  |  |

|            |                                            | • Enable the watchdog and watchdog reset in the WWDT MOD register and feed.                                     |  |  |  |  |  |  |

|            | Reset pin                                  | Always available.                                                                                               |  |  |  |  |  |  |

|            | RTC 1 Hz alarm timer                       | <ul> <li>Enable the RTC 1 Hz oscillator in the RTCOSCCTRL register.</li> </ul>                                  |  |  |  |  |  |  |

|            |                                            | <ul> <li>Enable the RTC bus clock in the AHBCLKCTRL0 register.</li> </ul>                                       |  |  |  |  |  |  |

|            |                                            | • Start RTC alarm timer by writing a time-out value to the RTC COUNT register.                                  |  |  |  |  |  |  |

|            |                                            | <ul> <li>Enable the RTCALARM interrupt in the STARTER0 register.</li> </ul>                                     |  |  |  |  |  |  |

|            | RTC 1 kHz timer time-out and alarm         | • Enable the RTC 1 Hz oscillator and the RTC 1 kHz oscillator in the RTC CTRL register.                         |  |  |  |  |  |  |

|            |                                            | <ul> <li>Start RTC 1 kHz timer by writing a value to the WAKE register of the RTC.</li> </ul>                   |  |  |  |  |  |  |

|            |                                            | <ul> <li>Enable the RTC wake-up interrupt in the STARTER0 register.</li> </ul>                                  |  |  |  |  |  |  |

|            | Micro-tick timer                           | <ul> <li>Enable the watchdog oscillator in the PDRUNCFG0 register.</li> </ul>                                   |  |  |  |  |  |  |

|            | (intended for ultra-low power wake-up from | <ul> <li>Enable the Micro-tick timer clock by writing to the AHBCLKCTRL1 register.</li> </ul>                   |  |  |  |  |  |  |

|            | deep-sleep mode                            | <ul> <li>Start the Micro-tick timer by writing UTICK CTRL register.</li> </ul>                                  |  |  |  |  |  |  |

|            |                                            | Enable the Micro-tick timer interrupt in the STARTER0 register.                                                 |  |  |  |  |  |  |

|            | I <sup>2</sup> C interrupt                 | Interrupt from I <sup>2</sup> C in slave mode.                                                                  |  |  |  |  |  |  |

|            | SPI interrupt                              | Interrupt from SPI in slave mode.                                                                               |  |  |  |  |  |  |

|            | USART interrupt                            | Interrupt from USART in slave or 32 kHz mode.                                                                   |  |  |  |  |  |  |

|            | USB need clock<br>interrupt                | Interrupt from USB when activity is detected that requires a clock.                                             |  |  |  |  |  |  |

|            | DMA interrupt                              | See the LPC5411x User Manual for details of DMA-related interrupts.                                             |  |  |  |  |  |  |

|            | HWWAKE                                     | Certain Flexcomm Interface and DMIC subsystem activity.                                                         |  |  |  |  |  |  |

| Deep       | RTC 1 Hz alarm timer                       | Enable the RTC 1 Hz oscillator in the RTC CTRL register.                                                        |  |  |  |  |  |  |

| power-down |                                            | • Start RTC alarm timer by writing a time-out value to the RTC COUNT register.                                  |  |  |  |  |  |  |

|            | RTC 1 kHz timer<br>time-out and alarm      | <ul> <li>Enable the RTC 1 Hz oscillator and the RTC 1 kHz oscillator in the<br/>RTCOSCCTRL register.</li> </ul> |  |  |  |  |  |  |

|            |                                            | <ul> <li>Enable the RTC bus clock in the AHBCLKCTRL0 register.</li> </ul>                                       |  |  |  |  |  |  |

|            |                                            |                                                                                                                 |  |  |  |  |  |  |

|            |                                            | <ul> <li>Start RTC 1 kHz timer by writing a value to the WAKE register of the RTC.</li> </ul>                   |  |  |  |  |  |  |

## Table 9. Wake-up sources for reduced power modes

## 7.17.1 Features

- Pin interrupts:

- Up to eight pins can be selected from all GPIO pins on ports 0 and 1 as edge-sensitive or level-sensitive interrupt requests. Each request creates a separate interrupt in the NVIC.

- Edge-sensitive interrupt pins can interrupt on rising or falling edges or both.

- Level-sensitive interrupt pins can be HIGH-active or LOW-active.

- Level-sensitive interrupt pins can be HIGH-active or LOW-active.

- Pin interrupts can wake up the device from sleep mode and deep-sleep mode.

- Pattern match engine:

- Up to eight pins can be selected from all digital pins on ports 0 and 1 to contribute to a boolean expression. The boolean expression consists of specified levels and/or transitions on various combinations of these pins.

- Each bit slice minterm (product term) comprising of the specified boolean expression can generate its own, dedicated interrupt request.

- Any occurrence of a pattern match can also be programmed to generate an RXEV notification to the CPU. The RXEV signal can be connected to a pin.

- Pattern match can be used in conjunction with software to create complex state machines based on pin inputs.

- Pattern match engine facilities wake-up only from active and sleep modes.

## 7.18 AHB peripherals

#### 7.18.1 DMA controller

The DMA controller allows peripheral-to memory, memory-to-peripheral, and memory-to-memory transactions. Each DMA stream provides unidirectional DMA transfers for a single source and destination.

#### 7.18.1.1 Features

- 20 channels, 19 of which are connected to peripheral DMA requests. These come from the Flexcomm Interfaces (USART, SPI, I<sup>2</sup>C, and I2S) and digital microphone interfaces.

- DMA operations can be triggered by on-chip or off-chip events.

- Priority is user selectable for each channel (up to eight priority levels).

- Continuous priority arbitration.

- Address cache with four entries.

- Efficient use of data bus.

- Supports single transfers up to 1,024 words.

- · Address increment options allow packing and/or unpacking data.

Every action that the SCTimer/PWM block can perform occurs in direct response to one of these user-defined events without any software overhead. Any event can be enabled to:

- Start, stop, or halt the counter.

- Limit the counter which means to clear the counter in unidirectional mode or change its direction in bi-directional mode.

- Set, clear, or toggle any SCTimer/PWM output.

- Force a capture of the count value into any capture registers.

- Generate an interrupt of DMA request.

#### 7.20.2.1 Features

- The SCTimer/PWM Supports:

- Eight inputs.

- Eight outputs.

- Ten match/capture registers.

- Ten events.

- Ten states.

- Counter/timer features:

- Each SCTimer/PWM is configurable as two 16-bit counters or one 32-bit counter.

- Counters clocked by system clock or selected input.

- Configurable number of match and capture registers. Up to five match and capture registers total.

- Ten events.

- Ten states.

- Upon match and/or an input or output transition create the following events: interrupt; stop, limit, halt the timer or change counting direction; toggle outputs; change the state.

- Counter value can be loaded into capture register triggered by a match or input/output toggle.

## **10.3** Power consumption

Power measurements in active, sleep, and deep-sleep modes were performed under the following conditions:

- Configure all pins as GPIO with pull-up resistor disabled in the IOCON block.

- Configure GPIO pins as outputs using the GPIO DIR register.

- Write 1 to the GPIO CLR register to drive the outputs LOW.

- All peripherals disabled.

| Table 14. | Static characteristics: Power consumption in active mode |

|-----------|----------------------------------------------------------|

|-----------|----------------------------------------------------------|

$T_{amb} = -40$  °C to +105 °C, unless otherwise specified. 1.62 V  $\leq V_{DD} \leq 3.6$  V.

| Symbol          | Parameter           | Conditions                                                |                     | Min | Typ[1] | Max | Unit |

|-----------------|---------------------|-----------------------------------------------------------|---------------------|-----|--------|-----|------|

| ARM Cortex      | k-M0+ in active mod | de; ARM Cortex-M4 in sleep mode                           | 1                   |     |        |     | II   |

| I <sub>DD</sub> | supply current      | CoreMark code executed from<br>SRAMX; flash powered down: |                     |     |        |     |      |

|                 |                     | CCLK = 12 MHz                                             | [2][3][4][6][7]     | -   | 1.1    | -   | mA   |

|                 |                     | CCLK = 48 MHz                                             | [2][3][4][6][7]     | -   | 3.0    | -   | mA   |

|                 |                     | CCLK = 96 MHz                                             | [2][3][4][6]        | -   | 7.1    | -   | mA   |

| I <sub>DD</sub> | supply current      | CoreMark code executed from flash;                        |                     |     |        |     |      |

|                 |                     | CCLK = 12 MHz; 1 system clock flash access time.          | [2][3][4][5][7]     | -   | 1.3    | -   | mA   |

|                 |                     | CCLK = 48 MHz; 3 system clock<br>flash access time.       | [2][3][4][5][7]     | -   | 3.6    | -   | mA   |

|                 |                     | CCLK = 96 MHz; 7 system clock<br>flash access time.       | <u>[2][3][4][5]</u> | -   | 8.0    | -   | mA   |

| ARM Cortex      | c-M4 in active mode | e; ARM Cortex-M0+ in sleep mode                           |                     |     |        | 1   |      |

| I <sub>DD</sub> | supply current      | CoreMark code executed from<br>SRAMX; flash powered down: |                     |     |        |     |      |

|                 |                     | CCLK = 12 MHz                                             | [2][3][4][6][7]     | -   | 1.3    | -   | mA   |

|                 |                     | CCLK = 48 MHz                                             | [2][3][4][6][7]     | -   | 3.9    | -   | mA   |

|                 |                     | CCLK = 96 MHz                                             | [2][3][4][6]        | -   | 9.3    | -   | mA   |

| I <sub>DD</sub> | supply current      | CoreMark code executed from flash;                        |                     |     |        |     |      |

|                 |                     | CCLK = 12 MHz; 1 system clock<br>flash access time.       | [2][3][4][5][7]     | -   | 1.5    | -   | mA   |

|                 |                     | CCLK = 48 MHz; 3 system clock flash access time.          | [2][3][4][5][7]     | -   | 4.6    | -   | mA   |

|                 |                     | CCLK = 96 MHz; 7 system clock flash access time.          | <u>[2][3][4][5]</u> | -   | 9.9    | -   | mA   |

[1] Typical ratings are not guaranteed. Typical values listed are at room temperature (25 °C), 3.3V.

[2] Clock source FRO. PLL disabled.

[3] Characterized through bench measurements using typical samples.

- [4] Compiler settings: Keil µVision 5.17., optimization level 0, optimized for time off.

- [5] Prefetch disabled in FLASHCFG register. SRAM0 powered. SRAM1, SRAM2, and SRAMX powered down. All peripheral clocks disabled.

[6] Flash is powered down; SRAM0 and SRAMX are powered; SRAM1 and SRAM2 are powered down. All peripheral clocks disabled.

[7] Characterized using low power regulation mode.

# LPC5411x

#### 32-bit ARM Cortex-M4/M0+ microcontroller

## **11. Dynamic characteristics**

## 11.1 Flash memory

#### Table 21. Flash characteristics

$T_{amb}$  = -40 °C to +105 °C, unless otherwise specified. 1.62 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V unless otherwise specified.

| Symbol            | Parameter           | Conditions                                    |     | Min   | Typ <u>[1]</u> | Max | Unit   |

|-------------------|---------------------|-----------------------------------------------|-----|-------|----------------|-----|--------|

| N <sub>endu</sub> | endurance           | sector erase/program                          | [2] | 10000 | -              | -   | cycles |

|                   |                     | page erase/program; page in a sector          |     | 1000  | -              | -   | cycles |

| t <sub>ret</sub>  | retention time      | powered                                       |     | 10    | -              | -   | years  |

|                   |                     | unpowered                                     |     | 10    | -              | -   | years  |

| t <sub>er</sub>   | erase time          | page, sector, or multiple consecutive sectors |     | -     | 100            | -   | ms     |

| t <sub>prog</sub> | programming<br>time |                                               | [3] | -     | 1              | -   | ms     |

[1] Typical ratings are not guaranteed.

[2] Number of erase/program cycles.

[3] Programming times are given for writing 256 bytes from RAM to the flash.

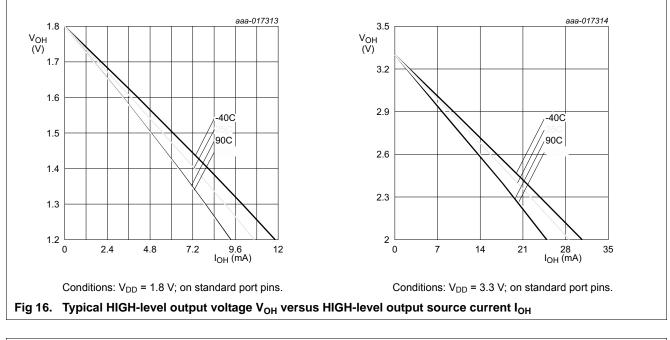

## 11.2 I/O pins

#### Table 22. Dynamic characteristic: I/O pins<sup>[1]</sup>

$T_{amb}$  = -40 °C to +85 °C unless otherwise specified; 1.62 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V unless otherwise specified.

| Symbol         | Parameter      | Conditions                                                   |        | Min | Тур | Max | Unit |

|----------------|----------------|--------------------------------------------------------------|--------|-----|-----|-----|------|

| Standard       | l I/O pins - n | ormal drive strength                                         | 1      | 1   |     |     | -1   |

| t <sub>r</sub> | rise time      | pin configured as output; SLEW = 1 (fast mode);              | [2][3] |     |     |     |      |

|                |                | $2.7~V \leq V_{DD} \leq 3.6~V$                               |        | 1.0 | -   | 2.5 | ns   |

|                |                | $1.62 \text{ V} \le \text{V}_{DD} \le 1.98 \text{ V}$        |        | 1.6 | -   | 3.8 | ns   |

| t <sub>f</sub> | fall time      | pin configured as output; SLEW = 1 (fast mode);              | [2][3] |     |     |     |      |

|                |                | $2.7~V \leq V_{DD} \leq 3.6~V$                               |        | 0.9 | -   | 2.5 | ns   |

|                |                | $1.62 \text{ V} \leq V_{DD} \leq 1.98 \text{ V}$             |        | 1.7 | -   | 4.1 | ns   |

| t <sub>r</sub> | rise time      | pin configured as output; SLEW = 0<br>(standard mode);       | [2][3] |     |     |     |      |

|                |                | $2.7~V \leq V_{DD} \leq 3.6~V$                               |        | 1.9 | -   | 4.3 | ns   |

|                |                | $1.62 \text{ V} \le \text{V}_{\text{DD}} \le 1.98 \text{ V}$ |        | 2.9 | -   | 7.8 | ns   |

| t <sub>f</sub> | fall time      | pin configured as output; SLEW = 0<br>(standard mode);       | [2][3] |     |     |     |      |

|                |                | $2.7~V \leq V_{DD} \leq 3.6~V$                               |        | 1.9 | -   | 4.0 | ns   |

|                |                | $1.62~V \leq V_{DD} \leq 1.98~V$                             |        | 2.7 | -   | 6.7 | ns   |

| t <sub>r</sub> | rise time      | pin configured as input                                      | [4]    | 0.3 | -   | 1.3 | ns   |

| t <sub>f</sub> | fall time      | pin configured as input                                      | [4]    | 0.2 | -   | 1.2 | ns   |

[1] Simulated data.

- [2] Clock Divider register (DIV) = 0x0.

- [3] Typical ratings are not guaranteed.

- [4] The Flexcomm Interface function clock frequency should not be above 48 MHz. See the data rates section in the I<sup>2</sup>S chapter (UM10912) to calculate clock and sample rates.

- [5] Based on simulation. Not tested in production.

LPC5411x

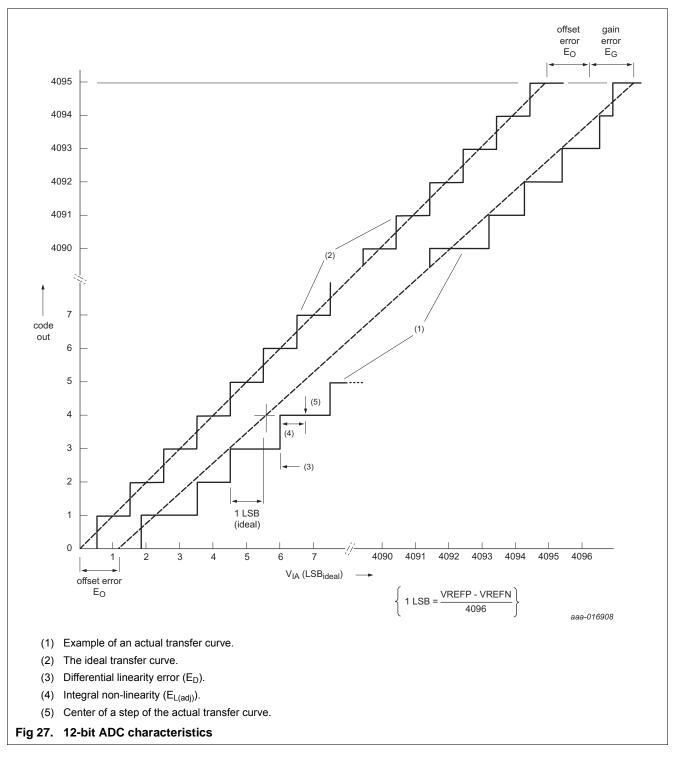

- [8] The full-scale error voltage or gain error (E<sub>G</sub>) is the difference between the straight-line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See Figure 27.

- [9]  $T_{amb} = 25 \text{ °C}$ ; maximum sampling frequency  $f_s = 5.0$  Msamples/s and analog input capacitance  $C_{ia} = 5 \text{ pF}$ .

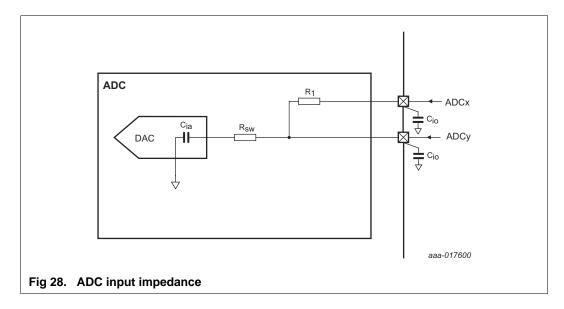

- [10] Input impedance  $Z_i$  is inversely proportional to the sampling frequency and the total input capacity including  $C_{ia}$  and  $C_{io}$ :  $Z_i \propto 1 / (f_s \times C_i)$ . See <u>Table 20</u> for  $C_{io}$ . See <u>Figure 28</u>.

Product data sheet

© NXP Semiconductors N.V. 2018. All rights reserved.

## 12.3 Temperature sensor

## Table 39. Temperature sensor static and dynamic characteristics

| $V_{DD} = V_{DDA} = 1$ | 1.62 V to 3.6 V |

|------------------------|-----------------|

|------------------------|-----------------|

| Symbol             | Parameter                         | Conditions                                |     | Min | Тур | Max | Unit |

|--------------------|-----------------------------------|-------------------------------------------|-----|-----|-----|-----|------|

| DT <sub>sen</sub>  | sensor<br>temperature<br>accuracy | T <sub>amb</sub> = -40 °C to +105 °C      | [1] | -   | -   | 3   | °C   |

| EL                 | linearity error                   | $T_{amb}$ = -40 °C to +105 °C             |     | -   | -   | 3   | °C   |

| t <sub>s(pu)</sub> | power-up<br>settling time         | to 99% of temperature sensor output value | [2] | -   | 10  | 15  | μS   |

[1] Absolute temperature accuracy.

[2] Based on simulation.

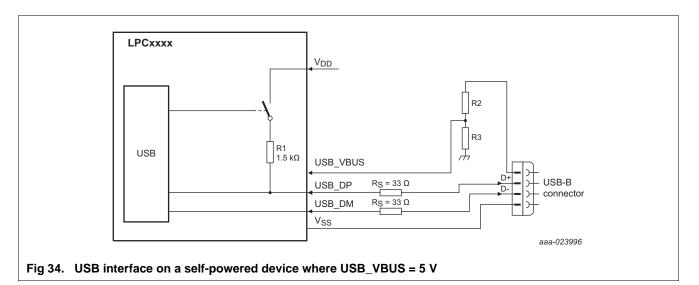

The internal pull-up (1.5 k $\Omega$ ) can be enabled by setting the DCON bit in the DEVCMDSTAT register to prevent the USB from timing out when there is a significant delay between power-up and handling USB traffic. External circuitry is not required.

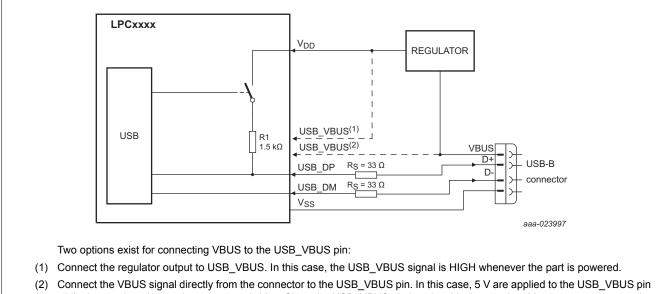

while the regulator is ramping up to supply  $V_{DD}$ . Since the USB\_VBUS pin is only 5 V tolerant when  $V_{DD}$  is at operating level, this connection can degrade the performance of the part over its lifetime. Simulation shows that lifetime is reduced to 15 years at  $T_{amb}$  = 45 °C and 8 years at  $T_{amb}$  = 55 °C assuming that USB\_VBUS = 5 V is applied continuously while  $V_{DD}$  = 0 V.

## Fig 35. USB interface on a bus-powered device

LPC5411x

# 18. Revision history

## Table 43.Revision history

| Document ID    | Release date                                                                                                                                                                                                                                                                                                                                                | Data sheet status                                                                                                                                                                                                                                                                                                  | Change notice     | Supersedes             |  |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------|--|--|--|--|

| LPC5411x v.2.1 | 20180509                                                                                                                                                                                                                                                                                                                                                    | Product data sheet                                                                                                                                                                                                                                                                                                 | -                 | LPC5411x v.2.0         |  |  |  |  |

| Modifications: | controller                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>Updated <u>Section 2 "Features and benefits"</u>: text for serial interfaces: USB 2.0 full-speed device<br/>controller with on-chip PHY and dedicated DMA controller supporting crystal-less operation in<br/>device mode using software library. See Technical note TN00031 for more details.</li> </ul> |                   |                        |  |  |  |  |

| LPC5411x v.2.0 | 20180420                                                                                                                                                                                                                                                                                                                                                    | Product data sheet                                                                                                                                                                                                                                                                                                 | -                 | LPC5411x v.1.9         |  |  |  |  |

| Modifications: | <ul> <li>Fixed Figu</li> </ul>                                                                                                                                                                                                                                                                                                                              | re 38 "WLCSP49 Soldering footprint".                                                                                                                                                                                                                                                                               |                   |                        |  |  |  |  |

|                | <ul> <li>Added Fig</li> </ul>                                                                                                                                                                                                                                                                                                                               | ure 39 "LQFP64 Soldering footprint".                                                                                                                                                                                                                                                                               |                   |                        |  |  |  |  |

| LPC5411x v.1.9 | 20180126                                                                                                                                                                                                                                                                                                                                                    | Product data sheet                                                                                                                                                                                                                                                                                                 | -                 | LPC5411x v.1.8         |  |  |  |  |

| Modifications: | <ul><li>master mo</li><li>Updated S</li></ul>                                                                                                                                                                                                                                                                                                               | feature in Section 7.19.5 "SPI serial I/O co<br>ode and 15 Mbit/s in slave mode for SPI fu<br>section 11.10 "SPI interfaces": the maximu<br>Was 71 Mbit/s in master mode.                                                                                                                                          | nctions. Was 71 N | /bit/s in master mode. |  |  |  |  |

| LPC5411x v.1.8 | 20171102                                                                                                                                                                                                                                                                                                                                                    | Product data sheet                                                                                                                                                                                                                                                                                                 | -                 | LPC5411x v.1.7         |  |  |  |  |

| Modifications: | Updated b                                                                                                                                                                                                                                                                                                                                                   | roken cross references throughout the do                                                                                                                                                                                                                                                                           | cument.           |                        |  |  |  |  |

| LPC5411x v.1.7 | 20170417                                                                                                                                                                                                                                                                                                                                                    | Product data sheet                                                                                                                                                                                                                                                                                                 | -                 | LPC5411x v.1.6         |  |  |  |  |

| Modifications: | <ul> <li>Updated Table 30 "Dynamic characteristics: I2S-bus interface pins [1][4]"</li> <li>Updated Table 16 "Static characteristics: Power consumption in deep-sleep and deep power-down modes" and Table 17 "Static characteristics: Power consumption in deep-sleep and deep power-down modes": Conditions for I<sub>DD</sub> supply current.</li> </ul> |                                                                                                                                                                                                                                                                                                                    |                   |                        |  |  |  |  |

| LPC5411x v.1.6 | 20161222                                                                                                                                                                                                                                                                                                                                                    | Product data sheet                                                                                                                                                                                                                                                                                                 | -                 | LPC5411x v.1.5         |  |  |  |  |

| 11.2           | I/O pins                                    | 63       |

|----------------|---------------------------------------------|----------|

| 11.3           | Wake-up process                             | 64       |

| 11.4           | System PLL                                  | 65       |

| 11.5           | FRO                                         | 66       |

| 11.6           | RTC oscillator                              | 66       |

| 11.7           | Watchdog oscillator                         | 67       |

| 11.8           | I <sup>2</sup> C-bus                        | 67       |

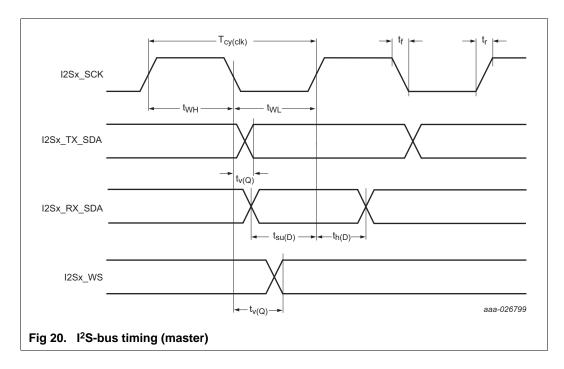

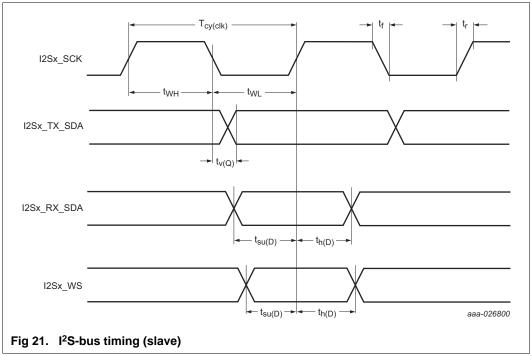

| 11.9           | I <sup>2</sup> S-bus interface              | 68       |

| 11.10          | SPI interfaces                              | 72       |

| 11.11<br>11.12 |                                             | 75<br>76 |

| 11.12          | SCTimer/PWM output timing                   | 70       |

| 11.13          | DMIC subsystemUSB interface characteristics | 77       |

| 12             | Analog characteristics                      | 79       |

| 12.1           | BOD                                         | 79       |

| 12.2           | 12-bit ADC characteristics                  | 80       |

| 12.2.1         | ADC input impedance                         | 83       |

| 12.3           | Temperature sensor                          | 84       |

| 13             | Application information.                    | 86       |

| 13.1           | Start-up behavior                           | 86       |

| 13.2           | Standard I/O pin configuration              | 86       |

| 13.3           | Connecting power, clocks, and debug         |          |

|                | functions                                   | 88       |

| 13.4           | I/O power consumption                       | 89       |

| 13.5           | RTC oscillator                              | 90       |

| 13.5.1         | RTC Printed Circuit Board (PCB) design      |          |

|                | guidelines                                  | 91       |

| 13.6           | Suggested USB interface solutions           | 91       |

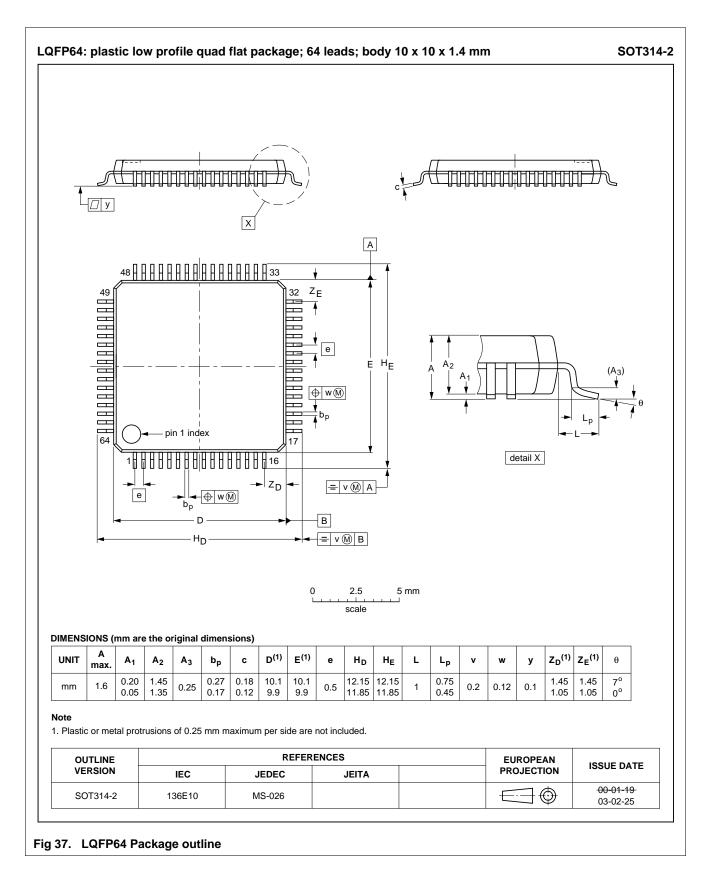

| 14             | Package outline                             | 93       |

| 15             | Soldering                                   | 95       |

| 16             | Abbreviations                               | 97       |

| 17             | References                                  | 97       |

| 18             | Revision history                            | 98       |

| 19             | Legal information                           | 102      |

| 19.1           | Data sheet status                           | 102      |

| 19.2           |                                             | 102      |

| 19.3           |                                             | 102      |

| 19.4           |                                             | 103      |

| 20             |                                             | 103      |

| 21             | Contents                                    | 104      |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP Semiconductors N.V. 2018.

18. All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 9 May 2018 Document identifier: LPC5411x