Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

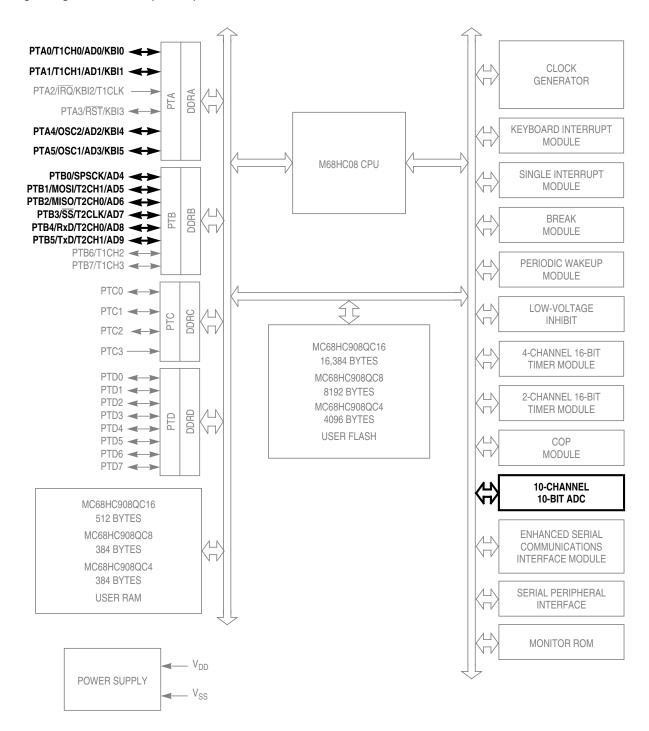

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM                                                         |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 10x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 28-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qc16cdre |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|  |  |  | nts |

|--|--|--|-----|

|  |  |  |     |

|  |  |  |     |

| S.7.1   KBI Input Pins (KBI7:KBI0)   89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8.7          | I/O Signals                           | 80   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------|------|

| 3.8 Registers         88           3.8.1 Keyboard Status and Control Register (KBSCR)         89           3.8.2 Keyboard Interrupt Enable Register (KBIER)         90           3.8.3 Keyboard Interrupt Polarity Register (KBIPR)         91           Chapter 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8.7.1        |                                       |      |

| Reyboard Status and Control Register (KBSCR).   88   3.8.2   Keyboard Interrupt Enable Register (KBIER).   90   3.8.3   Keyboard Interrupt Polarity Register (KBIPR).   91   Chapter 9   Low-Voltage Inhibit (LVI)   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8.8          |                                       |      |

| Chapter 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8.8.1        |                                       |      |

| Chapter 9   Low-Voltage Inhibit (LVI)   93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8.8.2        | g v ,                                 |      |

| Chapter 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8.8.3        |                                       |      |

| Low-Voltage Inhibit (LVI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                                       |      |

| 9.1       Introduction       93         9.2       Features       93         9.3       Functional Description       93         9.3.1       Polled LVI Operation       94         9.3.2       Forced Reset Operation       94         9.3.3       LVI Hysteresis       94         9.4       LVI Interrupts       95         9.5       Low-Power Modes       95         9.5.1       Wait Mode       95         9.5.2       Stop Mode       95         9.6.6       Registers       95         Chapter 10         Oscillator Mode (OSC)         10.1       Introduction       97         10.2       Features       97         10.3       Functional Description       97         10.3.1       Internal Signal Definitions       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       98         10.3.1.4       Internal Oscillator Clock (KTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.2.1       Internal Oscillator Trimming       99         10.3.2.2       Inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |                                       |      |

| 9.2       Features       93         9.3       Functional Description       93         9.3.1       Polled LVI Operation       94         9.3.2       Forced Reset Operation       94         9.3.3       LVI Hysteresis       94         9.3.4       LVI Interrupts       95         9.5       Low-Power Modes       95         9.5.1       Wait Mode       95         9.5.2       Stop Mode       95         9.6       Registers       95         Chapter 10         Oscillator Mode (OSC)         10.1       Introduction       97         10.2       Features       97         10.3       Functional Description       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.2       XTAL Oscillator Clock (KTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.2.1       Internal Oscillator Trimming       99         10.3.2.2       Internal Oscillator Trimming       99         10.3.2.3       External to Internal Clock Switching       100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.4          |                                       | 00   |

| 9.3.1       Functional Description       93         9.3.1.1       Polled LVI Operation       94         9.3.2.2       Forced Reset Operation       94         9.3.3.3       LVI Hysteresis       94         9.3.4       LVI Trip Selection       94         9.4       LVI Interrupts       95         0.5       Low-Power Modes       95         9.5.1       Wait Mode       95         9.5.2       Stop Mode       95         9.6       Registers       95         Chapter 10         Oscillator Mode (OSC)         10.1       Introduction       97         10.2       Features       97         10.3       Functional Description       97         10.3       Internal Signal Definitions       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.2       XTAL Oscillator Clock (INTCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.2.1       Internal Oscillator Timming       99         10.3.2.2       Internal Oscillator Timming       99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                       |      |

| 9.3.1       Polled LVI Operation       94         9.3.2       Forced Reset Operation       94         9.3.3       LVI Hysteresis       94         9.4       LVI Interrupts       95         9.5       Low-Power Modes       95         9.5.1       Wait Mode       95         9.6       Registers       95         Chapter 10         Oscillator Mode (OSC)         Introduction       97         10.2       Features       97         10.3       Functional Description       97         10.3.1       Internal Signal Definitions       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.2       XTAL Oscillator Clock (KTALCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2.1       Internal Oscillator       99         10.3.2.2       Internal Oscillator Trimming       99         10.3.2.3       External to Internal Clock Switching       100         10.3.3       External Oscillator       100<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _            |                                       |      |

| 9.3.2       Forced Reset Operation       94         9.3.3       LVI Hysteresis       94         9.3.4       LVI Interrupts       95         9.5       Low-Power Modes       95         9.5.1       Wait Mode       95         9.5.2       Stop Mode       95         9.6       Registers       95         Chapter 10         Oscillator Mode (OSC)         10.1       Introduction       97         10.2       Features       97         10.3.1       Internal Signal Definitions       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.3       RC Oscillator Clock (RCCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.1.6       Bus Clock Times 4 (BUSCLKX2)       99         10.3.2.1       Internal Oscillator       99         10.3.2.2       Internal to Internal Clock Switching       100         10.3.3.0       External to Internal Clock Switching       100         10.3.4       XTAL Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              | ·                                     |      |

| 9.3.3       LVI Hysteresis       94         9.3.4       LVI Interrupts       95         9.5       Low-Power Modes       95         9.5.1       Wait Mode       95         9.5.2       Stop Mode       95         9.6       Registers       95         Chapter 10         Oscillator Mode (OSC)         10.1       Introduction       97         10.2       Features       97         10.3.1       Internal Signal Definitions       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.3       RC Oscillator Clock (RCCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.1.6       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2.1       Internal Oscillator       99         10.3.2.2       Internal to External Clock Switching       100         10.3.3       External to Internal Clock Switching       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              | ·                                     |      |

| 9.3.4       LVI Trip Selection.       94         9.4       LVI Interrupts.       95         9.5       Low-Power Modes.       95         9.5.1       Wait Mode.       95         9.5.2       Stop Mode.       95         9.6       Registers.       95         Chapter 10         Oscillator Mode (OSC)         10.1       Introduction.       97         10.2       Features.       97         10.3       Functional Description.       97         10.3.1       Internal Signal Definitions.       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN).       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK).       99         10.3.1.3       RC Oscillator Clock (RCCLK).       99         10.3.1.4       Internal Oscillator Clock (INTCLK).       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4).       99         10.3.2.1       Internal Oscillator.       99         10.3.2.2       Internal Oscillator Trimming.       99         10.3.2.2.       Internal Oscillator Trimming.       99         10.3.2.3       External to Internal Clock Switching.       100         10.3.4       XTAL Oscillat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              | ·                                     |      |

| 9.4       LVI Interrupts       95         9.5       Low-Power Modes       95         9.5.1       Wait Mode       95         9.6       Registers       95         Chapter 10         Oscillator Mode (OSC)         10.1       Introduction       97         10.2       Features       97         10.3       Functional Description       97         10.3.1       Internal Signal Definitions       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.3       RC Oscillator Clock (RCCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.1.6       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2.2       Internal Oscillator       99         10.3.2.2       Internal oscillator Trimming       99         10.3.2.2       Internal to External Clock Switching       100         10.3.2.3       External to Internal Clock Switching       100         10.3.3       External Oscillator       100         10.3.5 <td< td=""><td></td><td>· · · · · · · · · · · · · · · · · · ·</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              | · · · · · · · · · · · · · · · · · · · |      |

| 9.5       Low-Power Modes       95         9.5.1       Wait Mode       95         9.6       Registers       95         Chapter 10         Oscillator Mode (OSC)         10.1       Introduction       97         10.2       Features       97         10.3.1       Functional Description       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.1       Oscillator Clock (XTALCLK)       99         10.3.1.2       XTAL Oscillator Clock (RCCLK)       99         10.3.1.3       RC Oscillator Clock (RCCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.1.6       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2.1       Internal Oscillator       99         10.3.2.2       Internal Oscillator Trimming       99         10.3.2.3       External to Internal Clock Switching       100         10.3.3.       External Oscillator       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                       |      |

| 9.5.1       Wait Mode       95         9.5.2       Stop Mode       95         9.6       Registers       95         Chapter 10         Oscillator Mode (OSC)         10.1       Introduction       97         10.2       Features       97         10.3       Functional Description       97         10.3.1       Internal Signal Definitions       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.3       RC Oscillator Clock (RCCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.2.1       Internal Oscillator       99         10.3.2.2       Internal Oscillator Trimming       99         10.3.2.3       External to Internal Clock Switching       100         10.3.2.3       External Oscillator       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                                       |      |

| Stop Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                                       |      |

| Chapter 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |                                       |      |

| Chapter 10           Oscillator Mode (OSC)           10.1 Introduction         97           10.2 Features         97           10.3 Functional Description         97           10.3.1 Internal Signal Definitions         97           10.3.1.1 Oscillator Enable Signal (SIMOSCEN)         97           10.3.1.2 XTAL Oscillator Clock (XTALCLK)         99           10.3.1.3 RC Oscillator Clock (RCCLK)         99           10.3.1.4 Internal Oscillator Clock (INTCLK)         99           10.3.1.5 Bus Clock Times 4 (BUSCLKX4)         99           10.3.1.6 Bus Clock Times 2 (BUSCLKX2)         99           10.3.2 Internal Oscillator         99           10.3.2.1 Internal Oscillator Trimming         99           10.3.2.2 Internal to External Clock Switching         100           10.3.3 External to Internal Clock Switching         100           10.3.4 XTAL Oscillator         100           10.3.5 RC Oscillator         101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | ·                                     |      |

| Oscillator Mode (OSC)           10.1 Introduction         97           10.2 Features         97           10.3 Functional Description         97           10.3.1 Internal Signal Definitions         97           10.3.1.1 Oscillator Enable Signal (SIMOSCEN)         97           10.3.1.2 XTAL Oscillator Clock (XTALCLK)         99           10.3.1.3 RC Oscillator Clock (RCCLK)         99           10.3.1.4 Internal Oscillator Clock (INTCLK)         99           10.3.1.5 Bus Clock Times 4 (BUSCLKX4)         99           10.3.2 Internal Oscillator         99           10.3.2.1 Internal Oscillator Trimming         99           10.3.2.2 Internal to External Clock Switching         100           10.3.3 External to Internal Clock Switching         100           10.3.3 External Oscillator         100           10.3.4 XTAL Oscillator         100           10.3.5 RC Oscillator         101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.0          | riegisters                            | . 50 |

| 10.1       Introduction       97         10.2       Features       97         10.3       Functional Description       97         10.3.1       Internal Signal Definitions       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.3       RC Oscillator Clock (RCCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.1.6       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2       Internal Oscillator       99         10.3.2.1       Internal Oscillator Trimming       99         10.3.2.2       Internal to External Clock Switching       100         10.3.2.3       External to Internal Clock Switching       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                                       |      |

| 10.2       Features.       97         10.3       Functional Description       97         10.3.1       Internal Signal Definitions       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.3       RC Oscillator Clock (RCCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.1.6       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2       Internal Oscillator       99         10.3.2.1       Internal Oscillator Trimming       99         10.3.2.2       Internal to External Clock Switching       100         10.3.3       External to Internal Clock Switching       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              | Oscillator Mode (OSC)                 |      |

| 10.3       Functional Description       97         10.3.1       Internal Signal Definitions       97         10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.3       RC Oscillator Clock (RCCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.1.6       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2       Internal Oscillator       99         10.3.2.1       Internal Oscillator Trimming       99         10.3.2.2       Internal to External Clock Switching       100         10.3.2.3       External to Internal Clock Switching       100         10.3.3       External Oscillator       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10.1         |                                       |      |

| 10.3.1         Internal Signal Definitions         97           10.3.1.1         Oscillator Enable Signal (SIMOSCEN)         97           10.3.1.2         XTAL Oscillator Clock (XTALCLK)         99           10.3.1.3         RC Oscillator Clock (RCCLK)         99           10.3.1.4         Internal Oscillator Clock (INTCLK)         99           10.3.1.5         Bus Clock Times 4 (BUSCLKX4)         99           10.3.1.6         Bus Clock Times 2 (BUSCLKX2)         99           10.3.2         Internal Oscillator         99           10.3.2.1         Internal Oscillator Trimming         99           10.3.2.2         Internal to External Clock Switching         100           10.3.2.3         External to Internal Clock Switching         100           10.3.3         External Oscillator         100           10.3.4         XTAL Oscillator         100           10.3.5         RC Oscillator         101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10.2         |                                       |      |

| 10.3.1.1       Oscillator Enable Signal (SIMOSCEN)       97         10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.3       RC Oscillator Clock (RCCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.2.1       Internal Oscillator       99         10.3.2.1       Internal Oscillator Trimming       99         10.3.2.2       Internal to External Clock Switching       100         10.3.2.3       External to Internal Clock Switching       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | ·                                     |      |

| 10.3.1.2       XTAL Oscillator Clock (XTALCLK)       99         10.3.1.3       RC Oscillator Clock (RCCLK)       99         10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.1.6       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2.1       Internal Oscillator       99         10.3.2.2       Internal Oscillator Trimming       99         10.3.2.2       Internal to External Clock Switching       100         10.3.2.3       External to Internal Clock Switching       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              | · · · · · · · · · · · · · · · · · · · |      |

| 10.3.1.3       RC Oscillator Clock (RCCLK).       99         10.3.1.4       Internal Oscillator Clock (INTCLK).       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4).       99         10.3.1.6       Bus Clock Times 2 (BUSCLKX2).       99         10.3.2       Internal Oscillator.       99         10.3.2.1       Internal Oscillator Trimming.       99         10.3.2.2       Internal to External Clock Switching.       100         10.3.2.3       External to Internal Clock Switching.       100         10.3.3       External Oscillator.       100         10.3.4       XTAL Oscillator.       100         10.3.5       RC Oscillator.       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | <b>5</b> \                            |      |

| 10.3.1.4       Internal Oscillator Clock (INTCLK)       99         10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.1.6       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2       Internal Oscillator       99         10.3.2.1       Internal Oscillator Trimming       99         10.3.2.2       Internal to External Clock Switching       100         10.3.2.3       External to Internal Clock Switching       100         10.3.3       External Oscillator       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | ,                                     |      |

| 10.3.1.5       Bus Clock Times 4 (BUSCLKX4)       99         10.3.1.6       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2       Internal Oscillator       99         10.3.2.1       Internal Oscillator Trimming       99         10.3.2.2       Internal to External Clock Switching       100         10.3.2.3       External to Internal Clock Switching       100         10.3.3       External Oscillator       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              | \                                     |      |

| 10.3.1.6       Bus Clock Times 2 (BUSCLKX2)       99         10.3.2       Internal Oscillator       99         10.3.2.1       Internal Oscillator Trimming       99         10.3.2.2       Internal to External Clock Switching       100         10.3.2.3       External to Internal Clock Switching       100         10.3.3       External Oscillator       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | \ /                                   |      |

| 10.3.2       Internal Oscillator       99         10.3.2.1       Internal Oscillator Trimming       99         10.3.2.2       Internal to External Clock Switching       100         10.3.2.3       External to Internal Clock Switching       100         10.3.3       External Oscillator       100         10.3.4       XTAL Oscillator       100         10.3.5       RC Oscillator       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              | ,                                     |      |

| 10.3.2.1Internal Oscillator Trimming9910.3.2.2Internal to External Clock Switching10010.3.2.3External to Internal Clock Switching10010.3.3External Oscillator10010.3.4XTAL Oscillator10010.3.5RC Oscillator101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                                       |      |

| 10.3.2.2Internal to External Clock Switching10010.3.2.3External to Internal Clock Switching10010.3.3External Oscillator10010.3.4XTAL Oscillator10010.3.5RC Oscillator101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |                                       |      |

| 10.3.2.3External to Internal Clock Switching10010.3.3External Oscillator10010.3.4XTAL Oscillator10010.3.5RC Oscillator101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              | 9                                     |      |