Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

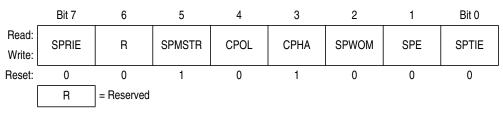

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM                                                         |

| Number of I/O              | 12                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 10x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 16-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qc16cdte |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 13.3.2.        | 2 Character Transmission             | 126 |

|----------------|--------------------------------------|-----|

| 13.3.2.        | Break Characters                     | 127 |

| 13.3.2.        | 4 Idle Characters                    | 128 |

| 13.3.2.        | 5 Inversion of Transmitted Output    | 128 |

| 13.3.3         | Receiver                             | 128 |

| 13.3.3.        | 1 Character Length                   | 128 |

| 13.3.3.        | •                                    |     |

| 13.3.3.        | 3 Data Sampling                      | 130 |

| 13.3.3.        | 4 Framing Errors                     | 131 |

| 13.3.3.        |                                      |     |

| 13.3.3.        | Receiver Wakeup                      | 133 |

| 13.4           | Interrupts                           |     |

| 13.4.1         | Transmitter Interrupts               |     |

| 13.4.2         | Receiver Interrupts                  | 134 |

| 13.4.3         | Error Interrupts                     | 134 |

| 13.5           | Low-Power Modes                      |     |

| 13.5.1         | Wait Mode                            | 135 |

| 13.5.2         | Stop Mode                            | 135 |

| 13.6           | ESCI During Break Interrupts         | 135 |

| 13.7           | I/O Signals                          | 135 |

| 13.7.1         | ESCI Transmit Data (TxD)             | 135 |

| 13.7.2         | ESCI Receive Data (RxD)              | 136 |

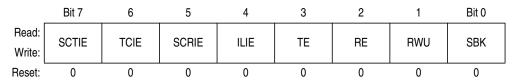

| 13.8           | Registers                            | 136 |

| 13.8.1         | ESCI Control Register 1              | 136 |

| 13.8.2         | ESCI Control Register 2              | 138 |

| 13.8.3         | ESCI Control Register 3              |     |

| 13.8.4         | ESCI Status Register 1               |     |

| 13.8.5         | ESCI Status Register 2               | 143 |

| 13.8.6         | ESCI Data Register                   | 144 |

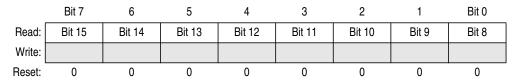

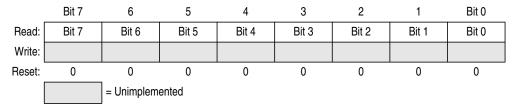

| 13.8.7         | ESCI Baud Rate Register              | 144 |

| 13.8.8         | ESCI Prescaler Register              | 145 |

| 13.9           | ESCI Arbiter                         | 149 |

| 13.9.1         | ESCI Arbiter Control Register        | 149 |

| 13.9.2         | ESCI Arbiter Data Register           |     |

| 13.9.3         | Bit Time Measurement                 | 150 |

| 13.9.4         | Arbitration Mode                     | 151 |

|                |                                      |     |

|                | Chapter 14                           |     |

| 4.4.4          | System Integration Module (SIM)      | 150 |

|                | Introduction                         |     |

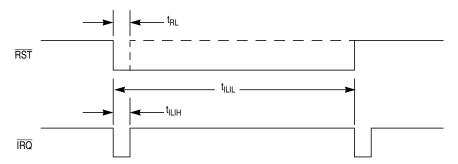

|                | RST and IRQ Pins Initialization      |     |

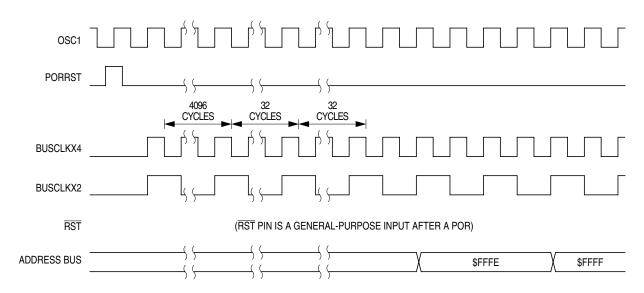

| 14.3           | SIM Bus Clock Control and Generation |     |

| 14.3.1         | Bus Timing                           |     |

| 14.3.2         | Clock Start-Up from POR              |     |

| 14.3.3         | Clocks in Stop Mode and Wait Mode    |     |

| 14.4<br>14.4 1 | Reset and System Initialization      | 155 |

| 1/1/1          | HVIGTORI PIN ROCAT                   | 166 |

MC68HC908QC16 • MC68HC908QC8 • MC68HC908QC4 Data Sheet, Rev. 5

# Memory

| TIMZ Counter Register Low (TZHOTL)   See page 215.   Reset:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Addr.           | Register Name             |         | Bit 7  | 6                         | 5      | 4              | 3              | 2         | 1      | Bit 0     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------|---------|--------|---------------------------|--------|----------------|----------------|-----------|--------|-----------|

| See   Page   P |                 | TIM2 Counter Register Low | Read:   | Bit 7  | Bit 6                     | Bit 5  | Bit 4          | Bit 3          | Bit 2     | Bit 1  | Bit 0     |

| TIM2 Counter Modulo   Register High (T2MODH)   See page 215   Reset:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | \$0242          | (T2CNTL)                  | Write:  |        |                           |        |                |                |           |        |           |

| Social Register High (TZMODH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | See page 214.             | Reset:  | 0      | 0                         | 0      | 0              | 0              | 0         | 0      | 0         |

| See page 215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00040           |                           |         | Bit 15 | Bit 14                    | Bit 13 | Bit 12         | Bit 11         | Bit 10    | Bit 9  | Bit 8     |

| TIM2 Channel O Register Cept (T2SCD)   See page 215.   Feed:   See page 215.   See page 216.   See page 216.   See page 216.   See page 218.   See page 218.   See page 218.   See page 215.   See page 216.   Bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | \$0243          |                           | l l     | 1      | 1                         | 1      | 1              | 1              | 1         | 1      | 1         |

| See page 215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 | TIMO 0                    |         | •      | · ·                       | · ·    | · ·            |                | •         |        |           |

| TIM2 Channel O Status and Control Register (T2CO)   Mrite:   See page 215.   Reset:   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | \$0244          |                           |         | Bit 7  | Bit 6                     | Bit 5  | Bit 4          | Bit 3          | Bit 2     | Bit 1  | Bit 0     |

| S0245   Control Register (T2SC0)   See page 215.   Reset:   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                           | l       | 1      | 1                         | 1      | 1              | 1              | 1         | 1      | 1         |

| South   Control Register (T2SC0)   See page 215.   Reset:   O   O   O   O   O   O   O   O   O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | TIM2 Channel 0 Status and | Read:   | CH0F   |                           |        |                |                |           |        |           |

| TIM2 Channel 0 Register   High (T2CHOH)   See page 218.   Reset:   Indeterminate after reset     Read:   CH1F   See page 218.   Reset:   Indeterminate after reset     Read:   CH1F   See page 218.   Reset:   Indeterminate after reset     Read:   CH1F   See page 218.   Reset:   Indeterminate after reset     Read:   CH1F   See page 218.   Reset:   Indeterminate after reset     Read:   CH1F   CH1IE   O   MS1A   ELS1B   ELS1A   TOV1   CH1MAX   Reset:   Indeterminate after reset     Read:   See page 218.   Reset:   Indeterminate after reset     Read:   Read:   See page 218.   Reset:   Indeterminate after reset     Read:   Read:   See page 218.   Reset:   Indeterminate after reset     Reset:   Reset:   Indeterminate after reset     Reset:   Indeterminate | \$0245          |                           | Write:  | 0      | CH0IE                     | MS0B   | MS0A           | ELS0B          | ELS0A     | TOV0   | CH0MAX    |

| S0246   High (T2CH0H)   See page 218.   Reset:   Indeterminate after reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | See page 215.             | Reset:  | 0      | 0                         | 0      | 0              | 0              | 0         | 0      | 0         |

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 00040           |                           |         | Bit 15 | Bit 14                    | Bit 13 | Bit 12         | Bit 11         | Bit 10    | Bit 9  | Bit 8     |

| Time    | \$0246          |                           | l       |        |                           |        | la data maia a |                |           |        |           |

| S0247                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | . •                       |         |        |                           |        | Indetermina    | te atter reset |           |        |           |

| TIM2 Channel 1 Status and Control Register (T2SC1)   See page 215.   Reset:   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | \$0247          | \$0247 Low (T2CH0L)       |         | Bit 7  | Bit 6                     | Bit 5  | Bit 4          | Bit 3          | Bit 2     | Bit 1  | Bit 0     |

| Control Register (T2SC1)   See page 215.   See page 215.   Reset:   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | See page 218.             | Reset:  |        | Indeterminate after reset |        |                |                |           |        |           |

| Source   Control Register (T2SC1)   See page 215.   Reset:   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | Control Register (T2SC1)  | Read:   | CH1F   | CHIE                      | 0      | MS1A           | FI S1B         | FI S1A    | TOV1   | CH1MAX    |

| TIM2 Channel 1 Register   High (T2CH1H)   See page 218.   Read:   Write:   Bit 15   Bit 14   Bit 13   Bit 12   Bit 11   Bit 10   Bit 9   Bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | \$0248          |                           | l l     | 0      | OTTIL                     |        | WOTA           | LLOID          | LLOTA     | 1011   | OTTIW/ DC |

| Solid   Fragister   Solid   See page 218.   See page 218.   Reset:   Indeterminate after reset   Solid   See page 218.   Reset:   Indeterminate after reset   Solid   See page 218.   Solid   See page 219.   See pa |                 | See page 215.             |         | 0      | 0                         | 0      | 0              | 0              | 0         | 0      | 0         |

| See page 218.   Reset:   Indeterminate after reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | \$0249          |                           |         | Bit 15 | Bit 14                    | Bit 13 | Bit 12         | Bit 11         | Bit 10    | Bit 9  | Bit 8     |

| South   Continue   Preside   South   See page   218.   Reset:   South   See page   219.   See page   219.   Reset:   South   See page   219.   Reset:   So |                 | See page 218.             | Reset:  |        |                           | l      | Indetermina    | te after reset |           |        |           |

| See page 218.   Reset:   Indeterminate after reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | \$በ <b>ን</b> ላለ |                           |         | Bit 7  | Bit 6                     | Bit 5  | Bit 4          | Bit 3          | Bit 2     | Bit 1  | Bit 0     |

| Periodic Wakeup Status and Control Register (PWUSC)   See page 119.   Reset:   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ΨυΖτΛ           |                           | l l     |        |                           |        | Indeterminat   | te after reset |           |        |           |

| Periodic Wakeup Status and Control Register (PWUSC)   See page 119.   Reset:   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | \$024B          | Reserved                  | 1100011 |        |                           |        |                |                |           |        |           |

| \$024C         and Control Register (PWUSC) See page 119.         Write:         PWUON SEL         PWUACK         PWUACK         PWUIE SMODE           \$024D         Periodic Wakeup Prescaler Register (PWUP) See page 120.         Read:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ψ02 1Β          |                           | l       |        |                           |        |                |                |           |        |           |

| \$024C         and Control Register (PWUSC) See page 119.         Write:         PWUON SEL         PWUACK         PWUACK         PWUIE         SMODE           \$024D         Periodic Wakeup Prescaler Register (PWUP) See page 120.         Read:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td></td> <td>Periodic Wakeup Status</td> <td>Read:</td> <td>0</td> <td>0</td> <td></td> <td>DWITCI K</td> <td>PWUF</td> <td>0</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | Periodic Wakeup Status    | Read:   | 0      | 0                         |        | DWITCI K       | PWUF           | 0         |        |           |

| Periodic Wakeup Prescaler   Register (PWUP)   See page 120.   Reset:   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | \$024C          | and Control Register      |         | •      |                           | PWUON  |                |                | -         | PWUIE  | SMODE     |

| \$024D Register (PWUP) See page 120.  Reset: 0 0 0 0 0 0 0 0 0 0  Periodic Wakeup Modulo Register (PWUMOD) See page 121.  Reset: 0 0 0 0 0 0 0 0 0 0  Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0  See page 121.  Reset: 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ψ0210           |                           | l       | 0      | 0                         | 0      | 0              | 0              |           | 0      | 0         |

| \$024D Register (PWUP) Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | Periodic Wakeun Prescaler | Read:   | 0      | 0                         | 0      | 0              | D00            | DOO       | 504    | B00       |

| Periodic Wakeup Modulo   Read:   Bit 7   Bit 6   Bit 5   Bit 4   Bit 3   Bit 2   Bit 1   Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | \$024D          |                           | Write:  |        |                           |        |                | PS3            | PS2       | PS1    | PS0       |

| \$024E Register (PWUMOD) Write: Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0  See page 121. Reset: 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                           | Reset:  | 0      | 0                         | 0      | 0              | 0              | 0         | 0      | 0         |

| See page 121. Reset: 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | \$024E          |                           |         | Bit 7  | Bit 6                     | Bit 5  | Bit 4          | Bit 3          | Bit 2     | Bit 1  | Bit 0     |

| _ Heimplemented D December 11 Heaffacted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                           | Į.      | 0      | 0                         | 0      | 0              | 0              | 0         | 0      | 0         |

| = onlinpiemented   H  = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |                           | [       |        | = Unimplem                | ented  | R              | = Reserved     | U = Unaff | fected |           |

Figure 2-2. Control, Status, and Data Registers (Sheet 6 of 8)

MC68HC908QC16 • MC68HC908QC8 • MC68HC908QC4 Data Sheet, Rev. 5

# 2.6.4 FLASH Program Operation

Programming of the FLASH memory is done on a row basis. A row consists of 32 consecutive bytes starting from addresses \$XX00, \$XX20, \$XX40, \$XX60, \$XX80, \$XXA0, \$XXC0, or \$XXE0. Use the following step-by-step procedure to program a row of FLASH memory

Figure 2-4 shows a flowchart of the programming algorithm.

#### NOTE

Do not program any byte in the FLASH more than once after a successful erase operation. Reprogramming bits to a byte which is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire FLASH memory. Programming without first erasing may disturb data stored in the FLASH.

- 1. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range desired.

- 4. Wait for a time, t<sub>NVS</sub>.

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>PGS</sub>.

- 7. Write data to the FLASH address being programmed<sup>(1)</sup>.

- 8. Wait for time, t<sub>PROG</sub>.

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM bit (1).

- 11. Wait for time, t<sub>NVH</sub>.

- 12. Clear the HVEN bit.

- 13. After time, t<sub>RCV</sub>, the memory can be accessed in read mode again.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed  $t_{PROG}$  maximum, see 19.17 Memory Characteristics.

MC68HC908QC16 • MC68HC908QC8 • MC68HC908QC4 Data Sheet, Rev. 5

<sup>1.</sup> The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

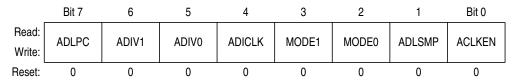

#### Analog-to-Digital Converter (ADC10) Module

clocks are too fast, then the clock must be divided to the appropriate frequency. This divider is specified by ADIV[1:0] and can be divide-by 1, 2, 4, or 8.

# 3.3.2 Input Select and Pin Control

Only one analog input may be used for conversion at any given time. The channel select bits in ADSCR are used to select the input signal for conversion.

## 3.3.3 Conversion Control

Conversions can be performed in either 10-bit mode or 8-bit mode as determined by the MODE bits. Conversions can be initiated by either a software or hardware trigger. In addition, the ADC10 module can be configured for low power operation, long sample time, and continuous conversion.

## 3.3.3.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADSCR (with ADCH bits not all 1s) if software triggered operation is selected.