#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16LX                                                           |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 24MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, UART/USART                                         |

| Peripherals                | DMA, POR, WDT                                                                    |

| Number of I/O              | 82                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | Mask ROM                                                                         |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 6K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 16x8/10b                                                                     |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP                                                                         |

| Supplier Device Package    | 100-LQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90347espmc-gs-309e1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin No.              |                       | l/O<br>Dia nome |                               | Eurotion                                                                                                                                                                                           |  |  |

|----------------------|-----------------------|-----------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QFP100* <sup>1</sup> | LQFP100* <sup>2</sup> | Pin name        | Circuit<br>type <sup>*3</sup> | Function                                                                                                                                                                                           |  |  |

|                      |                       |                 |                               | General purpose I/O pin. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or when the hold function is disabled.           |  |  |

| 9                    | 7                     | HRQ             | G                             | Hold request input pin. This function is enabled when both the external bus and the hold function are enabled.                                                                                     |  |  |

|                      |                       | OUT4            |                               | Waveform output pin for output compare.                                                                                                                                                            |  |  |

|                      |                       | P35             |                               | General purpose I/O pin. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or when the hold function is disabled.           |  |  |

| 10                   | 8                     | HAK             | G                             | Hold acknowledge output pin. This function is enabled when both the external bus and the hold function are enabled.                                                                                |  |  |

|                      |                       | OUT5            |                               | Waveform output pin for output compare.                                                                                                                                                            |  |  |

|                      |                       | P36             | _                             | General purpose I/O pin. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or when the external ready function is disabled. |  |  |

| 11                   | 9                     | RDY             | G                             | External ready input pin. This function is enabled when both the external bus and the external ready function are enabled.                                                                         |  |  |

|                      |                       | OUT6            |                               | Waveform output pin for output compare.                                                                                                                                                            |  |  |

|                      | P37                   |                 |                               | General purpose I/O pin. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or when the clock output is disabled.            |  |  |

| 12                   | 10                    | G               | G                             | Clock output pin. This function is enabled when both the external bus and clock output are enabled.                                                                                                |  |  |

|                      |                       | OUT7            |                               | Waveform output pin for output compare                                                                                                                                                             |  |  |

| 10 14                | 11 12                 | P40, P41        | F                             | General purpose I/O pins.<br>(devices with an S suffix in the part number and or MB90V340E-101)                                                                                                    |  |  |

| 13, 14               | 11, 12                | X0A, X1A        | в                             | Oscillation pins for sub clock<br>(devices without an S suffix in the part number and or MB90V340E-102)                                                                                            |  |  |

| 15                   | 13                    | V <sub>CC</sub> | <b>—</b>                      | Power (3.5 V to 5.5 V) input pin                                                                                                                                                                   |  |  |

| 16                   | 14                    | V <sub>SS</sub> |                               | GND pin                                                                                                                                                                                            |  |  |

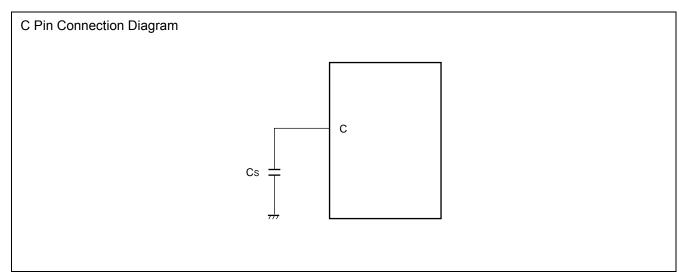

| 17                   | 15                    | С               | к                             | This is the power supply stabilization capacitor This pin should be connected to a ceramic capacitor with a capacitance greater than or equal to 0.1 $\mu$ F.                                      |  |  |

|                      |                       | P42             |                               | General purpose I/O pin.                                                                                                                                                                           |  |  |

|                      |                       | IN6             | ]_                            | Trigger input pin for input capture.                                                                                                                                                               |  |  |

| 18                   | 16                    | RX1             | F                             | RX input pin for CAN1 Interface<br>(MB90341E/342E/F342E/F345E only)                                                                                                                                |  |  |

|                      |                       | INT9R           |                               | External interrupt request input pin                                                                                                                                                               |  |  |

| Pin No.              |                       | I/O                          |                               |                                                                                                                                                                      |  |  |  |

|----------------------|-----------------------|------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| QFP100* <sup>1</sup> | LQFP100* <sup>2</sup> | Pin name                     | Circuit<br>type* <sup>3</sup> | Function                                                                                                                                                             |  |  |  |

| 33                   | 31                    | AVRH                         | L                             | Reference voltage input pin for the A/D Converter. This power supply must be turned on or off while a voltage higher than or equal to AVRH is applied to $AV_{CC}$ . |  |  |  |

| 34                   | 32                    | AVRL                         | К                             | Lower reference voltage input pin for the A/D Converter                                                                                                              |  |  |  |

| 35                   | 33                    | AV <sub>SS</sub>             | К                             | Analog GND pin for the A/D Converter                                                                                                                                 |  |  |  |

|                      |                       | P60 to P67                   |                               | General purpose I/O pins.                                                                                                                                            |  |  |  |

| 36 to 43             | 34 to 41              | AN0 to AN7                   | 1                             | Analog input pins for the A/D converter                                                                                                                              |  |  |  |

|                      |                       | PPG0, 2, 4, 6, 8,<br>A, C, E |                               | Output pins for PPGs                                                                                                                                                 |  |  |  |

| 44                   | 42                    | V <sub>SS</sub>              |                               | GND pin                                                                                                                                                              |  |  |  |

|                      |                       | P70 to P75                   |                               | General purpose I/O pins.                                                                                                                                            |  |  |  |

| 45 to 50             | 43 to 48              | AN16 to AN21                 | 1                             | Analog input pins for the A/D converter (devices with a C suffix in the part number)                                                                                 |  |  |  |

|                      |                       | INT0 to INT5                 |                               | External interrupt request input pins                                                                                                                                |  |  |  |

| 51                   | 49                    | MD2                          | D                             | Input pin for specifying the operating mode.                                                                                                                         |  |  |  |

| 52, 53               | 50, 51                | MD1, MD0                     | С                             | Input pins for specifying the operating mode.                                                                                                                        |  |  |  |

| 54                   | 52                    | RST                          | E                             | Reset input pin                                                                                                                                                      |  |  |  |

|                      |                       | P76, P77                     |                               | General purpose I/O pins.                                                                                                                                            |  |  |  |

| 55, 56 53, 54        |                       | AN22, AN23                   | 1                             | Analog input pins for the A/D converter (devices with a C suffix in the part number)                                                                                 |  |  |  |

|                      |                       | INT6, INT7                   |                               | External interrupt request input pins                                                                                                                                |  |  |  |

|                      |                       | P80                          |                               | General purpose I/O pin.                                                                                                                                             |  |  |  |

| F7                   |                       | TIN0                         | F                             | Event input pin for the reload timer                                                                                                                                 |  |  |  |

| 57                   | 55                    | ADTG                         |                               | Trigger input pin for the A/D converter                                                                                                                              |  |  |  |

|                      |                       | INT12R                       |                               | External interrupt request input pin                                                                                                                                 |  |  |  |

|                      |                       | P81                          |                               | General purpose I/O pin.                                                                                                                                             |  |  |  |

| 50                   | 50                    | ТОТО                         | F                             | Output pin for the reload timer                                                                                                                                      |  |  |  |

| 58                   | 56                    | СКОТ                         |                               | Output pin for the clock monitor                                                                                                                                     |  |  |  |

|                      |                       | INT13R                       |                               | External interrupt request input pin                                                                                                                                 |  |  |  |

|                      |                       | P82                          |                               | General purpose I/O pin.                                                                                                                                             |  |  |  |

| 50                   | <b>F</b> 7            | SIN0                         |                               | Serial data input pin for UART0                                                                                                                                      |  |  |  |

| 59 57 T              |                       | TIN2                         | M                             | Event input pin for the reload timer                                                                                                                                 |  |  |  |

|                      | INT14R                |                              | 1                             | External interrupt request input pin                                                                                                                                 |  |  |  |

|                      |                       | P83                          | 1                             | General purpose I/O pin.                                                                                                                                             |  |  |  |

| 60                   | 58                    | SOT0                         | F                             | Serial data output pin for UART0                                                                                                                                     |  |  |  |

|                      |                       | TOT2                         |                               | Output pin for the reload timer                                                                                                                                      |  |  |  |

| Туре | Circuit                                                                                                                                                            | Remarks                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F    | P-ch Pout<br>N-ch Nout<br>R<br>7/7<br>CMOS hysteresis<br>input<br>Automotive input<br>Standby control for<br>input shutdown                                        | <ul> <li>CMOS level output<br/>(I<sub>OL</sub> = 4 mA, I<sub>OH</sub> = -4 mA)</li> <li>CMOS hysteresis input (with function to disconnect<br/>input during standby)</li> <li>Automotive input (with function to<br/>disconnect input during standby)</li> </ul>                                                                                                                                     |

| G    | P-ch P-ch Pout<br>P-ch P-ch Pout<br>P-ch Pout<br>R<br>R<br>R<br>CMOS hysteresis<br>input<br>Automotive input<br>TTL input<br>Standby control for<br>input shutdown | <ul> <li>CMOS level output<br/>(I<sub>OL</sub> = 4 mA, I<sub>OH</sub> = -4 mA)</li> <li>CMOS hysteresis input (with function to disconnect<br/>input during standby)</li> <li>Automotive input (with function to<br/>disconnect input during standby)</li> <li>TTL input (with function to disconnect<br/>input during standby)</li> <li>Programmable pull-up resistor: 50 kΩ<br/>approx.</li> </ul> |

| н    | P-ch Pout<br>P-ch Pout<br>N-ch Nout<br>R 777<br>CMOS hysteresis<br>input<br>Automotive input<br>Standby control for<br>input shutdown                              | <ul> <li>CMOS level output<br/>(I<sub>OL</sub> = 3 mA, I<sub>OH</sub> = -3 mA)</li> <li>CMOS hysteresis input (with function to disconnect<br/>input during standby)</li> <li>Automotive input (with function to<br/>disconnect input during standby)</li> </ul>                                                                                                                                     |

## 5. Handling Devices

## 1. Preventing latch-up

CMOS IC may suffer latch-up under the following conditions:

- A voltage higher than V<sub>CC</sub> or lower than V<sub>SS</sub> is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between V<sub>CC</sub> and V<sub>SS</sub> pins.

- The AV<sub>CC</sub> power supply is applied before the V<sub>CC</sub> voltage.

Latch-up may increase the power supply current drastically, causing thermal damage to the device.

For the same reason, also be careful not to let the analog power-supply voltage (AV<sub>CC</sub>, AVRH) exceed the digital power-supply voltage.

### 2. Handling unused pins

Leaving unused input terminals open may lead to permanent damage due to malfunction and latch-up; pull up or pull down the terminals through the resistors of 2 k $\Omega$  or more.

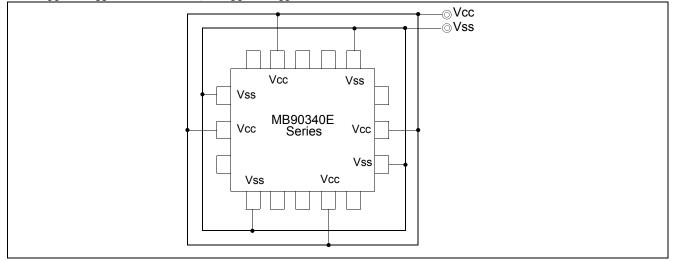

## 3.Power supply pins (V<sub>CC</sub>/V<sub>SS</sub>)

■ If there are multiple V<sub>CC</sub> and V<sub>SS</sub> pins, from the point of view of device design, pins to be of the same potential are connected inside of the device to prevent malfunction such as latch-up.

To reduce unnecessary radiation, prevent malfunctioning of the strobe signal due to the rise of ground level, and observe the standard for total output current, be sure to connect the  $V_{CC}$  and  $V_{SS}$  pins to the power supply and ground externally. Connect  $V_{CC}$  and  $V_{SS}$  pins to the device from the current supply source at a possibly low impedance.

As a measure against power supply noise, it is recommended to connect a capacitor of about 0.1 μF as a bypass capacitor between V<sub>CC</sub> and V<sub>SS</sub> pins in the vicinity of V<sub>CC</sub> and V<sub>SS</sub> pins of the device.

### 4.Mode Pins (MD0 to MD2)

Connect the mode pins directly to  $V_{CC}$  or  $V_{SS}$  pins. To prevent the device unintentionally entering test mode due to noise, lay out the printed circuit board so as to minimize the distance from the mode pins to  $V_{CC}$  or  $V_{SS}$  pins and to provide a low-impedance connection.

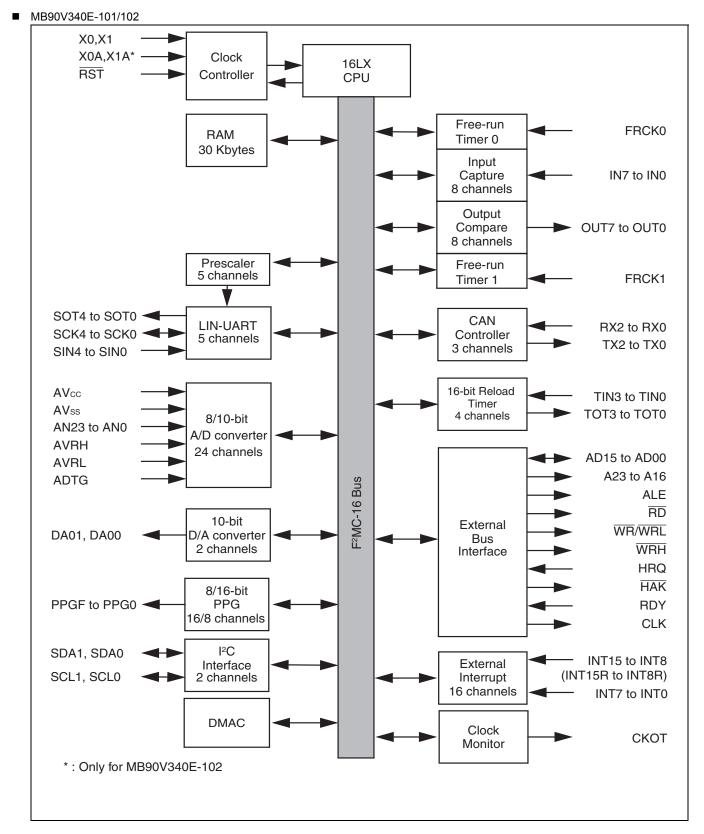

## 6. Block Diagrams

| Address             | Register                                    | Abbreviation | Access | Resource name       | Initial value         |

|---------------------|---------------------------------------------|--------------|--------|---------------------|-----------------------|

| 000040 <sub>H</sub> | PPG 8 Operation Mode Control Register       | PPGC8        | W,R/W  |                     | 0X000XX1 <sub>B</sub> |

| 000041 <sub>H</sub> | PPG 9 Operation Mode Control Register       | PPGC9        | W,R/W  | 16-bit PPG 8/9      | 0X000001 <sub>B</sub> |

| 000042 <sub>H</sub> | PPG 8/PPG 9 Count Clock Control<br>Register | PPG89        | R/W    |                     | 000000X0 <sub>B</sub> |

| 000043 <sub>H</sub> | Reserved                                    |              |        | •                   |                       |

| 000044 <sub>H</sub> | PPG A Operation Mode Control Register       | PPGCA        | W,R/W  |                     | 0X000XX1 <sub>B</sub> |

| 000045 <sub>H</sub> | PPG B Operation Mode Control Register       | PPGCB        | W,R/W  | 16-bit PPG A/B      | 0X000001 <sub>B</sub> |

| 000046 <sub>H</sub> | PPG A/PPG B Count Clock Select<br>Register  | PPGAB        | R/W    |                     | 000000X0 <sub>B</sub> |

| 000047 <sub>H</sub> | Reserved                                    | ·            |        |                     | ·                     |

| 000048 <sub>H</sub> | PPG C Operation Mode Control Register       | PPGCC        | W,R/W  |                     | 0X000XX1 <sub>B</sub> |

| 000049 <sub>H</sub> | PPG D Operation Mode Control Register       | PPGCD        | W,R/W  | 16-bit PPG C/D      | 0X000001 <sub>B</sub> |

| 00004A <sub>H</sub> | PPG C/PPG D Count Clock Select<br>Register  | PPGCD        | R/W    |                     | 000000X0 <sub>B</sub> |

| 00004B <sub>H</sub> | Reserved                                    | ·            |        | ·                   |                       |

| 00004C <sub>H</sub> | PPG E Operation Mode Control Register       | PPGCE        | W,R/W  |                     | 0X000XX1 <sub>B</sub> |

| 00004D <sub>H</sub> | PPG F Operation Mode Control Register       | PPGCF        | W,R/W  | 16-bit PPG E/F      | 0X000001 <sub>B</sub> |

| 00004E <sub>H</sub> | PPG E/PPG F Count Clock Select<br>Register  | PPGEF        | R/W    |                     | 000000X0 <sub>B</sub> |

| 00004F <sub>H</sub> | Reserved                                    | ·            |        |                     |                       |

| 000050 <sub>H</sub> | Input Capture Control Status 0/1            | ICS01        | R/W    | Input Conturo 0/1   | 00000000 <sub>B</sub> |

| 000051 <sub>H</sub> | Input Capture Edge 0/1                      | ICE01        | R/W, R | Input Capture 0/1   | XXX0X0XX <sub>B</sub> |

| 000052 <sub>H</sub> | Input Capture Control Status 2/3            | ICS23        | R/W    | Input Conturo 2/2   | 00000000 <sub>B</sub> |

| 000053 <sub>H</sub> | Input Capture Edge 2/3                      | ICE23        | R      | Input Capture 2/3   | XXXXXXXX <sub>B</sub> |

| 000054 <sub>H</sub> | Input Capture Control Status 4/5            | ICS45        | R/W    | Input Capture 4/5   | 00000000 <sub>B</sub> |

| 000055 <sub>H</sub> | Input Capture Edge 4/5                      | ICE45        | R      | Input Capture 4/5   | XXXXXXXAB             |

| 000056 <sub>H</sub> | Input Capture Control Status 6/7            | ICS67        | R/W    | Input Capture 6/7   | 00000000 <sub>B</sub> |

| 000057 <sub>H</sub> | Input Capture Edge 6/7                      | ICE67        | R/W, R |                     | XXX000XX <sub>B</sub> |

| 000058 <sub>H</sub> | Output Compare Control Status 0             | OCS0         | R/W    | Output Compare 0/1  | 0000XX00 <sub>B</sub> |

| 000059 <sub>H</sub> | Output Compare Control Status 1             | OCS1         | R/W    | Output Compare of I | 0XX00000 <sub>B</sub> |

| 00005A <sub>H</sub> | Output Compare Control Status 2             | OCS2         | R/W    | Output Compare 2/3  | 0000XX00 <sub>B</sub> |

| 00005B <sub>H</sub> | Output Compare Control Status 3             | OCS3         | R/W    |                     | 0XX00000 <sub>B</sub> |

| 00005C <sub>H</sub> | Output Compare Control Status 4             | OCS4         | R/W    | Output Compare 4/5  | 0000XX00 <sub>B</sub> |

| 00005D <sub>H</sub> | Output Compare Control Status 5             | OCS5         | R/W    |                     | 0XX00000 <sub>B</sub> |

| 00005E <sub>H</sub> | Output Compare Control Status 6             | OCS6         | R/W    | Output Compare 6/7  | 0000XX00 <sub>B</sub> |

| 00005F <sub>H</sub> | Output Compare Control Status 7             | OCS7         | R/W    |                     | 0XX00000 <sub>B</sub> |

| Address                                          | Register                                     | Abbreviation   | Access                | Resource name        | Initial value         |

|--------------------------------------------------|----------------------------------------------|----------------|-----------------------|----------------------|-----------------------|

| 0000C4 <sub>H</sub> ,<br>0000C5 <sub>H</sub>     | Reserved                                     |                | •                     |                      |                       |

| 0000C6 <sub>H</sub>                              | External Interrupt Enable 0                  | ENIR0          | R/W                   |                      | 00000000 <sub>B</sub> |

| 0000C7 <sub>H</sub>                              | External Interrupt Source 0                  | EIRR0          | R/W                   |                      | XXXXXXXAB             |

| 0000C8 <sub>H</sub>                              | External Interrupt Level Setting 0           | ELVR0          | R/W                   | External Interrupt 0 | 00000000 <sub>B</sub> |

| 0000C9 <sub>H</sub>                              | External Interrupt Level Setting 0           | ELVR0          | R/W                   |                      | 00000000 <sub>B</sub> |

| 0000CA <sub>H</sub>                              | External Interrupt Enable 1                  | ENIR1          | R/W                   |                      | 00000000 <sub>B</sub> |

| 0000CB <sub>H</sub>                              | External Interrupt Source 1                  |                | XXXXXXXX <sub>B</sub> |                      |                       |

| 0000CC <sub>H</sub>                              | External Interrupt Level Setting 1           | ELVR1          | R/W                   | External Interrupt 1 | 00000000 <sub>B</sub> |

| 0000CD <sub>H</sub>                              | External Interrupt Level Setting 1           | ELVR1          | R/W                   |                      | 00000000 <sub>B</sub> |

| 0000CE <sub>H</sub>                              | External Interrupt Source Select             | EISSR          | R/W                   |                      | 00000000 <sub>B</sub> |

| 0000CF <sub>H</sub>                              | PLL/Sub clock Control Register               | PSCCR          | W                     | PLL                  | XXXX0000 <sub>B</sub> |

| 0000D0 <sub>H</sub>                              | DMA Buffer Address Pointer L Register        | BAPL           | R/W                   |                      | XXXXXXXAB             |

| 0000D1 <sub>H</sub>                              | DMA Buffer Address Pointer M Register        | BAPM           | R/W                   |                      | XXXXXXX <sub>B</sub>  |

| 0000D2 <sub>H</sub>                              | DMA Buffer Address Pointer H Register        | BAPH           | R/W                   |                      | XXXXXXXAB             |

| 0000D3 <sub>H</sub>                              | DMA Control Register                         | DMACS          | R/W                   |                      | XXXXXXX <sub>B</sub>  |

| 0000D4 <sub>H</sub>                              | I/O Register Address Pointer L<br>Register   | IOAL           | R/W                   | DMA                  | XXXXXXXX <sub>B</sub> |

| 0000D5 <sub>H</sub>                              | I/O Register Address Pointer H<br>Register   | IOAH           | R/W                   |                      | XXXXXXXXB             |

| 0000D6 <sub>H</sub>                              | Data Counter L Register                      | DCTL           | R/W                   |                      | XXXXXXX <sub>B</sub>  |

| 0000D7 <sub>H</sub>                              | Data Counter H Register                      | DCTH           | R/W                   |                      | XXXXXXX <sub>B</sub>  |

| 0000D8 <sub>H</sub>                              | Serial Mode Register 2                       | SMR2           | W,R/W                 |                      | 00000000 <sub>B</sub> |

| 0000D9 <sub>H</sub>                              | Serial Control Register 2                    | SCR2           | W,R/W                 |                      | 00000000 <sub>B</sub> |

| 0000DA <sub>H</sub>                              | Reception/Transmission Data<br>Register 2    | RDR2/TDR2      | R/W                   |                      | 00000000 <sub>B</sub> |

| 0000DB <sub>H</sub>                              | Serial Status Register 2                     | SSR2           | R,R/W                 |                      | 00001000 <sub>B</sub> |

| 0000DC <sub>H</sub>                              | Extended Communication Control<br>Register 2 | ECCR2          | R,W,<br>R/W           | UART2                | 000000XX <sub>B</sub> |

| 0000DD <sub>H</sub>                              | Extended Status Control Register 2           | ESCR2          | R/W                   |                      | 00000100 <sub>B</sub> |

| 0000DE <sub>H</sub>                              | Baud Rate Generator Register 20              | BGR20          | R/W                   |                      | 00000000 <sub>B</sub> |

| 0000DF <sub>H</sub>                              | Baud Rate Generator Register 21              | BGR21          | R/W                   | 1                    | 00000000 <sub>B</sub> |

| 0000E0 <sub>H</sub><br>to<br>0000EF <sub>H</sub> | Reserved for CAN Controller 2. Refer to "CAN | I Controllers" | •                     | ·                    |                       |

| 0000F0 <sub>H</sub><br>to<br>0000FF <sub>H</sub> | External                                     |                |                       |                      |                       |

| Address             | Register               | Abbreviation | Access | Resource name      | Initial value         |

|---------------------|------------------------|--------------|--------|--------------------|-----------------------|

| 007924 <sub>H</sub> | Input Capture 2        | IPCP2        | R      |                    | XXXXXXXXB             |

| 007925 <sub>H</sub> | Input Capture 2        | IPCP2        | R      | Innut Conturo 2/2  | XXXXXXXX <sub>B</sub> |

| 007926 <sub>H</sub> | Input Capture 3        | IPCP3        | R      | Input Capture 2/3  | XXXXXXXXB             |

| 007927 <sub>H</sub> | Input Capture 3        | IPCP3        | R      |                    | XXXXXXXXB             |

| 007928 <sub>H</sub> | Input Capture 4        | IPCP4        | R      |                    | XXXXXXXXB             |

| 007929 <sub>H</sub> | Input Capture 4        | IPCP4        | R      | Input Capture 4/5  | XXXXXXXXB             |

| 00792A <sub>H</sub> | Input Capture 5        | IPCP5        | R      | Input Capture 4/5  | XXXXXXXXB             |

| 00792B <sub>H</sub> | Input Capture 5        | IPCP5        | R      |                    | XXXXXXXX <sub>B</sub> |

| 00792C <sub>H</sub> | Input Capture 6        | IPCP6        | R      |                    | XXXXXXXXB             |

| 00792D <sub>H</sub> | Input Capture 6        | IPCP6        | R      | Input Conturo 6/7  | XXXXXXXXB             |

| 00792E <sub>H</sub> | Input Capture 7        | IPCP7        | R      | Input Capture 6/7  | XXXXXXXX <sub>B</sub> |

| 00792F <sub>H</sub> | Input Capture 7        | IPCP7        | R      |                    | XXXXXXXXB             |

| 007930 <sub>H</sub> | Output Compare 0       | OCCP0        | R/W    |                    | XXXXXXXXB             |

| 007931 <sub>H</sub> | Output Compare 0       | OCCP0        | R/W    | Output Compare 0/1 | XXXXXXXX <sub>B</sub> |

| 007932 <sub>H</sub> | Output Compare 1       | OCCP1        | R/W    |                    | XXXXXXXXB             |

| 007933 <sub>H</sub> | Output Compare 1       | OCCP1        | R/W    |                    | XXXXXXXXB             |

| 007934 <sub>H</sub> | Output Compare 2       | OCCP2        | R/W    |                    | XXXXXXXX <sub>B</sub> |

| 007935 <sub>H</sub> | Output Compare 2       | OCCP2        | R/W    | Output Compare 2/3 | XXXXXXXXB             |

| 007936 <sub>H</sub> | Output Compare 3       | OCCP3        | R/W    |                    | XXXXXXXXB             |

| 007937 <sub>H</sub> | Output Compare 3       | OCCP3        | R/W    |                    | XXXXXXXX <sub>B</sub> |

| 007938 <sub>H</sub> | Output Compare 4       | OCCP4        | R/W    |                    | XXXXXXXXB             |

| 007939 <sub>H</sub> | Output Compare 4       | OCCP4        | R/W    | Output Compare 4/5 | XXXXXXXX <sub>B</sub> |

| 00793A <sub>H</sub> | Output Compare 5       | OCCP5        | R/W    |                    | XXXXXXXX <sub>B</sub> |

| 00793B <sub>H</sub> | Output Compare 5       | OCCP5        | R/W    |                    | XXXXXXXX <sub>B</sub> |

| 00793C <sub>H</sub> | Output Compare 6       | OCCP6        | R/W    |                    | XXXXXXXX <sub>B</sub> |

| 00793D <sub>H</sub> | Output Compare 6       | OCCP6        | R/W    | Output Compare 6/7 | XXXXXXXX <sub>B</sub> |

| 00793E <sub>H</sub> | Output Compare 7       | OCCP7        | R/W    |                    | XXXXXXXX <sub>B</sub> |

| 00793F <sub>H</sub> | Output Compare 7       | OCCP7        | R/W    |                    | XXXXXXXX <sub>B</sub> |

| 007940 <sub>H</sub> | Timer Data 0           | TCDT0        | R/W    |                    | 00000000 <sub>B</sub> |

| 007941 <sub>H</sub> | Timer Data 0           | TCDT0        | R/W    | Eroo run Timor 0   | 00000000 <sub>B</sub> |

| 007942 <sub>H</sub> | Timer Control Status 0 | TCCSL0       | R/W    | Free-run Timer 0   | 00000000 <sub>B</sub> |

| 007943 <sub>H</sub> | Timer Control Status 0 | TCCSH0       | R/W    |                    | 0XXXXXXAB             |

| 007944 <sub>H</sub> | Timer Data 1           | TCDT1        | R/W    |                    | 00000000 <sub>B</sub> |

| 007945 <sub>H</sub> | Timer Data 1           | TCDT1        | R/W    | Eroo run Timor 1   | 00000000 <sub>B</sub> |

| 007946 <sub>H</sub> | Timer Control Status 1 | TCCSL1       | R/W    | Free-run Timer 1   | 00000000 <sub>B</sub> |

| 007947 <sub>H</sub> | Timer Control Status 1 | TCCSH1       | R/W    |                    | 0XXXXXXAB             |

| List of Control | Registers (2) |

|-----------------|---------------|

|-----------------|---------------|

| Address             |                     | Pagiotor                    | Abbreviation | A       | Initial Value                                 |

|---------------------|---------------------|-----------------------------|--------------|---------|-----------------------------------------------|

| CAN0                | CAN1                | Register                    | Appreviation | Access  |                                               |

| 007B00 <sub>H</sub> | 007D00 <sub>H</sub> | Control Status              | CSR          | R/W, W  | 0XXXX0X1 <sub>B</sub>                         |

| 007B01 <sub>H</sub> | 007D01 <sub>H</sub> | Register                    | CSR          | R/W, R  | 00XXX000 <sub>B</sub>                         |

| 007B02 <sub>H</sub> | 007D02 <sub>H</sub> | Last Event                  | LEIR         | R/W     | 000X0000 <sub>B</sub><br>XXXXXXX <sub>B</sub> |

| 007B03 <sub>H</sub> | 007D03 <sub>H</sub> | Indicator Register          |              | r./ v v | XXXXXXXXX                                     |

| 007B04 <sub>H</sub> | 007D04 <sub>H</sub> | Receive And Transmit        | RTEC         | R       | 00000000 <sub>B</sub>                         |

| 007B05 <sub>H</sub> | 007D05 <sub>H</sub> | Error Counter               | KILO         | n.      | 00000000B                                     |

| 007B06 <sub>H</sub> | 007D06 <sub>H</sub> | Bit Timing                  | BTR          | R/W     | 11111111 <sub>B</sub>                         |

| 007B07 <sub>H</sub> | 007D07 <sub>H</sub> | Register                    | DIK          |         | X1111111 <sub>B</sub>                         |

| 007B08 <sub>H</sub> | 007D08 <sub>H</sub> | IDE Register                | IDER         | R/W     | XXXXXXXX <sub>B</sub>                         |

| 007B09 <sub>H</sub> | 007D09 <sub>H</sub> |                             | IDER         |         | XXXXXXXXB                                     |

| 007B0A <sub>H</sub> | 007D0A <sub>H</sub> | Transmit RTR                | TRTRR        | R/W     | 00000000 <sub>B</sub>                         |

| 007B0B <sub>H</sub> | 007D0B <sub>H</sub> | Register                    |              |         | 00000000B                                     |

| 007B0C <sub>H</sub> | 007D0C <sub>H</sub> | Remote Frame                | RFWTR        | R/W     | XXXXXXXX                                      |

| 007B0D <sub>H</sub> | 007D0D <sub>H</sub> | Receive Waiting<br>Register | REVIR        |         | XXXXXXXXB                                     |

| 007B0E <sub>H</sub> | 007D0E <sub>H</sub> | Transmit Interrupt          | TIER         | R/W     | 00000000 <sub>B</sub>                         |

| 007B0F <sub>H</sub> | 007D0F <sub>H</sub> | Enable Register             |              |         | 00000000B                                     |

| 007B10 <sub>H</sub> | 007D10 <sub>H</sub> |                             |              |         | XXXXXXXXB                                     |

| 007B11 <sub>H</sub> | 007D11 <sub>H</sub> | Acceptance Mask             | AMSR         | R/W     | XXXXXXXXB                                     |

| 007B12 <sub>H</sub> | 007D12 <sub>H</sub> | Select Register             |              |         | XXXXXXXXB                                     |

| 007B13 <sub>H</sub> | 007D13 <sub>H</sub> |                             |              |         | XXXXXXXXB                                     |

| 007B14 <sub>H</sub> | 007D14 <sub>H</sub> |                             |              |         | XXXXXXXXB                                     |

| 007B15 <sub>H</sub> | 007D15 <sub>H</sub> | Acceptance Mask             | AMR0         | R/W     | XXXXXXXXB                                     |

| 007B16 <sub>H</sub> | 007D16 <sub>H</sub> | Register 0                  |              |         | XXXXXXXXB                                     |

| 007B17 <sub>H</sub> | 007D17 <sub>H</sub> |                             |              |         | XXXXXXXX <sub>B</sub>                         |

| 007B18 <sub>H</sub> | 007D18 <sub>H</sub> |                             |              |         | XXXXXXXXB                                     |

| 007B19 <sub>H</sub> | 007D19 <sub>H</sub> | Acceptance Mask             | AMR1         | R/W     | XXXXXXXXB                                     |

| 007B1A <sub>H</sub> | 007D1A <sub>H</sub> | Register 1                  |              |         | XXXXXXXXB                                     |

| 007B1B <sub>H</sub> | 007D1B <sub>H</sub> |                             |              |         | XXXXXXXXB                                     |

| Address                                          |                                                  | Pagiotor                | Abbreviation | A      | Initial Value                |

|--------------------------------------------------|--------------------------------------------------|-------------------------|--------------|--------|------------------------------|

| CAN0                                             | CAN1                                             | Register                | Appreviation | Access |                              |

| 007A00 <sub>H</sub><br>to<br>007A1F <sub>H</sub> | 007C00 <sub>H</sub><br>to<br>007C1F <sub>H</sub> | General-<br>Purpose RAM | _            | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB |

| 007A20 <sub>H</sub>                              | 007C20 <sub>H</sub>                              |                         |              |        | XXXXXXXX <sub>B</sub>        |

| 007A21 <sub>H</sub>                              | 007C21 <sub>H</sub>                              | ID De sister 0          |              |        | XXXXXXXAB                    |

| 007A22 <sub>H</sub>                              | 007C22 <sub>H</sub>                              | ID Register 0           | IDR0         | R/W    | XXXXXXXX <sub>B</sub>        |

| 007A23 <sub>H</sub>                              | 007C23 <sub>H</sub>                              |                         |              |        | XXXXXXXAB                    |

| 007A24 <sub>H</sub>                              | 007C24 <sub>H</sub>                              |                         |              |        | XXXXXXXXB                    |

| 007A25 <sub>H</sub>                              | 007C25 <sub>H</sub>                              | ID De sister 1          |              |        | XXXXXXXXB                    |

| 007A26 <sub>H</sub>                              | 007C26 <sub>H</sub>                              | ID Register 1           | IDR1         | R/W    | XXXXXXXX <sub>B</sub>        |

| 007A27 <sub>H</sub>                              | 007C27 <sub>H</sub>                              |                         |              |        | XXXXXXXB                     |

| 007A28 <sub>H</sub>                              | 007C28 <sub>H</sub>                              |                         |              |        | XXXXXXXXB                    |

| 007A29 <sub>H</sub>                              | 007C29 <sub>H</sub>                              | ID Desister 2           |              |        | XXXXXXXXB                    |

| 007A2A <sub>H</sub>                              | 007C2A <sub>H</sub>                              | ID Register 2           | IDR2         | R/W    | XXXXXXXX <sub>B</sub>        |

| 007A2B <sub>H</sub>                              | 007C2B <sub>H</sub>                              |                         |              |        | XXXXXXXXB                    |

| 007A2C <sub>H</sub>                              | 007C2C <sub>H</sub>                              |                         |              |        | XXXXXXXX <sub>B</sub>        |

| 007A2D <sub>H</sub>                              | 007C2D <sub>H</sub>                              | ID Degister 2           | IDR3         | R/W    | XXXXXXXXB                    |

| 007A2E <sub>H</sub>                              | 007C2E <sub>H</sub>                              | ID Register 3           |              |        | XXXXXXXX <sub>B</sub>        |

| 007A2F <sub>H</sub>                              | 007C2F <sub>H</sub>                              |                         |              |        | XXXXXXXXB                    |

| 007A30 <sub>H</sub>                              | 007C30 <sub>H</sub>                              |                         |              |        | XXXXXXXXR                    |

| 007A31 <sub>H</sub>                              | 007C31 <sub>H</sub>                              | ID Pagistar 4           | IDR4         | R/W    | XXXXXXXXB<br>XXXXXXXXB       |

| 007A32 <sub>H</sub>                              | 007C32 <sub>H</sub>                              | ID Register 4           | IDR4         |        | XXXXXXXX <sub>B</sub>        |

| 007A33 <sub>H</sub>                              | 007C33 <sub>H</sub>                              |                         |              |        | XXXXXXXXB                    |

| 007A34 <sub>H</sub>                              | 007C34 <sub>H</sub>                              |                         |              |        | XXXXXXXXB                    |

| 007A35 <sub>H</sub>                              | 007C35 <sub>H</sub>                              | ID Register 5           | IDR5         | R/W    | XXXXXXXX                     |

| 007A36 <sub>H</sub>                              | 007C36 <sub>H</sub>                              |                         | IDKJ         |        | XXXXXXXXB                    |

| 007A37 <sub>H</sub>                              | 007C37 <sub>H</sub>                              |                         |              |        | XXXXXXXXB                    |

| 007A38 <sub>H</sub>                              | 007C38 <sub>H</sub>                              |                         |              |        | XXXXXXXAB                    |

| 007A39 <sub>H</sub>                              | 007C39 <sub>H</sub>                              | ID Register 6           | IDR6         | DAA/   | XXXXXXXXB                    |

| 007A3A <sub>H</sub>                              | 007C3A <sub>H</sub>                              |                         |              | R/W    | XXXXXXXAB                    |

| 007A3B <sub>H</sub>                              | 007C3B <sub>H</sub>                              |                         |              |        | XXXXXXXXB                    |

| 007A3C <sub>H</sub>                              | 007C3C <sub>H</sub>                              |                         |              |        | XXXXXXXXB                    |

| 007A3D <sub>H</sub>                              | 007C3D <sub>H</sub>                              | ID Register 7           | IDR7         | R/W    | XXXXXXXXB                    |

| 007A3E <sub>H</sub>                              | 007C3E <sub>H</sub>                              | INEGISIEI I             |              |        | XXXXXXXX <sub>B</sub>        |

| 007A3F <sub>H</sub>                              | 007C3F <sub>H</sub>                              |                         |              |        | XXXXXXXXB                    |

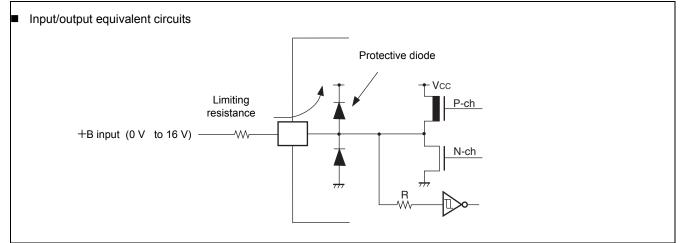

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the

resulting supply voltage may not be sufficient to operate the power-on reset.

- Care must be taken not to leave the +B input pin open.

- Sample recommended circuits:

\*6: The maximum output current is defined as the peak value of the current of any one of the corresponding pins.

\*7: The average output current is defined as the value of the average current flowing over 100 ms at any one of the corresponding pins.

\*8: The average total output current is defined as the value of the average current flowing over 100 ms at all of the corresponding pins.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

## 11.2 Recommended Operating Conditions

$(V_{SS} = AV_{SS} = 0 V)$

| Parameter             | Symbol                                | Value |     |      | Unit | Remarks                                                                                                                             |

|-----------------------|---------------------------------------|-------|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| Falameter             | Symbol                                | Min   | Тур | Мах  | Onit | Reliaiks                                                                                                                            |

|                       |                                       | 4.0   | 5.0 | 5.5  | V    | Under normal operation                                                                                                              |

| Power supply voltage  | V <sub>CC</sub> ,<br>AV <sub>CC</sub> | 3.5   | 5.0 | 5.5  | v    | Under normal operation, when not using the A/D converter and not Flash programming.                                                 |

|                       |                                       | 4.5   | 5.0 | 5.5  | V    | When External bus is used.                                                                                                          |

|                       |                                       | 3.0   | —   | 5.5  | V    | Maintains RAM data in stop mode                                                                                                     |

| Smoothing capacitor   | C <sub>S</sub>                        | 0.1   |     | 1.0  | μF   | Use a ceramic capacitor or capacitor of better AC characteristics. Capacitor at the $V_{CC}$ should be greater than this capacitor. |

| Operating temperature | T <sub>A</sub>                        | -40   |     | +105 | °C   |                                                                                                                                     |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

## **11.3 DC Characteristics**

| Deveration                                                | Symb             | Dia                                 | Condition                               | Value                 |             |                       | 11   | Bemerke                                                                                                           |  |  |  |

|-----------------------------------------------------------|------------------|-------------------------------------|-----------------------------------------|-----------------------|-------------|-----------------------|------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                                                 | ol               | Pin                                 | Condition                               | Min                   | Min Typ Max |                       | Unit | Remarks                                                                                                           |  |  |  |

|                                                           | V <sub>IHS</sub> |                                     |                                         | 0.8 V <sub>CC</sub>   |             | V <sub>CC</sub> + 0.3 | v    | Port inputs if CMOS<br>hysteresis input levels are selected<br>(except P12, P44, P45, P46, P47,<br>P50, P82, P85) |  |  |  |

|                                                           | V <sub>IHA</sub> |                                     |                                         | 0.8 V <sub>CC</sub>   |             | $V_{CC} + 0.3$        | V    | Port inputs if<br>Automotive input levels are selected                                                            |  |  |  |

| Input H                                                   | V <sub>IHT</sub> |                                     |                                         | 2.0                   |             | $V_{CC} + 0.3$        | V    | Port inputs if TTL input levels are selected                                                                      |  |  |  |

| voltage<br>(At V <sub>CC</sub> =<br>5 V ± 10%)            | V <sub>IHS</sub> |                                     |                                         | 0.7 V <sub>CC</sub>   |             | $V_{CC} + 0.3$        | v    | P12, P50, P82, P85<br>inputs if CMOS input levels are<br>selected                                                 |  |  |  |

|                                                           | V <sub>IHI</sub> |                                     |                                         | 0.7 V <sub>CC</sub>   |             | V <sub>CC</sub> + 0.3 | v    | P44, P45, P46, P47<br>inputs if CMOS hysteresis<br>input levels are selected                                      |  |  |  |

|                                                           | V <sub>IHR</sub> |                                     |                                         | 0.8 V <sub>CC</sub>   |             | $V_{CC} + 0.3$        | V    | RST input pin<br>(CMOS hysteresis)                                                                                |  |  |  |

|                                                           | V <sub>IHM</sub> |                                     |                                         | $V_{\rm CC} - 0.3$    |             | $V_{CC} + 0.3$        | V    | MD input pin                                                                                                      |  |  |  |

| Input L<br>voltage<br>(At V <sub>CC</sub> =<br>5 V ± 10%) | V <sub>ILS</sub> |                                     |                                         | V <sub>SS</sub> – 0.3 |             | 0.2 V <sub>CC</sub>   | v    | Port inputs if CMOS<br>hysteresis input levels are selected<br>(except P12, P44, P45, P46, P47,<br>P50, P82, P85) |  |  |  |

|                                                           | V <sub>ILA</sub> |                                     |                                         | $V_{\rm SS} - 0.3$    |             | 0.5 V <sub>CC</sub>   | V    | Port inputs if<br>Automotive input levels are selected                                                            |  |  |  |

|                                                           | V <sub>ILT</sub> |                                     |                                         | $V_{\rm SS} - 0.3$    |             | 0.8                   | V    | Port inputs if TTL<br>input levels are selected                                                                   |  |  |  |

|                                                           | V <sub>ILS</sub> |                                     |                                         | V <sub>SS</sub> - 0.3 |             | 0.3 V <sub>CC</sub>   | v    | P12, P50, P82, P85<br>inputs if CMOS input levels are<br>selected                                                 |  |  |  |

|                                                           | V <sub>ILI</sub> |                                     |                                         | V <sub>SS</sub> - 0.3 |             | 0.3 V <sub>CC</sub>   | v    | P44, P45, P46, P47<br>inputs if CMOS hysteresis<br>input levels are selected                                      |  |  |  |

|                                                           | V <sub>ILR</sub> |                                     |                                         | $V_{\rm SS} - 0.3$    |             | 0.2 V <sub>CC</sub>   | V    | RST input pin<br>(CMOS hysteresis)                                                                                |  |  |  |

|                                                           | V <sub>ILM</sub> |                                     |                                         | $V_{\rm SS} - 0.3$    |             | $V_{SS} + 0.3$        | V    | MD input pin                                                                                                      |  |  |  |

| Output H<br>voltage                                       | V <sub>OH</sub>  | Normal<br>outputs                   | $V_{CC} = 4.5 V,$<br>$I_{OH} = -4.0 mA$ | V <sub>CC</sub> - 0.5 |             |                       | V    |                                                                                                                   |  |  |  |

| Output H<br>voltage                                       | V <sub>OHI</sub> | I <sup>2</sup> C current<br>outputs | $V_{CC} = 4.5 V,$<br>$I_{OH} = -3.0 mA$ | V <sub>CC</sub> - 0.5 |             |                       | v    |                                                                                                                   |  |  |  |

| Output L<br>voltage                                       | V <sub>OL</sub>  | Normal outputs                      | $V_{CC} = 4.5 V,$<br>$I_{OL} = 4.0 mA$  |                       |             | 0.4                   | v    |                                                                                                                   |  |  |  |

| Output L<br>voltage                                       | V <sub>OLI</sub> | I <sup>2</sup> C current outputs    | $V_{CC} = 4.5 V,$<br>$I_{OL} = 3.0 mA$  |                       |             | 0.4                   | V    |                                                                                                                   |  |  |  |

(T\_A = -40°C to +105°C, V\_{CC} = 5.0 V  $\pm$  10%, f\_{CP}  $\leq$  24 MHz, V\_{SS} = AV\_{SS} = 0 V)

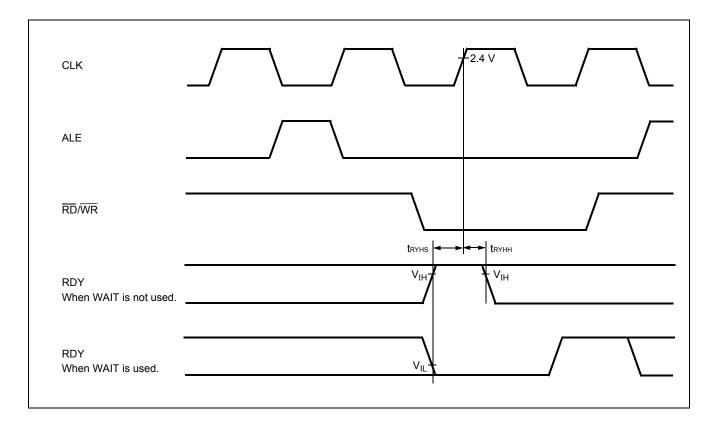

## 11.4.7 Ready Input Timing

(T\_A = -40°C to +105°C, V\_{CC} = 5.0 V  $\pm$  10%, V\_{SS} = 0.0 V, f\_{CP} {\leq} 24 MHz)

| Parameter      | Symbol            | Pin | Test      | Rated | Value | Unit | Remarks                   |  |

|----------------|-------------------|-----|-----------|-------|-------|------|---------------------------|--|

| Falameter      |                   |     | Condition | Min   | Max   | Unit |                           |  |

| RDY setup time | t <sub>RYHS</sub> | RDY |           | 45    |       | ns   | $f_{CP} = 16 \text{ MHz}$ |  |

| RDT setup time |                   |     |           | 32    | —     | ns   | $f_{CP} = 24 \text{ MHz}$ |  |

| RDY hold time  | t <sub>RYHH</sub> | RDY |           | 0     |       | ns   |                           |  |

**Note:** : If the RDY setup time is insufficient, use the auto-ready function.

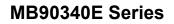

## 11.4.9 LIN-UART0/1/2/3 ■ Bit setting: ESCR:SCES = 0, ECCR:SCDE = 0

(T\_A = -40°C to +105°C, V\_{CC} = 5.0 V  $\pm$  10%, f\_{CP} \leq 24 MHz, V\_{SS} = 0 V)

| Baramatar                                                                       | Symbol             | Pin                           | Condition                                                                              | Va                                 | Unit                   |      |

|---------------------------------------------------------------------------------|--------------------|-------------------------------|----------------------------------------------------------------------------------------|------------------------------------|------------------------|------|

| Parameter                                                                       | Symbol             | Pin                           | Condition                                                                              | Min                                | Max                    | Unit |

| Serial clock cycle time                                                         | t <sub>SCYC</sub>  | SCK0 to SCK3                  |                                                                                        | 5 t <sub>CP</sub>                  | —                      | ns   |

| $SCK \downarrow \to SOT$ delay time                                             | t <sub>SLOVI</sub> | SCK0 to SCK3,<br>SOT0 to SOT3 | Internal shift clock                                                                   | -50                                | +50                    | ns   |

| Valid SIN $\rightarrow$ SCK $\uparrow$                                          | t <sub>IVSHI</sub> | SCK0 to SCK3,<br>SIN0 to SIN3 | mode output pins are $C_L = 80 \text{ pF} + 1 \text{ TTL}.$                            | t <sub>CP</sub> + 80               |                        | ns   |

| $SCK\!\uparrow\!\to\!ValidSINholdtime$                                          | t <sub>SHIXI</sub> | SCK0 to SCK3,<br>SIN0 to SIN3 |                                                                                        | 0                                  |                        | ns   |

| Serial clock "L" pulse width                                                    | t <sub>SHSL</sub>  | SCK0 to SCK3                  |                                                                                        | 3 t <sub>CP</sub> - t <sub>R</sub> |                        | ns   |

| Serial clock "H" pulse width                                                    | t <sub>SLSH</sub>  | SCK0 to SCK3                  |                                                                                        | t <sub>CP</sub> + 10               |                        | ns   |

| $SCK \downarrow \to SOT$ delay time                                             | t <sub>SLOVE</sub> | SCK0 to SCK3,<br>SOT0 to SOT3 |                                                                                        |                                    | 2 t <sub>CP</sub> + 60 | ns   |

| Valid SIN $\rightarrow$ SCK $\uparrow$                                          | t <sub>IVSHE</sub> | SCK0 to SCK3,<br>SIN0 to SIN3 | External shift clock<br>mode output pins are<br>$C_L = 80 \text{ pF} + 1 \text{ TTL}.$ | 30                                 |                        | ns   |

| $\text{SCK} \uparrow \rightarrow \text{Valid SIN hold time}$ $t_{\text{SHIXE}}$ |                    | SCK0, SCK1,<br>SIN0 to SIN3   |                                                                                        | t <sub>CP</sub> + 30               |                        | ns   |

| SCK fall time t <sub>F</sub>                                                    |                    | SCK0 to SCK3                  |                                                                                        |                                    | 10                     | ns   |

| SCK rise time                                                                   | t <sub>R</sub>     | SCK0 to SCK3                  |                                                                                        |                                    | 10                     | ns   |

Note: • AC characteristic in CLK synchronized mode.

C<sub>L</sub> is load capacity value of pins when testing.

t<sub>CP</sub> is internal operating clock cycle time (machine clock). Refer to " (1) Clock Timing".

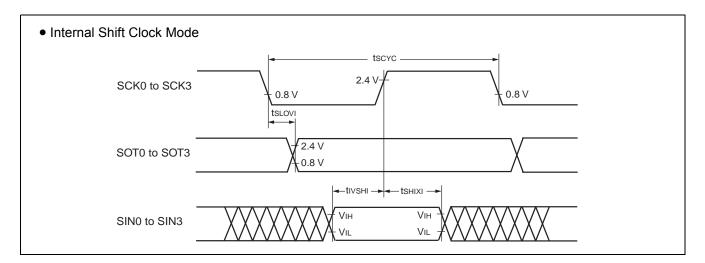

# 11.4.13 I<sup>2</sup>C Timing

| $(T_A = -40^{\circ}C \text{ to } +105^{\circ}C, V_{CC} = 5.0 \text{ V}$ | $/ \pm 10\%$ , V <sub>SS</sub> = 0.0 V) |

|-------------------------------------------------------------------------|-----------------------------------------|

|-------------------------------------------------------------------------|-----------------------------------------|

| Parameter                                                                          | Symbol             | Condition                             | Standard-mode |                    | Fast-mode* <sup>1</sup> |                   | Unit |

|------------------------------------------------------------------------------------|--------------------|---------------------------------------|---------------|--------------------|-------------------------|-------------------|------|

| Parameter                                                                          | Symbol             | Condition                             | Min           | Max                | Min                     | Max               | Unit |

| SCL clock frequency                                                                | f <sub>SCL</sub>   |                                       | 0             | 100                | 0                       | 400               | kHz  |

| Hold time (repeated) START condition SDA $\downarrow \rightarrow$ SCL $\downarrow$ | t <sub>HDSTA</sub> |                                       | 4.0           |                    | 0.6                     |                   | μs   |

| "L" width of the SCL clock                                                         | t <sub>LOW</sub>   |                                       | 4.7           | —                  | 1.3                     | —                 | μs   |

| "H" width of the SCL clock                                                         | t <sub>HIGH</sub>  |                                       | 4.0           | —                  | 0.6                     | —                 | μs   |

| Set-up time (repeated) START condition SCL $\uparrow \rightarrow$ SDA $\downarrow$ | t <sub>SUSTA</sub> | $R = 1.7 k\Omega$<br>$C = 50 pF^{*2}$ | 4.7           |                    | 0.6                     |                   | μs   |

| Data hold time SCL $\downarrow \rightarrow$ SDA $\downarrow \uparrow$              | t <sub>HDDAT</sub> | $C = 50 \text{ pc}^{-2}$              | 0             | 3.45* <sup>3</sup> | 0                       | 0.9* <sup>4</sup> | μs   |

| Data set-up time SDA $\downarrow \uparrow \rightarrow$ SCL $\uparrow$              | t <sub>SUDAT</sub> |                                       | 250           |                    | 100                     |                   | ns   |

| Set-up time for STOP condition SCL $\uparrow \rightarrow$ SDA $\uparrow$           | t <sub>susтo</sub> |                                       | 4.0           |                    | 0.6                     |                   | μs   |

| Bus free time between a STOP and START condition                                   | t <sub>BUS</sub>   |                                       | 4.7           |                    | 1.3                     | —                 | μs   |

\*1:For use at over 100 kHz, set the machine clock to at least 6 MHz.

\*2:R,C: Pull-up resistor and load capacitor of the SCL and SDA lines.

\*3:The maximum  $t_{HDDAT}$  meets the requirement that it does not extend the "L" width ( $t_{LOW}$ ) of the SCL signal.

\*4:A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement  $t_{SUDAT} \ge 250$  ns must then be met.

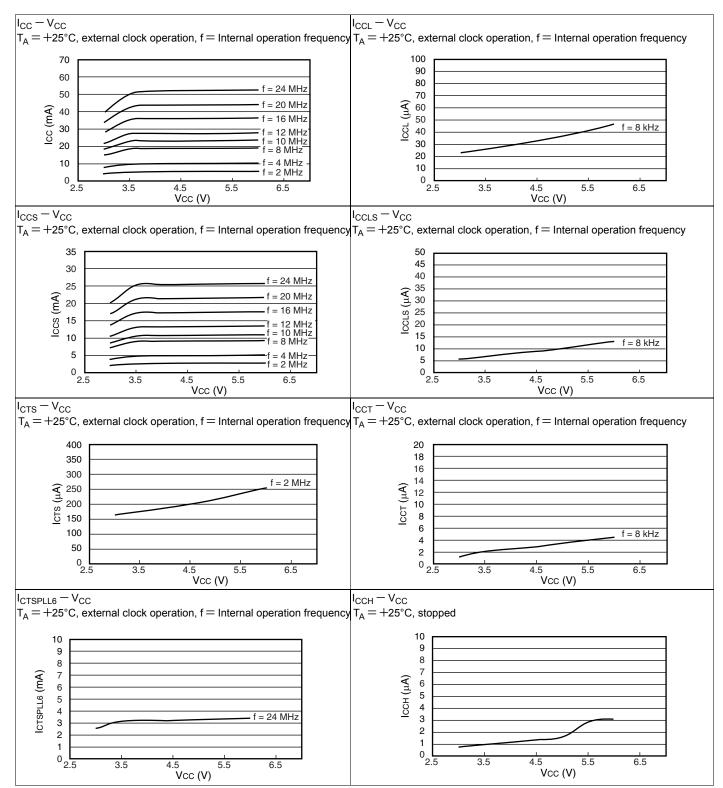

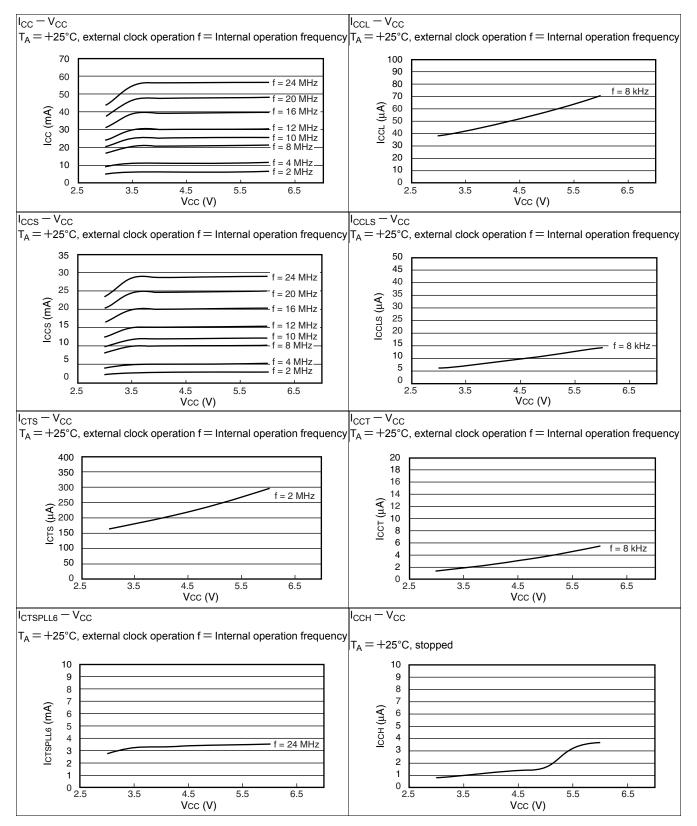

# **12. Example Characteristics**

### ■ MB90F349E, MB90F349ES, MB90F349CE, MB90F349CES

## Sales, Solutions, and Legal Information

## Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |  |  |  |  |

|-------------------------------------------------------|------------------------|--|--|--|--|

| Automotive                                            | cypress.com/automotive |  |  |  |  |

| Clocks & Buffers                                      | cypress.com/clocks     |  |  |  |  |

| Interface                                             | cypress.com/interface  |  |  |  |  |

| Lighting & Power Control                              | cypress.com/powerpsoc  |  |  |  |  |

| Memory                                                | cypress.com/memory     |  |  |  |  |

| PSoC                                                  | cypress.com/psoc       |  |  |  |  |

| Touch Sensing                                         | cypress.com/touch      |  |  |  |  |

| USB Controllers                                       | cypress.com/usb        |  |  |  |  |

| Wireless/RF                                           | cypress.com/wireless   |  |  |  |  |

## PSoC<sup>®</sup> Solutions

cypress.com/psoc PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Community | Forums | Blogs | Video | Training

Technical Support cypress.com/support

© Cypress Semiconductor Corporation, 2006-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.