Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                             |

|---------------------------------|-----------------------------------------------------------------------------|

| Product Status                  | Active                                                                      |

| Core Processor                  | ARM926EJ-S                                                                  |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                              |

| Speed                           | 180MHz                                                                      |

| Co-Processors/DSP               | -                                                                           |

| RAM Controllers                 | SDRAM, SRAM                                                                 |

| Graphics Acceleration           | No                                                                          |

| Display & Interface Controllers | LCD, Touchscreen                                                            |

| Ethernet                        | 10/100Mbps                                                                  |

| SATA                            | -                                                                           |

| JSB                             | USB 2.0 (3)                                                                 |

| oltage - I/O                    | 1.8V, 2.5V, 3.3V                                                            |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                           |

| ecurity Features                | -                                                                           |

| ackage / Case                   | 208-BFQFP                                                                   |

| Supplier Device Package         | 208-PQFP (28x28)                                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/at91sam9xe512b-qu |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 9.3 Peripheral Signals Multiplexing on I/O Lines

The SAM9XE devices feature three PIO controllers (PIOA, PIOB, PIOC) which multiplex the I/O lines of the peripheral set.

Each PIO Controller controls up to 32 lines. Each line can be assigned to one of two peripheral functions, A or B. The multiplexing tables in the following sections define how the I/O lines of peripherals A and B are multiplexed on the PIO Controllers. The two columns "Function" and "Comments" have been inserted in this table for the user's own comments; they may be used to track how pins are defined in an application.

Note that some peripheral functions which are output only, might be duplicated within both tables.

The column "Reset State" indicates whether the PIO Line resets in I/O mode or in peripheral mode. If I/O is mentioned, the PIO Line resets in input with the pull-up enabled, so that the device is maintained in a static state as soon as the reset is released. As a result, the bit corresponding to the PIO Line in the register PIO\_PSR (Peripheral Status Register) resets low.

If a signal name is mentioned in the "Reset State" column, the PIO Line is assigned to this function and the corresponding bit in PIO\_PSR resets high. This is the case of pins controlling memories, in particular the address lines, which require the pin to be driven as soon as the reset is released. Note that the pull-up resistor is also enabled in this case.

### 10.4.1 CP15 Registers Access

CP15 registers can only be accessed in privileged mode by:

- MCR (Move to Coprocessor from ARM Register) instruction is used to write an ARM register to CP15.

- MRC (Move to ARM Register from Coprocessor) instruction is used to read the value of CP15 to an ARM register.

Other instructions like CDP, LDC, STC can cause an undefined instruction exception.

The assembler code for these instructions is:

MCR/MRC{cond} p15, opcode\_1, Rd, CRn, CRm, opcode\_2.

The MCR, MRC instructions bit pattern is shown below:

| 31 | 30       | 29 | 28 | 27  | 26 | 25 | 24 |

|----|----------|----|----|-----|----|----|----|

|    | cond     |    |    | 1   | 1  | 1  | 0  |

| 23 | 22       | 21 | 20 | 19  | 18 | 17 | 16 |

|    | opcode_1 |    | L  | CRn |    |    |    |

| 15 | 14       | 13 | 12 | 11  | 10 | 9  | 8  |

|    | R        | d  |    | 1   | 1  | 1  | 1  |

| 7  | 6        | 5  | 4  | 3   | 2  | 1  | 0  |

|    | opcode_2 |    | 1  | CRm |    |    |    |

#### • CRm[3:0]: Specified Coprocessor Action

Determines specific coprocessor action. Its value is dependent on the CP15 register used. For details, refer to CP15 specific register behavior.

#### opcode\_2[7:5]

Determines specific coprocessor operation code. By default, set to 0.

### • Rd[15:12]: ARM Register

Defines the ARM register whose value is transferred to the coprocessor. If R15 is chosen, the result is unpredictable.

#### CRn[19:16]: Coprocessor Register

Determines the destination coprocessor register.

#### • L: Instruction Bit

0: MCR instruction

1: MRC instruction

### • opcode\_1[23:20]: Coprocessor Code

Defines the coprocessor specific code. Value is c15 for CP15.

## • cond [31:28]: Condition

For more details, see Chapter 2 in ARM926EJ-S TRM.

Table 13-3. Command Bit Coding

| DATA[15:0] | Symbol | Command Executed                    |

|------------|--------|-------------------------------------|

| 0x0011     | READ   | Read Flash                          |

| 0x0012     | WP     | Write Page Flash                    |

| 0x0022     | WPL    | Write Page and Lock Flash           |

| 0x0032     | EWP    | Erase Page and Write Page           |

| 0x0042     | EWPL   | Erase Page and Write Page then Lock |

| 0x0013     | EA     | Erase All                           |

| 0x0014     | SLB    | Set Lock Bit                        |

| 0x0024     | CLB    | Clear Lock Bit                      |

| 0x0015     | GLB    | Get Lock Bit                        |

| 0x0034     | SGPB   | Set General Purpose NVM bit         |

| 0x0044     | CGPB   | Clear General Purpose NVM bit       |

| 0x0025     | GGPB   | Get General Purpose NVM bit         |

| 0x0054     | SSE    | Set Security Bit                    |

| 0x0035     | GSE    | Get Security Bit                    |

| 0x001F     | WRAM   | Write Memory                        |

| 0x001E     | GVE    | Get Version                         |

### 13.2.3 Entering Programming Mode

The following algorithm puts the device in Parallel Programming Mode:

- Apply GND, VDDIO, VDDCORE and VDDPLL.

- Apply XIN clock within T<sub>POR RESET</sub> if an external clock is available.

- Wait for T<sub>POR\_RESET</sub>

- Start a read or write handshaking.

Note: After reset, the device is clocked by the internal RC oscillator. Before clearing RDY signal, if an external clock ( > 32 kHz) is connected to XIN, then the device switches on the external clock. Else, XIN input is not considered. A higher frequency on XIN speeds up the programmer handshake.

#### 13.2.4 Programmer Handshaking

An handshake is defined for read and write operations. When the device is ready to start a new operation (RDY signal set), the programmer starts the handshake by clearing the NCMD signal. The handshaking is achieved once NCMD signal is high and RDY is high.

### 13.2.4.1 Write Handshaking

For details on the write handshaking sequence, refer to Figure 13-2 and Table 13-4.

Table 13-18. Reset TAP Controller and Go to Select-DR-Scan

| TDI | TMS | TAP Controller State |

|-----|-----|----------------------|

| Х   | 1   |                      |

| Х   | 1   |                      |

| Х   | 1   |                      |

| Х   | 1   |                      |

| Х   | 1   | Test-Logic Reset     |

| X   | 0   | Run-Test/Idle        |

| Xt  | 1   | Select-DR-Scan       |

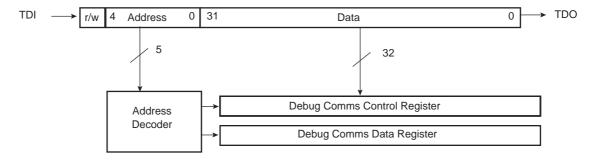

#### 13.3.3 Read/Write Handshake

The read/write handshake is done by carrying out read/write operations on two registers of the device that are accessible through the JTAG:

Debug Comms Control Register: DCCRDebug Comms Data Register: DCDR

Access to these registers is done through the TAP 38-bit DR register comprising a 32-bit data field, a 5-bit address field and a read/write bit. The data to be written is scanned into the 32-bit data field with the address of the register to the 5-bit address field and 1 to the read/write bit. A register is read by scanning its address into the address field and 0 into the read/write bit, going through the UPDATE-DR TAP state, then scanning out the data.

Refer to the ARM7TDMI reference manuel for more information on Comm channel operations.

Figure 13-5. TAP 8-bit DR Register

A read or write takes place when the TAP controller enters UPDATE-DR state. Refer to the IEEE 1149.1 for more details on JTAG operations.

- The address of the Debug Comms Control Register is 0x04.

- The address of the Debug Comms Data Register is 0x05.

The Debug Comms Control Register is read-only and allows synchronized handshaking between the processor and the debugger.

- Bit 1 (W): Denotes whether the programmer can read a data through the Debug Comms Data Register. If the device is busy W = 0, then the programmer must poll until W = 1.

- Bit 0 (R): Denotes whether the programmer can send data from the Debug Comms Data Register. If R

1, data previously placed there through the scan chain has not been collected by the device and so the programmer must wait.

The write handshake is done by polling the Debug Comms Control Register until the R bit is cleared. Once cleared, data can be written to the Debug Comms Data Register.

# 16.4.4 Periodic Interval Timer Image Register

Name: PIT\_PIIR

Address: 0xFFFFFD3C

Access: Read-only

|    | ,     |     |    |     |    |     |    |  |  |  |  |

|----|-------|-----|----|-----|----|-----|----|--|--|--|--|

| 31 | 30    | 29  | 28 | 27  | 26 | 25  | 24 |  |  |  |  |

|    | PICNT |     |    |     |    |     |    |  |  |  |  |

| 23 | 22    | 21  | 20 | 19  | 18 | 17  | 16 |  |  |  |  |

|    | PIC   | CNT |    |     | CF | PIV |    |  |  |  |  |

| 15 | 14    | 13  | 12 | 11  | 10 | 9   | 8  |  |  |  |  |

|    |       |     | CF | PIV |    |     |    |  |  |  |  |

| 7  | 6     | 5   | 4  | 3   | 2  | 1   | 0  |  |  |  |  |

|    |       |     | CF | PIV |    |     |    |  |  |  |  |

### • CPIV: Current Periodic Interval Value

Returns the current value of the periodic interval timer.

### • PICNT: Periodic Interval Counter

Returns the number of occurrences of periodic intervals since the last read of PIT\_PIVR.

- WDDIS: Watchdog Disable

- 0: Enables the Watchdog Timer.

- 1: Disables the Watchdog Timer.

# 19.3 Functional Description

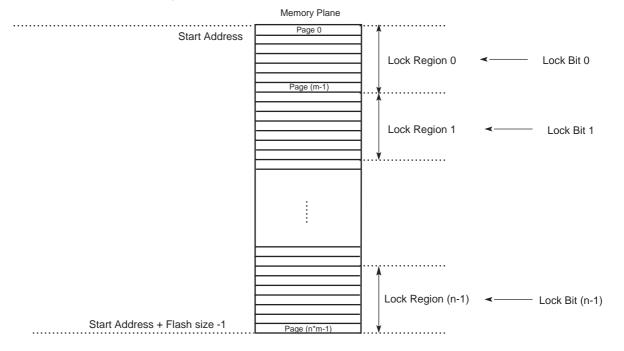

#### 19.3.1 Embedded Flash Organization

The embedded Flash interfaces directly with the 32-bit internal bus. The embedded Flash is composed of:

- One memory plane organized in several pages of the same size.

- Two 128-bit read buffers used for code read optimization.

- One 128-bit read buffer used for data read optimization.

- One write buffer that manages page programming. The write buffer size is equal to the page size. This buffer

is write-only and accessible all along the 1 MB address space, so that each word can be written to its final

address.

- Several lock bits used to protect write/erase operation on several pages (lock region). A lock bit is associated with a lock region composed of several pages in the memory plane.

- Several bits that may be set and cleared through the Enhanced Embedded Flash Controller (EEFC) interface, called General Purpose Non-volatile Memory bits (GPNVM bits).

The embedded Flash size, the page size, the lock regions organization and GPNVM bits definition are described in the product definition section. The Enhanced Embedded Flash Controller (EEFC) returns a descriptor of the Flash controlled after a get descriptor command issued by the application (see "Getting Embedded Flash Descriptor" on page 149).

Figure 19-1. Embedded Flash Organization

## 19.3.2 Read Operations

An optimized controller manages embedded Flash reads, thus increasing performance when the processor is running in ARM and Thumb mode by means of the 128-bit wide memory interface.

The Flash memory is accessible through 8-, 16- and 32-bit reads.

As the Flash block size is smaller than the address space reserved for the internal memory area, the embedded Flash wraps around the address space and appears to be repeated within it.

### 22.14.2 SMC Pulse Register

Name: SMC\_PULSE[0..7]

**Address:** 0xFFFFEC04 [0], 0xFFFFEC14 [1], 0xFFFFEC24 [2], 0xFFFFEC34 [3], 0xFFFFEC44 [4],

0xFFFFEC54 [5], 0xFFFFEC64 [6], 0xFFFFEC74 [7]

Access: Read/Write

| 31 | 30 | 29        | 28 | 27           | 26 | 25 | 24 |  |  |  |

|----|----|-----------|----|--------------|----|----|----|--|--|--|

| _  |    |           |    | NCS_RD_PULSE |    |    |    |  |  |  |

| •  | •  |           |    |              |    |    |    |  |  |  |

| 23 | 22 | 21        | 20 | 19           | 18 | 17 | 16 |  |  |  |

| _  |    | NRD_PULSE |    |              |    |    |    |  |  |  |

|    |    |           |    |              |    |    |    |  |  |  |

| 15 | 14 | 13        | 12 | 11           | 10 | 9  | 8  |  |  |  |

| _  |    |           |    | NCS_WR_PULSE |    |    |    |  |  |  |

|    |    |           |    |              |    |    |    |  |  |  |

| 7  | 6  | 5         | 4  | 3            | 2  | 1  | 0  |  |  |  |

| _  |    |           |    | NWE_PULSE    |    |    |    |  |  |  |

|    | •  |           |    |              |    |    |    |  |  |  |

### • NWE\_PULSE: NWE Pulse Length

The NWE signal pulse length is defined as:

NWE pulse length = (256\* NWE\_PULSE[6] + NWE\_PULSE[5:0]) clock cycles

The NWE pulse length must be at least 1 clock cycle.

#### NCS\_WR\_PULSE: NCS Pulse Length in WRITE Access

In write access, the NCS signal pulse length is defined as:

NCS pulse length = (256\* NCS\_WR\_PULSE[6] + NCS\_WR\_PULSE[5:0]) clock cycles

The NCS pulse length must be at least 1 clock cycle.

# • NRD\_PULSE: NRD Pulse Length

In standard read access, the NRD signal pulse length is defined in clock cycles as:

NRD pulse length = (256\* NRD\_PULSE[6] + NRD\_PULSE[5:0]) clock cycles

The NRD pulse length must be at least 1 clock cycle.

In page mode read access, the NRD PULSE parameter defines the duration of the subsequent accesses in the page.

### • NCS RD PULSE: NCS Pulse Length in READ Access

In standard read access, the NCS signal pulse length is defined as:

NCS pulse length = (256\* NCS RD PULSE[6] + NCS RD PULSE[5:0]) clock cycles

The NCS pulse length must be at least 1 clock cycle.

In page mode read access, the NCS\_RD\_PULSE parameter defines the duration of the first access to one page.

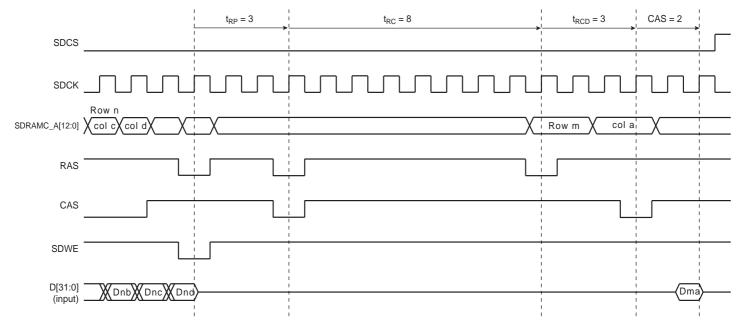

### 23.5.4 SDRAM Controller Refresh Cycles

An auto-refresh command is used to refresh the SDRAM device. Refresh addresses are generated internally by the SDRAM device and incremented after each auto-refresh automatically. The SDRAM Controller generates these auto-refresh commands periodically. An internal timer is loaded with the value in the register SDRAMC\_TR that indicates the number of clock cycles between refresh cycles.

A refresh error interrupt is generated when the previous auto-refresh command did not perform. It is acknowledged by reading the Interrupt Status Register (SDRAMC\_ISR).

When the SDRAM Controller initiates a refresh of the SDRAM device, internal memory accesses are not delayed. However, if the CPU tries to access the SDRAM, the slave indicates that the device is busy and the master is held by a wait signal. See Figure 23-5.

Figure 23-5. Refresh Cycle Followed by a Read Access

## 23.5.5 Power Management

Three low-power modes are available:

- Self-refresh Mode: The SDRAM executes its own Auto-refresh cycle without control of the SDRAM Controller. Current drained by the SDRAM is very low.

- Power-down Mode: Auto-refresh cycles are controlled by the SDRAM Controller. Between auto-refresh

cycles, the SDRAM is in power-down. Current drained in Power-down mode is higher than in Self-refresh

Mode.

- Deep Power-down Mode: (available only with mobile SDRAM) The SDRAM contents are lost, but the SDRAM does not drain any current.

The SDRAM Controller activates one low-power mode as soon as the SDRAM device is not selected. It is possible to delay the entry in self-refresh and power-down mode after the last access by programming a timeout value in the Low Power Register.

### • RECERR15: Recoverable Error in the page between the 3840th and the 4095th bytes

Fixed to 0 if TYPECORREC = 0.

0: No Errors Detected.

1: Errors Detected. If MUL\_ERROR is 0, a single correctable error was detected. Otherwise, multiple uncorrected errors were detected

### • ECCERR15: ECC Error in the page between the 3840th and the 4095th bytes

Fixed to 0 if TYPECORREC = 0

0: No Errors Detected.

1: A single bit error occurred in the ECC bytes.

Read ECC Parity 15 register, the error occurred at the location which contains a 1 in the least significant 24 bits.

### • MULERR15: Multiple Error in the page between the 3840th and the 4095th bytes

Fixed to 0 if TYPECORREC = 0.

0: No Multiple Errors Detected.

1: Multiple Errors Detected.

### 24.7.9 ECC Parity Register 8

Name: ECC\_PR8

Address: 0xFFFFE830

Access: Read-only

| 31 | 30         | 29 | 28 | 27 | 26 | 25        | 24 |  |

|----|------------|----|----|----|----|-----------|----|--|

| _  | _          | -  | _  | _  | _  | _         | -  |  |

| 23 | 22         | 21 | 20 | 19 | 18 | 17        | 16 |  |

| 0  | NPARITY8   |    |    |    |    |           |    |  |

| 15 | 14         | 13 | 12 | 11 | 10 | 9         | 8  |  |

|    | NPARITY8 0 |    |    |    |    | WORDADDR8 |    |  |

| 7  | 6          | 5  | 4  | 3  | 2  | 1         | 0  |  |

|    | WORDADDR8  |    |    |    |    | BITADDR8  |    |  |

Once the entire main area of a page is written with data, the register content must be stored at any free location of the spare area.

### BITADDR8: corrupted Bit Address in the page between the 2048th and the 2303rd bytes

During a page read, this value contains the corrupted bit offset where an error occurred, if a single error was detected. If multiple errors were detected, this value is meaningless.

# • WORDADDR8: corrupted Word Address in the page between the 2048th and the 2303rd bytes

During a page read, this value contains the word address (8-bit word) where an error occurred, if a single error was detected. If multiple errors were detected, this value is meaningless.

#### • NPARITY8:

Parity N.

### 24.7.14 ECC Parity Register 13

Name: ECC\_PR13 Address: 0xFFFFE844

Access: Read-only

| 31 | 30          | 29        | 28 | 27 | 26 | 25         | 24 |  |

|----|-------------|-----------|----|----|----|------------|----|--|

| -  | _           | -         | _  | _  | _  | _          | _  |  |

| 23 | 22          | 21        | 20 | 19 | 18 | 17         | 16 |  |

| 0  |             | NPARITY13 |    |    |    |            |    |  |

| 15 | 14          | 13        | 12 | 11 | 10 | 9          | 8  |  |

|    | NPARITY13 0 |           |    |    |    | WORDADDR13 | ,  |  |

| 7  | 6           | 5         | 4  | 3  | 2  | 1          | 0  |  |

|    | WORDADDR13  |           |    |    |    | BITADDR13  |    |  |

Once the entire main area of a page is written with data, the register content must be stored at any free location of the spare area.

#### . BITADDR13: corrupted Bit Address in the page between the 3328th and the 3583rd bytes

During a page read, this value contains the corrupted bit offset where an error occurred, if a single error was detected. If multiple errors were detected, this value is meaningless.

### • WORDADDR13: corrupted Word Address in the page between the 3328th and the 3583rd bytes

During a page read, this value contains the word address (8-bit word) where an error occurred, if a single error was detected. If multiple errors were detected, this value is meaningless.

#### • NPARITY13:

Parity N

# 33.7.11 USART Transmitter Timeguard Register

Name: US\_TTGR

**Address:** 0xFFFB0028 (0), 0xFFFB4028 (1), 0xFFFB8028 (2), 0xFFFD0028 (3), 0xFFFD4028 (4)

Access: Read/Write

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|----|----|----|----|----|----|----|----|

| _  | _  | -  | _  | _  | _  | 1  | _  |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| _  | _  | -  | _  | _  |    | ı  | _  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| _  | _  | 1  | _  | _  | 1  | I  | _  |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    |    |    | Т  | G  |    |    |    |

# • TG: Timeguard Value

0: The Transmitter Timeguard is disabled.

1–255: The Transmitter timeguard is enabled and the timeguard delay is TG x Bit Period.

# 35. Timer Counter (TC)

### 35.1 Description

The Timer Counter (TC) includes three identical 16-bit Timer Counter channels.

Each channel can be independently programmed to perform a wide range of functions including frequency measurement, event counting, interval measurement, pulse generation, delay timing and pulse width modulation.

Each channel has three external clock inputs, five internal clock inputs and two multi-purpose input/output signals which can be configured by the user. Each channel drives an internal interrupt signal which can be programmed to generate processor interrupts.

The Timer Counter block has two global registers which act upon all three TC channels.

The Block Control Register allows the three channels to be started simultaneously with the same instruction.

The Block Mode Register defines the external clock inputs for each channel, allowing them to be chained.

Table 35-1 gives the assignment of the device Timer Counter clock inputs common to Timer Counter 0 to 2.

Table 35-1. Timer Counter Clock Assignment

| Name         | Definition |

|--------------|------------|

| TIMER_CLOCK1 | MCK/2      |

| TIMER_CLOCK2 | MCK/8      |

| TIMER_CLOCK3 | MCK/32     |

| TIMER_CLOCK4 | MCK/128    |

| TIMER_CLOCK5 | SLCK       |

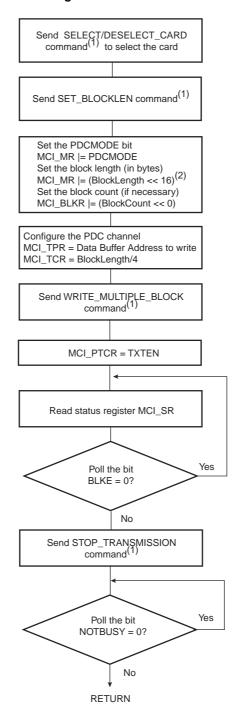

The following flowchart, (Figure 36-12) shows how to manage a multiple write block transfer with the PDC. Polling or interrupt method can be used to wait for the end of write according to the contents of the Interrupt Mask Register (MCI\_IMR).

Figure 36-12. Multiple Write Functional Flow Diagram

Notes: 1. It is assumed that this command has been correctly sent (see Figure 36-9).

2. This field is also accessible in the MCI Block Register (MCI\_BLKR).

### 36.9.11 MCI Status Register

Name: MCI\_SR

Address: 0xFFFA8040

Access: Read-only

| 31     | 30     | 29      | 28   | 27    | 26    | 25       | 24       |

|--------|--------|---------|------|-------|-------|----------|----------|

| UNRE   | OVRE   | _       |      | _     |       | -        | _        |

| 23     | 22     | 21      | 20   | 19    | 18    | 17       | 16       |

| _      | DTOE   | DCRCE   | RTOE | RENDE | RCRCE | RDIRE    | RINDE    |

| 15     | 14     | 13      | 12   | 11    | 10    | 9        | 8        |

| TXBUFE | RXBUFF | _       | ı    | ı     | ı     | SDIOIRQB | SDIOIRQA |

| 7      | 6      | 5       | 4    | 3     | 2     | 1        | 0        |

| ENDTX  | ENDRX  | NOTBUSY | DTIP | BLKE  | TXRDY | RXRDY    | CMDRDY   |

### • CMDRDY: Command Ready

0: A command is in progress.

1: The last command has been sent. Cleared when writing in the MCI\_CMDR.

#### RXRDY: Receiver Ready

0: Data has not yet been received since the last read of MCI\_RDR.

1: Data has been received since the last read of MCI\_RDR.

### • TXRDY: Transmit Ready

0: The last data written in MCI\_TDR has not yet been transferred in the Shift Register.

1: The last data written in MCI\_TDR has been transferred in the Shift Register.

#### • BLKE: Data Block Ended

This flag must be used only for Write Operations.

0: A data block transfer is not yet finished. Cleared when reading the MCI\_SR.

1: A data block transfer has ended, including the CRC16 Status transmission.

In PDC mode (PDCMODE=1), the flag is set when the CRC Status of the last block has been transmitted (TXBUFE already set).

Otherwise (PDCMODE=0), the flag is set for each transmitted CRC Status.

Refer to the MMC or SD Specification for more details concerning the CRC Status.

#### DTIP: Data Transfer in Progress

0: No data transfer in progress.

1: The current data transfer is still in progress, including CRC16 calculation. Cleared at the end of the CRC16 calculation.

# 37. Ethernet MAC 10/100 (EMAC)

### 37.1 Description

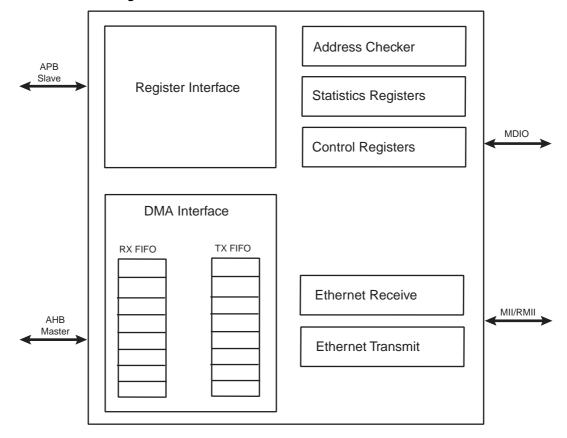

The EMAC module implements a 10/100 Ethernet MAC compatible with the IEEE 802.3 standard using an address checker, statistics and control registers, receive and transmit blocks, and a DMA interface.

The address checker recognizes four specific 48-bit addresses and contains a 64-bit hash register for matching multicast and unicast addresses. It can recognize the broadcast address of all ones, copy all frames, and act on an external address match signal.

The statistics register block contains registers for counting various types of event associated with transmit and receive operations. These registers, along with the status words stored in the receive buffer list, enable software to generate network management statistics compatible with IEEE 802.3.

### 37.2 Block Diagram

Figure 37-1. EMAC Block Diagram

# 37.5.13 Pause Time Register

| Name:<br>Address: | EMAC_PTF<br>0xFFFC403 |            |          |           |    |    |    |  |  |  |  |

|-------------------|-----------------------|------------|----------|-----------|----|----|----|--|--|--|--|

| Access:           | Read/Write            | Read/Write |          |           |    |    |    |  |  |  |  |

| 31                | 30                    | 29         | 28       | 27        | 26 | 25 | 24 |  |  |  |  |

| _                 | _                     | -          | _        | _         | _  | _  | _  |  |  |  |  |

| 23                | 22                    | 21         | 20       | 19        | 18 | 17 | 16 |  |  |  |  |

| _                 | _                     | _          | _        | _         | -  | _  | _  |  |  |  |  |

| 15                | 14                    | 13         | 12<br>PT | 11<br>IME | 10 | 9  | 8  |  |  |  |  |

| 7                 | 6                     | 5          | 4<br>DT. | 3<br>IME  | 2  | 1  | 0  |  |  |  |  |

# • PTIME: Pause Time

Stores the current value of the pause time register which is decremented every 512 bit times.

# 38.6.4 UDP Interrupt Enable Register

Name: UDP\_IER

Address: 0xFFFA4010

Access: Write-only

| Access. | Wille Offig |        |        |        |        |        |        |

|---------|-------------|--------|--------|--------|--------|--------|--------|

| 31      | 30          | 29     | 28     | 27     | 26     | 25     | 24     |

| _       | -           | _      | _      | _      | -      | _      | -      |

| 23      | 22          | 21     | 20     | 19     | 18     | 17     | 16     |

| _       | -           | _      | _      | _      | -      | -      | -      |

| 15      | 14          | 13     | 12     | 11     | 10     | 9      | 8      |

| _       | _           | WAKEUP | _      | SOFINT | EXTRSM | RXRSM  | RXSUSP |

| 7       | 6           | 5      | 4      | 3      | 2      | 1      | 0      |

|         |             | EP5INT | EP4INT | EP3INT | EP2INT | EP1INT | EP0INT |

• EP0INT: Enable Endpoint 0 Interrupt

• EP1INT: Enable Endpoint 1 Interrupt

• EP2INT: Enable Endpoint 2Interrupt

• EP3INT: Enable Endpoint 3 Interrupt

• EP4INT: Enable Endpoint 4 Interrupt

• EP5INT: Enable Endpoint 5 Interrupt

0: No effect.

1: Enables corresponding Endpoint Interrupt.

• RXSUSP: Enable UDP Suspend Interrupt

0: No effect.

1: Enables UDP Suspend Interrupt.

• RXRSM: Enable UDP Resume Interrupt

0: No effect.

1: Enables UDP Resume Interrupt.

• EXTRSM: Enable External Resume Interrupt

0: No effect.

1: Enables External Resume Interrupt.

• SOFINT: Enable Start Of Frame Interrupt

0: No effect.

1: Enables Start Of Frame Interrupt.

# 42.6.5 Crystal Characteristics

Table 42-16. Crystal Characteristics

| Symbol             | Parameter                     | Conditions           | Min | Тур | Max | Unit |

|--------------------|-------------------------------|----------------------|-----|-----|-----|------|

| ESR                | Equivalent Series Resistor Rs | Fundamental @ 3 MHz  |     |     | 200 |      |

|                    |                               | Fundamental @ 8 MHz  |     |     | 100 | Ω    |

|                    |                               | Fundamental @ 16 MHz |     |     | 80  |      |

|                    |                               | Fundamental @ 20 MHz |     |     | 50  |      |

| C <sub>m</sub>     | Motional Capacitance          |                      |     |     | 8   | fF   |

| C <sub>SHUNT</sub> | Shunt Capacitance             |                      |     |     | 7   | pF   |

### 42.6.6 PLL Characteristics

Table 42-17. PLLA Characteristics<sup>(1)</sup>

| Symbol           | Parameter           | Conditions               | Min | Тур | Max | Unit |

|------------------|---------------------|--------------------------|-----|-----|-----|------|

| f <sub>OUT</sub> | Output Frequency    | Field CKGR_PLL.OUTA = 00 | 80  |     | 160 | MHz  |

|                  |                     | Field CKGR_PLL.OUTA = 10 | 150 |     | 220 | MHz  |

| f <sub>IN</sub>  | Input Frequency     |                          | 1   |     | 32  | MHz  |

| I <sub>PLL</sub> | Current Consumption | Active mode @ 240 MHz    |     | 3.6 | 4.5 | mA   |

|                  |                     | Standby mode             |     |     | 1   | μA   |

Note: 1. Startup time depends on PLL RC filter. A calculation tool is provided by Atmel.

Table 42-18. PLLB Characteristics

| Symbol             | Parameter           | Conditions               | Min | Тур | Max              | Unit |

|--------------------|---------------------|--------------------------|-----|-----|------------------|------|

| f <sub>OUT</sub>   | Output Frequency    | Field CKGR_PLL.OUTA = 01 | 70  |     | 130              | MHz  |

| f <sub>IN</sub>    | Input Frequency     |                          | 1   |     | 5 <sup>(1)</sup> | MHz  |

| I <sub>PLL</sub>   | Current Consumption | Active mode @ 130 MHz    |     |     | 1.2              | mA   |

|                    |                     | Standby mode             |     |     | 1                | μΑ   |

| t <sub>START</sub> | Startup TIme        |                          |     |     | 1                | ms   |

Note: 1. The embedded filter is optimized for a 2 MHz input frequency. DIVB must be selected to meet this requirement.