Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | F <sup>2</sup> MC-8FX                                                          |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 16MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                             |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 20KB (20K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                    |

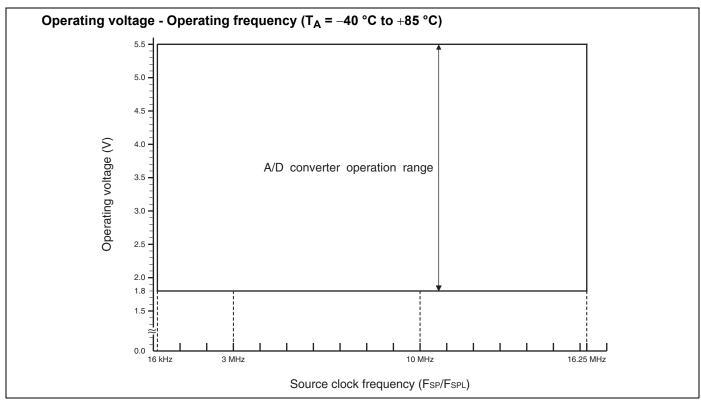

| Data Converters            | A/D 6x8/12b                                                                    |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 24-TSSOP (0.173", 4.40mm Width)                                                |

| Supplier Device Package    | 24-TSSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f654epft-g-sne2 |

#### Power-on reset

A power-on reset is generated when the power is switched on.

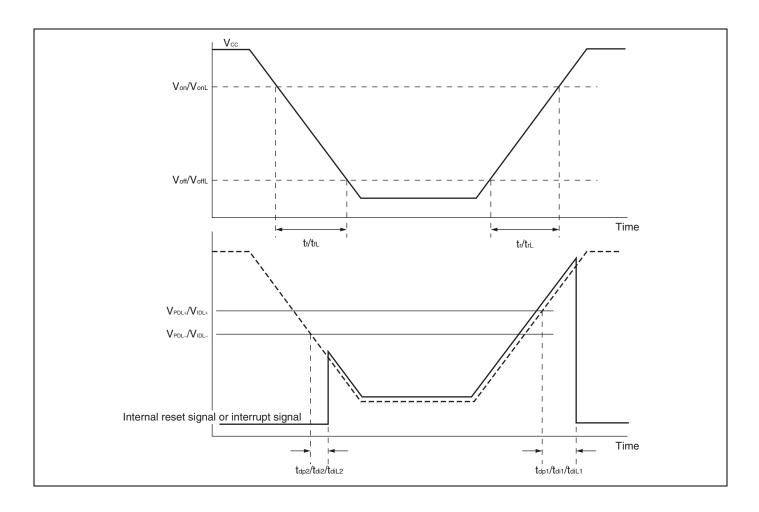

Low-voltage detection reset circuit and low-voltage detection interrupt circuit (only available on MB95F652E/F653E/F654E/F656E)

Built-in low-voltage detection function

### **Clock supervisor counter**

Built-in clock supervisor counter

#### **Dual operation Flash memory**

The program/erase operation and the read operation can be executed in different banks (upper bank/lower bank) simultaneously.

#### Flash memory security function

Protects the content of the Flash memory.

### **Contents**

| Product Line-up                     | 4  |

|-------------------------------------|----|

| Packages and Corresponding Products | 6  |

| Differences among Products and      |    |

| Notes on Product Selection          | 7  |

| Pin Assignment                      | 8  |

| Pin Functions                       |    |

| I/O Circuit Type                    | 12 |

| Handling Precautions                | 15 |

| Precautions for Product Design      |    |

| Precautions for Package Mounting    | 16 |

| Precautions for Use Environment     |    |

| Notes On Device Handling            | 18 |

| Pin Connection                      |    |

| Block Diagram                       | 20 |

| CPU Core                            |    |

| Memory Space                        |    |

| Areas for Specific Applications     | 24 |

| I/O Map                             |    |

| I/O Ports                                  | 29 |

|--------------------------------------------|----|

| Port 0                                     | 30 |

| Port 1                                     |    |

| Port 6                                     | 42 |

| Port F                                     |    |

| Port G                                     |    |

| Interrupt Source Table                     |    |

| Pin States in each Mode                    |    |

| Electrical Characteristics                 |    |

| Absolute Maximum Ratings                   |    |

| Recommended Operating Conditions           |    |

| DC Characteristics                         |    |

| AC Characteristics                         |    |

| A/D Converter                              |    |

| Flash Memory Program/Erase Characteristics |    |

| Sample Characteristics                     |    |

| Mask Options                               |    |

| Ordering Information                       |    |

| Package Dimension                          |    |

| Major Changes                              |    |

| Document History                           |    |

| Type | Circuit                                                                                                             | Remarks                                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| D    | Pull-up control  P-ch  Digital output  N-ch  Standby control  Hysteresis input                                      | <ul><li>CMOS output</li><li>Hysteresis input</li><li>Pull-up control</li><li>High current output</li></ul> |

| E    | Pull-up control  P-ch  Digital output  Digital output  Analog input  A/D control  Standby control  Hysteresis input | <ul><li>CMOS output</li><li>Hysteresis input</li><li>Pull-up control</li><li>Analog input</li></ul>        |

| F    | Pull-up control  P-ch  Digital output  Digital output  Analog input  A/D control Standby control CMOS input         | CMOS output CMOS input Pull-up control Analog input                                                        |

| н    | Standby control  Hysteresis input  N-ch                                                                             | N-ch open drain output     Hysteresis input                                                                |

| I    | Digital output  N-ch  Standby control  CMOS input                                                                   | N-ch open drain output CMOS input  Continued                                                               |

#### Static Electricity

Because semiconductor devices are particularly susceptible to damage by static electricity, you must take the following precautions:

- 1. Maintain relative humidity in the working environment between 40% and 70%. Use of an apparatus for ion generation may be needed to remove electricity.

- 2. Electrically ground all conveyors, solder vessels, soldering irons and peripheral equipment.

- Eliminate static body electricity by the use of rings or bracelets connected to ground through high resistance (on the level of 1 MΩ).

Wearing of conductive clothing and shoes, use of conductive floor mats and other measures to minimize shock loads is recommended.

- 4. Ground all fixtures and instruments, or protect with anti-static measures.

- 5. Avoid the use of styrofoam or other highly static-prone materials for storage of completed board assemblies.

#### 7.3 Precautions for Use Environment

Reliability of semiconductor devices depends on ambient temperature and other conditions as described above.

For reliable performance, do the following:

1. Humidity

Prolonged use in high humidity can lead to leakage in devices as well as printed circuit boards. If high humidity levels are anticipated, consider anti-humidity processing.

2. Discharge of Static Electricity

When high-voltage charges exist close to semiconductor devices, discharges can cause abnormal operation. In such cases, use anti-static measures or processing to prevent discharges.

3. Corrosive Gases, Dust, or Oil

Exposure to corrosive gases or contact with dust or oil may lead to chemical reactions that will adversely affect the device. If you use devices in such conditions, consider ways to prevent such exposure or to protect the devices.

4. Radiation, Including Cosmic Radiation

Most devices are not designed for environments involving exposure to radiation or cosmic radiation. Users should provide shielding as appropriate.

5. Smoke, Flame

CAUTION: Plastic molded devices are flammable, and therefore should not be used near combustible substances. If devices begin to smoke or burn, there is danger of the release of toxic gases.

Customers considering the use of Cypress products in other special environmental conditions should consult with sales representatives.

Document Number: 002-04696 Rev. \*B

# 14. I/O Map

| Address                | Register abbreviation | Register name                                         | R/W | Initial value |

|------------------------|-----------------------|-------------------------------------------------------|-----|---------------|

| 0x0000                 | PDR0                  | Port 0 data register                                  | R/W | 0b00000000    |

| 0x0001                 | DDR0                  | Port 0 direction register                             | R/W | 0b00000000    |

| 0x0002                 | PDR1                  | Port 1 data register                                  | R/W | 0b00000000    |

| 0x0003                 | DDR1                  | Port 1 direction register                             | R/W | 0b00000000    |

| 0x0004                 | _                     | (Disabled)                                            | _   | _             |

| 0x0005                 | WATR                  | Oscillation stabilization wait time setting register  | R/W | 0b11111111    |

| 0x0006                 | PLLC                  | PLL control register                                  | R/W | 0b000X0000    |

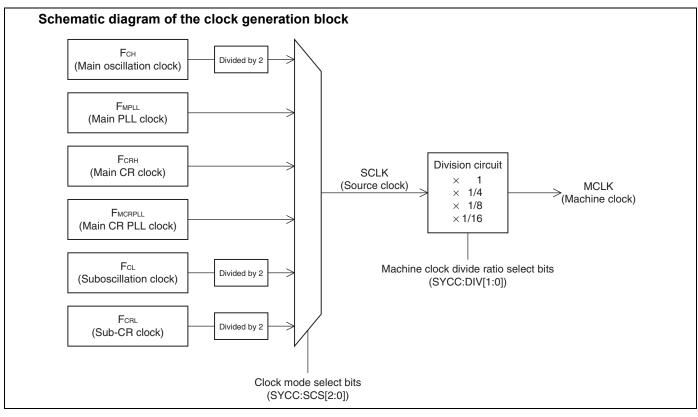

| 0x0007                 | SYCC                  | System clock control register                         | R/W | 0bXXX11011    |

| 0x0008                 | STBC                  | Standby control register                              | R/W | 0b00000000    |

| 0x0009                 | RSRR                  | Reset source register                                 | R/W | 0b000XXXXX    |

| 0x000A                 | TBTC                  | Time-base timer control register                      | R/W | 0b00000000    |

| 0x000B                 | WPCR                  | Watch prescaler control register                      | R/W | 0b00000000    |

| 0x000C                 | WDTC                  | Watchdog timer control register                       | R/W | 0b00XX0000    |

| 0x000D                 | SYCC2                 | System clock control register 2                       | R/W | 0bXXXX0011    |

| 0x000E<br>to<br>0x0015 | _                     | (Disabled)                                            | _   | _             |

| 0x0016                 | PDR6                  | Port 6 data register                                  | R/W | 0b00000000    |

| 0x0017                 | DDR6                  | Port 6 direction register                             | R/W | 0b00000000    |

| 0x0018<br>to<br>0x0027 | _                     | (Disabled)                                            | _   | _             |

| 0x0028                 | PDRF                  | Port F data register                                  | R/W | 0b00000000    |

| 0x0029                 | DDRF                  | Port F direction register                             | R/W | 0b00000000    |

| 0x002A                 | PDRG                  | Port G data register                                  | R/W | 0b00000000    |

| 0x002B                 | DDRG                  | Port G direction register                             | R/W | 0b00000000    |

| 0x002C                 | PUL0                  | Port 0 pull-up register                               | R/W | 0b00000000    |

| 0x002D<br>to<br>0x0032 | _                     | (Disabled)                                            |     | _             |

| 0x0033                 | PUL6                  | Port 6 pull-up register                               | R/W | 0b00000000    |

| 0x0034                 | _                     | (Disabled)                                            | _   | _             |

| 0x0035                 | PULG                  | Port G pull-up register                               | R/W | 0b00000000    |

| 0x0036                 | T01CR1                | 8/16-bit composite timer 01 status control register 1 | R/W | 0b00000000    |

| 0x0037                 | T00CR1                | 8/16-bit composite timer 00 status control register 1 | R/W | 0b00000000    |

| 0x0038                 | T11CR1                | 8/16-bit composite timer 11 status control register 1 | R/W | 0b00000000    |

| 0x0039                 | T10CR1                | 8/16-bit composite timer 10 status control register 1 | R/W | 0b00000000    |

| 0x003A<br>to<br>0x0048 | _                     | (Disabled)                                            | _   | _             |

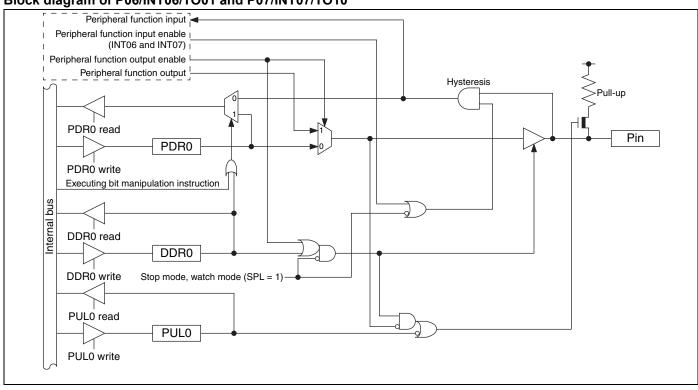

### P06/INT06/TO01 pin

This pin has the following peripheral functions:

- External interrupt input pin (INT06)

- 8/16-bit composite timer ch. 0 output pin (TO01)

## P07/INT07/TO10 pin

This pin has the following peripheral functions:

- External interrupt input pin (INT07)

- 8/16-bit composite timer ch. 1 output pin (TO10)

## Block diagram of P06/INT06/TO01 and P07/INT07/TO10

### 15.1.3 Port 0 registers

## Port 0 register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                              |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|------------------------------------|--|--|--|--|

| PDR0                  | 0    | Pin state is "L" level. | PDR0 value is "0".                          | As output port, outputs "L" level. |  |  |  |  |

| PDRU                  | 1    | Pin state is "H" level. | PDR0 value is "1".                          | As output port, outputs "H" level. |  |  |  |  |

| DDR0                  | 0    |                         | Port input enabled                          |                                    |  |  |  |  |

| DDRU                  | 1    | Port output enabled     |                                             |                                    |  |  |  |  |

| PUL0                  | 0    |                         | Pull-up disabled                            |                                    |  |  |  |  |

| POLO                  | 1    | Pull-up enabled         |                                             |                                    |  |  |  |  |

| AIDRL                 | 0    |                         | Analog input enabled                        |                                    |  |  |  |  |

| AIDRL                 | 1    | Port input enabled      |                                             |                                    |  |  |  |  |

## Correspondence between registers and pins for port 0

|          | Correspondence between related register bits and pins |      |      |      |      |      |      |      |      |      |

|----------|-------------------------------------------------------|------|------|------|------|------|------|------|------|------|

| Pin name | P07                                                   | P06  | P05  | P04  | P03  | P02  | P01  | P00  |      |      |

| PDR0     |                                                       |      |      |      |      |      |      |      |      |      |

| DDR0     | bit7                                                  | bit7 | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

| PUL0     |                                                       |      | טונט | DIL4 | Dito | DILZ | DILI | bito |      |      |

| AIDRL    | -                                                     | -    |      |      |      |      |      |      |      |      |

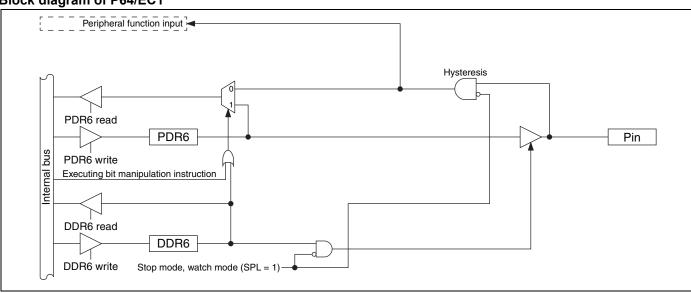

### P64/EC1 pin

This pin has the following peripheral function:

• 8/16-bit composite timer ch. 1 clock input pin (EC1)

## Block diagram of P64/EC1

## 16. Interrupt Source Table

| Interrupt source                        | Interrupt request | Vector tab | le address |          | evel setting<br>ister | Priority order of interrupt sources of the same level |

|-----------------------------------------|-------------------|------------|------------|----------|-----------------------|-------------------------------------------------------|

|                                         | number            | Upper      | Lower      | Register | Bit                   | (occurring simultaneously)                            |

| External interrupt ch. 4                | IRQ00             | 0xFFFA     | 0xFFFB     | ILR0     | L00 [1:0]             | High                                                  |

| External interrupt ch. 5                | IRQ01             | 0xFFF8     | 0xFFF9     | ILR0     | L01 [1:0]             | 1 🛕                                                   |

| External interrupt ch. 2                | IRQ02             | 0xFFF6     | 0xFFF7     | ILR0     | L02 [1:0]             | ]                                                     |

| External interrupt ch. 6                | IRQ02             | UXFFF0     | UXFFF1     | ILKU     | LUZ [1.0]             |                                                       |

| External interrupt ch. 3                | IDO03             | 0,45554    | 0xFFF5     | II D0    | 1.02 [4:0]            | 1                                                     |

| External interrupt ch. 7                | IRQ03             | 0xFFF4     | UXFFF5     | ILR0     | L03 [1:0]             |                                                       |

| Low-voltage detection interrupt circuit | IDO04             | ٥٠،٢٢٢٥    | ٥٠،٢٢٢٥    | II D4    | 1.04 [4.0]            |                                                       |

| UART/SIO ch. 0                          | IRQ04             | 0xFFF2     | 0xFFF3     | ILR1     | L04 [1:0]             |                                                       |

| 8/16-bit composite timer ch. 0 (lower)  | IRQ05             | 0xFFF0     | 0xFFF1     | ILR1     | L05 [1:0]             |                                                       |

| 8/16-bit composite timer ch. 0 (upper)  | IRQ06             | 0xFFEE     | 0xFFEF     | ILR1     | L06 [1:0]             |                                                       |

| LIN-UART (reception)                    | IRQ07             | 0xFFEC     | 0xFFED     | ILR1     | L07 [1:0]             |                                                       |

| LIN-UART (transmission)                 | IRQ08             | 0xFFEA     | 0xFFEB     | ILR2     | L08 [1:0]             | -                                                     |

| _                                       | IRQ09             | 0xFFE8     | 0xFFE9     | ILR2     | L09 [1:0]             |                                                       |

| I <sup>2</sup> C bus interface ch. 1    | IRQ10             | 0xFFE6     | 0xFFE7     | ILR2     | L10 [1:0]             | 1                                                     |

| _                                       | IRQ11             | 0xFFE4     | 0xFFE5     | ILR2     | L11 [1:0]             | 1                                                     |

| _                                       | IRQ12             | 0xFFE2     | 0xFFE3     | ILR3     | L12 [1:0]             | 1                                                     |

| _                                       | IRQ13             | 0xFFE0     | 0xFFE1     | ILR3     | L13 [1:0]             | 1                                                     |

| 8/16-bit composite timer ch. 1 (upper)  | IRQ14             | 0xFFDE     | 0xFFDF     | ILR3     | L14 [1:0]             | 1                                                     |

| _                                       | IRQ15             | 0xFFDC     | 0xFFDD     | ILR3     | L15 [1:0]             | 1                                                     |

| I <sup>2</sup> C bus interface ch. 0    | IRQ16             | 0xFFDA     | 0xFFDB     | ILR4     | L16 [1:0]             | 1                                                     |

| _                                       | IRQ17             | 0xFFD8     | 0xFFD9     | ILR4     | L17 [1:0]             | 1                                                     |

| 8/12-bit A/D converter                  | IRQ18             | 0xFFD6     | 0xFFD7     | ILR4     | L18 [1:0]             | -                                                     |

| Time-base timer                         | IRQ19             | 0xFFD4     | 0xFFD5     | ILR4     | L19 [1:0]             | 1                                                     |

| Watch prescaler                         | IRQ20             | 0xFFD2     | 0xFFD3     | ILR5     | L20 [1:0]             | 1                                                     |

| _                                       | IRQ21             | 0xFFD0     | 0xFFD1     | ILR5     | L21 [1:0]             | 1                                                     |

| 8/16-bit composite timer ch. 1 (lower)  | IRQ22             | 0xFFCE     | 0xFFCF     | ILR5     | L22 [1:0]             | 1                                                     |

| Flash memory                            | IRQ23             | 0xFFCC     | 0xFFCD     | ILR5     | L23 [1:0]             | Low                                                   |

## 17. Pin States in each Mode

| Din nome                                    | Normal                                                   | lormal Sleep made                                        |                                                                                         | mode                                                                     | Watch                                                                                   | On reset                                                                 |                                                                                      |

|---------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Pin name                                    | operation                                                | Sleep mode                                               | SPL=0                                                                                   | SPL=1                                                                    | SPL=0                                                                                   | SPL=1                                                                    | On reset                                                                             |

|                                             | Oscillation input                                        | Oscillation input                                        | Hi-Z                                                                                    | Hi-Z                                                                     | Hi-Z                                                                                    | Hi-Z                                                                     | _                                                                                    |

| PF0/X0                                      | I/O port* <sup>1</sup>                                   | I/O port* <sup>1</sup>                                   | - Previous state<br>kept<br>- Input<br>blocked*1, *2                                    | - Hi-Z<br>- Input<br>blocked* <sup>1, *2</sup>                           | - Previous state<br>kept<br>- Input<br>blocked*1, *2                                    | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.) |

|                                             | Oscillation input                                        | Oscillation input                                        | Hi-Z                                                                                    | Hi-Z                                                                     | Hi-Z                                                                                    | Hi-Z                                                                     | _                                                                                    |

| PF1/X1                                      | I/O port* <sup>1</sup>                                   | I/O port* <sup>1</sup>                                   | - Previous state<br>kept<br>- Input<br>blocked* <sup>1, *2</sup>                        | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Previous state<br>kept<br>- Input<br>blocked*1, *2                                    | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.) |

|                                             | Reset input                                              | Reset input                                              | Reset input                                                                             | Reset input                                                              | Reset input                                                                             | Reset input                                                              | Reset input*4                                                                        |

| PF2/RST                                     | I/O port* <sup>1</sup>                                   | I/O port* <sup>1</sup>                                   | - Previous state<br>kept<br>- Input<br>blocked* <sup>1, *2</sup>                        | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Previous state<br>kept<br>- Input<br>blocked* <sup>1, *2</sup>                        | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.) |

|                                             | Oscillation input                                        | Oscillation input                                        | Hi-Z                                                                                    | Hi-Z                                                                     | Hi-Z                                                                                    | Hi-Z                                                                     | _                                                                                    |

| PG1/X0A                                     | I/O port* <sup>1</sup>                                   | I/O port* <sup>1</sup>                                   | - Previous state<br>kept<br>- Input<br>blocked* <sup>1, *2</sup>                        | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Previous state<br>kept<br>- Input<br>blocked* <sup>1, *2</sup>                        | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.) |

|                                             | Oscillation input                                        | Oscillation input                                        | Hi-Z                                                                                    | Hi-Z                                                                     | Hi-Z                                                                                    | Hi-Z                                                                     | _                                                                                    |

| PG2/X1A                                     | I/O port* <sup>1</sup>                                   | I/O port* <sup>1</sup>                                   | - Previous state<br>kept<br>- Input<br>blocked* <sup>1, *2</sup>                        | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Previous state<br>kept<br>- Input<br>blocked*1, *2                                    | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.) |

| P00/AN00                                    |                                                          |                                                          |                                                                                         |                                                                          |                                                                                         |                                                                          |                                                                                      |

| P01/AN01                                    |                                                          |                                                          |                                                                                         |                                                                          |                                                                                         |                                                                          |                                                                                      |

| P02/INT02/<br>AN02/SCK                      |                                                          |                                                          |                                                                                         |                                                                          |                                                                                         |                                                                          |                                                                                      |

| P03/INT03/<br>AN03/SOT                      | I/O port/<br>peripheral<br>function I/O/<br>analog input | I/O port/<br>peripheral<br>function I/O/<br>analog input | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*<sup>2, *5</sup></li> </ul> | - Hi-Z* <sup>6</sup><br>- Input<br>blocked* <sup>2,</sup> * <sup>5</sup> | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*<sup>2, *5</sup></li> </ul> | - Hi-Z* <sup>6</sup><br>- Input<br>blocked* <sup>2,</sup> * <sup>5</sup> | - Hi-Z<br>- Input<br>blocked* <sup>2</sup>                                           |

| AN04/SIN/<br>EC0<br>P05/INT05/<br>AN05/TO00 |                                                          | 3                                                        | <del></del>                                                                             |                                                                          | <del>-</del>                                                                            |                                                                          |                                                                                      |

## 18.3 DC Characteristics

(V<sub>CC</sub> = 3.0 V±10%, V<sub>SS</sub> = 0.0 V,  $T_A$  = -40 °C to +85 °C)

|                                                        |                   |                                                                            |                                          | Value                 |     |                       |      |                                                |  |

|--------------------------------------------------------|-------------------|----------------------------------------------------------------------------|------------------------------------------|-----------------------|-----|-----------------------|------|------------------------------------------------|--|

| Parameter                                              | Symbol            | Pin name                                                                   | Condition                                | Min                   | Тур | Max                   | Unit | Remarks                                        |  |

|                                                        | V <sub>IHI1</sub> | P04, P16, P17                                                              | *1                                       | 0.7 V <sub>CC</sub>   | _   | V <sub>CC</sub> + 0.3 | V    | CMOS input level                               |  |

| "H" level input<br>voltage                             | V <sub>IHI2</sub> | P14, P15                                                                   | *1                                       | 0.7 V <sub>CC</sub>   | _   | V <sub>CC</sub> + 5.5 | V    | CMOS input level                               |  |

|                                                        | V <sub>IHS</sub>  | P00 to P03,<br>P05 to P07,<br>P12,<br>P62 to P64,<br>PF0, PF1,<br>PG1, PG2 | *1                                       | 0.8 V <sub>CC</sub>   | _   | V <sub>CC</sub> + 0.3 | V    | Hysteresis input                               |  |

|                                                        | $V_{IHM}$         | PF2                                                                        | _                                        | 0.8 V <sub>CC</sub>   | —   | $V_{CC} + 0.3$        | V    | Hysteresis input                               |  |

|                                                        | V <sub>ILI</sub>  | P04, P14 to P17                                                            | *1                                       | $V_{SS}-0.3$          | _   | 0.3 V <sub>CC</sub>   | V    | CMOS input level                               |  |

| "L" level input<br>voltage                             | V <sub>ILS</sub>  | P00 to P03,<br>P05 to P07,<br>P12,<br>P62 to P64,<br>PF0, PF1,<br>PG1, PG2 | *1                                       | V <sub>SS</sub> - 0.3 | _   | 0.2 V <sub>CC</sub>   | V    | Hysteresis input                               |  |

|                                                        | $V_{ILM}$         | PF2                                                                        | _                                        | V <sub>SS</sub> - 0.3 | _   | 0.2 V <sub>CC</sub>   | V    | Hysteresis input                               |  |

| Open-drain                                             | V <sub>D1</sub>   | P12, PF2                                                                   | _                                        | $V_{SS}-0.3$          | _   | V <sub>SS</sub> + 5.5 | V    |                                                |  |

| output application                                     | V <sub>D2</sub>   | P14, P15                                                                   | _                                        | V <sub>SS</sub> - 0.3 | _   | V <sub>SS</sub> + 5.5 | V    |                                                |  |

| voltage                                                | V <sub>D3</sub>   | P16, P17                                                                   | _                                        | V <sub>SS</sub> - 0.3 | _   | V <sub>SS</sub> + 5.5 | V    | In I <sup>2</sup> C mode                       |  |

| "H" level output                                       | V <sub>OH1</sub>  | Output pins other than P05 to P07, P12, P62, P63                           | $I_{OH} = -4 \text{ mA}^{*2}$            | V <sub>CC</sub> - 0.5 | _   | _                     | ٧    |                                                |  |

| voltage                                                | V <sub>OH2</sub>  | P05 to P07, P62,<br>P63                                                    | $I_{OH} = -8 \text{ mA}^{*3}$            | V <sub>CC</sub> - 0.5 | _   | _                     | V    |                                                |  |

| "L" level output                                       | V <sub>OL1</sub>  | Output pins other<br>than P05 to P07,<br>P62, P63                          | I <sub>OL</sub> = 4 mA* <sup>4</sup>     | _                     | _   | 0.4                   | V    |                                                |  |

| voitage                                                | V <sub>OL2</sub>  | P05 to P07, P62,<br>P63                                                    | I <sub>OL</sub> = 12 mA* <sup>5</sup>    | _                     | _   | 0.4                   | ٧    |                                                |  |

| Input leak<br>current (Hi-Z<br>output leak<br>current) | ILI               | All input pins                                                             | 0.0 V < V <sub>I</sub> < V <sub>CC</sub> | -5                    | _   | +5                    | μΑ   | When the internal pull-up resistor is disabled |  |

| Internal pull-up resistor                              | R <sub>PULL</sub> | P00 to P07,<br>P62 to P64,<br>PG1, PG2                                     | V <sub>I</sub> = 0 V                     | 75                    | 100 | 150                   | kΩ   | When the internal pull-up resistor is enabled  |  |

| Input capacitance                                      | C <sub>IN</sub>   | Other than V <sub>CC</sub> and V <sub>SS</sub>                             | f = 1 MHz                                |                       | 5   | 15                    | pF   |                                                |  |

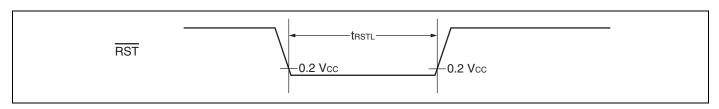

### 18.4.3 External Reset

(V<sub>CC</sub> = 3.0 V to 5.5 V, V<sub>SS</sub> = 0.0 V,  $T_A$  = -40 °C to +85 °C)

| Parameter                 | Symbol            | Value                 |     |      | Remarks |  |

|---------------------------|-------------------|-----------------------|-----|------|---------|--|

|                           |                   | Min                   | Max | Unit | Kemarks |  |

| RST "L" level pulse width | t <sub>RSTL</sub> | 2 t <sub>MCLK</sub> * |     | ns   |         |  |

<sup>\*:</sup> See "18.4.2. Source Clock/Machine Clock" for  $t_{\mbox{\scriptsize MCLK}}$ .

#### 18.4.6 LIN-UART Timing

Sampling is executed at the rising edge of the sampling  $clock^{*1}$ , and serial clock delay is disabled\*<sup>2</sup>. (ESCR register : SCES bit = 0, ECCR register : SCDE bit = 0)

(V<sub>CC</sub> = 3.0 V to 5.5 V, V<sub>SS</sub> = 0.0 V,  $T_A$  = -40 °C to +85 °C)

| Parameter                                     | Symbol             | Pin name     | Condition                                     | Va                                    | Unit                        |      |

|-----------------------------------------------|--------------------|--------------|-----------------------------------------------|---------------------------------------|-----------------------------|------|

| raidilletei                                   | Symbol             | Fill lialile | Condition                                     | Min                                   | Max                         | Onne |

| Serial clock cycle time                       | t <sub>SCYC</sub>  | SCK          |                                               | 5 t <sub>MCLK</sub> *3                | _                           | ns   |

| $SCK_{\downarrow} \rightarrow SOT$ delay time | t <sub>SLOVI</sub> | SCK, SOT     | Internal clock operation                      | -50                                   | +50                         | ns   |

| Valid SIN → SCK↑                              | t <sub>IVSHI</sub> | SCK, SIN     | output pin:<br>C <sub>I</sub> = 80 pF + 1 TTL | t <sub>MCLK</sub> *3 + 80             | _                           | ns   |

| SCK↑ → valid SIN hold time                    | t <sub>SHIXI</sub> | SCK, SIN     |                                               | 0                                     | _                           | ns   |

| Serial clock "L" pulse width                  | t <sub>SLSH</sub>  | SCK          |                                               | 3 t <sub>MCLK</sub> *3–t <sub>R</sub> | _                           | ns   |

| Serial clock "H" pulse width                  | t <sub>SHSL</sub>  | SCK          |                                               | t <sub>MCLK</sub> *3 + 10             | _                           | ns   |

| $SCK \downarrow \rightarrow SOT$ delay time   | t <sub>SLOVE</sub> | SCK, SOT     | External clock operation                      | _                                     | 2 t <sub>MCLK</sub> *3 + 60 | ns   |

| Valid SIN → SCK $\uparrow$                    | t <sub>IVSHE</sub> | SCK, SIN     | output pin:                                   | 30                                    | _                           | ns   |

| SCK↑ → valid SIN hold time                    | t <sub>SHIXE</sub> | SCK, SIN     | C <sub>L</sub> = 80 pF + 1 TTL                | t <sub>MCLK</sub> *3 + 30             | _                           | ns   |

| SCK fall time                                 | t <sub>F</sub>     | SCK          |                                               | _                                     | 10                          | ns   |

| SCK rise time                                 | t <sub>R</sub>     | SCK          |                                               | _                                     | 10                          | ns   |

<sup>\*1:</sup> There is a function used to choose whether the sampling of reception data is performed at a rising edge or a falling edge of the serial clock.

Document Number: 002-04696 Rev. \*B

<sup>\*2:</sup> The serial clock delay function is a function used to delay the output signal of the serial clock for half the clock.

<sup>\*3:</sup> See "18.4.2. Source Clock/Machine Clock" for t<sub>MCLK</sub>.

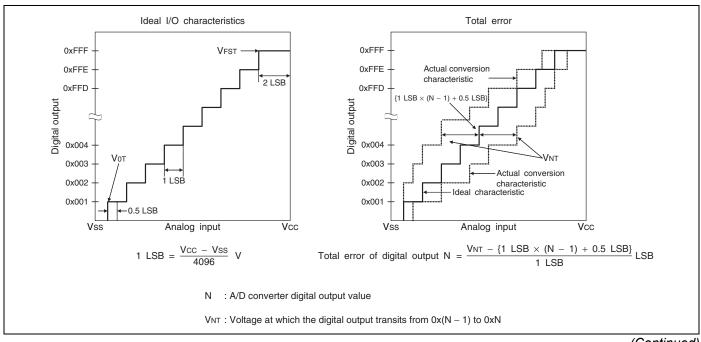

#### 18.5.3 Definitions of A/D Converter Terms

#### Resolution

It indicates the level of analog variation that can be distinguished by the A/D converter.

When the number of bits is 12, analog voltage can be divided into  $2^{12}$  = 4096.

### Linearity error (unit: LSB)

It indicates how much an actual conversion value deviates from the straight line connecting the zero transition point ("00000000000"  $\leftarrow \rightarrow$  "000000000001") of a device to the full-scale transition point ("111111111111"  $\leftarrow \rightarrow$  "111111111110") of the same device.

#### Differential linear error (unit: LSB)

It indicates how much the input voltage required to change the output code by 1 LSB deviates from an ideal value.

#### Total error (unit: LSB)

It indicates the difference between an actual value and a theoretical value. The error can be caused by a zero transition error, a full-scale transition errors, a linearity error, a quantum error, or noise.

## 19. Sample Characteristics

## Power supply current temperature characteristics

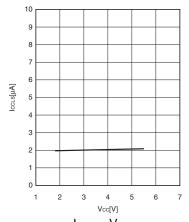

$I_{CC}-V_{CC} \\ T_A=+25~^{\circ}C,~F_{MP}=2,~4,~8,~10,~16~MHz~(divided~by~2) \\ Main~clock~mode~with~the~external~clock~operating$

$I_{CCS}-V_{CC}\\ T_A=+25~^{\circ}C,~F_{MP}=2,~4,~8,~10,~16~MHz~(divided~by~2)\\ Main~sleep~mode~with~the~external~clock~operating$

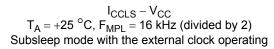

$I_{CCL} - V_{CC} \\ T_A = +25~^{\circ}C,~F_{MPL} = 16~\text{kHz (divided by 2)} \\ \text{Subclock mode with the external clock operating}$

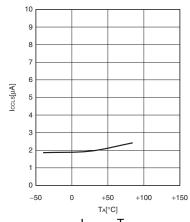

$\begin{array}{c} I_{CC}-T_{A} \\ V_{CC}=3.3V,\,F_{MP}=2,\,4,\,8,\,10,\,16\text{ MHz (divided by 2)} \\ \text{Main clock mode with the external clock operating} \end{array}$

$I_{CCS}-T_A \\ V_{CC}=3.3~V,~F_{MP}=2,~4,~8,~10,~16~MHz~(divided~by~2) \\ Main~sleep~mode~with~the~external~clock~operating$

$I_{CCL}-T_A \\ V_{CC}=3.3~V,~F_{MPL}=16~kHz~(divided~by~2) \\ Subclock mode with the external clock operating$

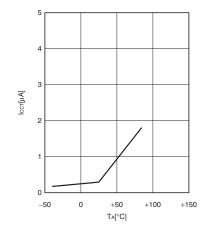

$I_{CCT} - V_{CC}$   $T_A = +25$  °C,  $F_{MPL} = 16$  kHz (divided by 2) Watch mode with the external clock operating

$I_{CCTS}-V_{CC}\\T_A=+25~^{\circ}C,~F_{MP}=2,~4,~8,~10,~16~MHz~(divided~by~2)\\Time-base~timer~mode~with~the~external~clock~operating$

$I_{CCLS}-T_A \\ V_{CC}=3.3~V,~F_{MPL}=16~kHz~(divided~by~2) \\ Subsleep~mode~with~the~external~clock~operating$

$I_{CCT}-T_A \\ V_{CC}=3.3 \text{ V, } F_{MPL}=16 \text{ kHz (divided by 2)} \\ Watch mode with the external clock operating}$

$I_{CCTS}-T_A \\ V_{CC}=3.3~V,~F_{MP}=2,~4,~8,~10,~16~MHz~(divided~by~2) \\ Time-base~timer~mode~with~the~external~clock~operating$

## 21. Ordering Information

| Part number                                                                                                                                                                                                                                                                                                                                                                                               | Package                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| MB95F652EPFT-G-SNE2<br>MB95F652LPFT-G-SNE2<br>MB95F653EPFT-G-SNE2<br>MB95F653LPFT-G-SNE2<br>MB95F654EPFT-G-SNE2<br>MB95F654LPFT-G-SNE2<br>MB95F656EPFT-G-SNE2<br>MB95F656LPFT-G-SNE2                                                                                                                                                                                                                      | 24-pin plastic TSSOP<br>(FPT-24P-M10) |

| MB95F652EPF-G-SNE2<br>MB95F652LPF-G-SNE2<br>MB95F653EPF-G-SNE2<br>MB95F653LPF-G-SNE2<br>MB95F654EPF-G-SNE2<br>MB95F654LPF-G-SNE2<br>MB95F656EPF-G-SNE2<br>MB95F656LPF-G-SNE2                                                                                                                                                                                                                              | 24-pin plastic SOP<br>(FPT-24P-M34)   |

| MB95F652EWQN-G-SNE1 MB95F652EWQN-G-SNERE1 MB95F652LWQN-G-SNERE1 MB95F652LWQN-G-SNERE1 MB95F653EWQN-G-SNERE1 MB95F653EWQN-G-SNERE1 MB95F653LWQN-G-SNERE1 MB95F653LWQN-G-SNERE1 MB95F654EWQN-G-SNERE1 MB95F654EWQN-G-SNERE1 MB95F654LWQN-G-SNERE1 MB95F656EWQN-G-SNERE1 MB95F656EWQN-G-SNERE1 MB95F656EWQN-G-SNERE1 MB95F656EWQN-G-SNERE1 MB95F656LWQN-G-SNERE1 MB95F656LWQN-G-SNERE1 MB95F656LWQN-G-SNERE1 | 32-pin plastic QFN<br>(LCC-32P-M19)   |

## Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers

Automotive

Clocks & Buffers

Interface

Internet of Things

cypress.com/automotive

cypress.com/clocks

cypress.com/interface

cypress.com/interface

cypress.com/iot

Memory cypress.com/memory

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

#### PSoC<sup>®</sup>Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2012-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress parally grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.