Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | F <sup>2</sup> MC-8FX                                                          |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 16MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, UART/USART                                      |

| Peripherals                | POR, PWM, WDT                                                                  |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 36KB (36K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                    |

| Data Converters            | A/D 6x8/12b                                                                    |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 24-TSSOP (0.173", 4.40mm Width)                                                |

| Supplier Device Package    | 24-TSSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f656lpft-g-sne2 |

## New 8FX 8-bit Microcontrollers

The MB95650L Series is a series of general-purpose, single-chip microcontrollers. In addition to a compact instruction set, the microcontrollers of this series contain a variety of peripheral functions.

#### **Features**

## F<sup>2</sup>MC-8FX CPU core

Instruction set optimized for controllers

- Multiplication and division instructions

- 16-bit arithmetic operations

- Bit test branch instructions

- Bit manipulation instructions, etc.

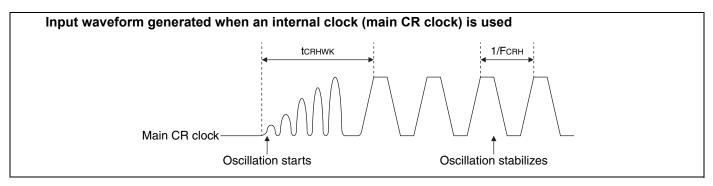

#### Clock

- Selectable main clock source

- Main oscillation clock (up to 16.25 MHz, maximum machine clock frequency: 8.125 MHz)

- □ External clock (up to 32.5 MHz, maximum machine clock frequency: 16.25 MHz)

- □ Main CR clock (4 MHz ±2%)

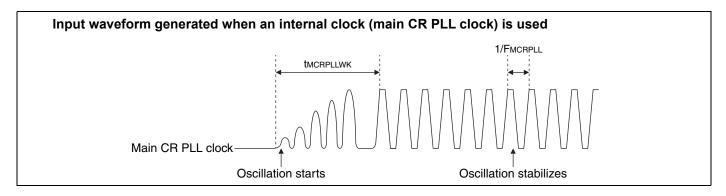

- ☐ Main CR PLL clock

- The main CR PLL clock frequency becomes 8 MHz  $\pm 2\%$  when the PLL multiplication rate is 2.

- The main CR PLL clock frequency becomes 10 MHz  $\pm 2\%$  when the PLL multiplication rate is 2.5.

- The main CR PLL clock frequency becomes 12 MHz  $\pm 2\%$  when the PLL multiplication rate is 3.

- The main CR PLL clock frequency becomes 16 MHz  $\pm 2\%$  when the PLL multiplication rate is 4.

- Main PLL clock (maximum machine clock frequency: 16 MHz)

- Selectable subclock source

- □ Suboscillation clock (32.768 kHz)

- □ External clock (32.768 kHz)

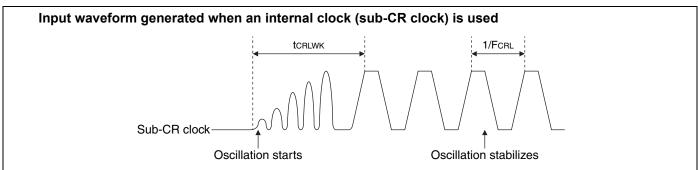

- □ Sub-CR clock (Typ: 100 kHz, Min: 50 kHz, Max: 150 kHz)

#### Timer

- 8/16-bit composite timer × 2 channels

- Time-base timer × 1 channel

- Watch prescaler × 1 channel

# UART/SIO $\times$ 1 channel (The channel can be used either as a UART/SIO channel or as an I<sup>2</sup>C bus interface channel.)

- The function of this channel can be switched between UART/SIO and I<sup>2</sup>C bus interface.

- Full duplex double buffer

- Capable of clock asynchronous (UART) serial data transfer and clock synchronous (SIO) serial data transfer

## $I^2C$ bus interface $\times$ 2 channels (One of the two channels can be used either as an $I^2C$ bus interface channel or as a UART/SIO channel.)

- Supports Standard-mode and Fast-mode (400 kHz).

- Built-in wake-up function

#### **LIN-UART**

- Full duplex double buffer

- Capable of clock asynchronous serial data transfer and clock synchronous serial data transfer

#### External interrupt × 6 channels

- Interrupt by edge detection (rising edge, falling edge, and both edges can be selected)

- Can be used to wake up the device from different low power consumption (standby) modes

#### 8/12-bit A/D converter × 6 channels

8-bit or 12-bit resolution can be selected.

#### Low power consumption (standby) modes

There are four standby modes as follows:

- Stop mode

- Sleep mode

- Watch mode

- Time-base timer mode

#### I/O port

- MB95F652E/F653E/F654E/F656E (number of I/O ports: 21)

- ☐ General-purpose I/O ports (CMOS I/O) : 17

- ☐ General-purpose I/O ports (N-ch open drain) : 4

- MB95F652L/F653L/F654L/F656L (number of I/O ports: 20)

- ☐ General-purpose I/O ports (CMOS I/O) : 17

- ☐ General-purpose I/O ports (N-ch open drain) : 3

#### On-chip debug

- 1-wire serial control

- Serial writing supported (asynchronous mode)

## Hardware/software watchdog timer

- Built-in hardware watchdog timer

- Built-in software watchdog timer

**Cypress Semiconductor Corporation** • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600 Document Number: 002-04696 Rev. \*B Revised August 7, 2017

| Pin n                                          | 0.                  |          | I/O                           |                                                |             | I/O type |                  |      |

|------------------------------------------------|---------------------|----------|-------------------------------|------------------------------------------------|-------------|----------|------------------|------|

| SOP24* <sup>1</sup> ,<br>TSSOP24* <sup>2</sup> | QFN32* <sup>3</sup> | Pin name | circuit<br>type* <sup>4</sup> | Function                                       | Input       | Output   | OD* <sup>5</sup> | PU*6 |

| 16                                             | 18                  | P00      | Е                             | General-purpose I/O port                       | Hysteresis/ | CMOS     |                  | О    |

| 10                                             | 10                  | AN00     |                               | 8/12-bit A/D converter analog input pin        | analog      | CIVIOS   | _                |      |

| 17                                             | 18                  | P01      | Е                             | General-purpose I/O port                       | Hysteresis/ | CMOS     |                  | О    |

| 17                                             | 10                  | AN01     | L                             | 8/12-bit A/D converter analog input pin        | analog      | CIVIOS   | _                |      |

|                                                |                     | P02      |                               | General-purpose I/O port                       |             |          |                  |      |

| 18                                             | 20                  | INT02    | Е                             | External interrupt input pin                   | Hysteresis/ | CMOS     |                  | О    |

| 10                                             | 20                  | AN02     |                               | 8/12-bit A/D converter analog input pin        | analog      | CIVIOS   | _                |      |

|                                                |                     | SCK      |                               | LIN-UART clock I/O pin                         |             |          |                  |      |

|                                                |                     | P03      |                               | General-purpose I/O port                       |             |          |                  |      |

| 10                                             | 21                  | INT03    | Е                             | External interrupt input pin                   | Hysteresis/ | CMOS     |                  | О    |

| 19                                             | 21                  | AN03     | _                             | 8/12-bit A/D converter analog input pin        | analog      | OIVIOO   | _                |      |

|                                                | SOT                 |          |                               | LIN-UART data output pin                       |             |          |                  |      |

|                                                |                     | P04      |                               | General-purpose I/O port                       |             |          |                  |      |

|                                                |                     | INT04    |                               | External interrupt input pin                   |             |          |                  | О    |

| 20                                             | 22                  | AN04     | F                             | 8/12-bit A/D converter analog input pin        | CMOS/       | CMOS     | _                |      |

| 20                                             | 22                  | SIN      |                               | LIN-UART data input pin                        | analog      | CIVIOS   |                  |      |

|                                                |                     | EC0      |                               | 8/16-bit composite timer ch. 0 clock input pin |             |          |                  |      |

|                                                |                     | P05      |                               | General-purpose I/O port<br>High-current pin   |             |          |                  |      |

| 21                                             | 23                  | INT05    | K                             | External interrupt input pin                   | Hysteresis/ | CMOS     | _                | О    |

|                                                |                     | AN05     |                               | 8/12-bit A/D converter analog input pin        | analog      |          |                  |      |

|                                                |                     | TO00     |                               | 8/16-bit composite timer ch. 0 output pin      |             |          |                  |      |

|                                                |                     | P06      |                               | General-purpose I/O port<br>High-current pin   |             |          |                  |      |

| 22                                             | 24                  | INT06    | D                             | External interrupt input pin                   | Hysteresis  | CMOS     | _                | О    |

|                                                |                     | TO01     |                               | 8/16-bit composite timer ch. 0 output pin      |             |          |                  |      |

|                                                |                     | P07      |                               | General-purpose I/O port<br>High-current pin   |             |          |                  |      |

| 23                                             | 26                  | INT07    | K                             | External interrupt input pin                   | Hysteresis  | CMOS     | _                | О    |

|                                                |                     | TO10     |                               | 8/16-bit composite timer ch. 1 output pin      |             |          |                  |      |

(Continued)

## (Continued)

| Pin n                                          | 0.                  |          | I/O                           |                                                |            | I/O type |                  |      |

|------------------------------------------------|---------------------|----------|-------------------------------|------------------------------------------------|------------|----------|------------------|------|

| SOP24* <sup>1</sup> ,<br>TSSOP24* <sup>2</sup> | QFN32* <sup>3</sup> | Pin name | circuit<br>type* <sup>4</sup> | Function                                       | Input      | Output   | OD* <sup>5</sup> | PU*6 |

|                                                |                     | P12      |                               | General-purpose I/O port                       |            |          | О                |      |

| 24                                             | 25                  | DBG      | Н                             | DBG input pin                                  | Hysteresis | CMOS     |                  | _    |

| 2.                                             |                     | EC0      |                               | 8/16-bit composite timer ch. 0 clock input pin | ,          |          |                  |      |

|                                                | 11                  |          |                               |                                                |            |          |                  |      |

|                                                | 12                  |          |                               |                                                |            | _        |                  | _    |

|                                                | 13                  |          |                               |                                                |            |          |                  |      |

|                                                | 14                  | NC       |                               | It is an internally connected pin. Always      |            |          |                  |      |

| _                                              | 27                  | INC      | _                             | leave it unconnected.                          | _          |          |                  |      |

|                                                | 28                  |          |                               |                                                |            |          |                  |      |

|                                                | 29                  |          |                               |                                                |            |          |                  |      |

|                                                | 30                  |          |                               |                                                |            |          |                  |      |

O: Available

\*1: FPT-24P-M34

\*2: FPT-24P-M10

\*3: LCC-32P-M19

\*4: For the I/O circuit types, see "6. I/O Circuit Type".

\*5: N-ch open drain

\*6: Pull-up

\*7: In I<sup>2</sup>C mode, the pin becomes an N-ch open drain pin.

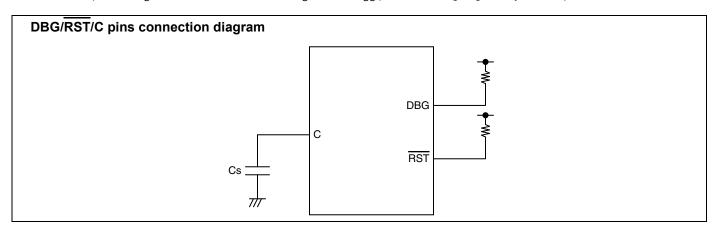

#### 9. Pin Connection

#### Treatment of unused pins

If an unused input pin is left unconnected, a component may be permanently damaged due to malfunctions or latch-ups. Always pull up or pull down an unused input pin through a resistor of at least  $2 \text{ k}\Omega$ . Set an unused input/output pin to the output state and leave it unconnected, or set it to the input state and treat it the same as an unused input pin. If there is an unused output pin, leave it unconnected.

#### Power supply pins

To reduce unnecessary electro-magnetic emission, prevent malfunctions of strobe signals due to an increase in the ground level, and conform to the total output current standard, always connect the  $V_{CC}$  pin and the  $V_{SS}$  pin to the power supply and ground outside the device. In addition, connect the current supply source to the  $V_{CC}$  pin and the  $V_{SS}$  pin with low impedance.

It is also advisable to connect a ceramic capacitor of approximately 1.0  $\mu$ F as a bypass capacitor between the  $V_{CC}$  pin and the  $V_{SS}$  pin at a location close to this device.

#### **DBG** pin

Connect the DBG pin to an external pull-up resistor of 2 k $\Omega$  or above.

After power-on, ensure that the DBG pin does not stay at "L" level until the reset output is released.

The DBG pin becomes a communication pin in debug mode. Since the actual pull-up resistance depends on the tool used and the interconnection length, refer to the tool document when selecting a pull-up resistor.

#### RST pin

Connect the  $\overline{RST}$  pin to an external pull-up resistor of 2 k $\Omega$  or above.

To prevent the device from unintentionally entering the reset mode due to noise, minimize the interconnection length between a pull-up resistor and the RST pin and that between a pull-up resistor and the  $V_{CC}$  pin when designing the layout of the printed circuit board.

The PF2/RST pin functions as the reset input/output pin after power-on. In addition, the reset output of the PF2/RST pin can be enabled by the RSTOE bit in the SYSC register, and the reset input function and the general purpose I/O function can be selected by the RSTEN bit in the SYSC register.

#### C pin

Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. The decoupling capacitor for the  $V_{CC}$  pin must have a capacitance equal to or larger than the capacitance of  $C_S$ . For the connection to a decoupling capacitor  $C_S$ , see the diagram below. To prevent the device from unintentionally entering a mode to which the device is not set to transit due to noise, minimize the distance between the C pin and  $C_S$  and the distance between  $C_S$  and the  $V_{SS}$  pin when designing the layout of a printed circuit board.

#### Note on serial communication

In serial communication, reception of wrong data may occur due to noise or other causes. Therefore, design a printed circuit board to prevent noise from occurring. Taking account of the reception of wrong data, take measures such as adding a checksum to the end of data in order to detect errors. If an error is detected, retransmit the data.

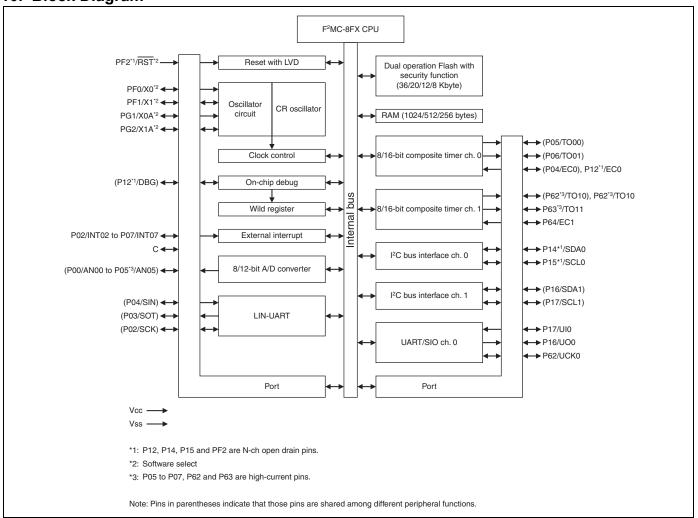

10. Block Diagram

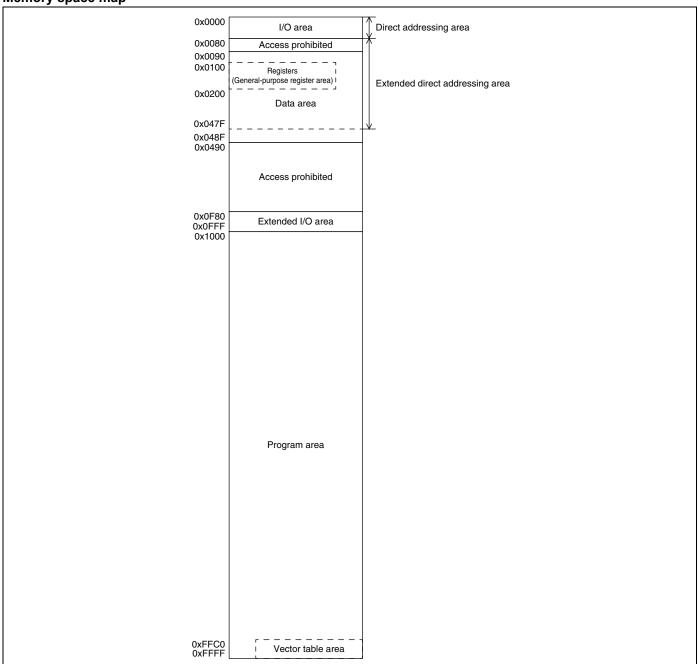

Memory space map

## 15.2.3 Port 1 registers

## Port 1 register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                               |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|-------------------------------------|--|--|--|--|

| PDR1                  | 0    | Pin state is "L" level. | PDR1 value is "0".                          | As output port, outputs "L" level.  |  |  |  |  |

| FDRI                  | 1    | Pin state is "H" level. | PDR1 value is "1".                          | As output port, outputs "H" level.* |  |  |  |  |

| DDR1                  | 0    |                         | Port input enabled                          |                                     |  |  |  |  |

| DDK1                  | 1    |                         | Port output enabled                         |                                     |  |  |  |  |

<sup>\*:</sup> If the pin is an N-ch open drain pin, the pin state becomes Hi-Z.

## Correspondence between registers and pins for port 1

|          |      | Correspondence between related register bits and pins |      |      |   |      |   |   |  |  |  |

|----------|------|-------------------------------------------------------|------|------|---|------|---|---|--|--|--|

| Pin name | P17  | P16                                                   | P15  | P14  | - | P12  | - | - |  |  |  |

| PDR1     | bit7 | bit6                                                  | bit5 | bit4 |   | bit2 |   |   |  |  |  |

| DDR1     | DILI | טונט                                                  | טונט | DIL4 |   | DILZ | - | - |  |  |  |

## 17. Pin States in each Mode

| Din nome                                    | Normal                                                   | Class made                               | Stop                                                                                    | mode                                                                     | Watch                                                                                   | mode                                                                     | 0::::::::::::::::::::::::::::::::::::::                                              |

|---------------------------------------------|----------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Pin name                                    | operation                                                | Sleep mode                               | SPL=0                                                                                   | SPL=1                                                                    | SPL=0                                                                                   | SPL=1                                                                    | On reset                                                                             |

|                                             | Oscillation input                                        | Oscillation input                        | Hi-Z                                                                                    | Hi-Z                                                                     | Hi-Z                                                                                    | Hi-Z                                                                     | _                                                                                    |

| PF0/X0                                      | I/O port* <sup>1</sup>                                   | I/O port* <sup>1</sup>                   | - Previous state<br>kept<br>- Input<br>blocked*1, *2                                    | - Hi-Z<br>- Input<br>blocked* <sup>1, *2</sup>                           | - Previous state<br>kept<br>- Input<br>blocked*1, *2                                    | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.) |

|                                             | Oscillation input                                        | Oscillation input                        | Hi-Z                                                                                    | Hi-Z                                                                     | Hi-Z                                                                                    | Hi-Z                                                                     | _                                                                                    |

| PF1/X1                                      | I/O port* <sup>1</sup>                                   | I/O port* <sup>1</sup>                   | - Previous state<br>kept<br>- Input<br>blocked* <sup>1, *2</sup>                        | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Previous state<br>kept<br>- Input<br>blocked*1, *2                                    | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.) |

|                                             | Reset input                                              | Reset input                              | Reset input                                                                             | Reset input                                                              | Reset input                                                                             | Reset input                                                              | Reset input*4                                                                        |

| PF2/RST                                     | I/O port* <sup>1</sup>                                   | - Previous<br>kept<br>- Input<br>blocked |                                                                                         | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Previous state<br>kept<br>- Input<br>blocked* <sup>1, *2</sup>                        | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.) |

|                                             | Oscillation input                                        | Oscillation input                        | Hi-Z                                                                                    | Hi-Z                                                                     | Hi-Z                                                                                    | Hi-Z                                                                     | _                                                                                    |

| PG1/X0A I/O port*1                          |                                                          | I/O port* <sup>1</sup>                   | - Previous state<br>kept<br>- Input<br>blocked* <sup>1, *2</sup>                        | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Previous state<br>kept<br>- Input<br>blocked* <sup>1, *2</sup>                        | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.) |

|                                             | Oscillation input                                        | Oscillation input                        | Hi-Z                                                                                    | Hi-Z                                                                     | Hi-Z                                                                                    | Hi-Z                                                                     | _                                                                                    |

| PG2/X1A                                     | I/O port* <sup>1</sup>                                   | - Previous st                            |                                                                                         | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Previous state<br>kept<br>- Input<br>blocked*1, *2                                    | - Hi-Z<br>- Input<br>blocked* <sup>1,</sup> * <sup>2</sup>               | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.) |

| P00/AN00                                    |                                                          |                                          |                                                                                         |                                                                          |                                                                                         |                                                                          |                                                                                      |

| P01/AN01                                    |                                                          |                                          |                                                                                         |                                                                          |                                                                                         |                                                                          |                                                                                      |

| P02/INT02/<br>AN02/SCK                      |                                                          |                                          |                                                                                         |                                                                          |                                                                                         |                                                                          |                                                                                      |

| P03/INT03/<br>AN03/SOT                      | I/O port/<br>peripheral<br>function I/O/<br>analog input |                                          | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*<sup>2, *5</sup></li> </ul> | - Hi-Z* <sup>6</sup><br>- Input<br>blocked* <sup>2,</sup> * <sup>5</sup> | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*<sup>2, *5</sup></li> </ul> | - Hi-Z* <sup>6</sup><br>- Input<br>blocked* <sup>2,</sup> * <sup>5</sup> | - Hi-Z<br>- Input<br>blocked* <sup>2</sup>                                           |

| AN04/SIN/<br>EC0<br>P05/INT05/<br>AN05/TO00 |                                                          | 3                                        | <del></del>                                                                             |                                                                          | <del>-</del>                                                                            |                                                                          |                                                                                      |

## 18. Electrical Characteristics

## 18.1 Absolute Maximum Ratings

| Downwater                              | Cumahaal                    | Rat                   | ting                | l lmi4 | Domonto                                                                                                 |

|----------------------------------------|-----------------------------|-----------------------|---------------------|--------|---------------------------------------------------------------------------------------------------------|

| Parameter                              | Symbol                      | Min                   | Max                 | Unit   | Remarks                                                                                                 |

| Power supply voltage*1                 | V <sub>CC</sub>             | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 6 | V      |                                                                                                         |

| Input voltage*1                        | V <sub>I</sub>              | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 6 | V      | *2                                                                                                      |

| Output voltage*1                       | V <sub>O</sub>              | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 6 | V      | *2                                                                                                      |

| Maximum clamp current                  | I <sub>CLAMP</sub>          | -2                    | +2                  | mA     | Applicable to specific pins*3                                                                           |

| Total maximum clamp current            | $\Sigma  I_{\text{CLAMP}} $ | _                     | 20                  | mA     | Applicable to specific pins*3                                                                           |

| "L" level maximum output current       | I <sub>OL</sub>             | _                     | 15                  | mA     |                                                                                                         |

| "L" level average current              | I <sub>OLAV1</sub>          |                       | 4                   | - mA   | Other than P05 to P07, P62 and P63 Average output current = operating current × operating ratio (1 pin) |

| L level average current                | I <sub>OLAV2</sub>          | _                     | 12                  |        | P05 to P07, P62 and P63 Average output current = operating current × operating ratio (1 pin)            |

| "L" level total maximum output current | $\Sigma$ I <sub>OL</sub>    | _                     | 100                 | mA     |                                                                                                         |

| "L" level total average output current | $\Sigma I_{OLAV}$           | _                     | 37                  | mA     | Total average output current = operating current × operating ratio (Total number of pins)               |

| "H" level maximum output current       | I <sub>OH</sub>             | _                     | -15                 | mA     |                                                                                                         |

| "H" level average current              | I <sub>OHAV1</sub>          |                       | -4                  | - mA   | Other than P05 to P07, P62 and P63 Average output current = operating current × operating ratio (1 pin) |

| Thever average current                 | I <sub>OHAV2</sub>          | _                     | -8                  |        | P05 to P07, P62 and P63 Average output current = operating current × operating ratio (1 pin)            |

| "H" level total maximum output current | $\Sigma$ I <sub>OH</sub>    | _                     | -100                | mA     |                                                                                                         |

| "H" level total average output current | $\Sigma$ I $_{OHAV}$        | _                     | -47                 | mA     | Total average output current = operating current × operating ratio (Total number of pins)               |

| Power consumption                      | $P_{d}$                     | _                     | 320                 | mW     |                                                                                                         |

| Operating temperature                  | $T_A$                       | -40                   | +85                 | °C     |                                                                                                         |

| Storage temperature                    | $T_{stg}$                   | -55                   | +150                | °C     |                                                                                                         |

<sup>\*1:</sup> These parameters are based on the condition that  $V_{SS}$  is 0.0 V.

(Continued)

Document Number: 002-04696 Rev. \*B

<sup>\*2:</sup>  $V_1$  and  $V_0$  must not exceed  $V_{CC}$  + 0.3 V.  $V_1$  must not exceed the rated voltage. However, if the maximum current to/from an input is limited by means of an external component, the  $I_{CLAMP}$  rating is used instead of the  $V_1$  rating.

## 18.3 DC Characteristics

(V<sub>CC</sub> = 3.0 V±10%, V<sub>SS</sub> = 0.0 V,  $T_A$  = -40 °C to +85 °C)

|                                                        |                   |                                                                            |                                          |                       | Value |                       |      | , 1 <sub>A</sub> 10 0 to 100 0                 |  |

|--------------------------------------------------------|-------------------|----------------------------------------------------------------------------|------------------------------------------|-----------------------|-------|-----------------------|------|------------------------------------------------|--|

| Parameter                                              | Symbol            | Pin name                                                                   | Condition                                | Min                   | Тур   | Max                   | Unit | Remarks                                        |  |

|                                                        | V <sub>IHI1</sub> | P04, P16, P17                                                              | *1                                       | 0.7 V <sub>CC</sub>   | _     | V <sub>CC</sub> + 0.3 | V    | CMOS input level                               |  |

|                                                        | V <sub>IHI2</sub> | P14, P15                                                                   | *1                                       | 0.7 V <sub>CC</sub>   | _     | V <sub>CC</sub> + 5.5 | V    | CMOS input level                               |  |

| "H" level input<br>voltage                             | V <sub>IHS</sub>  | P00 to P03,<br>P05 to P07,<br>P12,<br>P62 to P64,<br>PF0, PF1,<br>PG1, PG2 | *1                                       | 0.8 V <sub>CC</sub>   | _     | V <sub>CC</sub> + 0.3 | V    | Hysteresis input                               |  |

|                                                        | $V_{IHM}$         | PF2                                                                        | _                                        | 0.8 V <sub>CC</sub>   | —     | $V_{CC} + 0.3$        | V    | Hysteresis input                               |  |

|                                                        | V <sub>ILI</sub>  | P04, P14 to P17                                                            | *1                                       | $V_{SS}-0.3$          | _     | 0.3 V <sub>CC</sub>   | V    | CMOS input level                               |  |

| "L" level input<br>voltage                             | V <sub>ILS</sub>  | P00 to P03,<br>P05 to P07,<br>P12,<br>P62 to P64,<br>PF0, PF1,<br>PG1, PG2 | *1                                       | V <sub>SS</sub> - 0.3 | _     | 0.2 V <sub>CC</sub>   | V    | Hysteresis input                               |  |

|                                                        | $V_{ILM}$         | PF2                                                                        | _                                        | V <sub>SS</sub> - 0.3 | _     | 0.2 V <sub>CC</sub>   | V    | Hysteresis input                               |  |

| Open-drain                                             | V <sub>D1</sub>   | P12, PF2                                                                   | _                                        | $V_{SS}-0.3$          | _     | V <sub>SS</sub> + 5.5 | V    |                                                |  |

| output application                                     | $V_{D2}$          | P14, P15                                                                   | _                                        | V <sub>SS</sub> - 0.3 | _     | V <sub>SS</sub> + 5.5 | V    |                                                |  |

| voltage                                                | V <sub>D3</sub>   | P16, P17                                                                   | _                                        | V <sub>SS</sub> - 0.3 | _     | V <sub>SS</sub> + 5.5 | V    | In I <sup>2</sup> C mode                       |  |

| "H" level output                                       | V <sub>OH1</sub>  | Output pins other than P05 to P07, P12, P62, P63                           | $I_{OH} = -4 \text{ mA}^{*2}$            | V <sub>CC</sub> - 0.5 | _     | _                     | ٧    |                                                |  |

| voltage                                                | V <sub>OH2</sub>  | P05 to P07, P62,<br>P63                                                    | $I_{OH} = -8 \text{ mA}^{*3}$            | V <sub>CC</sub> - 0.5 | _     | _                     | V    |                                                |  |

| "L" level output                                       | V <sub>OL1</sub>  | Output pins other<br>than P05 to P07,<br>P62, P63                          | I <sub>OL</sub> = 4 mA* <sup>4</sup>     | _                     | _     | 0.4                   | V    |                                                |  |

| voitage                                                | V <sub>OL2</sub>  | P05 to P07, P62,<br>P63                                                    | I <sub>OL</sub> = 12 mA* <sup>5</sup>    | _                     | _     | 0.4                   | V    |                                                |  |

| Input leak<br>current (Hi-Z<br>output leak<br>current) | ILI               | All input pins                                                             | 0.0 V < V <sub>I</sub> < V <sub>CC</sub> | -5                    | _     | +5                    | μΑ   | When the internal pull-up resistor is disabled |  |

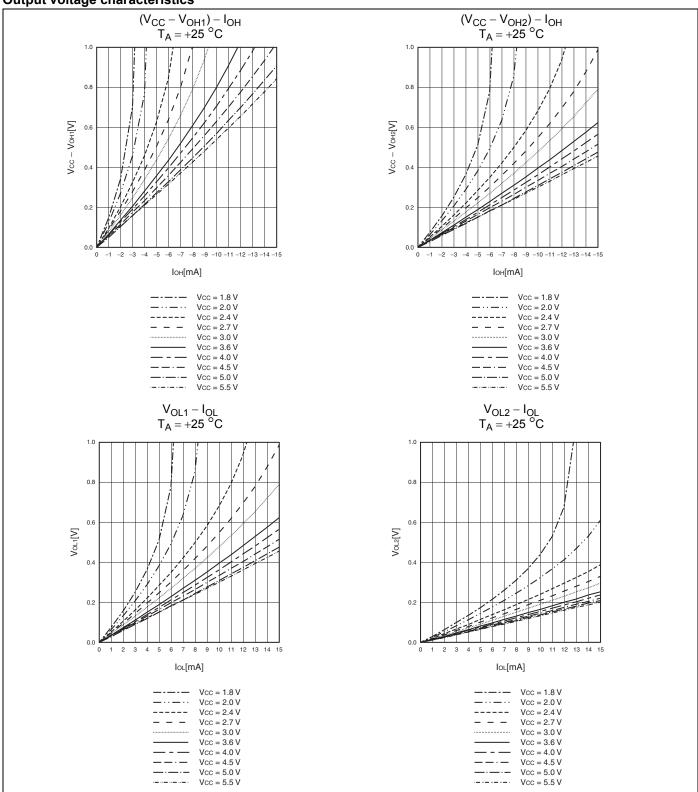

| Internal pull-up resistor                              | R <sub>PULL</sub> | P00 to P07,<br>P62 to P64,<br>PG1, PG2                                     | V <sub>I</sub> = 0 V                     | 75                    | 100   | 150                   | kΩ   | When the internal pull-up resistor is enabled  |  |

| Input capacitance                                      | C <sub>IN</sub>   | Other than V <sub>CC</sub> and V <sub>SS</sub>                             | f = 1 MHz                                |                       | 5     | 15                    | pF   |                                                |  |

(Continued)

(V<sub>CC</sub> = 3.0 V±10%, V<sub>SS</sub> = 0.0 V,  $T_A$  = -40 °C to +85 °C)

|                                     |                                   |                                                                                                         |                                                                                                                           | (*66 |       | 10 70, 155        | 0.0 1 | , 1 <sub>A</sub> 10 0 to 100 0) |

|-------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------|-------|---------------------------------|

| Parameter                           | Symbol                            | Pin name                                                                                                | Condition                                                                                                                 |      | Value |                   | Unit  | Remarks                         |

| Parameter                           | Symbol                            | Fill liallie                                                                                            | Condition                                                                                                                 | Min  | Typ*1 | Max* <sup>6</sup> | Offic | Remarks                         |

|                                     | I <sub>CCTS</sub> V <sub>CC</sub> | V <sub>CC</sub><br>(External clock                                                                      | F <sub>CH</sub> = 32 MHz<br>Time-base timer mode<br>T <sub>A</sub> = +25 °C                                               | _    | 450   | 500               | μΑ    |                                 |

|                                     | I <sub>CCH</sub>                  |                                                                                                         | Substop mode<br>T <sub>A</sub> = +25 °C                                                                                   | _    | 0.7   | 5                 | μΑ    |                                 |

| I <sub>PLVD</sub> I <sub>ILVD</sub> | I <sub>PLVD</sub>                 |                                                                                                         | Current consumption of<br>the low-voltage<br>detection reset circuit in<br>operation                                      | _    | 6     | 26                | μΑ    |                                 |

|                                     |                                   | Current consumption of<br>the low-voltage<br>detection interrupt<br>circuit operating in<br>normal mode | _                                                                                                                         | 6    | 14    | μΑ                |       |                                 |

| current* <sup>7</sup>               | I <sub>ILVDL</sub>                | V <sub>cc</sub>                                                                                         | Current consumption of<br>the low-voltage<br>detection interrupt<br>circuit operating in low<br>power consumption<br>mode | _    | 3     | 10                | μΑ    |                                 |

|                                     | I <sub>CRH</sub>                  |                                                                                                         | Current consumption of the main CR oscillator                                                                             | _    | 270   | 320               | μΑ    |                                 |

|                                     | I <sub>CRL</sub>                  |                                                                                                         | Current consumption of<br>the sub-CR oscillator<br>oscillating at 100 kHz                                                 | _    | 5     | 20                | μΑ    |                                 |

|                                     | I <sub>SOSC</sub>                 |                                                                                                         | Current consumption of the suboscillator                                                                                  | _    | 0.8   | 7                 | μΑ    |                                 |

<sup>\*1:</sup>  $V_{CC}$  = 3.0 V,  $T_A$  = +25 °C

- See "18.4. AC Characteristics 18.4.1. Clock Timing" for F<sub>CH</sub>, F<sub>CL</sub>, F<sub>CRH</sub>, F<sub>MCRPLL</sub> and F<sub>MPLL</sub>.

- See "18.4. AC Characteristics 18.4.2. Source Clock/Machine Clock" for F<sub>MP</sub> and F<sub>MPI</sub>.

- The power supply current in subclock mode is determined by the external clock. In subclock mode, current consumption in using

the crystal oscillator is higher than that in using the external clock. When the crystal oscillator is used, the power supply current

is the sum of adding I<sub>SOSC</sub> (current consumption of the suboscillator) to the power supply current in using the external clock.

For details of controlling the subclock, refer to "Chapter 3 Clock Controller" And "chapter 24 System Configuration Register" in

"New 8FX MB95650L Series Hardware Manual".

<sup>\*2:</sup> When  $V_{CC}$  is smaller than 4.5 V, the condition becomes  $I_{OH} = -2$  mA.

<sup>\*3:</sup> When  $V_{CC}$  is smaller than 4.5 V, the condition becomes  $I_{OH} = -4$  mA.

<sup>\*4:</sup> When  $V_{CC}$  is smaller than 4.5 V, the condition becomes  $I_{OL}$  = 2 mA.

<sup>\*5:</sup> When  $V_{CC}$  is smaller than 4.5 V, the condition becomes  $I_{OH}$  = 6 mA.

<sup>\*6:</sup>  $V_{CC}$  = 3.3 V,  $T_A$  = +85 °C (unless otherwise specified)

<sup>\*7: •</sup> The power supply current is determined by the external clock. When the low-voltage detection reset circuit is selected, the power supply current is the sum of adding the current consumption of the low-voltage detection reset circuit (I<sub>PLVD</sub>) to one of the values from I<sub>CC</sub> to I<sub>CCH</sub>. In addition, when the low-voltage detection reset circuit and a CR oscillator are selected, the power supply current is the sum of adding up the current consumption of the low-voltage detection reset circuit (I<sub>PLVD</sub>), the current consumption of the CR oscillator (I<sub>CRH</sub> or I<sub>CRL</sub>) and one of the values from I<sub>CC</sub> to I<sub>CCH</sub>. In on-chip debug mode, the main CR oscillator (I<sub>CRH</sub>) and the low-voltage detection reset circuit are always in operation, and current consumption therefore increases accordingly.

#### 18.4.6 LIN-UART Timing

Sampling is executed at the rising edge of the sampling  $clock^{*1}$ , and serial clock delay is disabled\*<sup>2</sup>. (ESCR register : SCES bit = 0, ECCR register : SCDE bit = 0)

(V<sub>CC</sub> = 3.0 V to 5.5 V, V<sub>SS</sub> = 0.0 V,  $T_A$  = -40 °C to +85 °C)

| Parameter                                     | Symbol             | Pin name     | Condition                                     | Va                                    | lue                         | Unit |

|-----------------------------------------------|--------------------|--------------|-----------------------------------------------|---------------------------------------|-----------------------------|------|

| raidilletei                                   | Symbol             | Fill lialile | Condition                                     | Min                                   | Max                         | Onit |

| Serial clock cycle time                       | t <sub>SCYC</sub>  | SCK          |                                               | 5 t <sub>MCLK</sub> *3                | _                           | ns   |

| $SCK_{\downarrow} \rightarrow SOT$ delay time | t <sub>SLOVI</sub> | SCK, SOT     | Internal clock operation                      | -50                                   | +50                         | ns   |

| Valid SIN → SCK↑                              | t <sub>IVSHI</sub> | SCK, SIN     | output pin:<br>C <sub>I</sub> = 80 pF + 1 TTL | t <sub>MCLK</sub> *3 + 80             | _                           | ns   |

| SCK↑ → valid SIN hold time                    | t <sub>SHIXI</sub> | SCK, SIN     |                                               | 0                                     | _                           | ns   |

| Serial clock "L" pulse width                  | t <sub>SLSH</sub>  | SCK          |                                               | 3 t <sub>MCLK</sub> *3–t <sub>R</sub> | _                           | ns   |

| Serial clock "H" pulse width                  | t <sub>SHSL</sub>  | SCK          |                                               | t <sub>MCLK</sub> *3 + 10             | _                           | ns   |

| $SCK \downarrow \rightarrow SOT$ delay time   | t <sub>SLOVE</sub> | SCK, SOT     | External clock operation                      | _                                     | 2 t <sub>MCLK</sub> *3 + 60 | ns   |

| Valid SIN → SCK $\uparrow$                    | t <sub>IVSHE</sub> | SCK, SIN     | output pin:                                   | 30                                    | _                           | ns   |

| SCK↑ → valid SIN hold time                    | t <sub>SHIXE</sub> | SCK, SIN     | C <sub>L</sub> = 80 pF + 1 TTL                | t <sub>MCLK</sub> *3 + 30             | _                           | ns   |

| SCK fall time                                 | t <sub>F</sub>     | SCK          |                                               | _                                     | 10                          | ns   |

| SCK rise time                                 | t <sub>R</sub>     | SCK          |                                               | _                                     | 10                          | ns   |

<sup>\*1:</sup> There is a function used to choose whether the sampling of reception data is performed at a rising edge or a falling edge of the serial clock.

Document Number: 002-04696 Rev. \*B

<sup>\*2:</sup> The serial clock delay function is a function used to delay the output signal of the serial clock for half the clock.

<sup>\*3:</sup> See "18.4.2. Source Clock/Machine Clock" for t<sub>MCLK</sub>.

## 18.4.7 Low-vo Itage Detection

## Normal mode

(V<sub>CC</sub> = 1.8 V to 5.5 V, V<sub>SS</sub> = 0.0 V,  $T_A$  = –40 °C to +85 °C)

| D                                                         | 0                   |       | Value |      | 11!4 | Bourantes                                                                                                               |

|-----------------------------------------------------------|---------------------|-------|-------|------|------|-------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                 | Symbol              | Min   | Тур   | Max  | Unit | Remarks                                                                                                                 |

| Reset release voltage                                     | $V_{PDL+}$          | 1.88  | 2.03  | 2.18 | V    | At power supply rise                                                                                                    |

| Reset detection voltage                                   | $V_{\mathrm{PDL}-}$ | 1.8   | 1.93  | 2.06 | V    | At power supply fall                                                                                                    |

| Interrupt release voltage 0                               | V <sub>IDL0+</sub>  | 2.13  | 2.3   | 2.47 | V    | At power supply rise                                                                                                    |

| Interrupt detection voltage 0                             | V <sub>IDL0-</sub>  | 2.05  | 2.2   | 2.35 | V    | At power supply fall                                                                                                    |

| Interrupt release voltage 1                               | V <sub>IDL1+</sub>  | 2.41  | 2.6   | 2.79 | V    | At power supply rise                                                                                                    |

| Interrupt detection voltage 1                             | V <sub>IDL1-</sub>  | 2.33  | 2.5   | 2.67 | V    | At power supply fall                                                                                                    |

| Interrupt release voltage 2                               | $V_{IDL2^+}$        | 2.69  | 2.9   | 3.11 | V    | At power supply rise                                                                                                    |

| Interrupt detection voltage 2                             | V <sub>IDL2</sub>   | 2.61  | 2.8   | 2.99 | V    | At power supply fall                                                                                                    |

| Interrupt release voltage 3                               | V <sub>IDL3+</sub>  | 3.06  | 3.3   | 3.54 | V    | At power supply rise                                                                                                    |

| Interrupt detection voltage 3                             | V <sub>IDL3</sub>   | 2.98  | 3.2   | 3.42 | V    | At power supply fall                                                                                                    |

| Interrupt release voltage 4                               | $V_{\text{IDL4+}}$  | 3.43  | 3.7   | 3.97 | V    | At power supply rise                                                                                                    |

| Interrupt detection voltage 4                             | V <sub>IDL4-</sub>  | 3.35  | 3.6   | 3.85 | V    | At power supply fall                                                                                                    |

| Interrupt release voltage 5                               | V <sub>IDL5+</sub>  | 3.81  | 4.1   | 4.39 | V    | At power supply rise                                                                                                    |

| Interrupt detection voltage 5                             | V <sub>IDL5-</sub>  | 3.73  | 4     | 4.27 | V    | At power supply fall                                                                                                    |

| Power supply start voltage                                | $V_{\rm off}$       | _     | _     | 1.6  | V    |                                                                                                                         |

| Power supply end voltage                                  | V <sub>on</sub>     | 4.39  | _     | _    | V    |                                                                                                                         |

| Power supply voltage change time (at power supply rise)   | t <sub>r</sub>      | 697.5 | _     | _    | μs   | Slope of power supply that the reset release signal generates within the rating (V <sub>PDL+</sub> /V <sub>IDL+</sub> ) |

| Power supply voltage change time (at power supply fall)   | t <sub>f</sub>      | 697.5 | _     | _    | μs   | Slope of power supply that the reset release signal generates within the rating (V <sub>PDL</sub> _/V <sub>IDL</sub> _) |

| Reset release delay time                                  | t <sub>dp1</sub>    | _     | _     | 30   | μs   |                                                                                                                         |

| Reset detection delay time                                | t <sub>dp2</sub>    | _     | _     | 30   | μs   |                                                                                                                         |

| Interrupt release delay time                              | t <sub>di1</sub>    | _     | _     | 30   | μs   |                                                                                                                         |

| Interrupt detection delay time                            | t <sub>di2</sub>    | _     | _     | 30   | μs   |                                                                                                                         |

| LVD reset threshold voltage transition stabilization time | t <sub>stb</sub>    |       | _     | 30   | μs   |                                                                                                                         |

## 18.6 Flash Memory Program/Erase Characteristics

| Parameter                              |                 | Value                                                                                      |                   | Unit  | Remarks                                                                           |

|----------------------------------------|-----------------|--------------------------------------------------------------------------------------------|-------------------|-------|-----------------------------------------------------------------------------------|

| Parameter                              | Min             | Тур                                                                                        | Max               | Ullit | Remarks                                                                           |

| Sector erase time (2 Kbyte sector)     | 1               | 0.3*1                                                                                      | 1.6* <sup>2</sup> | s     | The time of writing "0x00" prior to erasure is excluded.                          |

| Sector erase time<br>(32 Kbyte sector) | _               | 0.6* <sup>1</sup>                                                                          | 3.1* <sup>2</sup> | s     | The time of writing "0x00" prior to erasure is excluded.                          |

| Byte writing time                      | _               | 17                                                                                         | 272               | μs    | System-level overhead is excluded.                                                |

| Program/erase cycle                    | 100000          | _                                                                                          | _                 | cycle |                                                                                   |

| Power supply voltage at program/erase  | 1.8             | _                                                                                          | 5.5               | V     |                                                                                   |

|                                        | 20*3            | _                                                                                          | _                 |       | Average T <sub>A</sub> = +85 °C<br>Number of program/erase cycles: 1000 or below  |

| Flash memory data retention time       |                 | Average T <sub>A</sub> = +85 °C<br>Number of program/erase cycles: 1001 to 10000 inclusive |                   |       |                                                                                   |

|                                        | 5* <sup>3</sup> | _                                                                                          | _                 |       | Average T <sub>A</sub> = +85 °C<br>Number of program/erase cycles: 10001 or above |

$<sup>\</sup>overline{*1: V_{CC} = 5.5 \text{ V}, T_A = +25 ^{\circ}\text{C}, 0 \text{ cycle}}$

<sup>\*2:</sup>  $V_{CC}$  = 1.8 V,  $T_A$  = +85 °C, 100000 cycles

<sup>\*3:</sup> These values were converted from the result of a technology reliability assessment. (These values were converted from the result of a high temperature accelerated test using the Arrhenius equation with the average temperature being +85 °C.)

$I_{CCT} - V_{CC}$   $T_A = +25$  °C,  $F_{MPL} = 16$  kHz (divided by 2) Watch mode with the external clock operating

$I_{CCTS}-V_{CC}\\T_A=+25~^{\circ}C,~F_{MP}=2,~4,~8,~10,~16~MHz~(divided~by~2)\\Time-base~timer~mode~with~the~external~clock~operating$

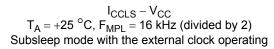

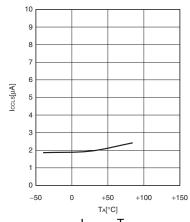

$I_{CCLS}-T_A \\ V_{CC}=3.3~V,~F_{MPL}=16~kHz~(divided~by~2) \\ Subsleep~mode~with~the~external~clock~operating$

$I_{CCT}-T_A \\ V_{CC}=3.3 \text{ V, } F_{MPL}=16 \text{ kHz (divided by 2)} \\ Watch mode with the external clock operating}$

$I_{CCTS}-T_A \\ V_{CC}=3.3~V,~F_{MP}=2,~4,~8,~10,~16~MHz~(divided~by~2) \\ Time-base~timer~mode~with~the~external~clock~operating$

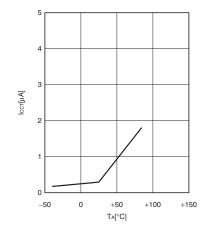

## **Output voltage characteristics**

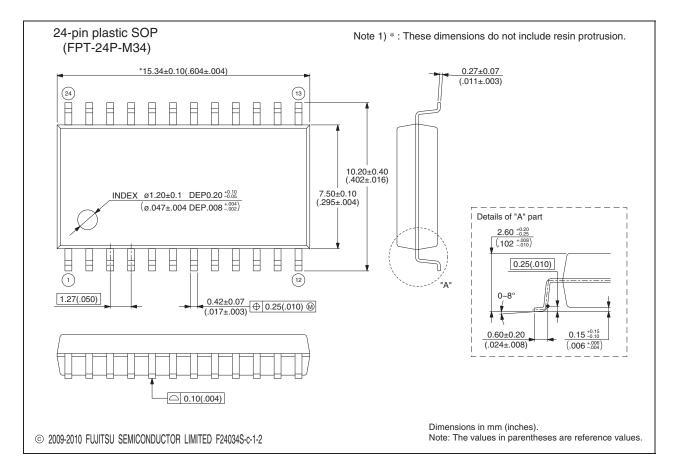

| 24-pin plastic SOP | Lead pitch                     | 1.27 mm            |

|--------------------|--------------------------------|--------------------|

|                    | Package width × package length | 7.50 mm × 15.34 mm |

|                    | Lead shape                     | Gullwing           |

|                    | Lead bend direction            | Normal bend        |

|                    | Sealing method                 | Plastic mold       |

|                    | Mounting height                | 2.80 mm MAX        |

| (FPT-24P-M34)      | Weight                         | 0.44 g             |

(Continued)