Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | F <sup>2</sup> MC-8FX                                                          |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 16MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, UART/USART                                      |

| Peripherals                | POR, PWM, WDT                                                                  |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 36KB (36K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                    |

| Data Converters            | A/D 6x8/12b                                                                    |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 32-WQFN Exposed Pad                                                            |

| Supplier Device Package    | 32-QFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f656lwqn-g-sne1 |

|                            |                                                                                |

# 1. Product Line-up

| Part number                      |                                                                                               |                                |                                     |                                                        |                                                               |               |                       |                 |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|---------------|-----------------------|-----------------|--|--|

|                                  | MB95F652E                                                                                     | MB95F653E                      | MB95F654E                           | MB95F656E                                              | MB95F652L                                                     | MB95F653L     | MB95F654L             | MB95F656L       |  |  |

| Parameter                        |                                                                                               |                                |                                     |                                                        |                                                               |               |                       |                 |  |  |

| Туре                             |                                                                                               |                                |                                     | Flash mem                                              | ory product                                                   |               |                       |                 |  |  |

| Clock supervisor counter         | It supervises                                                                                 | the main clock                 | coscillation ar                     | d the subclocl                                         | c oscillation.                                                |               |                       |                 |  |  |

| Flash memory capacity            | 8 Kbyte                                                                                       | 12 Kbyte                       | 20 Kbyte                            | 36 Kbyte                                               | 8 Kbyte                                                       | 12 Kbyte      | 20 Kbyte              | 36 Kbyte        |  |  |

| RAM capacity                     | 256 bytes                                                                                     | 512 bytes                      | 1024 bytes                          | 1024 bytes                                             | 256 bytes                                                     | 512 bytes     | 1024 bytes            | 1024 bytes      |  |  |

| Power-on reset                   |                                                                                               |                                |                                     | Ye                                                     | es                                                            |               |                       |                 |  |  |

| Low-voltage detection reset      |                                                                                               | Y                              | es                                  |                                                        |                                                               | N             | Ю                     |                 |  |  |

| Reset input                      |                                                                                               | Selected thro                  | ough software                       |                                                        |                                                               | With dedicate | ed reset input        |                 |  |  |

| CPU functions                    | <ul><li>Instruction I</li><li>Instruction I</li><li>Data bit Ien</li><li>Minimum in</li></ul> | ength                          |                                     |                                                        |                                                               |               |                       |                 |  |  |

| General-purpose                  | <ul><li>I/O port</li><li>CMOS I/O</li><li>N-ch open of</li></ul>                              |                                | : 21<br>: 17<br>: 4                 |                                                        | <ul><li>I/O port</li><li>CMOS I/O</li><li>N-ch open</li></ul> |               | : 20<br>: 17<br>: 3   |                 |  |  |

| Time-base timer                  | Interval time:                                                                                | 0.256 ms to 8                  | .3 s (external                      | clock frequenc                                         | y = 4 MHz)                                                    |               |                       |                 |  |  |

| Hardware/software watchdog timer |                                                                                               | lation clock at                | 10 MHz: 105<br>used as the s        | ms (Min)<br>source clock of                            | f the software                                                | watchdog time | er.                   |                 |  |  |

| Wild register                    | It can be used                                                                                | d to replace 3                 | bytes of data.                      |                                                        |                                                               |               |                       |                 |  |  |

| LIN-UART                         | <ul><li>It has a full</li><li>Both clock s</li></ul>                                          | duplex double<br>synchronous s | e buffer.<br>serial data trar       | can be selecte<br>sfer and clock<br>master or a Ll     | asynchronou                                                   |               | er.<br>ransfer are en | abled.          |  |  |

| 8/12-bit                         | 6 channels                                                                                    |                                |                                     |                                                        |                                                               |               |                       |                 |  |  |

| A/D converter                    | 8-bit or 12-bit                                                                               | resolution car                 | n be selected.                      |                                                        |                                                               |               |                       |                 |  |  |

|                                  | 2 channels                                                                                    |                                |                                     |                                                        |                                                               |               |                       |                 |  |  |

| 8/16-bit<br>composite timer      | <ul><li>It has the fo</li><li>Count clock</li></ul>                                           | llowing function               | ons: interval tir<br>ected from int | it timer × 2 cha<br>mer function, F<br>ernal clocks (s | PWC function,                                                 | PWM function  | n and input ca        | oture function. |  |  |

|                                  | 6 channels                                                                                    |                                |                                     |                                                        |                                                               |               |                       |                 |  |  |

| External interrupt               |                                                                                               |                                |                                     | edge, falling e<br>om different st                     |                                                               |               | e selected.)          |                 |  |  |

| On-chip debug                    | <ul><li>1-wire seria</li><li>It supports</li></ul>                                            |                                | asynchronous                        | mode).                                                 |                                                               |               |                       |                 |  |  |

| Pin n                                          | 0.                        |          | I/O                           |                                                |             | I/O type |                  |      |

|------------------------------------------------|---------------------------|----------|-------------------------------|------------------------------------------------|-------------|----------|------------------|------|

| SOP24* <sup>1</sup> ,<br>TSSOP24* <sup>2</sup> | QFN32* <sup>3</sup>       | Pin name | circuit<br>type* <sup>4</sup> | Function                                       | Input       | Output   | OD* <sup>5</sup> | PU*6 |

| 16                                             | 18                        | P00      | Е                             | General-purpose I/O port                       | Hysteresis/ | CMOS     |                  | О    |

| 10                                             | 10                        | AN00     |                               | 8/12-bit A/D converter analog input pin        | analog      | CIVIOS   | _                |      |

| 17                                             | 18 P01 General-purpose I/ |          | General-purpose I/O port      | Hysteresis/                                    | CMOS        |          | О                |      |

| 17                                             | 10                        | AN01     | L                             | 8/12-bit A/D converter analog input pin        | analog      | CIVIOS   | _                | U    |

|                                                |                           | P02      |                               | General-purpose I/O port                       |             |          |                  |      |

| 18                                             | 20                        | INT02    | Е                             | External interrupt input pin                   | Hysteresis/ | CMOS     | _                | O    |

| 10                                             | 20                        | AN02     |                               | 8/12-bit A/D converter analog input pin        | analog      |          |                  |      |

|                                                |                           | SCK      |                               | LIN-UART clock I/O pin                         |             |          |                  |      |

|                                                |                           | P03      |                               | General-purpose I/O port                       |             |          |                  |      |

| 10                                             | 24                        | INT03    | Е                             | External interrupt input pin                   | Hysteresis/ | CMOS     |                  |      |

| 19                                             | 19 21                     | AN03     | _                             | 8/12-bit A/D converter analog input pin        | analog      | CIVIOS   | _                | О    |

|                                                |                           | SOT      |                               | LIN-UART data output pin                       |             |          |                  |      |

|                                                |                           | P04      |                               | General-purpose I/O port                       |             |          |                  | O    |

|                                                |                           | INT04    |                               | External interrupt input pin                   |             |          |                  |      |

| 20                                             | 22                        | AN04     | F                             | 8/12-bit A/D converter analog input pin        | CMOS/       | CMOS     | _                |      |

| 20                                             | 22                        | SIN      |                               | LIN-UART data input pin                        | analog      | Sivies   |                  |      |

|                                                |                           | EC0      |                               | 8/16-bit composite timer ch. 0 clock input pin |             |          |                  |      |

|                                                |                           | P05      |                               | General-purpose I/O port<br>High-current pin   |             |          |                  |      |

| 21                                             | 23                        | INT05    | K                             | External interrupt input pin                   | Hysteresis/ | CMOS     | _                | О    |

|                                                |                           | AN05     |                               | 8/12-bit A/D converter analog input pin        | analog      |          |                  |      |

|                                                |                           | TO00     |                               | 8/16-bit composite timer ch. 0 output pin      |             |          |                  |      |

|                                                |                           | P06      |                               | General-purpose I/O port<br>High-current pin   |             |          |                  |      |

| 22                                             | 24                        | INT06    | D                             | External interrupt input pin                   | Hysteresis  | CMOS     | _                | О    |

|                                                |                           | TO01     |                               | 8/16-bit composite timer ch. 0 output pin      |             |          |                  |      |

|                                                |                           | P07      |                               | General-purpose I/O port<br>High-current pin   |             | 0.1.5.5  | _                |      |

| 23                                             | 26                        | INT07    | K                             | External interrupt input pin                   | Hysteresis  | CMOS     |                  | О    |

|                                                |                           | TO10     |                               | 8/16-bit composite timer ch. 1 output pin      |             |          |                  |      |

### (Continued)

| Pin n                                          | 0.                  |          | 1/0                           |                                                |            | I/O type |                  |      |  |  |

|------------------------------------------------|---------------------|----------|-------------------------------|------------------------------------------------|------------|----------|------------------|------|--|--|

| SOP24* <sup>1</sup> ,<br>TSSOP24* <sup>2</sup> | QFN32* <sup>3</sup> | Pin name | circuit<br>type* <sup>4</sup> | Function                                       | Input      | Output   | OD* <sup>5</sup> | PU*6 |  |  |

|                                                |                     | P12      |                               | General-purpose I/O port                       |            |          | 0                |      |  |  |

| 24                                             | 25                  | DBG      | Н                             | DBG input pin                                  | Hysteresis | CMOS     |                  | _    |  |  |

| 24                                             | EC0                 | EC0      |                               | 8/16-bit composite timer ch. 0 clock input pin | ,          |          |                  |      |  |  |

|                                                | 11                  |          |                               |                                                |            |          |                  |      |  |  |

|                                                | 12                  |          |                               |                                                |            | _        | _                | _    |  |  |

|                                                | 13                  |          |                               |                                                |            |          |                  |      |  |  |

|                                                | 14                  | NC       |                               | It is an internally connected pin. Always      |            |          |                  |      |  |  |

| _                                              | 27                  | INC      | _                             | leave it unconnected.                          | _          |          |                  |      |  |  |

|                                                | 28                  |          |                               |                                                |            |          |                  |      |  |  |

|                                                | 29                  |          |                               |                                                |            |          |                  |      |  |  |

|                                                | 30                  |          |                               |                                                |            |          |                  |      |  |  |

O: Available

\*1: FPT-24P-M34

\*2: FPT-24P-M10

\*3: LCC-32P-M19

\*4: For the I/O circuit types, see "6. I/O Circuit Type".

\*5: N-ch open drain

\*6: Pull-up

\*7: In I<sup>2</sup>C mode, the pin becomes an N-ch open drain pin.

### 11. CPU Core

### Memory space

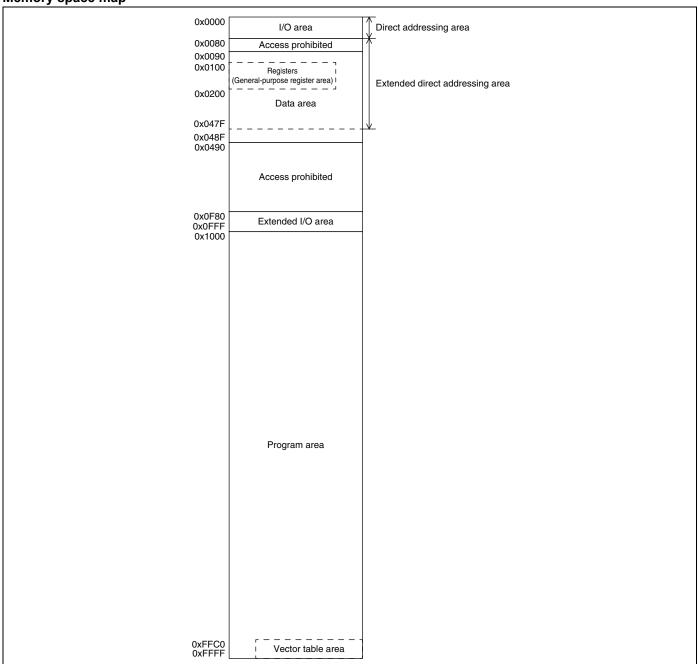

The memory space of the MB95650L Series is 64 Kbyte in size, and consists of an I/O area, an extended I/O area, a data area, and a program area. The memory space includes areas intended for specific purposes such as general-purpose registers and a vector table. The memory maps of the MB95650L Series are shown below.

### **Memory maps**

|                                                | MB95F652E/F652L                                    |                                                | MB95F653E/F653L                                    |                                                        | MB95F654E/F654L                                     |                                                    | MB95F656E/F656L                                     |

|------------------------------------------------|----------------------------------------------------|------------------------------------------------|----------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------|-----------------------------------------------------|

| 0x0000<br>0x0080<br>0x0090<br>0x0100<br>0x0190 | I/O area Access prohibited RAM 256 bytes Registers | 0x0000<br>0x0080<br>0x0090<br>0x0100<br>0x0200 | I/O area Access prohibited RAM 512 bytes Registers | 0x0000<br>- 0x0080<br>- 0x0090<br>- 0x0100<br>- 0x0200 | I/O area Access prohibited RAM 1024 bytes Registers | 0x0000<br>- 0x0080<br>- 0x0090<br>0x0100<br>0x0200 | I/O area Access prohibited RAM 1024 bytes Registers |

|                                                | Access prohibited                                  | 0x0290 -                                       | Access prohibited                                  | 0x0490 -                                               | Access prohibited                                   | - 0x0490 -                                         | Access prohibited                                   |

| 0x0F80<br>0x1000                               | Extended I/O area                                  | 0x0F80                                         | Extended I/O area                                  | 0x0F80 -                                               | Extended I/O area                                   | 0x0F80 -                                           | Extended I/O area                                   |

| 0x2000                                         | Flash memory 4 Kbyte                               | 0x1000                                         | Flash memory 4 Kbyte                               | 0x2000                                                 | Flash memory 4 Kbyte                                | 0x2000                                             | Flash memory 4 Kbyte                                |

|                                                |                                                    |                                                | Access prohibited                                  |                                                        | Access prohibited                                   | 0x8000 -                                           | Access prohibited                                   |

|                                                | Access prohibited                                  |                                                |                                                    | 0xC000 -                                               |                                                     |                                                    | Flash memory 32 Kbyte                               |

|                                                |                                                    |                                                |                                                    |                                                        |                                                     |                                                    |                                                     |

| 0xF000 -                                       |                                                    | 0xE000 -                                       | Flash memory 8 Kbyte                               | -                                                      | Flash memory 16 Kbyte                               |                                                    |                                                     |

### 12. Memory Space

The memory space of the MB95650L Series is 64 Kbyte in size, and consists of an I/O area, an extended I/O area, a data area, and a program area. The memory space includes areas for specific applications such as general-purpose registers and a vector table.

### I/O area (addresses: 0x0000 to 0x007F)

- This area contains the control registers and data registers for built-in peripheral functions.

- As the I/O area forms part of the memory space, it can be accessed in the same way as the memory. It can also be accessed at high-speed by using direct addressing instructions.

### Extended I/O area (addresses: 0x0F80 to 0x0FFF)

- This area contains the control registers and data registers for built-in peripheral functions.

- · As the extended I/O area forms part of the memory space, it can be accessed in the same way as the memory.

#### Data area

- Static RAM is incorporated in the data area as the internal data area.

- The internal RAM size varies according to product.

- The RAM area from 0x0090 to 0x00FF can be accessed at high-speed by using direct addressing instructions.

- In MB95F656E/F656L, the area from 0x0090 to 0x047F is an extended direct addressing area. It can be accessed at high-speed by direct addressing instructions with a direct bank pointer set.

- In MB95F654E/F654L, the area from 0x0090 to 0x047F is an extended direct addressing area. It can be accessed at high-speed by direct addressing instructions with a direct bank pointer set.

- In MB95F653E/F653L, the area from 0x0090 to 0x028F is an extended direct addressing area. It can be accessed at high-speed by direct addressing instructions with a direct bank pointer set.

- In MB95F652E/F652L, the area from 0x0090 to 0x018F is an extended direct addressing area. It can be accessed at high-speed by direct addressing instructions with a direct bank pointer set.

- In MB95F653E/F653L/F654E/F656L/F656E/F656L, the area from 0x0100 to 0x01FF can be used as a general-purpose register area.

- In MB95F652E/F652L, the area from 0x0100 to 0x018F can be used as a general-purpose register area.

#### Program area

- The Flash memory is incorporated in the program area as the internal program area.

- · The Flash memory size varies according to product.

- The area from 0xFFC0 to 0xFFFF is used as the vector table.

- The area from 0xFFBB to 0xFFBF is used to store data of the non-volatile register.

Memory space map

# 14. I/O Map

| Address                | Register abbreviation | Register name                                         | R/W | Initial value |

|------------------------|-----------------------|-------------------------------------------------------|-----|---------------|

| 0x0000                 | PDR0                  | Port 0 data register                                  | R/W | 0b00000000    |

| 0x0001                 | DDR0                  | Port 0 direction register                             | R/W | 0b00000000    |

| 0x0002                 | PDR1                  | Port 1 data register                                  | R/W | 0b00000000    |

| 0x0003                 | DDR1                  | Port 1 direction register                             | R/W | 0b00000000    |

| 0x0004                 | _                     | (Disabled)                                            | _   | _             |

| 0x0005                 | WATR                  | Oscillation stabilization wait time setting register  | R/W | 0b11111111    |

| 0x0006                 | PLLC                  | PLL control register                                  | R/W | 0b000X0000    |

| 0x0007                 | SYCC                  | System clock control register                         | R/W | 0bXXX11011    |

| 0x0008                 | STBC                  | Standby control register                              | R/W | 0b00000000    |

| 0x0009                 | RSRR                  | Reset source register                                 | R/W | 0b000XXXXX    |

| 0x000A                 | TBTC                  | Time-base timer control register                      | R/W | 0b00000000    |

| 0x000B                 | WPCR                  | Watch prescaler control register                      | R/W | 0b00000000    |

| 0x000C                 | WDTC                  | Watchdog timer control register                       | R/W | 0b00XX0000    |

| 0x000D                 | SYCC2                 | System clock control register 2                       | R/W | 0bXXXX0011    |

| 0x000E<br>to<br>0x0015 | _                     | (Disabled)                                            | _   | _             |

| 0x0016                 | PDR6                  | Port 6 data register                                  | R/W | 0b00000000    |

| 0x0017                 | DDR6                  | Port 6 direction register                             | R/W | 0b00000000    |

| 0x0018<br>to<br>0x0027 | _                     | (Disabled)                                            | _   | _             |

| 0x0028                 | PDRF                  | Port F data register                                  | R/W | 0b00000000    |

| 0x0029                 | DDRF                  | Port F direction register                             | R/W | 0b00000000    |

| 0x002A                 | PDRG                  | Port G data register                                  | R/W | 0b00000000    |

| 0x002B                 | DDRG                  | Port G direction register                             | R/W | 0b00000000    |

| 0x002C                 | PUL0                  | Port 0 pull-up register                               | R/W | 0b00000000    |

| 0x002D<br>to<br>0x0032 | _                     | (Disabled)                                            |     | _             |

| 0x0033                 | PUL6                  | Port 6 pull-up register                               | R/W | 0b00000000    |

| 0x0034                 | _                     | (Disabled)                                            | _   | _             |

| 0x0035                 | PULG                  | Port G pull-up register                               | R/W | 0b00000000    |

| 0x0036                 | T01CR1                | 8/16-bit composite timer 01 status control register 1 | R/W | 0b00000000    |

| 0x0037                 | T00CR1                | 8/16-bit composite timer 00 status control register 1 | R/W | 0b00000000    |

| 0x0038                 | T11CR1                | 8/16-bit composite timer 11 status control register 1 | R/W | 0b00000000    |

| 0x0039                 | T10CR1                | 8/16-bit composite timer 10 status control register 1 | R/W | 0b00000000    |

| 0x003A<br>to<br>0x0048 | _                     | (Disabled)                                            | _   | _             |

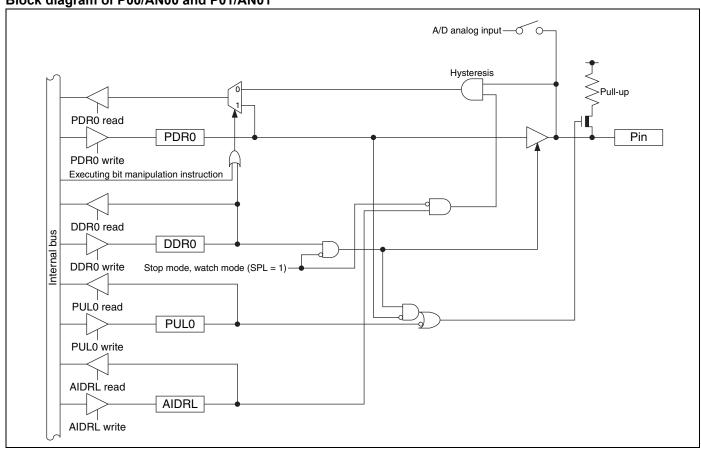

### 15.1 Port 0

Port 0 is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95650L Series Hardware Manual".

#### 15.1.1 Port 0 configuration

Port 0 is made up of the following elements.

- General-purpose I/O pins/peripheral function I/O pins

- Port 0 data register (PDR0)

- Port 0 direction register (DDR0)

- Port 0 pull-up register (PUL0)

- A/D input disable register (lower) (AIDRL)

### 15.1.2 Block diagrams of port 0

### P00/AN00 pin

This pin has the following peripheral function:

• 8/12-bit A/D converter analog input pin (AN00)

### P01/AN01 pin

This pin has the following peripheral function:

• 8/12-bit A/D converter analog input pin (AN01)

Block diagram of P00/AN00 and P01/AN01

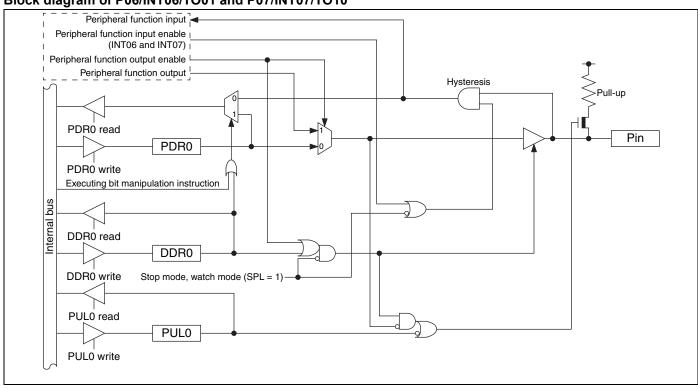

### P06/INT06/TO01 pin

This pin has the following peripheral functions:

- External interrupt input pin (INT06)

- 8/16-bit composite timer ch. 0 output pin (TO01)

### P07/INT07/TO10 pin

This pin has the following peripheral functions:

- External interrupt input pin (INT07)

- 8/16-bit composite timer ch. 1 output pin (TO10)

### Block diagram of P06/INT06/TO01 and P07/INT07/TO10

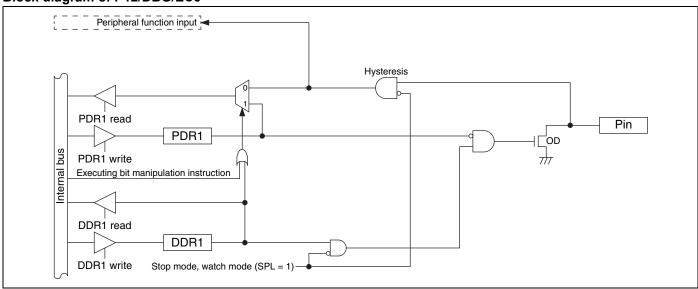

### 15.2 Port 1

Port 1 is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95650L Series Hardware Manual".

#### 15.2.1 Port 1 configuration

Port 1 is made up of the following elements.

- General-purpose I/O pins/peripheral function I/O pins

- Port 1 data register (PDR1)

- Port 1 direction register (DDR1)

#### 15.2.2 (2)Block diagrams of port 1

### P12/DBG/EC0 pin

This pin has the following peripheral functions:

- DBG input pin (DBG)

- 8/16-bit composite timer ch. 0 clock input pin (EC0)

### Block diagram of P12/DBG/EC0

### 15.3.3 Port 6 registers

# Port 6 register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                               |  |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|-------------------------------------|--|--|--|--|--|

| PDR6                  | 0    | Pin state is "L" level. | PDR6 value is "0".                          | As output port, outputs "L" level.  |  |  |  |  |  |

| FDR0                  | 1    | Pin state is "H" level. | PDR6 value is "1".                          | As output port, outputs "H" level.* |  |  |  |  |  |

| DDR6                  | 0    |                         | Port input enabled                          |                                     |  |  |  |  |  |

| DDRO                  | 1    |                         | Port output enabled                         |                                     |  |  |  |  |  |

| PUL6                  | 0    |                         | Pull-up disabled                            |                                     |  |  |  |  |  |

| FOLO                  | 1    | Pull-up enabled         |                                             |                                     |  |  |  |  |  |

<sup>\*:</sup> If the pin is an N-ch open drain pin, the pin state becomes Hi-Z.

# Correspondence between registers and pins for port 6

|          |   | Correspondence between related register bits and pins |   |      |      |      |   |   |  |  |  |

|----------|---|-------------------------------------------------------|---|------|------|------|---|---|--|--|--|

| Pin name | - | -                                                     | - | P64  | P63  | P62  | - | - |  |  |  |

| PDR6     |   |                                                       |   |      |      |      |   |   |  |  |  |

| DDR6     | - | -                                                     | - | bit4 | bit3 | bit2 | - | - |  |  |  |

| PUL6     |   |                                                       |   |      |      |      |   |   |  |  |  |

#### 15.3.4 Port 6 operations

#### Operation as an output port

- A pin becomes an output port if the bit in the DDR6 register corresponding to that pin is set to "1".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When a pin is used as an output port, it outputs the value of the PDR6 register to external pins.

- · If data is written to the PDR6 register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDR6 register returns the PDR6 register value.

#### Operation as an input port

- A pin becomes an input port if the bit in the DDR6 register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- If data is written to the PDR6 register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDR6 register returns the pin value. However, if the read-modify-write (RMW) type of instruction is used to read the PDR6 register, the PDR6 register value is returned.

#### Operation as a peripheral function output pin

- A pin becomes a peripheral function output pin if the peripheral output function is enabled by setting the output enable bit of a peripheral function corresponding to that pin.

- The pin value can be read from the PDR6 register even if the peripheral function output is enabled. Therefore, the output value of a peripheral function can be read by the read operation on the PDR6 register. However, if the read-modify-write (RMW) type of instruction is used to read the PDR6 register, the PDR6 register value is returned.

#### Operation as a peripheral function input pin

- To set a pin as an input port, set the bit in the DDR6 register corresponding to the input pin of a peripheral function to "0".

- Reading the PDR6 register returns the pin value, regardless of whether the peripheral function uses that pin as its input pin.

However, if the read-modify-write (RMW) type of instruction is used to read the PDR6 register, the PDR6 register value is returned.

### Operation at reset

If the CPU is reset, all bits in the DDR6 register are initialized to "0" and port input is enabled.

#### Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDR6 register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

### Operation of the pull-up register

Setting the bit in the PUL6 register to "1" makes the pull-up resistor be internally connected to the pin. When the pin output is "L" level, the pull-up resistor is disconnected regardless of the value of the PUL6 register.

### 15.4.3 Port F registers

### Port F register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                               |  |  |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|-------------------------------------|--|--|--|--|--|--|

| PDRF                  | 0    | Pin state is "L" level. | PDRF value is "0".                          | As output port, outputs "L" level.  |  |  |  |  |  |  |

| FDRF                  | 1    | Pin state is "H" level. | PDRF value is "1".                          | As output port, outputs "H" level.* |  |  |  |  |  |  |

| DDRF                  | 0    |                         | Port input enabled                          |                                     |  |  |  |  |  |  |

| DDRF                  | 1    |                         | Port output enabled                         |                                     |  |  |  |  |  |  |

<sup>\*:</sup> If the pin is an N-ch open drain pin, the pin state becomes Hi-Z.

# Correspondence between registers and pins for port F

|          | Correspondence between related register bits and pins |   |   |              |   |      |      |      |  |  |

|----------|-------------------------------------------------------|---|---|--------------|---|------|------|------|--|--|

| Pin name | -                                                     | - | - | -            | - | PF2* | PF1  | PF0  |  |  |

| PDRF     |                                                       |   |   |              |   | bit2 | bit1 | bit0 |  |  |

| DDRF     | -                                                     | - | - | <del>-</del> | - | DILZ | DILI | טונט |  |  |

<sup>\*:</sup> PF2/RST is the dedicated reset pin on MB95F652L/F653L/F654L/F656L.

# 16. Interrupt Source Table

| Interrupt source                        | Interrupt request | Vector tab | le address |          | evel setting<br>ister | Priority order of interrupt sources of the same level |

|-----------------------------------------|-------------------|------------|------------|----------|-----------------------|-------------------------------------------------------|

|                                         | number            | Upper      | Lower      | Register | Bit                   | (occurring simultaneously)                            |

| External interrupt ch. 4                | IRQ00             | 0xFFFA     | 0xFFFB     | ILR0     | L00 [1:0]             | High                                                  |

| External interrupt ch. 5                | IRQ01             | 0xFFF8     | 0xFFF9     | ILR0     | L01 [1:0]             | 1 🛕                                                   |

| External interrupt ch. 2                | IRQ02             | 0xFFF6     | 0xFFF7     | ILR0     | L02 [1:0]             | ]                                                     |

| External interrupt ch. 6                | IRQ02             | UXFFF0     | UXFFF1     | ILKU     | LUZ [1.0]             |                                                       |

| External interrupt ch. 3                | IDO03             | 0,45554    | 0xFFF5     | II D0    | 1.02 [4:0]            | 1                                                     |

| External interrupt ch. 7                | IRQ03             | 0xFFF4     | UXFFF5     | ILR0     | L03 [1:0]             |                                                       |

| Low-voltage detection interrupt circuit | IDO04             | ٥٠،٢٢٢٥    | ٥٧٢٢٢٥     | II D4    | 1.04 [4.0]            |                                                       |

| UART/SIO ch. 0                          | IRQ04             | 0xFFF2     | 0xFFF3     | ILR1     | L04 [1:0]             |                                                       |

| 8/16-bit composite timer ch. 0 (lower)  | IRQ05             | 0xFFF0     | 0xFFF1     | ILR1     | L05 [1:0]             |                                                       |

| 8/16-bit composite timer ch. 0 (upper)  | IRQ06             | 0xFFEE     | 0xFFEF     | ILR1     | L06 [1:0]             |                                                       |

| LIN-UART (reception)                    | IRQ07             | 0xFFEC     | 0xFFED     | ILR1     | L07 [1:0]             |                                                       |

| LIN-UART (transmission)                 | IRQ08             | 0xFFEA     | 0xFFEB     | ILR2     | L08 [1:0]             | -                                                     |

| _                                       | IRQ09             | 0xFFE8     | 0xFFE9     | ILR2     | L09 [1:0]             |                                                       |

| I <sup>2</sup> C bus interface ch. 1    | IRQ10             | 0xFFE6     | 0xFFE7     | ILR2     | L10 [1:0]             | 1                                                     |

| _                                       | IRQ11             | 0xFFE4     | 0xFFE5     | ILR2     | L11 [1:0]             | 1                                                     |

| _                                       | IRQ12             | 0xFFE2     | 0xFFE3     | ILR3     | L12 [1:0]             | 1                                                     |

| _                                       | IRQ13             | 0xFFE0     | 0xFFE1     | ILR3     | L13 [1:0]             | 1                                                     |

| 8/16-bit composite timer ch. 1 (upper)  | IRQ14             | 0xFFDE     | 0xFFDF     | ILR3     | L14 [1:0]             | 1                                                     |

| _                                       | IRQ15             | 0xFFDC     | 0xFFDD     | ILR3     | L15 [1:0]             | 1                                                     |

| I <sup>2</sup> C bus interface ch. 0    | IRQ16             | 0xFFDA     | 0xFFDB     | ILR4     | L16 [1:0]             | 1                                                     |

| _                                       | IRQ17             | 0xFFD8     | 0xFFD9     | ILR4     | L17 [1:0]             | 1                                                     |

| 8/12-bit A/D converter                  | IRQ18             | 0xFFD6     | 0xFFD7     | ILR4     | L18 [1:0]             | -                                                     |

| Time-base timer                         | IRQ19             | 0xFFD4     | 0xFFD5     | ILR4     | L19 [1:0]             | 1                                                     |

| Watch prescaler                         | IRQ20             | 0xFFD2     | 0xFFD3     | ILR5     | L20 [1:0]             | 1                                                     |

| _                                       | IRQ21             | 0xFFD0     | 0xFFD1     | ILR5     | L21 [1:0]             | 1                                                     |

| 8/16-bit composite timer ch. 1 (lower)  | IRQ22             | 0xFFCE     | 0xFFCF     | ILR5     | L22 [1:0]             | 1                                                     |

| Flash memory                            | IRQ23             | 0xFFCC     | 0xFFCD     | ILR5     | L23 [1:0]             | Low                                                   |

(V<sub>CC</sub> = 3.0 V±10%, V<sub>SS</sub> = 0.0 V,  $T_A$  = -40 °C to +85 °C)

|                       |                    |                                    |                                                                                                                           | (*66 |       | 10 70, 155        | - U.U V | , 1 <sub>A</sub> 10 0 to 100 0) |

|-----------------------|--------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------|---------|---------------------------------|

| Parameter             | Symbol             | Pin name                           | Condition                                                                                                                 |      | Value |                   | Unit    | Remarks                         |

| Parameter             | Symbol             | Fill liallie                       | Condition                                                                                                                 | Min  | Typ*1 | Max* <sup>6</sup> | Offic   | Remarks                         |

|                       | I <sub>CCTS</sub>  | V <sub>CC</sub><br>(External clock | F <sub>CH</sub> = 32 MHz<br>Time-base timer mode<br>T <sub>A</sub> = +25 °C                                               | _    | 450   | 500               | μΑ      |                                 |

|                       | I <sub>CCH</sub>   | operation)                         | Substop mode<br>T <sub>A</sub> = +25 °C                                                                                   | _    | 0.7   | 5                 | μΑ      |                                 |

|                       | I <sub>PLVD</sub>  | V <sub>CC</sub>                    | Current consumption of<br>the low-voltage<br>detection reset circuit in<br>operation                                      | _    | 6     | 26                | μΑ      |                                 |

| Power supply          | I <sub>ILVD</sub>  |                                    | Current consumption of<br>the low-voltage<br>detection interrupt<br>circuit operating in<br>normal mode                   | _    | 6     | 14                | μΑ      |                                 |

| current* <sup>7</sup> | I <sub>ILVDL</sub> |                                    | Current consumption of<br>the low-voltage<br>detection interrupt<br>circuit operating in low<br>power consumption<br>mode | _    | 3     | 10                | μΑ      |                                 |

|                       | I <sub>CRH</sub>   |                                    | Current consumption of the main CR oscillator                                                                             | _    | 270   | 320               | μΑ      |                                 |

|                       | I <sub>CRL</sub>   |                                    | Current consumption of<br>the sub-CR oscillator<br>oscillating at 100 kHz                                                 | _    | 5     | 20                | μΑ      |                                 |

|                       | I <sub>SOSC</sub>  |                                    | Current consumption of the suboscillator                                                                                  | _    | 0.8   | 7                 | μΑ      |                                 |

<sup>\*1:</sup>  $V_{CC}$  = 3.0 V,  $T_A$  = +25 °C

- See "18.4. AC Characteristics 18.4.1. Clock Timing" for F<sub>CH</sub>, F<sub>CL</sub>, F<sub>CRH</sub>, F<sub>MCRPLL</sub> and F<sub>MPLL</sub>.

- See "18.4. AC Characteristics 18.4.2. Source Clock/Machine Clock" for F<sub>MP</sub> and F<sub>MPI</sub>.

- The power supply current in subclock mode is determined by the external clock. In subclock mode, current consumption in using

the crystal oscillator is higher than that in using the external clock. When the crystal oscillator is used, the power supply current

is the sum of adding I<sub>SOSC</sub> (current consumption of the suboscillator) to the power supply current in using the external clock.

For details of controlling the subclock, refer to "Chapter 3 Clock Controller" And "chapter 24 System Configuration Register" in

"New 8FX MB95650L Series Hardware Manual".

<sup>\*2:</sup> When  $V_{CC}$  is smaller than 4.5 V, the condition becomes  $I_{OH} = -2$  mA.

<sup>\*3:</sup> When  $V_{CC}$  is smaller than 4.5 V, the condition becomes  $I_{OH} = -4$  mA.

<sup>\*4:</sup> When  $V_{CC}$  is smaller than 4.5 V, the condition becomes  $I_{OL}$  = 2 mA.

<sup>\*5:</sup> When  $V_{CC}$  is smaller than 4.5 V, the condition becomes  $I_{OH}$  = 6 mA.

<sup>\*6:</sup>  $V_{CC}$  = 3.3 V,  $T_A$  = +85 °C (unless otherwise specified)

<sup>\*7: •</sup> The power supply current is determined by the external clock. When the low-voltage detection reset circuit is selected, the power supply current is the sum of adding the current consumption of the low-voltage detection reset circuit (I<sub>PLVD</sub>) to one of the values from I<sub>CC</sub> to I<sub>CCH</sub>. In addition, when the low-voltage detection reset circuit and a CR oscillator are selected, the power supply current is the sum of adding up the current consumption of the low-voltage detection reset circuit (I<sub>PLVD</sub>), the current consumption of the CR oscillator (I<sub>CRH</sub> or I<sub>CRL</sub>) and one of the values from I<sub>CC</sub> to I<sub>CCH</sub>. In on-chip debug mode, the main CR oscillator (I<sub>CRH</sub>) and the low-voltage detection reset circuit are always in operation, and current consumption therefore increases accordingly.

### 18.4.7 Low-vo Itage Detection

### Normal mode

(V<sub>CC</sub> = 1.8 V to 5.5 V, V<sub>SS</sub> = 0.0 V,  $T_A$  = –40 °C to +85 °C)

| D                                                         | Symbol              | Value |      |      | 11.24 | Danie allea                                                                                                             |  |

|-----------------------------------------------------------|---------------------|-------|------|------|-------|-------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                 |                     | Min   | Тур  | Max  | Unit  | Remarks                                                                                                                 |  |

| Reset release voltage                                     | $V_{PDL+}$          | 1.88  | 2.03 | 2.18 | V     | At power supply rise                                                                                                    |  |

| Reset detection voltage                                   | $V_{\mathrm{PDL}-}$ | 1.8   | 1.93 | 2.06 | V     | At power supply fall                                                                                                    |  |

| Interrupt release voltage 0                               | V <sub>IDL0+</sub>  | 2.13  | 2.3  | 2.47 | V     | At power supply rise                                                                                                    |  |

| Interrupt detection voltage 0                             | V <sub>IDL0-</sub>  | 2.05  | 2.2  | 2.35 | V     | At power supply fall                                                                                                    |  |

| Interrupt release voltage 1                               | V <sub>IDL1+</sub>  | 2.41  | 2.6  | 2.79 | V     | At power supply rise                                                                                                    |  |

| Interrupt detection voltage 1                             | V <sub>IDL1-</sub>  | 2.33  | 2.5  | 2.67 | V     | At power supply fall                                                                                                    |  |

| Interrupt release voltage 2                               | V <sub>IDL2+</sub>  | 2.69  | 2.9  | 3.11 | V     | At power supply rise                                                                                                    |  |

| Interrupt detection voltage 2                             | V <sub>IDL2</sub>   | 2.61  | 2.8  | 2.99 | V     | At power supply fall                                                                                                    |  |

| Interrupt release voltage 3                               | V <sub>IDL3+</sub>  | 3.06  | 3.3  | 3.54 | V     | At power supply rise                                                                                                    |  |

| Interrupt detection voltage 3                             | V <sub>IDL3</sub>   | 2.98  | 3.2  | 3.42 | V     | At power supply fall                                                                                                    |  |

| Interrupt release voltage 4                               | $V_{\text{IDL4+}}$  | 3.43  | 3.7  | 3.97 | V     | At power supply rise                                                                                                    |  |

| Interrupt detection voltage 4                             | V <sub>IDL4-</sub>  | 3.35  | 3.6  | 3.85 | V     | At power supply fall                                                                                                    |  |

| Interrupt release voltage 5                               | V <sub>IDL5+</sub>  | 3.81  | 4.1  | 4.39 | V     | At power supply rise                                                                                                    |  |

| Interrupt detection voltage 5                             | V <sub>IDL5-</sub>  | 3.73  | 4    | 4.27 | V     | At power supply fall                                                                                                    |  |

| Power supply start voltage                                | $V_{\rm off}$       | _     | _    | 1.6  | V     |                                                                                                                         |  |

| Power supply end voltage                                  | V <sub>on</sub>     | 4.39  | _    | _    | V     |                                                                                                                         |  |

| Power supply voltage change time (at power supply rise)   | t <sub>r</sub>      | 697.5 | _    | _    | μs    | Slope of power supply that the reset release signal generates within the rating (V <sub>PDL+</sub> /V <sub>IDL+</sub> ) |  |

| Power supply voltage change time (at power supply fall)   | t <sub>f</sub>      | 697.5 | _    | _    | μs    | Slope of power supply that the reset release signal generates within the rating (V <sub>PDL</sub> _/V <sub>IDL</sub> _) |  |

| Reset release delay time                                  | t <sub>dp1</sub>    | _     | _    | 30   | μs    |                                                                                                                         |  |

| Reset detection delay time                                | t <sub>dp2</sub>    | _     | _    | 30   | μs    |                                                                                                                         |  |

| Interrupt release delay time                              | t <sub>di1</sub>    | _     | _    | 30   | μs    |                                                                                                                         |  |

| Interrupt detection delay time                            | t <sub>di2</sub>    | _     | _    | 30   | μs    |                                                                                                                         |  |

| LVD reset threshold voltage transition stabilization time | t <sub>stb</sub>    |       | _    | 30   | μs    |                                                                                                                         |  |

(V<sub>CC</sub> = 3.0 V to 5.5 V, V<sub>SS</sub> = 0.0 V,  $T_A$  = -40 °C to +85 °C)

| Parameter                                                            | Symbol              | Pin                                                                    | Condition | Valu                              | Unit                             | Remarks   |                                                                                                 |

|----------------------------------------------------------------------|---------------------|------------------------------------------------------------------------|-----------|-----------------------------------|----------------------------------|-----------|-------------------------------------------------------------------------------------------------|

| name                                                                 |                     | Oonaldon                                                               | Min Max   |                                   | Oilit                            | ixeman x3 |                                                                                                 |

| SCL clock "L" width                                                  | t <sub>LOW</sub>    | SCL0,<br>SCL1                                                          |           | (2 + nm/2)t <sub>MCLK</sub> - 20  | _                                | ns        | Master mode                                                                                     |

| SCL clock "H" width                                                  | t <sub>HIGH</sub>   | SCL0,<br>SCL1                                                          |           | (nm/2)t <sub>MCLK</sub> – 20      | (nm/2)t <sub>MCLK</sub> + 20     | ns        | Master mode                                                                                     |

| START<br>condition hold<br>time                                      | t <sub>HD;STA</sub> | SCL0,<br>SCL1,<br>SDA0,<br>SDA1                                        |           | (-1 + nm/2)t <sub>MCLK</sub> – 20 | (-1 + nm)t <sub>MCLK</sub> + 20  |           | Master mode Maximum value is applied when m, n = 1, 8. Otherwise, the minimum value is applied. |

| STOP condition setup time                                            | t <sub>SU;STO</sub> | t <sub>SU;STO</sub>   SCL0,<br>SCL1,<br>SDA0, R = 1.7<br>SDA1 C = 50 p |           | (1 + nm/2)t <sub>MCLK</sub> - 20  | (1 + nm/2)t <sub>MCLK</sub> + 20 | ns        | Master mode                                                                                     |

| START<br>condition setup<br>time                                     | t <sub>SU;STA</sub> | SCL0,<br>SCL1,<br>SDA0,<br>SDA1                                        |           | (1 + nm/2)t <sub>MCLK</sub> - 20  | (1 + nm/2)t <sub>MCLK</sub> + 20 | ns        | Master mode                                                                                     |

| Bus free time<br>between STOP<br>condition and<br>START<br>condition | t <sub>BUF</sub>    | SCL0,<br>SCL1,<br>SDA0,<br>SDA1                                        |           | (2 nm + 4) t <sub>MCLK</sub> – 20 | _                                | ns        |                                                                                                 |

| Data hold time                                                       | t <sub>HD;DAT</sub> | SCL0,<br>SCL1,<br>SDA0,<br>SDA1                                        |           | 3 t <sub>MCLK</sub> – 20          | _                                | ns        | Master mode                                                                                     |

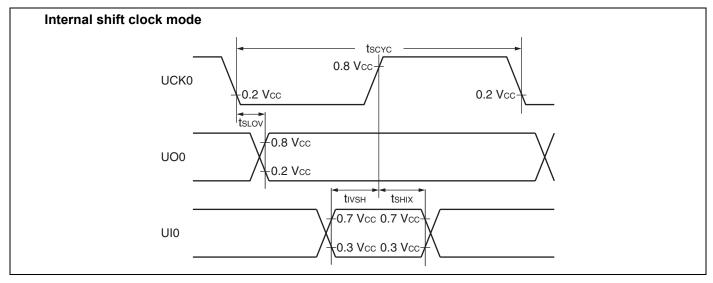

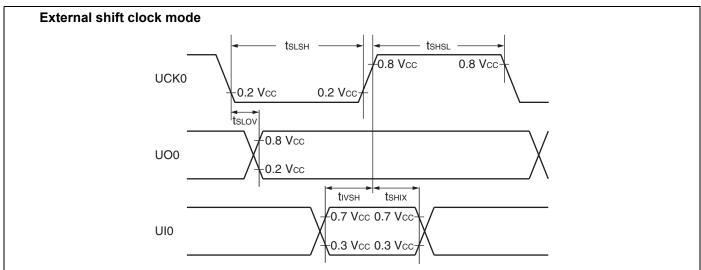

### 18.4.9 UART/SIO, Serial I/O Timing

(V<sub>CC</sub> = 3.0 V to 5.5 V, V<sub>SS</sub> = 0.0 V,  $T_A$  = –40 °C to +85 °C)

| Parameter                                     | Symbol            | Pin name     | Condition                | Value                 |      | Unit |

|-----------------------------------------------|-------------------|--------------|--------------------------|-----------------------|------|------|

| Farameter                                     | Symbol            | Pili lialile | Condition                | Min                   | Max  | Unit |

| Serial clock cycle time                       | t <sub>SCYC</sub> | UCK0         |                          | 4 t <sub>MCLK</sub> * | _    | ns   |

| $UCK \downarrow \rightarrow UO time$          | t <sub>SLOV</sub> | UCK0, UO0    | Internal alask aparation | -190                  | +190 | ns   |

| Valid UI → UCK ↑                              | t <sub>IVSH</sub> | UCK0, UI0    | Internal clock operation | 2 t <sub>MCLK</sub> * | _    | ns   |

| UCK $\uparrow \rightarrow$ valid UI hold time | t <sub>SHIX</sub> | UCK0, UI0    |                          | 2 t <sub>MCLK</sub> * | _    | ns   |

| Serial clock "H" pulse width                  | t <sub>SHSL</sub> | UCK0         |                          | 4 t <sub>MCLK</sub> * | _    | ns   |

| Serial clock "L" pulse width                  | t <sub>SLSH</sub> | UCK0         | External clock operation | 4 t <sub>MCLK</sub> * | _    | ns   |

| $UCK \downarrow \to UO$ time                  | t <sub>SLOV</sub> | UCK0, UO0    |                          | _                     | 190  | ns   |

| Valid UI → UCK ↑                              | t <sub>IVSH</sub> | UCK0, UI0    |                          | 2 t <sub>MCLK</sub> * | _    | ns   |

| UCK $\uparrow \rightarrow$ valid UI hold time | t <sub>SHIX</sub> | UCK0, UI0    |                          | 2 t <sub>MCLK</sub> * | _    | ns   |

<sup>\*:</sup> See "18.4.2. Source Clock/Machine Clock" for t<sub>MCLK</sub>.

### 18.6 Flash Memory Program/Erase Characteristics

| Parameter                              | Value            |                   |                   | Unit  | Remarks                                                                                    |  |

|----------------------------------------|------------------|-------------------|-------------------|-------|--------------------------------------------------------------------------------------------|--|

| Parameter                              | Min Typ Max      | Ullit             | Reilians          |       |                                                                                            |  |

| Sector erase time (2 Kbyte sector)     | ı                | 0.3*1             | 1.6* <sup>2</sup> | s     | The time of writing "0x00" prior to erasure is excluded.                                   |  |

| Sector erase time<br>(32 Kbyte sector) | _                | 0.6* <sup>1</sup> | 3.1* <sup>2</sup> | s     | The time of writing "0x00" prior to erasure is excluded.                                   |  |

| Byte writing time                      | _                | 17                | 272               | μs    | System-level overhead is excluded.                                                         |  |

| Program/erase cycle                    | 100000           | _                 | _                 | cycle |                                                                                            |  |

| Power supply voltage at program/erase  | 1.8              | _                 | 5.5               | V     |                                                                                            |  |

| Flash memory data retention time       | 20*3             | _                 | _                 |       | Average T <sub>A</sub> = +85 °C<br>Number of program/erase cycles: 1000 or below           |  |

|                                        | 10* <sup>3</sup> | _                 | _                 | year  | Average T <sub>A</sub> = +85 °C<br>Number of program/erase cycles: 1001 to 10000 inclusive |  |

|                                        | 5* <sup>3</sup>  | _                 | _                 |       | Average T <sub>A</sub> = +85 °C<br>Number of program/erase cycles: 10001 or above          |  |

$<sup>\</sup>overline{*1: V_{CC} = 5.5 \text{ V}, T_A = +25 \text{ °C}, 0 \text{ cycle}}$

<sup>\*2:</sup>  $V_{CC}$  = 1.8 V,  $T_A$  = +85 °C, 100000 cycles

<sup>\*3:</sup> These values were converted from the result of a technology reliability assessment. (These values were converted from the result of a high temperature accelerated test using the Arrhenius equation with the average temperature being +85 °C.)

$I_{CCT} - V_{CC}$   $T_A = +25$  °C,  $F_{MPL} = 16$  kHz (divided by 2) Watch mode with the external clock operating

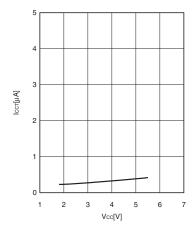

$I_{CCTS}-V_{CC}\\T_A=+25~^{\circ}C,~F_{MP}=2,~4,~8,~10,~16~MHz~(divided~by~2)\\Time-base~timer~mode~with~the~external~clock~operating$

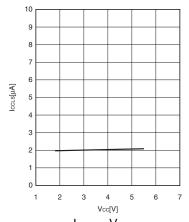

$I_{CCLS}-T_A \\ V_{CC}=3.3~V,~F_{MPL}=16~kHz~(divided~by~2) \\ Subsleep~mode~with~the~external~clock~operating$

$I_{CCT}-T_A \\ V_{CC}=3.3 \text{ V, } F_{MPL}=16 \text{ kHz (divided by 2)} \\ Watch mode with the external clock operating}$

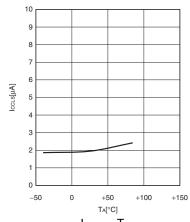

$I_{CCTS}-T_A \\ V_{CC}=3.3~V,~F_{MP}=2,~4,~8,~10,~16~MHz~(divided~by~2) \\ Time-base~timer~mode~with~the~external~clock~operating$