Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Obsolete                                                    |

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART            |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                  |

| Number of I/O              | 17                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 768 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | A/D 16x10b; D/A 1x10b                                       |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 20-VFQFN Exposed Pad                                        |

| Supplier Device Package    | 20-MLP (4x4)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f330 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

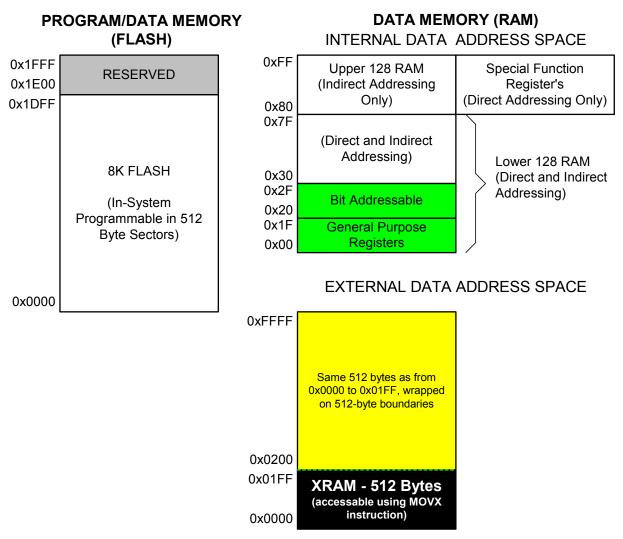

## 1.2. On-Chip Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

Program memory consists of 8k bytes of Flash. This memory may be reprogrammed in-system in 512 byte sectors, and requires no special off-chip programming voltage. See Figure 1.5 for the MCU system memory map.

Figure 1.5. On-Board Memory Map

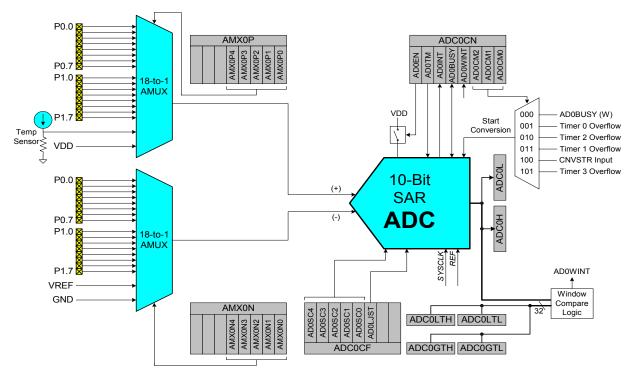

## 5. 10-Bit ADC (ADC0, C8051F330 and C8051F330D only)

The ADC0 subsystem for the C8051F330 and C8051F330D consists of two analog multiplexers (referred to collectively as AMUX0) with 16 total input selections, and a 200 ksps, 10-bit successive-approximation-register ADC with integrated track-and-hold and programmable window detector. The AMUX0, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shown in Figure 5.1. ADC0 operates in both Single-ended and Differential modes, and may be configured to measure Ports0-1, the Temperature Sensor output, or  $V_{DD}$  with respect to Ports0-1 or GND. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

Figure 5.1. ADC0 Functional Block Diagram

### 5.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

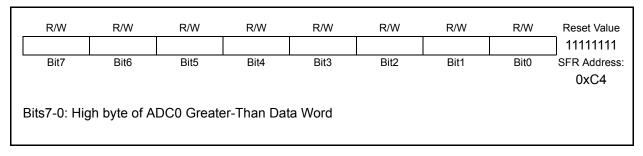

Figure 5.11. ADC0GTH: ADC0 Greater-Than Data High Byte Register

| R                                                | ./W  | R/W  | Reset Value              |

|--------------------------------------------------|------|------|------|------|------|------|------|------|--------------------------|

| B                                                | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | 11111111<br>SFR Address: |

|                                                  |      |      |      |      |      |      |      |      | 0xC3                     |

| Bits7-0: Low byte of ADC0 Greater-Than Data Word |      |      |      |      |      |      |      |      |                          |

Figure 5.12. ADC0GTL: ADC0 Greater-Than Data Low Byte Register

The Comparator output can be polled in software, used as an interrupt source, and/or routed to a Port pin. When routed to a Port pin, the Comparator output is available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP mode (with no system clock active). When disabled, the Comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and its supply current falls to less than 100 nA. See Section "14.1. Priority Crossbar Decoder" on page 115 for details on configuring Comparator outputs via the digital Crossbar. Comparator inputs can be externally driven from -0.25 V to ( $V_{DD}$ ) + 0.25 V without damage or upset. The complete Comparator electrical specifications are given in Table 8.1.

The Comparator response time may be configured in software via the CPT0MD register (see Figure 8.5). Selecting a longer response time reduces the Comparator supply current. See Table 8.1 for complete timing and power consumption specifications.

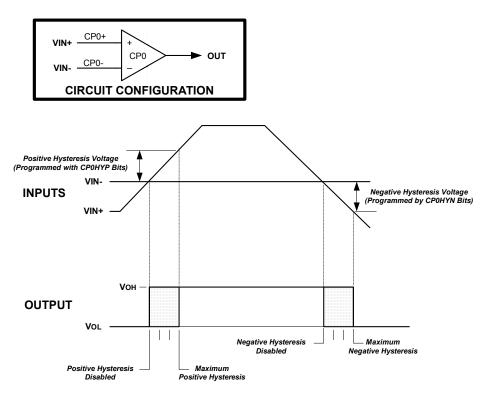

Figure 8.2. Comparator Hysteresis Plot

The Comparator hysteresis is software-programmable via its Comparator Control register CPT0CN. The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The Comparator hysteresis is programmed using Bits3-0 in the Comparator Control Register CPT0CN (shown in Figure 8.3). The amount of negative hysteresis voltage is determined by the settings of the CP0HYN bits. As shown in Figure 8.2, settings of 20, 10 or 5 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CP0HYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see **Section "8.3. Interrupt Handler" on page 58**). The CP0FIF flag is set

#### 9.4. Power Management Modes

The CIP-51 core has two software programmable power management modes: Idle and Stop. Idle mode halts the CPU while leaving the peripherals and clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not effected). Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode consumes the least power. Figure 1.15 describes the Power Control Register (PCON) used to control the CIP-51's power management modes.

Although the CIP-51 has Idle and Stop modes built in (as with any standard 8051 architecture), power management of the entire MCU is better accomplished by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off the oscillators lowers power consumption considerably; however a reset is required to restart the MCU.

#### 9.4.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

Note: If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from Idle mode when a future interrupt occurs. Therefore, instructions that set the IDLE bit should be followed by an instruction that has 2 or more opcode bytes, for example:

| <pre>// in `C': PCON  = 0x01; PCON = PCON;</pre>   | <pre>// set IDLE bit // followed by a 3-cycle dummy instruction</pre> |

|----------------------------------------------------|-----------------------------------------------------------------------|

| ; in assembly:<br>ORL PCON, #01h<br>MOV PCON, PCON | ; set IDLE bit<br>; followed by a 3-cycle dummy instruction           |

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "10.6. PCA Watchdog Timer Reset" on page 92 for more information on the use and configuration of the WDT.

#### 10.8. Software Reset

Software may force a reset by writing a '1' to the SWRSF bit (RSTSRC.4). The SWRSF bit will read '1' following a software forced reset. The state of the /RST pin is unaffected by this reset.

| R                                                                                                           | R                                                                                  | R/W           | R/W          | R                       | R/W                              | R/W           | R                      | Reset Value         |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------|--------------|-------------------------|----------------------------------|---------------|------------------------|---------------------|

| -                                                                                                           | FERROR                                                                             | CORSEF        | SWRSF        | WDTRSF                  | MCDRSF                           | PORSF         | PINRSF                 | Variable            |

| Bit7                                                                                                        | Bit6                                                                               | Bit5          | Bit4         | Bit3                    | Bit2                             | Bit1          | Bit0                   |                     |

|                                                                                                             |                                                                                    |               |              |                         |                                  |               | SFR Address            | :0xEF               |

|                                                                                                             |                                                                                    |               |              |                         |                                  |               |                        |                     |

| Bit7:                                                                                                       | UNUSED. R                                                                          | ead = 0. W    | rite = don't | care.                   |                                  |               |                        |                     |

| Bit6:                                                                                                       | FERROR: F                                                                          |               |              |                         |                                  |               |                        |                     |

|                                                                                                             | 0: Source of                                                                       |               |              |                         |                                  | -             |                        |                     |

|                                                                                                             | 1: Source of                                                                       |               |              |                         |                                  | error.        |                        |                     |

| Bit5:                                                                                                       | CORSEF: Co                                                                         | •             |              | •                       |                                  |               |                        |                     |

|                                                                                                             | 0: <b>Read:</b> So                                                                 | urce of last  | reset was    | not Compara             | ator0. Write                     | : Compara     | tor0 is not a          | reset               |

|                                                                                                             | source.                                                                            |               |              | 0                       |                                  |               |                        |                     |

|                                                                                                             | 1: Read: So                                                                        |               | reset was    | Comparator              | 0. write: Co                     | omparatoru    | is a reset s           | ource               |

| Bit4:                                                                                                       | (active-low).<br>SWRSF: Soi                                                        |               | t Earoa an   | d Elog                  |                                  |               |                        |                     |

| DIL4.                                                                                                       | 0: <b>Read:</b> So                                                                 |               |              |                         | o the SM/DS                      | E hit Writ    | • No Effect            |                     |

|                                                                                                             | 1: <b>Read:</b> Sol                                                                |               |              |                         |                                  |               |                        |                     |

| Bit3:                                                                                                       | WDTRSF: W                                                                          |               |              |                         |                                  |               | a system re            |                     |

| Dito.                                                                                                       | 0: Source of                                                                       |               |              |                         |                                  |               |                        |                     |

|                                                                                                             | 1: Source of                                                                       |               |              |                         | •                                |               |                        |                     |

| Bit2:                                                                                                       | MCDRSF: M                                                                          |               |              |                         |                                  |               |                        |                     |

|                                                                                                             | 0: Read: So                                                                        |               |              |                         | g Clock Det                      | ector timed   | out. Write: N          | lissing             |

|                                                                                                             | Clock Detect                                                                       | tor disabled  | Ι.           |                         | •                                |               |                        | •                   |

|                                                                                                             | 1: Read: So                                                                        | urce of last  | reset was    | a Missing C             | lock Detecto                     | or timeout.   | Write: Miss            | ing Clock           |

|                                                                                                             | Detector ena                                                                       | abled; trigge | ers a reset  | if a missing            | clock condit                     | ion is deteo  | cted.                  |                     |

| Bit1:                                                                                                       | PORSF: Pov                                                                         |               |              |                         |                                  |               |                        |                     |

|                                                                                                             | This bit is se                                                                     | et anytime a  | power-on     | reset occurs            | <ol> <li>Writing this</li> </ol> | s bit enable  | es/disables            | the V <sub>DD</sub> |

|                                                                                                             | monitor as a                                                                       |               |              |                         |                                  |               |                        |                     |

|                                                                                                             | and stabiliz                                                                       |               |              |                         |                                  |               |                        |                     |

|                                                                                                             | 0: <b>Read:</b> Las                                                                |               | s not a pow  | er-on or V <sub>D</sub> | D monitor re                     | eset. Write   | : V <sub>DD</sub> moni | tor is not a        |

|                                                                                                             | reset source                                                                       |               |              |                         |                                  | II . (I       |                        |                     |

|                                                                                                             | 1: Read: Las                                                                       |               |              |                         |                                  | ; all other r | eset flags             |                     |

| indeterminate. <b>Write:</b> V <sub>DD</sub> monitor is a reset source.<br>Bit0: PINRSF: HW Pin Reset Flag. |                                                                                    |               |              |                         |                                  |               |                        |                     |

|                                                                                                             |                                                                                    |               | 0            | T mim                   |                                  |               |                        |                     |

| DILU.                                                                                                       | 0: Source of last reset was not /RST pin.<br>1: Source of last reset was /RST pin. |               |              |                         |                                  |               |                        |                     |

| Dito.                                                                                                       |                                                                                    |               |              | •                       |                                  |               |                        |                     |

Figure 10.4. RSTSRC: Reset Source Register

#### **Table 10.1. Reset Electrical Characteristics**

-40 to +85 °C unless otherwise specified.

| Parameter                                           | Conditions                                                                            | Min                   | Тур  | Max                   | Units |

|-----------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| /RST Output Low Voltage                             | I <sub>OL</sub> = 8.5 mA,<br>V <sub>DD</sub> = 2.7 V to 3.6 V                         | _                     | _    | 0.6                   | V     |

| /RST Input High Voltage                             |                                                                                       | 0.7 x V <sub>DD</sub> |      |                       | V     |

| /RST Input Low Voltage                              |                                                                                       | —                     | _    | 0.3 x V <sub>DD</sub> |       |

| /RST Input Pullup Current                           | /RST = 0.0 V                                                                          | —                     | 25   | 40                    | μA    |

| $V_{DD}$ POR Threshold (V <sub>RST</sub> )          |                                                                                       | 2.40                  | 2.55 | 2.70                  | V     |

| Missing Clock Detector Time-<br>out                 | Time from last system clock rising edge to reset initiation                           | 100                   | 220  | 600                   | μs    |

| Reset Time Delay                                    | Delay between release of any<br>reset source and code<br>execution at location 0x0000 | 5.0                   |      | _                     | μs    |

| Minimum /RST Low Time to<br>Generate a System Reset |                                                                                       | 15                    | _    | _                     | μs    |

| V <sub>DD</sub> Monitor Turn-on Time                |                                                                                       | 100                   | _    | —                     | μs    |

| V <sub>DD</sub> Monitor Supply Current              |                                                                                       | —                     | 20   | 50                    | μA    |

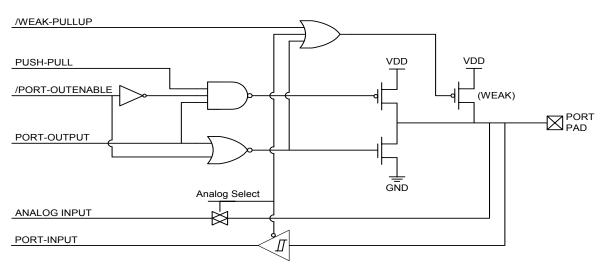

Figure 14.2. Port I/O Cell Block Diagram

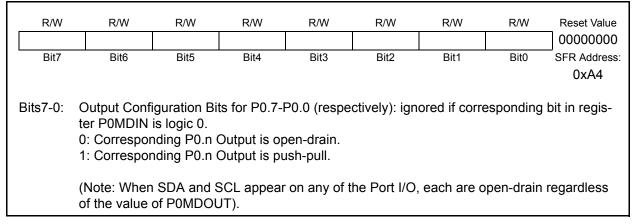

Figure 14.9. P0MDOUT: Port0 Output Mode Register

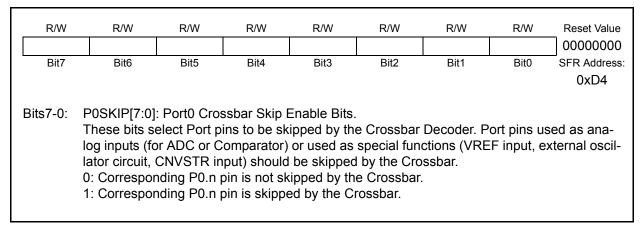

Figure 14.10. P0SKIP: Port0 Skip Register

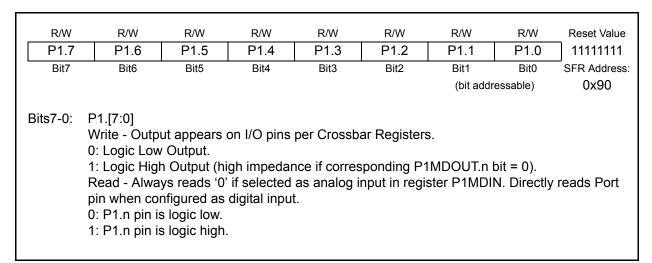

#### Figure 14.11. P1: Port1 Register

## **15.1. Supporting Documents**

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I2C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I2C-Bus Specification—Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification—Version 1.1, SBS Implementers Forum.

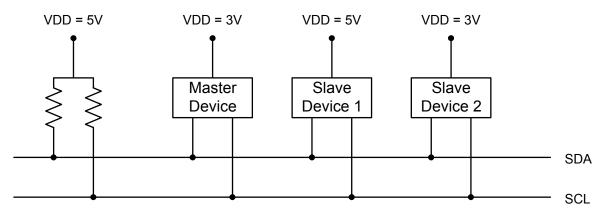

### 15.2. SMBus Configuration

Figure 15.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pull-up resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

Figure 15.2. Typical SMBus Configuration

| R/W      | R/W                                                                                             | R            | R/W         | R/W                       | R/W          | R/W           | R/W          | Reset Value |  |

|----------|-------------------------------------------------------------------------------------------------|--------------|-------------|---------------------------|--------------|---------------|--------------|-------------|--|

| ENSMB    | INH                                                                                             | BUSY         | EXTHOLD     | SMBTOE                    | SMBFTE       | SMBCS1        | SMBCS0       | 00000000    |  |

| Bit7     | Bit6                                                                                            | Bit5         | Bit4        | Bit3                      | Bit2         | Bit1          | Bit0         |             |  |

|          |                                                                                                 |              |             |                           |              |               | SFR Address  | s: 0xC1     |  |

|          |                                                                                                 |              |             |                           |              |               |              |             |  |

| Bit7:    | ENSMB: SM                                                                                       |              |             |                           |              |               |              |             |  |

|          | This bit enal                                                                                   |              |             | s interface.              | When enal    | oled, the int | erface cons  | tantly mon- |  |

|          | itors the SD                                                                                    |              | •           |                           |              |               |              |             |  |

|          | 0: SMBus in                                                                                     |              |             |                           |              |               |              |             |  |

| Bit6:    | 1: SMBus in                                                                                     |              |             |                           |              |               |              |             |  |

| DILO.    | INH: SMBus<br>When this bi                                                                      |              |             | MRue dooe                 | not genera   | ita an intarr | unt when el  | ava avante  |  |

|          | occur. This e                                                                                   |              |             |                           |              |               |              |             |  |

|          | not affected.                                                                                   |              |             |                           |              | bus. music    |              |             |  |

|          | 0: SMBus S                                                                                      |              | enabled.    |                           |              |               |              |             |  |

|          | 1: SMBus S                                                                                      |              |             |                           |              |               |              |             |  |

| Bit5:    | BUSY: SMB                                                                                       | us Busy Ind  | dicator.    |                           |              |               |              |             |  |

|          | This bit is se                                                                                  | t to logic 1 | by hardware | e when a tra              | ansfer is in | progress. It  | is cleared t | o logic 0   |  |

|          | when a STC                                                                                      |              |             |                           |              |               |              |             |  |

| Bit4:    | EXTHOLD:                                                                                        |              | •           |                           |              |               |              |             |  |

|          | This bit cont                                                                                   |              | •           |                           | -            | to.           |              |             |  |

|          | 0: SDA Exte                                                                                     | •            |             |                           |              |               |              |             |  |

| Bit3:    | 1: SDA Exte<br>SMBTOE: S                                                                        |              |             |                           |              |               |              |             |  |

| Dito.    | This bit enal                                                                                   |              |             |                           |              | 1 the SMB     | us forces Ti | mer 3 to    |  |

|          | reload while                                                                                    |              |             |                           | -            |               |              |             |  |

|          | figured to Sp                                                                                   |              |             |                           |              |               |              |             |  |

|          | Timer 3 sho                                                                                     |              | • •         | •                         |              |               |              | -           |  |

|          | service routi                                                                                   | ne should r  | eset SMBus  | s communic                | ation.       |               |              |             |  |

| Bit2:    | SMBFTE: S                                                                                       |              |             |                           |              |               |              |             |  |

|          | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for |              |             |                           |              |               |              |             |  |

|          | more than 10 SMBus clock source periods.<br>SMBCS1-SMBCS0: SMBus Clock Source Selection.        |              |             |                           |              |               |              |             |  |

| Bits1-0: |                                                                                                 |              |             |                           |              | and to gone   | rata tha SM  | IRue hit    |  |

|          | These two bits select the SMBus clock source, which is used to generate the SMBus bit           |              |             |                           |              |               |              |             |  |

|          | rate. The selected device should be configured according to Equation 15.1.                      |              |             |                           |              |               |              |             |  |

|          | SMBCS1                                                                                          | SMBCS0       |             | Bus Clock                 |              |               |              |             |  |

|          | 0                                                                                               | 0            |             | Timer 0 Ove               |              |               |              |             |  |

|          | 0                                                                                               | 1            |             | Timer 1 Ove               |              |               |              |             |  |

|          | 1                                                                                               | 0            | Timor       |                           |              |               |              |             |  |

|          |                                                                                                 | 0            |             | 2 High Byte<br>2 Low Byte | e Overflow   |               |              |             |  |

Figure 15.5. SMB0CF: SMBus Clock/Configuration Register

|                    | Frequency: 3.6864 MHz           |                        |                                  |                              |                                                 |                  |                                     |  |

|--------------------|---------------------------------|------------------------|----------------------------------|------------------------------|-------------------------------------------------|------------------|-------------------------------------|--|

|                    | Target<br>Baud Rate<br>(bps)    | Baud<br>Rate%<br>Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source        | SCA1-SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value<br>(hex) |  |

|                    | 230400                          | 0.00%                  | 16                               | SYSCLK                       | XX <sup>2</sup>                                 | 1                | 0xF8                                |  |

| <u>ج</u> .:        | 115200                          | 0.00%                  | 32                               | SYSCLK                       | XX                                              | 1                | 0xF0                                |  |

| from<br>Osc.       | 57600                           | 0.00%                  | 64                               | SYSCLK                       | XX                                              | 1                | 0xE0                                |  |

|                    | 28800                           | 0.00%                  | 128                              | SYSCLK                       | XX                                              | 1                | 0xC0                                |  |

| SCLK               | 14400                           | 0.00%                  | 256                              | SYSCLK                       | XX                                              | 1                | 0x80                                |  |

| SYSCLK<br>External | 9600                            | 0.00%                  | 384                              | SYSCLK                       | XX                                              | 1                | 0x40                                |  |

| Ο                  | 2400                            | 0.00%                  | 1536                             | SYSCLK / 12                  | 00                                              | 0                | 0xC0                                |  |

|                    | 1200                            | 0.00%                  | 3072                             | SYSCLK / 12                  | 00                                              | 0                | 0x80                                |  |

| с.                 | 230400                          | 0.00%                  | 16                               | EXTCLK / 8                   | 11                                              | 0                | 0xFF                                |  |

| from<br>Osc.       | 115200                          | 0.00%                  | 32                               | EXTCLK / 8                   | 11                                              | 0                | 0xFE                                |  |

| $\sim$             | 57600                           | 0.00%                  | 64                               | EXTCLK / 8                   | 11                                              | 0                | 0xFC                                |  |

| SYSCLK<br>Internal | 28800                           | 0.00%                  | 128                              | EXTCLK / 8                   | 11                                              | 0                | 0xF8                                |  |

| SYS<br>Inte        | 14400                           | 0.00%                  | 256                              | EXTCLK / 8                   | 11                                              | 0                | 0xF0                                |  |

| თ —                | 9600                            | 0.00%                  | 384                              | EXTCLK / 8                   | 11                                              | 0                | 0xE8                                |  |

|                    | SCA1-SCA0 ar<br>( = Don't care. | nd T1M bit def         | initions can l                   | be found in <mark>Sec</mark> | tion 18.1.                                      |                  |                                     |  |

### Table 16.6. Timer Settings for Standard Baud Rates Using an External Oscillator

### 17.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 17.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 17.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 17.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

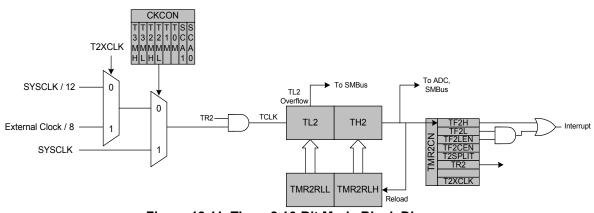

### 18.2. Timer 2

Timer 2 is a 16-bit timer formed by two 8-bit SFRs: TMR2L (low byte) and TMR2H (high byte). Timer 2 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T2SPLIT bit (TMR2CN.3) defines the Timer 2 operation mode.

Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 2 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 18.2.1. 16-bit Timer with Auto-Reload

When T2SPLIT (TMR2CN.3) is zero, Timer 2 operates as a 16-bit timer with auto-reload. Timer 2 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 2 reload registers (TMR2RLH and TMR2RLL) is loaded into the Timer 2 register as shown in Figure 18.11, and the Timer 2 High Byte Overflow Flag (TMR2CN.7) is set. If Timer 2 interrupts are enabled (if IE.5 is set), an interrupt will be generated on each Timer 2 overflow. Additionally, if Timer 2 interrupts are enabled and the TF2LEN bit is set (TMR2CN.5), an interrupt will be generated each time the lower 8 bits (TMR2L) overflow from 0xFF to 0x00.

Figure 18.11. Timer 2 16-Bit Mode Block Diagram

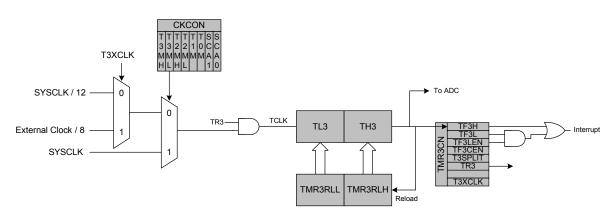

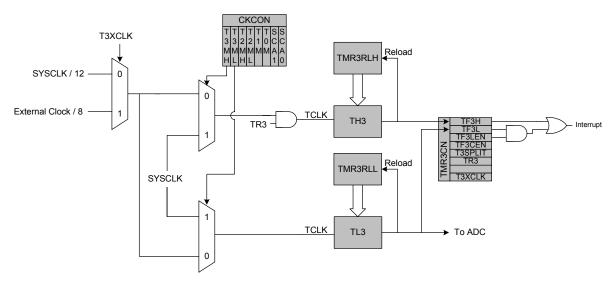

### 18.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T3SPLIT bit (TMR3CN.3) defines the Timer 3 operation mode.

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 3 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 18.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TM32RLL) is loaded into the Timer 3 register as shown in Figure 18.11, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TL3) overflow from 0xFF to 0x00.

Figure 18.18. Timer 3 16-Bit Mode Block Diagram

#### 18.3.2. 8-bit Timers with Auto-Reload

When T3SPLIT is set, Timer 3 operates as two 8-bit timers (TH3 and TL3). Both 8-bit timers operate in auto-reload mode as shown in Figure 18.12. TMR3RLL holds the reload value for TL3; TMR3RLH holds the reload value for TH3. The TR3 bit in TMR3CN handles the run control for TH3. TL3 is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 3 Clock Select bits (T3MH and T3ML in CKCON) select either SYSCLK or the clock defined by the Timer 3 External Clock Select bit (T3XCLK in TMR3CN), as follows:

| ТЗМН | T3XCLK | TH3 Clock<br>Source |

|------|--------|---------------------|

| 0    | 0      | SYSCLK / 12         |

| 0    | 1      | External Clock / 8  |

| 1    | Х      | SYSCLK              |

| T3ML | T3XCLK | TL3 Clock Source   |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF3H bit is set when TH3 overflows from 0xFF to 0x00; the TF3L bit is set when TL3 overflows from 0xFF to 0x00. When Timer 3 interrupts are enabled (IE.5), an interrupt is generated each time TH3 overflows. If Timer 3 interrupts are enabled and TF3LEN (TMR3CN.5) is set, an interrupt is generated each time either TL3 or TH3 overflows. When TF3LEN is enabled, software must check the TF3H and TF3L flags to determine the source of the Timer 3 interrupt. The TF3H and TF3L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 18.19. Timer 3 8-Bit Mode Block Diagram

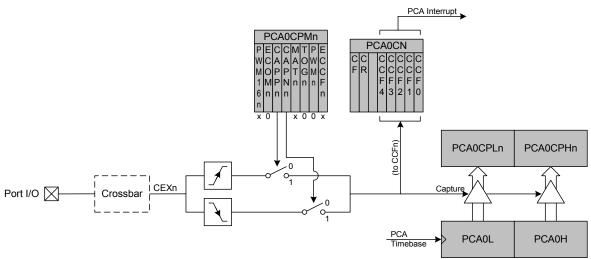

#### 19.2.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 19.4. PCA Capture Mode Diagram

Note: The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

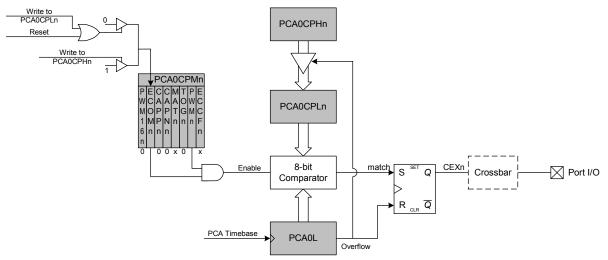

#### 19.2.5. 8-Bit Pulse Width Modulator Mode

Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer. The duty cycle of the PWM output signal is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 19.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register enables 8-Bit Pulse Width Modulator mode. The duty cycle for 8-Bit PWM Mode is given by Equation 19.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

$$DutyCycle = \frac{(256 - PCA0CPHn)}{256}$$

Equation 19.4. 8-Bit PWM Duty Cycle

Using Equation 19.4, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to '0'.

Figure 19.8. PCA 8-Bit PWM Mode Diagram

NOTES:

## **CONTACT INFORMATION**

#### Silicon Laboratories Inc.

4635 Boston Lane Austin, TX 78735 Tel: 1+(512) 416-8500 Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Email: productinfo@silabs.com Internet: www.silabs.com

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product so ray such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders