Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART            |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 17                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 768 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            |                                                             |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 20-VFQFN Exposed Pad                                        |

| Supplier Device Package    | 20-MLP (4x4)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f331 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

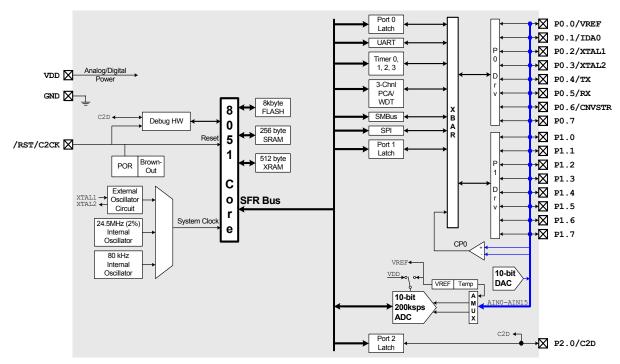

Figure 1.1. C8051F330 and C8051F330D Block Diagram

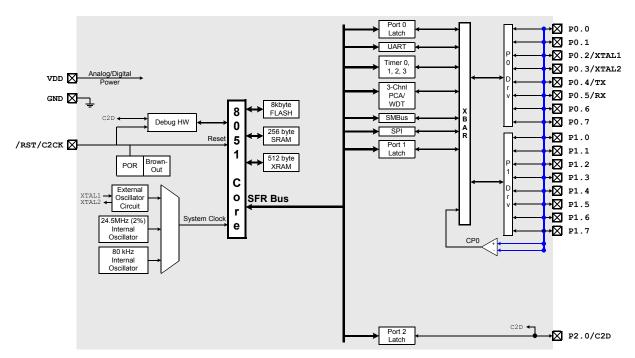

Figure 1.2. C8051F331 Block Diagram

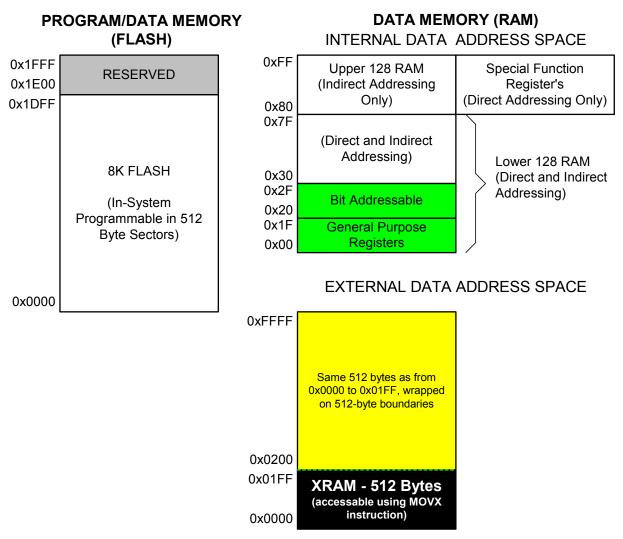

## 1.2. On-Chip Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

Program memory consists of 8k bytes of Flash. This memory may be reprogrammed in-system in 512 byte sectors, and requires no special off-chip programming voltage. See Figure 1.5 for the MCU system memory map.

Figure 1.5. On-Board Memory Map

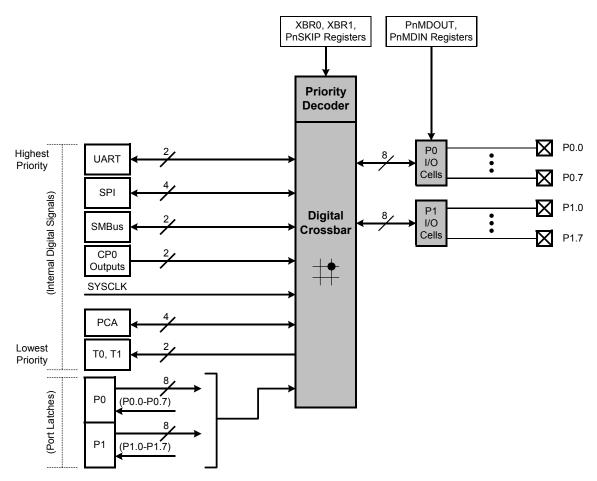

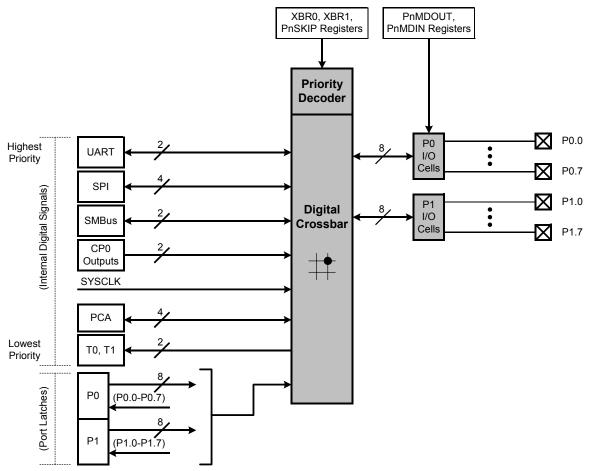

## 1.4. Programmable Digital I/O and Crossbar

C8051F330/1, C8051F330D devices include 17 I/O pins (two byte-wide Ports and one 1-bit-wide Port). The C8051F330/1, C8051F330D Ports behave like typical 8051 Ports with a few enhancements. Each Port pin may be configured as an analog input or a digital I/O pin. Pins selected as digital I/Os may additionally be configured for push-pull or open-drain output. The "weak pull-ups" that are fixed on typical 8051 devices may be globally disabled, providing power savings capabilities.

The Digital Crossbar allows mapping of internal digital system resources to Port I/O pins (See Figure 1.7). On-chip counter/timers, serial buses, HW interrupts, comparator output, and other digital signals in the controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This allows the user to select the exact mix of general purpose Port I/O and digital resources needed for the particular application.

Figure 1.7. Digital Crossbar Diagram

# 3. Global DC Electrical Characteristics

### **Table 3.1. Global DC Electrical Characteristics**

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Conditions                                                                                                                                  | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Мах                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                             | V <sub>RST</sub> <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $V_{DD}$ = 2.7 V, Clock = 25 MHz<br>$V_{DD}$ = 2.7 V, Clock = 1 MHz<br>$V_{DD}$ = 2.7 V, Clock = 80 kHz<br>$V_{DD}$ = 2.7 V, Clock = 32 kHz | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.4<br>0.36<br>20<br>9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | mA<br>mA<br>μA<br>μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $V_{DD}$ = 2.7 V, Clock = 25 MHz<br>$V_{DD}$ = 2.7 V, Clock = 1 MHz<br>$V_{DD}$ = 2.7 V, Clock = 80 kHz<br>$V_{DD}$ = 2.7 V, Clock = 32 kHz | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.2<br>180<br>14.5<br>7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | mΑ<br>μΑ<br>μΑ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Oscillator not running,<br>V <sub>DD</sub> Monitor Disabled                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | < 0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                             | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                             | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                             | -40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | +85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                             | $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 25 \text{ MHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 1 \text{ MHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 80 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 25 \text{ MHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 1 \text{ MHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 80 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ | $V_{BST}^{1}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 25 \text{ MHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 1 \text{ MHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 80 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 25 \text{ MHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 1 \text{ MHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 80 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ $V_{DD} = 2.7 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ $V_{DD}$ Monitor Disabled $0$ 18         18       18 | VDD       2.7 V, Clock = 25 MHz       VRST1 $3.0$ VDD = 2.7 V, Clock = 25 MHz       - $6.4$ $0.36$ $20$ $9$ VDD = 2.7 V, Clock = 80 kHz       9 $9$ $9$ $9$ $9$ VDD = 2.7 V, Clock = 32 kHz       - $3.2$ $180$ $14.5$ VDD = 2.7 V, Clock = 25 MHz       - $3.2$ $180$ $14.5$ VDD = 2.7 V, Clock = 1 MHz       - $180$ $14.5$ $7.5$ VDD = 2.7 V, Clock = 30 kHz       - $7.5$ $7.5$ $7.5$ VDD = 2.7 V, Clock = 32 kHz       - $180$ $14.5$ $7.5$ VDD = 2.7 V, Clock = 32 kHz       - $1.5$ $ 1.5$ Oscillator not running,       - $ 1.5$ $-$ Oscillator not running,       - $ 1.5$ $ 18$ - $18$ - $ 18$ - $18$ - $-$ | V <sub>RST</sub> <sup>1</sup> 3.0       3.6 $V_{DD} = 2.7 V$ , Clock = 25 MHz        6.4 $V_{DD} = 2.7 V$ , Clock = 1 MHz        6.4 $V_{DD} = 2.7 V$ , Clock = 80 kHz       9       9 $V_{DD} = 2.7 V$ , Clock = 32 kHz        3.2 $V_{DD} = 2.7 V$ , Clock = 25 MHz        3.2 $V_{DD} = 2.7 V$ , Clock = 1 MHz        180       14.5 $V_{DD} = 2.7 V$ , Clock = 1 MHz        180       14.5 $V_{DD} = 2.7 V$ , Clock = 32 kHz        180 $V_{DD} = 2.7 V$ , Clock = 32 kHz         20 $V_{DD} = 2.7 V$ , Clock = 32 kHz $V_{DD} = 2.7 V$ , Clock = 32 kHz $V_{DD}$ Monitor Disabled        <- |

1. Given in Table 10.1 on page 94.

2. SYSCLK must be at least 32 kHz to enable debugging.

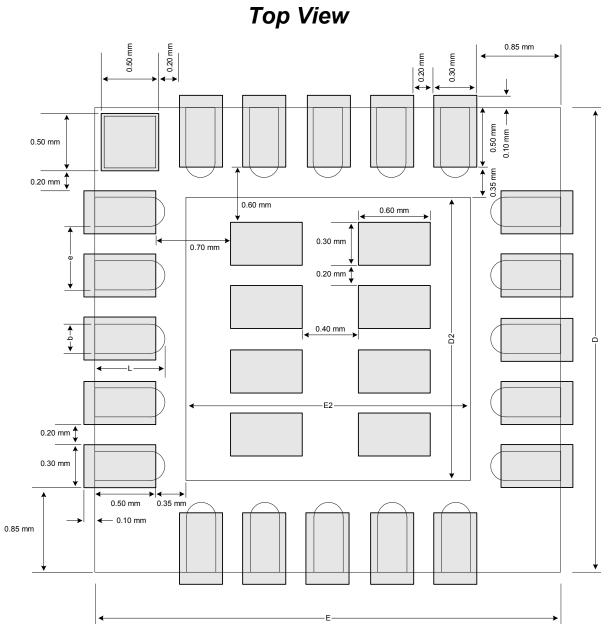

Figure 4.3. Typical MLP-20 Solder Paste Mask

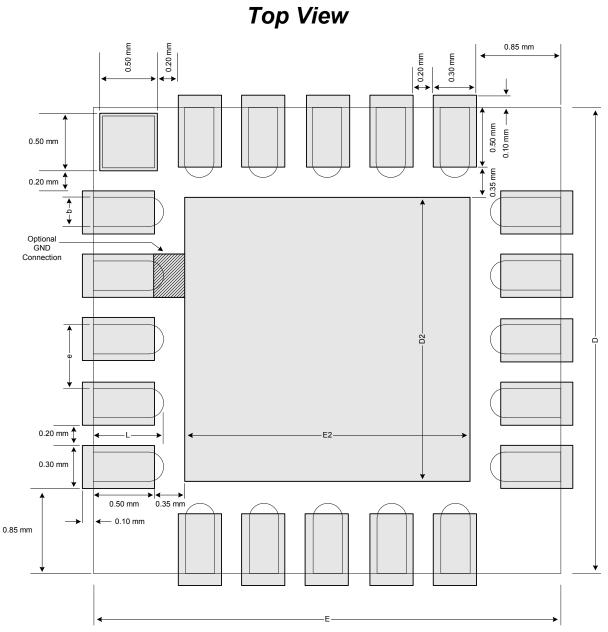

Figure 4.4. Typical MLP-20 Landing Diagram

| R/W      | R/W                           | R/W         | R/W           | R/W            | R/W            | R/W            | R/W           | Reset Value  |

|----------|-------------------------------|-------------|---------------|----------------|----------------|----------------|---------------|--------------|

| AD0EN    | AD0TM                         | AD0INT      | AD0BUSY       | <b>AD0WINT</b> | AD0CM2         | AD0CM1         | AD0CM0        | 00000000     |

| Bit7     | Bit6                          | Bit5        | Bit4          | Bit3           | Bit2           | Bit1           | Bit0          | SFR Address: |

|          |                               |             |               |                |                | (bit addr      | essable)      | 0xE8         |

|          |                               |             |               |                |                |                |               |              |

| Bit7:    | AD0EN: AD                     |             |               |                |                |                |               |              |

|          | 0: ADC0 Dis                   |             |               |                |                |                |               |              |

| D:40.    | 1: ADC0 En                    |             |               | and ready to   | r data conv    | ersions.       |               |              |

| Bit6:    | AD0TM: AD                     |             |               | 0 ia anablar   | t trocking i   | o continuou    |               | onvorsion    |

|          | 0: Normal Tr<br>is in progres |             | . When ADC    |                | i, liacking is | s continuou    | s uniess a c  | Sonversion   |

|          | 1: Low-powe                   |             | ode: Trackin  | a Defined b    |                | 0 hits (see    | helow)        |              |

| Bit5:    | ADOINT: AD                    |             |               |                |                |                | 501011).      |              |

| 2.101    | 0: ADC0 has                   |             |               |                |                | ast time AD    | 0INT was c    | leared.      |

|          | 1: ADC0 has                   |             |               |                |                |                |               |              |

| Bit4:    | AD0BUSY: /                    | •           |               |                |                |                |               |              |

|          | Read:                         |             |               |                |                |                |               |              |

|          | 0: ADC0 cor                   |             | •             |                | on is not cu   | rrently in pro | ogress. AD    | DINT is set  |

|          | to logic 1 on                 | •           | •             |                |                |                |               |              |

|          | 1: ADC0 cor                   | iversion is | in progress.  |                |                |                |               |              |

|          | Write:<br>0: No Effect.       |             |               |                |                |                |               |              |

|          | 1: Initiates A                |             | ersion if AD  | $0CM2_0 = 0$   | 00h            |                |               |              |

| Bit3:    | ADOWINT: A                    |             |               |                |                |                |               |              |

| 2.101    | 0: ADC0 Wi                    |             | •             | •              | -              | ed since this  | s flag was la | ast cleared. |

|          | 1: ADC0 Wi                    |             | •             |                |                |                | 0             |              |

| Bits2-0: | AD0CM2-0:                     | ADC0 Star   | rt of Convers | sion Mode S    | elect.         |                |               |              |

|          | When AD0T                     |             |               |                |                |                |               |              |

|          | 000: ADC0 0                   |             |               | •              |                | 0BUSY.         |               |              |

|          | 001: ADC0 (                   |             |               |                |                |                |               |              |

|          | 010: ADC0 (                   |             |               |                |                |                |               |              |

|          | 011: ADC0 o<br>100: ADC0 o    |             |               |                |                |                |               |              |

|          | 101: ADC0 (                   |             |               |                |                | ONVOTIN.       |               |              |

|          | 11x: Reserve                  |             |               |                |                |                |               |              |

|          | When AD0T                     | M = 1:      |               |                |                |                |               |              |

|          | 000: Trackin                  | g initiated | on write of " | I' to AD0BU    | SY and las     | ts 3 SAR cl    | ocks, follow  | ed by con-   |

|          | version.                      |             |               |                |                |                |               |              |

|          | 001: Trackin                  | g initiated | on overflow   | of Timer 0 a   | ind lasts 3 S  | SAR clocks     | , followed b  | y conver-    |

|          | sion.                         |             |               | ( <b>T</b> 0   |                |                | 6 - 11        |              |

|          | 010: Trackin sion.            | g initiated | on overnow    | or rimer 2 a   | ind lasts 3 S  | SAK CIOCKS     | , ioliowea b  | y conver-    |

|          | 011: Trackin                  | a initiated | on overflow   | of Timer 1 a   | nd laste 2 9   | SAR clocke     | followed b    | v conver-    |

|          | sion.                         | y milateu   |               |                |                |                |               | y 0011001-   |

|          | 100: ADC0 t                   | racks only  | when CNVS     | STR input is   | logic low: c   | conversion s   | starts on ris | ing          |

|          | CNVSTR ed                     |             |               | P              | J , C          |                |               | 5            |

|          | 101: Trackin                  | 0           | on overflow   | of Timer 3 a   | ind lasts 3 S  | SAR clocks     | , followed b  | y conver-    |

|          | sion.                         |             |               |                |                |                |               |              |

|          | 11x: Reserve                  | ed.         |               |                |                |                |               |              |

### Figure 5.10. ADC0CN: ADC0 Control Register

| R                 | R                                                                                                                      | R                                                                                                                  | R             | R/W   | R/W          | R/W         | R/W         | Reset Value  |

|-------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------|-------|--------------|-------------|-------------|--------------|

| -                 | -                                                                                                                      | -                                                                                                                  | -             | REFSL | TEMPE        | BIASE       | REFBE       | 00000000     |

| Bit7              | Bit6                                                                                                                   | Bit5                                                                                                               | Bit4          | Bit3  | Bit2         | Bit1        | Bit0        | SFR Address: |

|                   |                                                                                                                        |                                                                                                                    |               |       |              |             |             | 0xD1         |

| Bits7-4:<br>Bit3: |                                                                                                                        |                                                                                                                    |               |       |              |             |             |              |

| Bit2:             | 0: Internal Te                                                                                                         | TEMPE: Temperature Sensor Enable Bit.<br>0: Internal Temperature Sensor off.<br>1: Internal Temperature Sensor on. |               |       |              |             |             |              |

| Bit1:             | BIASE: Internal Analog Bias Generator Enable Bit.<br>0: Internal Bias Generator off.<br>1: Internal Bias Generator on. |                                                                                                                    |               |       |              |             |             |              |

| Bit0:             | REFBE: Inte<br>0: Internal R<br>1: Internal R                                                                          | eference B                                                                                                         | uffer disable | ed.   | voltage refe | rence drive | n on the VI | REF pin.     |

Figure 7.2. REF0CN: Reference Control Register

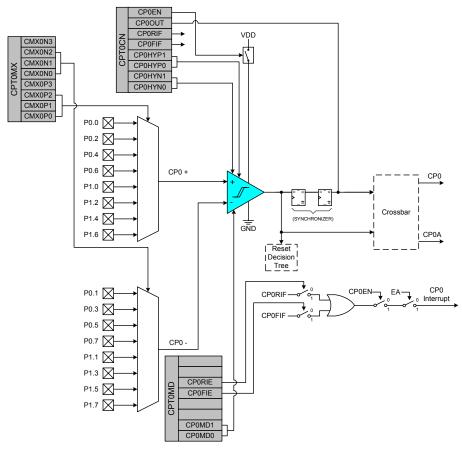

# 8. Comparator0

C8051F330/1, C8051F330D devices include an on-chip programmable voltage comparator, Comparator0, shown in Figure 8.1.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0), or an asynchronous "raw" output (CP0A). The asynchronous CP0A signal is available even when in when the system clock is not active. This allows the Comparator to operate and generate an output with the device in STOP mode. When assigned to a Port pin, the Comparator output may be configured as open drain or push-pull (see Section "14.2. Port I/O Initialization" on page 117). Comparator0 may also be used as a reset source (see Section "10.5. Comparator0 Reset" on page 92).

The Comparator0 inputs are selected in the CPT0MX register (Figure 8.4). The CMX0P1-CMX0P0 bits select the Comparator0 positive input; the CMX0N1-CMX0N0 bits select the Comparator0 negative input. **Important Note About Comparator Inputs:** The Port pins selected as comparator inputs should be configured as analog inputs in their associated Port configuration register, and configured to be skipped by the Crossbar (for details on Port configuration, see Section "14.3. General Purpose Port I/O" on page 120).

Figure 8.1. Comparator0 Functional Block Diagram

| Mnemonic             | Description                                                            |   | Clock<br>Cycles |

|----------------------|------------------------------------------------------------------------|---|-----------------|

| JNZ rel              | Jump if A does not equal zero                                          | 2 | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal                         | 3 | 3/4             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal                           | 3 | 3/4             |

| CJNE Rn, #data, rel  | INE Rn, #data, rel Compare immediate to Register and jump if not equal |   | 3/4             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal                    | 3 | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero                                | 2 | 2/3             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero                             | 3 | 3/4             |

| NOP                  | No operation                                                           | 1 | 1               |

### Table 9.1. CIP-51 Instruction Set Summary (Continued)

#### Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8K-byte program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

| R/W<br>ACC.7 | R/W<br>ACC.6 | R/W<br>ACC.5 | R/W<br>ACC.4 | R/W<br>ACC.3 | R/W<br>ACC.2 | R/W<br>ACC.1 | R/W<br>ACC.0 | Reset Value 00000000 |

|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|----------------------|

| Bit7         | Bit6         | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0         | SFR Address:         |

|              |              |              |              |              |              | (bit addr    | essable)     | 0xE0                 |

|              | ACC: Accum   |              | mulator for  | arithmetic o | operations.  |              |              |                      |

Figure 9.7. ACC: Accumulator

|       | R/W<br>B. <b>7</b> | R/W<br>B.6                    | R/W<br>B.5 | R/W<br>B.4  | R/W<br>B.3 | R/W<br>B.2    | R/W<br>B.1  | R/W<br>B.0 | Reset Value 0000000 |

|-------|--------------------|-------------------------------|------------|-------------|------------|---------------|-------------|------------|---------------------|

|       | Bit7               | Bit6                          | Bit5       | Bit4        | Bit3       | Bit2          | Bit1        | Bit0       | SFR Address:        |

|       |                    |                               |            |             |            |               | (bit addr   | essable)   | 0xF0                |

| Bits7 | 7-0:               | B: B Registe<br>This register |            | a second ad | ccumulator | for certain a | rithmetic o | perations. |                     |

Figure 9.8. B: B Register

### 9.3. Interrupt Handler

The CIP-51 includes an extended interrupt system supporting a total of 13 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interruptpending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE-EIE1). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

### 9.3.1. MCU Interrupt Sources and Vectors

The MCUs support 13 interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 9.4 on page 81. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

## 10.1. Power-On Reset

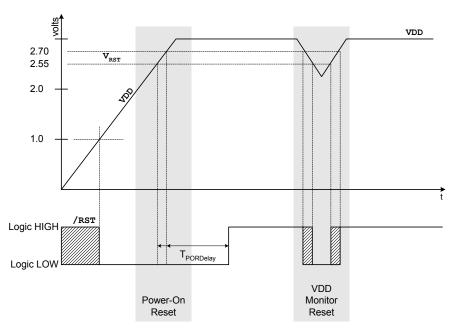

During power-up, the device is held in a reset state and the /RST pin is driven low until  $V_{DD}$  settles above  $V_{RST}$ . A delay occurs before the device is released from reset; the delay decreases as the  $V_{DD}$  ramp time increases ( $V_{DD}$  ramp time is defined as how fast  $V_{DD}$  ramps from 0 V to  $V_{RST}$ ). Figure 10.2. plots the power-on and  $V_{DD}$  monitor reset timing. The maximum  $V_{DD}$  ramp time is 1 ms; slower ramp times may cause the device to be released from reset before  $V_{DD}$  reaches the  $V_{RST}$  level. For ramp times less than 1 ms, the power-on reset delay ( $T_{PORDelay}$ ) is typically less than 0.3 ms.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The  $V_{DD}$  monitor is disabled following a power-on reset.

Figure 10.2. Power-On and  $V_{DD}$  Monitor Reset Timing

# 14. Port Input/Output

Digital and analog resources are available through 17 I/O pins. Port pins are organized as two byte-wide Ports and one 1-bit Port. Each of the Port pins can be defined as general-purpose I/O (GPIO) or analog input; Port pins P0.0 - P1.7 can be assigned to one of the internal digital resources as shown in Figure 14.3. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 14.3 and Figure 14.4). The registers XBR0 and XBR1, defined in Figure 14.5 and Figure 14.6, are used to select internal digital functions.

All Port I/Os are 5 V tolerant (refer to Figure 14.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Table 14.1 on page 124.

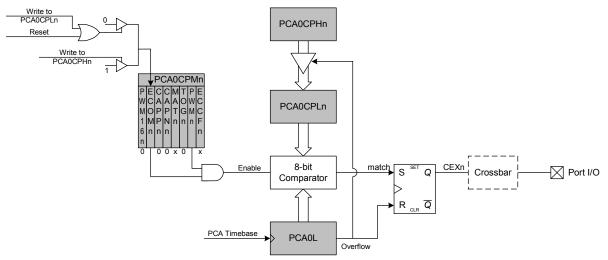

Figure 14.1. Port I/O Functional Block Diagram

| R/W      | R/W                          | R/W        | R/W        | R/W          | R            | R/W          | R/W       | Reset Value  |

|----------|------------------------------|------------|------------|--------------|--------------|--------------|-----------|--------------|

| WEAKP    | JD XBARE                     | T1E        | T0E        | ECIE         | -            | PCA          | 0ME       | 00000000     |

| Bit7     | Bit6                         | Bit5       | Bit4       | Bit3         | Bit2         | Bit1         | Bit0      | SFR Address: |

|          |                              |            |            |              |              |              |           | 0xE2         |

|          |                              |            |            |              |              |              |           |              |

| Bit7:    | WEAKPUD: P                   |            |            |              |              |              |           |              |

|          | 0: Weak Pull-u               | •          | · ·        | or Ports who | se I/O are o | configured a | is analog | input).      |

|          | 1: Weak Pull-u               | •          |            |              |              |              |           |              |

| Bit6:    | XBARE: Cross                 |            | Э.         |              |              |              |           |              |

|          | 0: Crossbar di               |            |            |              |              |              |           |              |

|          | 1: Crossbar er               |            |            |              |              |              |           |              |

| Bit5:    | T1E: T1 Enab                 |            |            |              |              |              |           |              |

|          | 0: T1 unavaila               |            | pin.       |              |              |              |           |              |

|          | 1: T1 routed to              | •          |            |              |              |              |           |              |

| Bit4:    | T0E: T0 Enab                 | -          |            |              |              |              |           |              |

|          | 0: T0 unavaila               |            | pin.       |              |              |              |           |              |

|          | 1: T0 routed to              |            |            |              |              |              |           |              |

| Bit3:    | ECIE: PCA0 E                 |            |            | Enable       |              |              |           |              |

|          | 0: ECI unavail               |            | •          |              |              |              |           |              |

|          | 1: ECI routed                |            |            |              |              |              |           |              |

| Bit2:    | Unused. Read                 |            |            |              |              |              |           |              |

| Bits1-0: | PCA0ME: PC                   |            |            |              |              |              |           |              |

|          | 00: All PCA I/0              |            | •          | oins.        |              |              |           |              |

|          | 01: CEX0 routed to Port pin. |            |            |              |              |              |           |              |

|          | 10: CEX0, CE                 |            |            |              |              |              |           |              |

|          | 11: CEX0, CE                 | X1, CEX2 I | outed to P | ort pins.    |              |              |           |              |

|          |                              |            |            |              |              |              |           |              |

|          |                              |            |            |              |              |              |           |              |

Figure 14.6. XBR1: Port I/O Crossbar Register 1

| R                                                                                                             |                           | R/W                                                                                                     | R/W          | R             |                 | R/W             | R/W           | Reset Value        |  |

|---------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------|--------------|---------------|-----------------|-----------------|---------------|--------------------|--|

| MASTEF                                                                                                        | TXMODE                    | STA                                                                                                     | STO          | ACKRQ         | ARBLOST         | ACK             | SI            | 0000000            |  |

| Bit7                                                                                                          | Bit6                      | Bit5                                                                                                    | Bit4         | Bit3          | Bit2            | Bit1            | Bit0          | Bit<br>Addressable |  |

|                                                                                                               |                           |                                                                                                         |              |               |                 |                 | SFR Address   |                    |  |

|                                                                                                               |                           |                                                                                                         |              |               |                 |                 |               |                    |  |

| Bit7:                                                                                                         | MASTER: SM                | /IBus Maste                                                                                             | er/Slave Inc | licator.      |                 |                 |               |                    |  |

|                                                                                                               | This read-onl             |                                                                                                         |              |               | s operating a   | as a master     | r.            |                    |  |

|                                                                                                               | 0: SMBus op               |                                                                                                         |              |               |                 |                 |               |                    |  |

|                                                                                                               | 1: SMBus op               |                                                                                                         |              |               |                 |                 |               |                    |  |

| Bit6:                                                                                                         | TXMODE: SI                |                                                                                                         |              |               |                 |                 |               |                    |  |

|                                                                                                               | This read-onl             |                                                                                                         |              | ie SMBus i    | s operating a   | as a transm     | nitter.       |                    |  |

|                                                                                                               | 0: SMBus in I             |                                                                                                         |              |               |                 |                 |               |                    |  |

| Bit5:                                                                                                         | 1: SMBus in<br>STA: SMBus |                                                                                                         | wode.        |               |                 |                 |               |                    |  |

| DIIJ.                                                                                                         | Write:                    | Start riay.                                                                                             |              |               |                 |                 |               |                    |  |

|                                                                                                               | 0: No Start ge            | enerated                                                                                                |              |               |                 |                 |               |                    |  |

|                                                                                                               | 1: When oper              |                                                                                                         | master, a S  | TART cond     | lition is trans | mitted if the   | e bus is fre  | e (If the bus      |  |

|                                                                                                               | is not free, th           |                                                                                                         |              |               |                 |                 |               |                    |  |

|                                                                                                               | STA is set by             |                                                                                                         |              |               |                 |                 |               | ,                  |  |

|                                                                                                               | next ACK cyc              |                                                                                                         |              |               | •               |                 | •             |                    |  |

|                                                                                                               | Read:                     |                                                                                                         |              |               |                 |                 |               |                    |  |

|                                                                                                               | 0: No Start or            |                                                                                                         |              | ed.           |                 |                 |               |                    |  |

|                                                                                                               | 1: Start or rep           |                                                                                                         |              |               |                 |                 |               |                    |  |

| Bit4:                                                                                                         | STO: SMBus                | Stop Flag.                                                                                              |              |               |                 |                 |               |                    |  |

|                                                                                                               | Write:                    |                                                                                                         |              |               |                 |                 |               |                    |  |

|                                                                                                               | 0: No STOP                |                                                                                                         |              |               | dition to be tr | o o o oo itto d | offer the pe  |                    |  |

|                                                                                                               | 1: Setting ST cycle. When |                                                                                                         |              |               |                 |                 |               |                    |  |

|                                                                                                               | and STO are               |                                                                                                         |              |               |                 |                 |               |                    |  |

|                                                                                                               | Read:                     | sel, a 510                                                                                              |              |               |                 | i by a STAI     |               | 11.                |  |

|                                                                                                               | 0: No Stop co             | ndition det                                                                                             | ected        |               |                 |                 |               |                    |  |

|                                                                                                               | 1: Stop condi             |                                                                                                         |              | ve Mode) o    | or pendina (if  | in Master       | Mode).        |                    |  |

| Bit3:                                                                                                         | ACKRQ: SMI                |                                                                                                         | •            |               | p =             |                 |               |                    |  |

|                                                                                                               | This read-onl             |                                                                                                         | •            |               | /Bus has rec    | eived a by      | te and nee    | ds the ACK         |  |

|                                                                                                               | bit to be writte          |                                                                                                         |              |               |                 |                 |               |                    |  |

| Bit2:                                                                                                         | ARBLOST: S                | MBus Arbit                                                                                              | ration Lost  | Indicator.    |                 |                 |               |                    |  |

|                                                                                                               | This read-onl             | •                                                                                                       | -            |               |                 |                 | •             | ting as a          |  |

|                                                                                                               | transmitter. A            |                                                                                                         |              | a slave indi  | cates a bus     | error condi     | tion.         |                    |  |

| Bit1:                                                                                                         | ACK: SMBus                |                                                                                                         |              |               |                 |                 |               |                    |  |

|                                                                                                               | This bit define           |                                                                                                         |              |               |                 | -               |               |                    |  |

|                                                                                                               | ten each time             |                                                                                                         |              |               |                 |                 |               |                    |  |

|                                                                                                               | 0: A "not acki            | -                                                                                                       | nas been re  | eceived (if i | n iransmitte    | r woae) Of      | x will be tra | insmitted (if      |  |

|                                                                                                               |                           | ceiver Mode).<br>"acknowledge" has been received (if in Transmitter Mode) OR will be transmitted (if in |              |               |                 |                 |               |                    |  |

|                                                                                                               | Receiver Mo               | -                                                                                                       | s been lece  |               |                 |                 |               | sinitted (ii in    |  |

| Bit0:                                                                                                         | SI: SMBus In              | ,                                                                                                       | n            |               |                 |                 |               |                    |  |

| Dito.                                                                                                         |                           | •                                                                                                       | -            | e condition   | s listed in Ta  | hle 15 3 S      | l must he i   | cleared hv         |  |

| This bit is set by hardware under the conditions listed software. While SI is set, SCL is held low and the SM |                           |                                                                                                         |              |               |                 |                 |               |                    |  |

### Figure 15.6. SMB0CN: SMBus Control Register

|                    |                                 |                        | Frequ                            | iency: 3.6864 M              | MHz                                             |                  |                                     |