Welcome to E-XFL.COM

### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

### Details

E·XFl

| Product Status          | Active                                                                 |

|-------------------------|------------------------------------------------------------------------|

| Туре                    | Fixed Point                                                            |

| Interface               | SPI, SSP, UART                                                         |

| Clock Rate              | 600MHz                                                                 |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 328kB                                                                  |

| Voltage - I/O           | 2.50V, 3.30V                                                           |

| Voltage - Core          | 1.35V                                                                  |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                        |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 256-LFBGA, CSPBGA                                                      |

| Supplier Device Package | 256-CSPBGA (12x12)                                                     |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf561skbcz-6v |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ADSP-BF561: Blackfin Embedded Symmetric Multiprocessor Data Sheet

### **Emulator Manuals**

- HPUSB, USB, and HPPCI Emulator User's Guide

- ICE-1000/ICE-2000 Emulator User's Guide

- ICE-100B Emulator User's Guide

### **Evaluation Kit Manuals**

- ADSP-BF561 EZ-KIT Lite<sup>®</sup> Evaluation System Manual

- Blackfin<sup>®</sup> A-V EZ-Extender<sup>®</sup> Manual

- Blackfin<sup>®</sup> EZ-Extender<sup>®</sup> Manual

- Blackfin<sup>®</sup> FPGA EZ-Extender<sup>®</sup> Manual

- Blackfin<sup>®</sup>/SHARC<sup>®</sup> USB EZ-Extender<sup>®</sup> Manual

### **Integrated Circuit Anomalies**

• ADSP-BF561 Blackfin Anomaly List for Revisions 0.3, 0.5

### **Processor Manuals**

- ADSP-BF561 Blackfin

Processor Hardware Reference

- ADSP-BF5xx/ADSP-BF60x Blackfin<sup>®</sup> Processor Programming Reference

- Blackfin Processors: Manuals

### **Product Highlight**

- ADSP-BF561 Blackfin Dual-Core Embedded Processor

- Blackfin Processor Family Product Highlight

- EZ-KIT Lite for Analog Devices ADSP-BF561 Blackfin Processor

### **Software Manuals**

- CrossCore<sup>®</sup> Embedded Studio 2.5.0 Assembler and Preprocessor Manual

- CrossCore<sup>®</sup> Embedded Studio 2.5.0 C/C++ Compiler and Library Manual for Blackfin Processors

- CrossCore<sup>®</sup> Embedded Studio 2.5.0 Linker and Utilities Manual

- CrossCore<sup>®</sup> Embedded Studio 2.5.0 Loader and Utilities Manual

- CrossCore<sup>®</sup> Software Licensing Guide

- IwIP for CrossCore® Embedded Studio 1.0.0 User's Guide

- VisualDSP++<sup>®</sup> 5.0 Assembler and Preprocessor Manual

- VisualDSP++<sup>®</sup> 5.0 C/C++ Compiler and Library Manual for Blackfin Processors

- VisualDSP++<sup>®</sup> 5.0 Device Drivers and System Services Manual for Blackfin Processors

- VisualDSP++<sup>®</sup> 5.0 Kernel (VDK) Users Guide

- VisualDSP++<sup>®</sup> 5.0 Licensing Guide

- VisualDSP++<sup>®</sup> 5.0 Linker and Utilities Manual

- VisualDSP++<sup>®</sup> 5.0 Loader and Utilities Manual

- VisualDSP++<sup>®</sup> 5.0 Product Release Bulletin

- VisualDSP++<sup>®</sup> 5.0 Quick Installation Reference Card

- VisualDSP++<sup>®</sup> 5.0 Users Guide

### SOFTWARE AND SYSTEMS REQUIREMENTS

• Software and Tools Anomalies Search

### TOOLS AND SIMULATIONS $\square$

- ADSP-BF561 Blackfin Processor BSDL File 256-Ball CSP BGA Package

- ADSP-BF561 Blackfin Processor BSDL File 256-Ball Sparse CSP\_BGA Package

- ADSP-BF561 Blackfin Processor BSDL File 297-Ball PBGA Package

- ADSP-BF561 Blackfin Processor Core B BSDL File All Packages

- Designing with BGA

- Blackfin Processors Software and Tools

- ADSP-BF561 Blackfin Processor IBIS Datafile for 12x12 CSP BGA Package (02/2008)

- ADSP-BF561 Blackfin Processor IBIS Datafile for 17x17 CSP BGA Package (11/2008)

- ADSP-BF561 Blackfin Processor IBIS Datafile for 27x27 PBGA Package (02/2008)

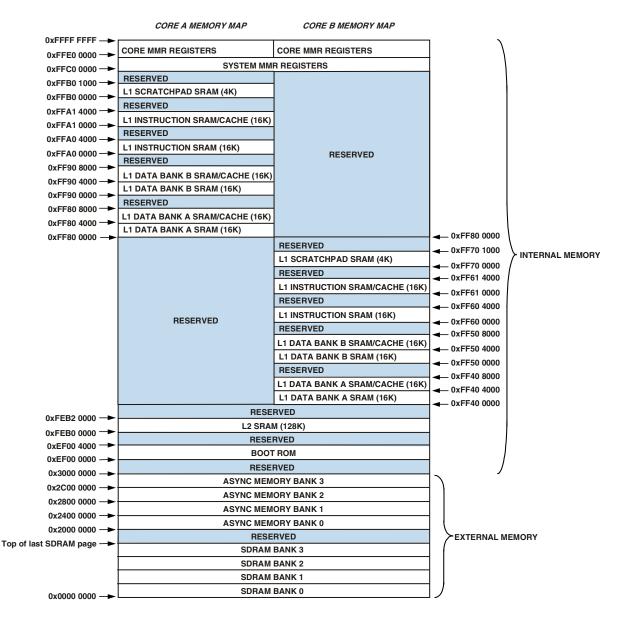

Figure 3. Memory Map

The fourth on-chip memory system is the L2 SRAM memory array which provides 128K bytes of high speed SRAM operating at one half the frequency of the core, and slightly longer latency than the L1 memory banks. The L2 memory is a unified instruction and data memory and can hold any mixture of code and data required by the system design. The Blackfin cores share a dedicated low latency 64-bit wide data path port into the L2 SRAM memory.

Each Blackfin core processor has its own set of core Memory Mapped Registers (MMRs) but share the same system MMR registers and 128K bytes L2 SRAM memory.

### External (Off-Chip) Memory

The ADSP-BF561 external memory is accessed via the External Bus Interface Unit (EBIU). This interface provides a glueless connection to up to four banks of synchronous DRAM (SDRAM) as well as up to four banks of asynchronous memory devices, including flash, EPROM, ROM, SRAM, and memory mapped I/O devices.

The PC133-compliant SDRAM controller can be programmed to interface to up to four banks of SDRAM, with each bank containing between 16M bytes and 128M bytes providing access to up to 512M bytes of SDRAM. Each bank is independently programmable and is contiguous with adjacent banks regardless of the sizes of the different banks or their placement. This allows

flexible configuration and upgradability of system memory while allowing the core to view all SDRAM as a single, contiguous, physical address space.

The asynchronous memory controller can also be programmed to control up to four banks of devices with very flexible timing parameters for a wide variety of devices. Each bank occupies a 64M byte segment regardless of the size of the devices used so that these banks will only be contiguous if fully populated with 64M bytes of memory.

### I/O Memory Space

Blackfin processors do not define a separate I/O space. All resources are mapped through the flat 32-bit address space. Onchip I/O devices have their control registers mapped into memory mapped registers (MMRs) at addresses near the top of the 4G byte address space. These are separated into two smaller blocks, one which contains the control MMRs for all core functions, and the other which contains the registers needed for setup and control of the on-chip peripherals outside of the core. The core MMRs are accessible only by the core and only in supervisor mode and appear as reserved space by on-chip peripherals. The system MMRs are accessible by the core in supervisor mode and can be mapped as either visible or reserved to other devices, depending on the system protection model desired.

### Booting

The ADSP-BF561 contains a small boot kernel, which configures the appropriate peripheral for booting. If the ADSP-BF561 is configured to boot from boot ROM memory space, the processor starts executing from the on-chip boot ROM.

### **Event Handling**

The event controller on the ADSP-BF561 handles all asynchronous and synchronous events to the processor. The ADSP-BF561 provides event handling that supports both nesting and prioritization. Nesting allows multiple event service routines to be active simultaneously. Prioritization ensures that servicing of a higher priority event takes precedence over servicing of a lower priority event. The controller provides support for five different types of events:

- Emulation An emulation event causes the processor to enter emulation mode, allowing command and control of the processor via the JTAG interface.

- Reset This event resets the processor.

- Nonmaskable Interrupt (NMI) The NMI event can be generated by the software watchdog timer or by the NMI input signal to the processor. The NMI event is frequently used as a power-down indicator to initiate an orderly shutdown of the system.

- Exceptions Events that occur synchronously to program flow, i.e., the exception will be taken before the instruction is allowed to complete. Conditions such as data alignment violations or undefined instructions cause exceptions.

• Interrupts – Events that occur asynchronously to program flow. They are caused by timers, peripherals, input pins, and an explicit software instruction.

Each event has an associated register to hold the return address and an associated "return from event" instruction. When an event is triggered, the state of the processor is saved on the supervisor stack.

The ADSP-BF561 event controller consists of two stages: the Core Event Controller (CEC) and the System Interrupt Controller (SIC). The Core Event Controller works with the System Interrupt Controller to prioritize and control all system events. Conceptually, interrupts from the peripherals enter into the SIC, and are then routed directly into the general-purpose interrupts of the CEC.

### Core Event Controller (CEC)

The CEC supports nine general-purpose interrupts (IVG15–7), in addition to the dedicated interrupt and exception events. Of these general-purpose interrupts, the two lowest priority interrupts (IVG15–14) are recommended to be reserved for software interrupt handlers, leaving seven prioritized interrupt inputs to support the peripherals of the ADSP-BF561. Table 1 describes the inputs to the CEC, identifies their names in the Event Vector Table (EVT), and lists their priorities.

| Priority       |                        |           |

|----------------|------------------------|-----------|

| (0 is Highest) | Event Class            | EVT Entry |

| 0              | Emulation/Test Control | EMU       |

| 1              | Reset                  | RST       |

| 2              | Nonmaskable Interrupt  | NMI       |

| 3              | Exceptions             | EVX       |

| 4              | Global Enable          |           |

| 5              | Hardware Error         | IVHW      |

| 6              | Core Timer             | IVTMR     |

| 7              | General Interrupt 7    | IVG7      |

| 8              | General Interrupt 8    | IVG8      |

| 9              | General Interrupt 9    | IVG9      |

| 10             | General Interrupt 10   | IVG10     |

| 11             | General Interrupt 11   | IVG11     |

| 12             | General Interrupt 12   | IVG12     |

| 13             | General Interrupt 13   | IVG13     |

| 14             | General Interrupt 14   | IVG14     |

| 15             | General Interrupt 15   | IVG15     |

#### Table 1. Core Event Controller (CEC)

### System Interrupt Controller (SIC)

The System Interrupt Controller provides the mapping and routing of events from the many peripheral interrupt sources to the prioritized general-purpose interrupt inputs of the CEC. Although the ADSP-BF561 provides a default mapping, the user can alter the mappings and priorities of interrupt events by

After a reset, software can determine if the watchdog was the source of the hardware reset by interrogating a status bit in the timer control register, which is set only upon a watchdog generated reset.

The timer is clocked by the system clock (SCLK) at a maximum frequency of  $f_{\mbox{\tiny SCLK}}$

### TIMERS

There are 14 programmable timer units in the ADSP-BF561.

Each of the 12 general-purpose timer units can be independently programmed as a Pulse Width Modulator (PWM), internally or externally clocked timer, or pulse width counter. The general-purpose timer units can be used in conjunction with the UART to measure the width of the pulses in the data stream to provide an autobaud detect function for a serial channel. The general-purpose timers can generate interrupts to the processor core providing periodic events for synchronization, either to the processor clock or to a count of external signals.

In addition to the 12 general-purpose programmable timers, another timer is also provided for each core. These extra timers are clocked by the internal processor clock (CCLK) and are typically used as a system tick clock for generation of operating system periodic interrupts.

### **SERIAL PORTS (SPORTs)**

The ADSP-BF561 incorporates two dual-channel synchronous serial ports (SPORT0 and SPORT1) for serial and multiprocessor communications. The SPORTs support the following features:

- I<sup>2</sup>S capable operation.

- Bidirectional operation Each SPORT has two sets of independent transmit and receive pins, enabling eight channels of I<sup>2</sup>S stereo audio.

- Buffered (8-deep) transmit and receive ports Each port has a data register for transferring data words to and from other DSP components and shift registers for shifting data in and out of the data registers.

- Clocking Each transmit and receive port can either use an external serial clock or generate its own, in frequencies ranging from ( $f_{sclk}/131,070$ ) Hz to ( $f_{sclk}/2$ ) Hz.

- Word length Each SPORT supports serial data words from 3 bits to 32 bits in length, transferred most significant bit first or least significant bit first.

- Framing Each transmit and receive port can run with or without frame sync signals for each data word. Frame sync signals can be generated internally or externally, active high or low, and with either of two pulse widths and early or late frame sync.

- Companding in hardware Each SPORT can perform A-law or μ-law companding according to ITU recommendation G.711. Companding can be selected on the transmit and/or receive channel of the SPORT without additional latencies.

- DMA operations with single-cycle overhead Each SPORT can automatically receive and transmit multiple buffers of memory data. The DSP can link or chain sequences of DMA transfers between a SPORT and memory.

- Interrupts Each transmit and receive port generates an interrupt upon completing the transfer of a data word or after transferring an entire data buffer or buffers through DMA.

- Multichannel capability Each SPORT supports 128 channels out of a 1,024-channel window and is compatible with the H.100, H.110, MVIP-90, and HMVIP standards.

An additional 250 mV of SPORT input hysteresis can be enabled by setting Bit 15 of the PLL\_CTL register. When this bit is set, all SPORT input pins have the increased hysteresis.

### SERIAL PERIPHERAL INTERFACE (SPI) PORT

The ADSP-BF561 processor has an SPI-compatible port that enables the processor to communicate with multiple SPI-compatible devices.

The SPI interface uses three pins for transferring data: two data pins (master output-slave input, MOSI, and master input-slave output, MISO) and a clock pin (serial clock, SCK). An SPI chip select input pin (SPISS) lets other SPI devices select the processor, and seven SPI chip select output pins (SPISEL7–1) let the processor select other SPI devices. The SPI select pins are reconfigured programmable flag pins. Using these pins, the SPI port provides a full-duplex, synchronous serial interface which supports both master/slave modes and multimaster environments.

The baud rate and clock phase/polarities for the SPI port are programmable, and it has an integrated DMA controller, configurable to support transmit or receive data streams. The SPI DMA controller can only service unidirectional accesses at any given time.

The SPI port clock rate is calculated as:

SPI Clock Rate =

$$\frac{f_{SCLK}}{2 \times SPI BAUD}$$

Where the 16-bit SPI\_BAUD register contains a value of 2 to 65,535.

During transfers, the SPI port simultaneously transmits and receives by serially shifting data in and out on its two serial data lines. The serial clock line synchronizes the shifting and sampling of data on the two serial data lines.

### **UART PORT**

The ADSP-BF561 processor provides a full-duplex universal asynchronous receiver/transmitter (UART) port, which is fully compatible with PC-standard UARTs. The UART port provides a simplified UART interface to other peripherals or hosts, supporting full-duplex, DMA-supported, asynchronous transfers of serial data. The UART port includes support for 5 data bits to 8 data bits, 1 stop bit or 2 stop bits, and none, even, or odd parity. The UART port supports two modes of operation:

regulator for the processor can be shut off by writing b#00 to the FREQ bits of the VR\_CTL register. This disables both CCLK and SCLK. Furthermore, it sets the internal power supply voltage ( $V_{DDINT}$ ) to 0 V to provide the lowest static power dissipation. Any critical information stored internally (memory contents, register contents, etc.) must be written to a nonvolatile storage device prior to removing power if the processor state is to be preserved. Since  $V_{DDEXT}$  is still supplied in this mode, all of the external pins three-state, unless otherwise specified. This allows other devices that may be connected to the processor to have power still applied without drawing unwanted current. The internal supply regulator can be woken up by asserting the RESET pin.

### **Power Savings**

As shown in Table 4, the ADSP-BF561 supports two different power domains. The use of multiple power domains maximizes flexibility, while maintaining compliance with industry standards and conventions. By isolating the internal logic of the ADSP-BF561 into its own power domain, separate from the I/O, the processor can take advantage of Dynamic Power Management, without affecting the I/O devices. There are no sequencing requirements for the various power domains.

#### Table 4. ADSP-BF561 Power Domains

| Power Domain       | V <sub>DD</sub> Range |

|--------------------|-----------------------|

| All internal logic | V <sub>DDINT</sub>    |

| I/O                | V <sub>DDEXT</sub>    |

The power dissipated by a processor is largely a function of the clock frequency of the processor and the square of the operating voltage. For example, reducing the clock frequency by 25% results in a 25% reduction in dynamic power dissipation, while reducing the voltage by 25% reduces dynamic power dissipation by more than 40%. Further, these power savings are additive, in that if the clock frequency and supply voltage are both reduced, the power savings can be dramatic.

The dynamic power management feature of the ADSP-BF561 allows both the processor's input voltage ( $V_{\text{DDINT}}$ ) and clock frequency ( $f_{\text{CCLK}}$ ) to be dynamically controlled.

The savings in power dissipation can be modeled using the power savings factor and % power savings calculations.

The power savings factor is calculated as:

power savings factor

$$= \frac{f_{CCLKRED}}{f_{CCLKNOM}} \times \left(\frac{V_{DDINTRED}}{V_{DDINTNOM}}\right)^2 \times \left(\frac{t_{RED}}{t_{NOM}}\right)^2$$

where the variables in the equations are:

$f_{CCLKNOM}$  is the nominal core clock frequency

$f_{CCLKRED}$  is the reduced core clock frequency

$V_{DDINTNOM}$  is the nominal internal supply voltage

$V_{DDINTRED}$  is the reduced internal supply voltage

$t_{NOM}$  is the duration running at  $f_{CCLKNOM}$

$t_{RED}$  is the duration running at  $f_{CCLKRED}$

The percent power savings is calculated as:

% power savings =  $(1 - power savings factor) \times 100\%$

### **VOLTAGE REGULATION**

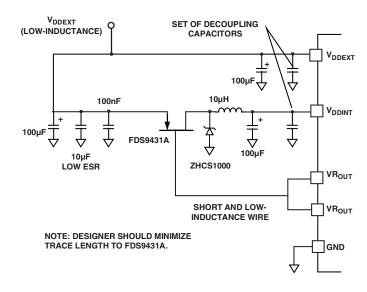

The ADSP-BF561 processor provides an on-chip voltage regulator that can generate appropriate  $V_{\text{DDINT}}$  voltage levels from the  $V_{\text{DDEXT}}$  supply. See Operating Conditions on Page 20 for regulator tolerances and acceptable  $V_{\text{DDEXT}}$  ranges for specific models.

Figure 4 shows the typical external components required to complete the power management system. The regulator controls the internal logic voltage levels and is programmable with the voltage regulator control register (VR\_CTL) in increments of 50 mV. To reduce standby power consumption, the internal voltage regulator can be programmed to remove power to the processor core while keeping I/O power ( $V_{DDEXT}$ ) supplied. While in the hibernate state,  $V_{DDEXT}$  can still be applied, thus eliminating the need for external buffers. The voltage regulator can be activated from this power-down state by asserting RESET, which will then initiate a boot sequence. The regulator can also be disabled and bypassed at the user's discretion.

The internal voltage regulation feature is not available on any of the 600 MHz speed grade models or automotive grade models. External voltage regulation is required to ensure correct operation of these parts at 600 MHz.

Figure 4. Voltage Regulator Circuit

### Voltage Regulator Layout Guidelines

Regulator external component placement, board routing, and bypass capacitors all have a significant effect on noise injected into the other analog circuits on-chip. The VROUT1–0 traces and voltage regulator external components should be considered as noise sources when doing board layout and should not be routed or placed near sensitive circuits or components on the

board. All internal and I/O power supplies should be well bypassed with bypass capacitors placed as close to the ADSP-BF561 processors as possible.

For further details on the on-chip voltage regulator and related board design guidelines, see the *Switching Regulator Design Considerations for ADSP-BF533 Blackfin Processors (EE-228)* applications note on the Analog Devices web site (www.analog.com)—use site search on "EE-228".

### **CLOCK SIGNALS**

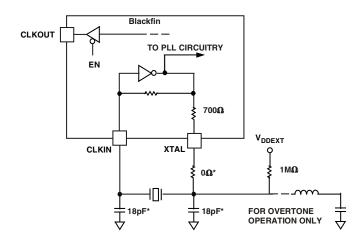

The ADSP-BF561 processor can be clocked by an external crystal, a sine wave input, or a buffered, shaped clock derived from an external clock oscillator.

If an external clock is used, it should be a TTL compatible signal and must not be halted, changed, or operated below the specified frequency during normal operation. This signal is connected to the processor's CLKIN pin. When an external clock is used, the XTAL pin must be left unconnected.

Alternatively, because the ADSP-BF561 processor includes an on-chip oscillator circuit, an external crystal may be used. For fundamental frequency operation, use the circuit shown in Figure 5. A parallel-resonant, fundamental frequency, microprocessor-grade crystal is connected across the CLKIN and XTAL pins. The on-chip resistance between CLKIN and the XTAL pin is in the 500 k $\Omega$  range. Further parallel resistors are typically not recommended. The two capacitors and the series resistor shown in Figure 5 fine tune the phase and amplitude of the sine frequency. The capacitor and resistor values shown in Figure 5 are typical values only. The capacitor values are dependent upon the crystal manufacturer's load capacitance recommendations and the physical PCB layout. The resistor value depends on the drive level specified by the crystal manufacturer. System designs should verify the customized values based on careful investigation on multiple devices over the allowed temperature range.

A third-overtone crystal can be used at frequencies above 25 MHz. The circuit is then modified to ensure crystal operation only at the third overtone, by adding a tuned inductor circuit as shown in Figure 5.

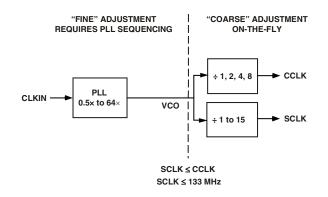

As shown in Figure 6, the core clock (CCLK) and system peripheral clock (SCLK) are derived from the input clock (CLKIN) signal. An on-chip PLL is capable of multiplying the CLKIN signal by a user-programmable 0.5× to 64× multiplication factor. The default multiplier is 10×, but it can be modified by a software instruction sequence. On the fly frequency changes can be effected by simply writing to the PLL\_DIV register.

All on-chip peripherals are clocked by the system clock (SCLK). The system clock frequency is programmable by means of the SSEL3–0 bits of the PLL\_DIV register. The values programmed

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED DEPENDING ON THE CRYSTAL AND LAYOUT. PLEASE ANALYZE CAREFULLY.

Figure 5. External Crystal Connections

into the SSEL fields define a divide ratio between the PLL output (VCO) and the system clock. SCLK divider values are 1 through 15. Table 5 illustrates typical system clock ratios.

Table 5. Example System Clock Ratios

| Signal Name | Divider Ratio | Example<br>Ratios (N |      |  |

|-------------|---------------|----------------------|------|--|

| SSEL3-0     | VCO/SCLK      | VCO                  | SCLK |  |

| 0001        | 1:1           | 100                  | 100  |  |

| 0110        | 6:1           | 300                  | 50   |  |

| 1010        | 10:1          | 500                  | 50   |  |

The maximum frequency of the system clock is  $f_{SCLK}$ . Note that the divisor ratio must be chosen to limit the system clock frequency to its maximum of  $f_{SCLK}$ . The SSEL value can be changed dynamically without any PLL lock latencies by writing the appropriate values to the PLL divisor register (PLL\_DIV).

### Table 8. Pin Descriptions (Continued)

| Pin Name              | Туре   | Function                                                                                                            | Driver<br>Type <sup>1</sup> |

|-----------------------|--------|---------------------------------------------------------------------------------------------------------------------|-----------------------------|

| SPORT1                |        |                                                                                                                     |                             |

| RSCLK1/PF30           | I/O    | Sport1 Receive Serial Clock/Programmable Flag                                                                       | D                           |

| RFS1/PF24             | I/O    | Sport1 Receive Frame Sync/Programmable Flag                                                                         | С                           |

| DR1PRI                | I      | Sport1 Receive Data Primary                                                                                         |                             |

| DR1SEC/PF25           | I/O    | Sport1 Receive Data Secondary/Programmable Flag                                                                     | С                           |

| TSCLK1/PF31           | I/O    | Sport1 Transmit Serial Clock/Programmable Flag                                                                      | D                           |

| TFS1/PF21             | I/O    | Sport1 Transmit Frame Sync/Programmable Flag                                                                        | С                           |

| DT1PRI/PF23           | I/O    | Sport1 Transmit Data Primary/Programmable Flag                                                                      | С                           |

| DT1SEC/PF22           | I/O    | Sport1 Transmit Data Secondary/Programmable Flag                                                                    | С                           |

| SPI                   |        |                                                                                                                     |                             |

| MOSI                  | I/O    | Master Out Slave In                                                                                                 | С                           |

| MISO                  | I/O    | Master In Slave Out (This pin should be pulled HIGH through a 4.7 k $\Omega$ resistor if booting via the SPI port.) | с                           |

| SCK                   | I/O    | SPI Clock                                                                                                           | D                           |

| UART                  |        |                                                                                                                     |                             |

| RX/ <i>PF27</i>       | I/O    | UART Receive/Programmable Flag                                                                                      | с                           |

| TX/PF26               | I/O    | UART Transmit/Programmable Flag                                                                                     | С                           |

| JTAG                  |        |                                                                                                                     |                             |

| EMU                   | 0      | Emulation Output                                                                                                    | с                           |

| TCK                   |        | JTAG Clock                                                                                                          | -                           |

| TDO                   | 0      | JTAG Serial Data Out                                                                                                | с                           |

| TDI                   | Ĩ      | JTAG Serial Data In                                                                                                 | •                           |

| TMS                   | l.     | JTAG Mode Select                                                                                                    |                             |

| TRST                  | 1      | JTAG Reset (This pin should be pulled LOW if JTAG is not used.)                                                     |                             |

| Clock                 |        |                                                                                                                     |                             |

| CLKIN                 |        | Clock/Crystal Input (This pin needs to be at a level or clocking.)                                                  |                             |

| XTAL                  | 0      | Crystal Connection                                                                                                  |                             |

| Mode Controls         | -      |                                                                                                                     |                             |

| RESET                 |        | Reset (This pin is always active during core power-on.)                                                             |                             |

| NMIO                  | l.     | Nonmaskable Interrupt Core A (This pin should be pulled LOW when not used.)                                         |                             |

| NMI1                  |        | Nonmaskable Interrupt Core B (This pin should be pulled LOW when not used.)                                         |                             |

| BMODE1-0              | l.     | Boot Mode Strap (These pins must be pulled to the state required for the desired boot mode.)                        |                             |

| SLEEP                 | 0      | Sleep                                                                                                               | с                           |

| BYPASS                | U U    | PLL BYPASS Control (Pull-up or pull-down Required.)                                                                 | C                           |

| Voltage Regulator     |        |                                                                                                                     |                             |

| V <sub>ROUT</sub> 1–0 | 0      | External FET Drive                                                                                                  |                             |

| Supplies              |        |                                                                                                                     |                             |

| V <sub>DDEXT</sub>    | Р      | Power Supply                                                                                                        |                             |

|                       | г<br>Р | Power Supply                                                                                                        |                             |

|                       | P<br>G | Power Supply<br>Power Supply Return                                                                                 |                             |

|                       |        |                                                                                                                     |                             |

| No Connection         | NC     | NC                                                                                                                  | <u> </u>                    |

<sup>1</sup> Refer to Figure 30 on Page 41 to Figure 34 on Page 42.

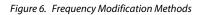

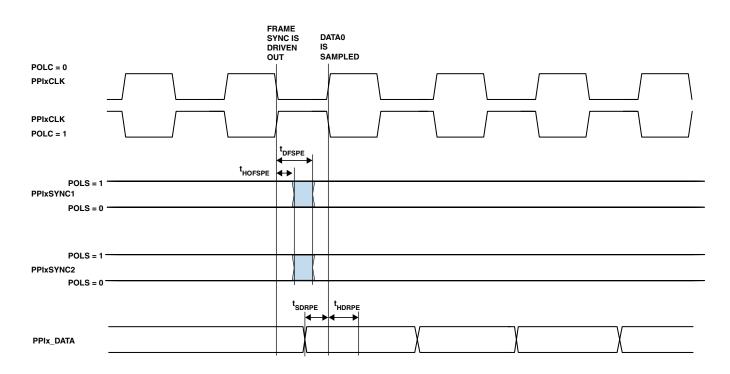

### Parallel Peripheral Interface Timing

Table 22, and Figure 14 through Figure 17 on Page 30, describe default Parallel Peripheral Interface operations.

If bit 4 of the PLL\_CTL register is set, then Figure 18 on Page 30 and Figure 19 on Page 31 apply.

### Table 22. Parallel Peripheral Interface Timing

| Param                        | neter                                    | Min  | Max | Unit |

|------------------------------|------------------------------------------|------|-----|------|

| Timing                       | Requirements                             |      |     |      |

| t <sub>pclkw</sub>           | PPIxCLK Width <sup>1</sup>               | 5.0  |     | ns   |

| t <sub>PCLK</sub>            | PPIxCLK Period <sup>1</sup>              | 13.3 |     | ns   |

| $\mathbf{t}_{\text{SFSPE}}$  | External Frame Sync Setup Before PPIxCLK | 4.0  |     | ns   |

| $\mathbf{t}_{\text{HFSPE}}$  | External Frame Sync Hold After PPIxCLK   | 1.0  |     | ns   |

| $\mathbf{t}_{\text{SDRPE}}$  | Receive Data Setup Before PPIxCLK        | 3.5  |     | ns   |

| $\mathbf{t}_{\text{HDRPE}}$  | Receive Data Hold After PPIxCLK          | 2.0  |     | ns   |

| Switch                       | ing Characteristics                      |      |     |      |

| $\mathbf{t}_{\text{DFSPE}}$  | Internal Frame Sync Delay After PPIxCLK  |      | 8.0 | ns   |

| $\mathbf{t}_{\text{HOFSPE}}$ | Internal Frame Sync Hold After PPIxCLK   | 1.7  |     | ns   |

| t <sub>DDTPE</sub>           | Transmit Data Delay After PPIxCLK        |      | 8.0 | ns   |

| $\mathbf{t}_{\text{HDTPE}}$  | Transmit Data Hold After PPIxCLK         | 2.0  |     | ns   |

<sup>1</sup> For PPI modes that use an internally generated frame sync, the PPIxCLK frequency cannot exceed  $f_{sclk}/2$ . For modes with no frame syncs or external frame syncs, PPIxCLK cannot exceed 75 MHz and  $f_{sclk}$  should be equal to or greater than PPIxCLK.

Figure 14. PPI GP Rx Mode with Internal Frame Sync Timing (Default)

Figure 19. PPI GP Tx Mode with External Frame Sync Timing (Bit 4 of PLL\_CTL Set)

### Serial Ports

Table 23 through Table 26 on Page 34 and Figure 20 on Page 33 through Figure 22 on Page 34 describe Serial Port operations.

### Table 23. Serial Ports—External Clock

| Parameter                     | irameter                                                                |      | Max  | Unit   |

|-------------------------------|-------------------------------------------------------------------------|------|------|--------|

| Timing Requirem               | ents                                                                    |      |      |        |

| t <sub>sfse</sub> TFSx/RFS>   | Setup Before TSCLKx/RSCLKx <sup>1</sup>                                 | 3.0  |      | ns     |

| t <sub>HFSE</sub> TFSx/RFS>   | Hold After TSCLKx/RSCLKx <sup>1</sup>                                   | 3.0  |      | ns     |

| t <sub>sDRE</sub> Receive D   | ata Setup Before RSCLKx <sup>1</sup>                                    | 3.0  |      | ns     |

| t <sub>HDRE</sub> Receive D   | ata Hold After RSCLKx <sup>1</sup>                                      | 3.0  |      | ns     |

| t <sub>sclkw</sub> TSCLKx/R   | SCLKx Width                                                             | 4.5  |      | ns     |

| t <sub>SCLK</sub> TSCLKx/R    | SCLKx Period                                                            | 15.0 |      | ns     |

| t <sub>supte</sub> Start-Up [ | Delay From SPORT Enable To First External TFSx                          | 4.0  |      | TSCLKx |

| t <sub>sudre</sub> Start-Up [ | Delay From SPORT Enable To First External RFSx                          | 4.0  |      | RSCLKx |

| Switching Charac              | teristics                                                               |      |      |        |

| t <sub>DFSE</sub> TFSx/RFSx   | Colay After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>2</sup> |      | 10.0 | ns     |

| t <sub>HOFSE</sub> TFSx/RFSx  | Hold After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>2</sup>  | 0.0  |      | ns     |

| t <sub>DDTE</sub> Transmit [  | Data Delay After TSCLKx <sup>2</sup>                                    |      | 10.0 | ns     |

| t <sub>HDTE</sub> Transmit [  | Data Hold After TSCLKx <sup>2</sup>                                     | 0.0  |      | ns     |

<sup>1</sup>Referenced to sample edge.

<sup>2</sup> Referenced to drive edge.

### Table 24. Serial Ports—Internal Clock

| Parar               | arameter                                                                          |      | Max | Unit |

|---------------------|-----------------------------------------------------------------------------------|------|-----|------|

| Timin               | g Requirements                                                                    |      |     |      |

| t <sub>sFSI</sub>   | TFSx/RFSx Setup Before TSCLKx/RSCLKx <sup>1</sup>                                 | 8.0  |     | ns   |

| t <sub>HFSI</sub>   | TFSx/RFSx Hold After TSCLKx/RSCLKx <sup>1</sup>                                   | -2.0 |     | ns   |

| t <sub>sdri</sub>   | Receive Data Setup Before RSCLKx <sup>1</sup>                                     | 6.0  |     | ns   |

| t <sub>HDRI</sub>   | Receive Data Hold After RSCLKx <sup>1</sup>                                       | 0.0  |     | ns   |

| t <sub>sclkw</sub>  | TSCLKx/RSCLKx Width                                                               | 4.5  |     | ns   |

| t <sub>sclk</sub>   | TSCLKx/RSCLKx Period                                                              | 15.0 |     | ns   |

| Switc               | hing Characteristics                                                              |      |     |      |

| t <sub>DFSI</sub>   | TFSx/RFSx Delay After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>2</sup> |      | 3.0 | ns   |

| t <sub>HOFSI</sub>  | TFSx/RFSx Hold After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>2</sup>  | -1.0 |     | ns   |

| t <sub>DDTI</sub>   | Transmit Data Delay After TSCLKx <sup>2</sup>                                     |      | 3.0 | ns   |

| t <sub>HDTI</sub>   | Transmit Data Hold After TSCLKx <sup>2</sup>                                      | -2.0 |     | ns   |

| t <sub>sclkiw</sub> | TSCLKx/RSCLKx Width                                                               | 4.5  |     | ns   |

<sup>1</sup>Referenced to sample edge.

<sup>2</sup> Referenced to drive edge.

### Table 25. Serial Ports—Enable and Three-State

| Param                     | neter                                                | Min  | Мах  | Unit |

|---------------------------|------------------------------------------------------|------|------|------|

| Switch                    | ing Characteristics                                  |      |      |      |

| t <sub>dtene</sub>        | Data Enable Delay from External TSCLKx <sup>1</sup>  | 0    |      | ns   |

| <b>t</b> <sub>DDTTE</sub> | Data Disable Delay from External TSCLKx <sup>1</sup> |      | 10.0 | ns   |

| t <sub>DTENI</sub>        | Data Enable Delay from Internal TSCLKx <sup>1</sup>  | -2.0 |      | ns   |

| t <sub>DDTTI</sub>        | Data Disable Delay from Internal TSCLKx <sup>1</sup> |      | 3.0  | ns   |

<sup>1</sup>Referenced to drive edge.

### Table 26. External Late Frame Sync

| Parameter                                                                                         |   | Max  | Unit |

|---------------------------------------------------------------------------------------------------|---|------|------|

| Switching Characteristics                                                                         |   |      |      |

| $t_{DDTLFSE}$ Data Delay from Late External TFSx or External RFSx with MCMEN = 1, MFD = $0^{1,2}$ |   | 10.0 | ns   |

| $t_{\text{DTENLFS}}$ Data Enable from Late FS or MCMEN = 1, MFD = $0^{1,2}$                       | 0 |      | ns   |

$^1\,MCMEN$  = 1, TFSx enable and TFSx valid follow  $t_{\mbox{\tiny DTENLFS}}$  and  $t_{\mbox{\tiny DDTLESE}}$

DTx

$^{2} If external RFSx/TFSx setup to RSCLKx/TSCLKx > t_{\text{SCLKE}}/2, then t_{\text{DDTTE/1}} and t_{\text{DTENE/1}} apply; otherwise t_{\text{DDTLFSE}} and t_{\text{DTENLFS}} apply.$

tDDTENFS

t<sub>DDTLFSE</sub>

### DRIVE SAMPLE DRIVE RSCLKx t<sub>HFSE/I</sub> t<sub>SFSE/I</sub> RFSx t<sub>DDTE/I</sub> tDDTENFS t<sub>HDTE/I</sub> 7 DTx 2ND BIT 1ST BIT t<sub>DDTLFSE</sub> LATE EXTERNAL TRANSMIT FS DRIVE SAMPLE DRIVE TSCLKx t<sub>HFSE/I</sub> t<sub>SFSE/I</sub> TFSx

#### EXTERNAL RECEIVE FS WITH MCMEN = 1, MFD = 0

t<sub>HDTE/I</sub>

1ST BIT

t<sub>DDTE/I</sub>

7

2ND BIT

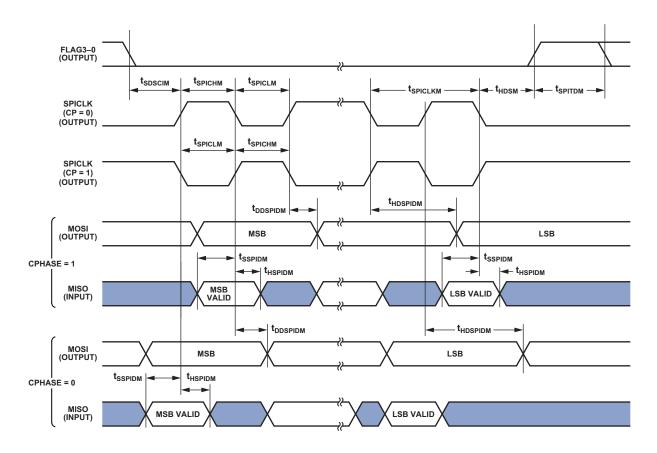

### Serial Peripheral Interface (SPI) Port— Master Timing

Table 27 and Figure 23 describe SPI port master operations.

Table 27. Serial Peripheral Interface (SPI) Port—Master Timing

| Parame               | ter                                             | Min                              | Max  | Unit |

|----------------------|-------------------------------------------------|----------------------------------|------|------|

| Timing F             | Requirements                                    |                                  |      |      |

| t <sub>sspidm</sub>  | Data Input Valid to SCK Edge (Data Input Setup) | 7.5                              |      | ns   |

| t <sub>HSPIDM</sub>  | SCK Sampling Edge to Data Input Invalid         | -1.5                             |      | ns   |

| Switchin             | ng Characteristics                              |                                  |      |      |

| t <sub>sdscim</sub>  | SPISELx Low to First SCK Edge                   | $2 	imes t_{\text{SCLK}} - 1.5$  |      | ns   |

| t <sub>spichm</sub>  | Serial Clock High Period                        | $2 	imes t_{\text{SCLK}} - 1.5$  |      | ns   |

| t <sub>spiclm</sub>  | Serial Clock Low Period                         | $2 \times t_{\text{SCLK}} - 1.5$ |      | ns   |

| t <sub>spiclk</sub>  | Serial Clock Period                             | $4 	imes t_{\text{SCLK}} - 1.5$  |      | ns   |

| t <sub>HDSM</sub>    | Last SCK Edge to SPISELx High                   | $2 	imes t_{\text{SCLK}} - 1.5$  |      | ns   |

| t <sub>spitdm</sub>  | Sequential Transfer Delay                       | $2 \times t_{\text{SCLK}} - 1.5$ |      | ns   |

|                      | SCK Edge to Data Out Valid (Data Out Delay)     | 0                                | 6    | ns   |

| t <sub>hdspidm</sub> | SCK Edge to Data Out Invalid (Data Out Hold)    | -1.0                             | +4.0 | ns   |

Figure 23. Serial Peripheral Interface (SPI) Port—Master Timing

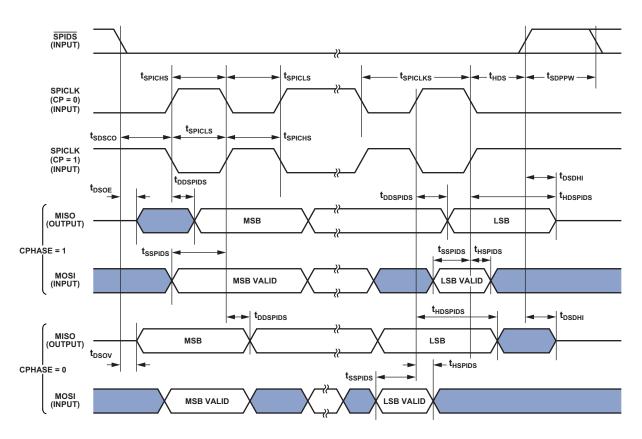

### Serial Peripheral Interface (SPI) Port— Slave Timing

Table 28 and Figure 24 describe SPI port slave operations.

### Table 28. Serial Peripheral Interface (SPI) Port—Slave Timing

| Param                     | eter                                            | Min                                          | Max | Unit |

|---------------------------|-------------------------------------------------|----------------------------------------------|-----|------|

| Timing                    | Requirements                                    |                                              |     |      |

| t <sub>spichs</sub>       | Serial Clock High Period                        | $2 \times t_{\scriptscriptstyle SCLK} - 1.5$ |     | ns   |

| t <sub>spicls</sub>       | Serial Clock Low Period                         | $2 \times t_{\scriptscriptstyle SCLK} - 1.5$ |     | ns   |

| t <sub>spiclk</sub>       | Serial Clock Period                             | $4 	imes t_{\text{SCLK}}$                    |     | ns   |

| $\mathbf{t}_{\text{HDS}}$ | Last SCK Edge to SPISS Not Asserted             | $2 	imes t_{\text{SCLK}} - 1.5$              |     | ns   |

| t <sub>spitds</sub>       | Sequential Transfer Delay                       | $2 	imes t_{\text{SCLK}} - 1.5$              |     | ns   |

| t <sub>sdsci</sub>        | SPISS Assertion to First SCK Edge               | $2 \times t_{\text{SCLK}} - 1.5$             |     | ns   |

| t <sub>sspid</sub>        | Data Input Valid to SCK Edge (Data Input Setup) | 1.6                                          |     | ns   |

| t <sub>HSPID</sub>        | SCK Sampling Edge to Data Input Invalid         | 1.6                                          |     | ns   |

| Switch                    | ing Characteristics                             |                                              |     |      |

| t <sub>DSOE</sub>         | SPISS Assertion to Data Out Active              | 0                                            | 8   | ns   |

| t <sub>dsdhi</sub>        | SPISS Deassertion to Data High Impedance        | 0                                            | 8   | ns   |

| t <sub>ddspid</sub>       | SCK Edge to Data Out Valid (Data Out Delay)     | 0                                            | 10  | ns   |

| t <sub>hdspid</sub>       | SCK Edge to Data Out Invalid (Data Out Hold)    | 0                                            | 10  | ns   |

Figure 24. Serial Peripheral Interface (SPI) Port—Slave Timing

The time for the voltage on the bus to decay by  $\Delta V$  is dependent on the capacitive load  $C_L$  and the load current  $I_L$ . This decay time can be approximated by the equation:

$$t_{DECAY} = (C_L \Delta V) / I_L$$

The time  $t_{\text{DECAY}}$  is calculated with test loads  $C_L$  and  $I_L$ , and with  $\Delta V$  equal to 0.5 V for  $V_{\text{DDEXT}}$  (nominal) = 2.5 V/3.3 V.

The time  $t_{DIS\_MEASURED}$  is the interval from when the reference signal switches, to when the output voltage decays  $\Delta V$  from the measured output high or output low voltage.

#### **Example System Hold Time Calculation**

To determine the data output hold time in a particular system, first calculate  $t_{DECAY}$  using the equation given above. Choose  $\Delta V$  to be the difference between the ADSP-BF561 processor's output voltage and the input threshold for the device requiring the hold time.  $C_L$  is the total bus capacitance (per data line), and  $I_L$  is the total leakage or three-state current (per data line). The hold time will be  $t_{DECAY}$  plus the various output disable times as specified in the Timing Specifications on Page 23 (for example  $t_{DSDAT}$  for an SDRAM write cycle as shown in SDRAM Interface Timing on Page 26).

Figure 38. Output Enable/Disable

#### **Capacitive Loading**

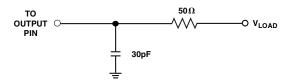

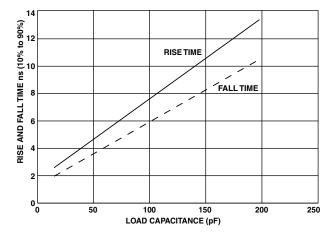

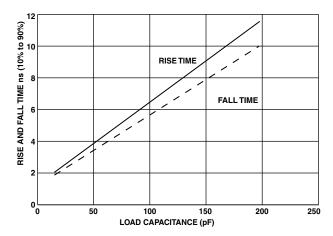

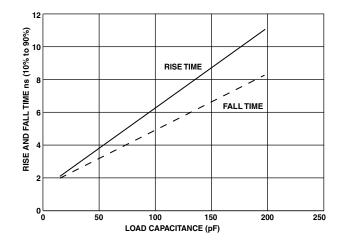

Output delays and holds are based on standard capacitive loads: 30 pF on all pins (see Figure 39).  $V_{\text{LOAD}}$  is 1.5 V for  $V_{\text{DDEXT}}$  (nominal) = 2.5 V/3.3 V. Figure 40 through Figure 47 on Page 44 show how output rise time varies with capacitance. The delay and hold specifications given should be derated by a factor derived from these figures. The graphs in these figures may not be linear outside the ranges shown.

Figure 39. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

Figure 40. Typical Rise and Fall Times (10% to 90%) versus Load Capacitance for Driver A at V<sub>DDEVT</sub> (min)

Figure 41. Typical Rise and Fall Times (10% to 90%) versus Load Capacitance for Driver A at V<sub>DDEXT</sub> (max)

Figure 42. Typical Rise and Fall Times (10% to 90%) versus Load Capacitance for Driver B at V<sub>DDEVT</sub> (min)

| Ball No. | Signal        | Ball No. | Signal | Ball No. | Signal  | Ball No. | Signal | Ball No. | Signal |

|----------|---------------|----------|--------|----------|---------|----------|--------|----------|--------|

| N9       | GND           | P5       | PF01   | R1       | PPI1D12 | R13      | RSCLK1 | Т9       | TDO    |

| N10      | BMODE1        | P6       | PF06   | R2       | PPI1D11 | R14      | TSCLK1 | T10      | TDI    |

| N11      | <b>BMODE0</b> | P7       | PF08   | R3       | PPI1D4  | R15      | NC     | T11      | EMU    |

| N12      | RX            | P8       | PF15   | R4       | PPI1D1  | R16      | TFS0   | T12      | MISO   |

| N13      | DR1SEC        | P9       | NMI1   | R5       | PF02    | T1       | VDDEXT | T13      | TX     |

| N14      | DT1SEC        | P10      | TMS    | R6       | PF07    | T2       | NC     | T14      | DR1PRI |

| N15      | RFS0          | P11      | NMI0   | R7       | PF11    | Т3       | PPI1D3 | T15      | DT1PRI |

| N16      | DATA30        | P12      | SCK    | R8       | PF14    | T4       | PPI1D2 | T16      | VDDEXT |

| P1       | PPI1D13       | P13      | RFS1   | R9       | TCK     | Т5       | PF03   |          |        |

| P2       | PPI1D8        | P14      | TFS1   | R10      | TRST    | Т6       | PF05   |          |        |

| Р3       | PPI1D6        | P15      | DR0SEC | R11      | SLEEP   | T7       | PF10   |          |        |

| P4       | PPI1D0        | P16      | DT0SEC | R12      | MOSI    | Т8       | PF13   |          |        |

Table 35. 256-Ball CSP\_BGA (17 mm × 17 mm) Ball Assignment (Numerically by Ball Number) (Continued)

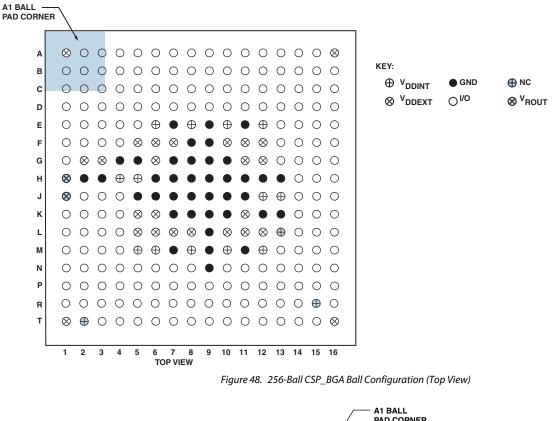

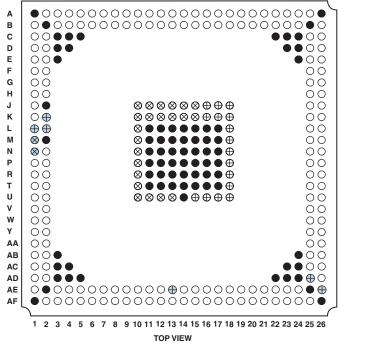

Figure 48 lists the top view of the 256-Ball CSP\_BGA ( $17 \text{ mm} \times 17 \text{ mm}$ ) ball configuration. Figure 49 lists the bottom view.

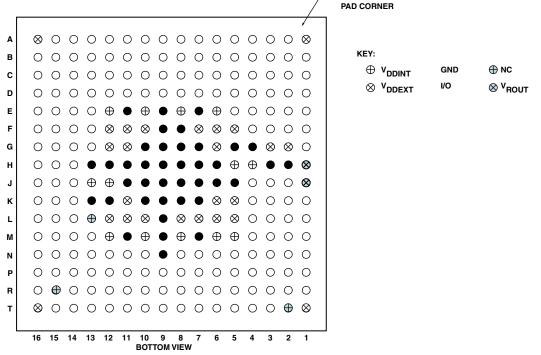

Figure 49. 256-Ball CSP\_BGA Ball Configuration (Bottom View)

| Ball No. | Signal  | Ball No. | Signal  |

|----------|--------|----------|--------|----------|--------|----------|---------|----------|---------|

| N09      | TDO    | P05      | GND    | R01      | PPI1D7 | R13      | TX/PF26 | T09      | TCK     |

| N10      | BMODE1 | P06      | PF5    | R02      | PPI1D6 | R14      | TSCLK1  | T10      | TMS     |

| N11      | MOSI   | P07      | PF11   | R03      | PPI1D2 | R15      | DT1PRI  | T11      | SLEEP   |

| N12      | GND    | P08      | PF15   | R04      | PPI1D0 | R16      | RFS0    | T12      | VDDEXT  |

| N13      | RFS1   | P09      | GND    | R05      | PF4    | T01      | VDDEXT  | T13      | RX/PF27 |

| N14      | GND    | P10      | TRST   | R06      | PF8    | T02      | PPI1D4  | T14      | DR1SEC  |

| N15      | DT0SEC | P11      | NMIO   | R07      | PF10   | T03      | VDDEXT  | T15      | DT1SEC  |

| N16      | TSCLK0 | P12      | GND    | R08      | PF14   | T04      | PF2     | T16      | VDDEXT  |

| P01      | PPI1D8 | P13      | RSCLK1 | R09      | NMI1   | T05      | PF6     |          |         |

| P02      | GND    | P14      | TFS1   | R10      | TDI    | T06      | VDDEXT  |          |         |

| P03      | PPI1D5 | P15      | RSCLK0 | R11      | EMU    | T07      | PF12    |          |         |

| P04      | PF0    | P16      | DR0SEC | R12      | MISO   | T08      | VDDEXT  |          |         |

Table 37. 256-Ball CSP\_BGA (12 mm × 12 mm) Ball Assignment (Numerically by Ball Number) (Continued)

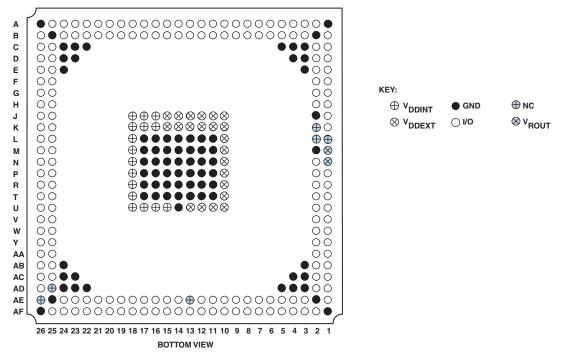

Figure 52 lists the top view of the 297-Ball PBGA ball configuration. Figure 53 lists the bottom view.

Figure 52. 297-Ball PBGA Ball Configuration (Top View)

Figure 53. 297-Ball PBGA Ball Configuration (Bottom View)

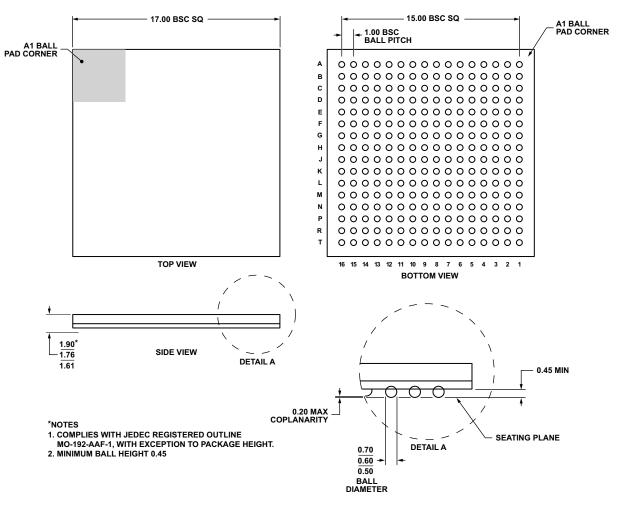

### **OUTLINE DIMENSIONS**

Dimensions in the outline dimension figures are shown in millimeters.

Figure 54. 256-Ball Chip Scale Package Ball Grid Array (CSP\_BGA) (BC-256-4)

### SURFACE-MOUNT DESIGN

Table 41 is provided as an aid to PCB design. For industrystandard design recommendations, refer to IPC-7351, *Generic Requirements for Surface Mount Design and Land Pattern Standard.*

Table 41. BGA Data for Use with Surface-Mount Design

| Package                     | Ball Attach Type    | Solder Mask Opening | Ball Pad Size    |

|-----------------------------|---------------------|---------------------|------------------|

| 256-Ball CSP_BGA (BC-256-1) | Solder Mask Defined | 0.30 mm diameter    | 0.43 mm diameter |

| 256-Ball CSP_BGA (BC-256-4) | Solder Mask Defined | 0.43 mm diameter    | 0.55 mm diameter |

| 297-Ball PBGA (B-297)       | Solder Mask Defined | 0.43 mm diameter    | 0.58 mm diameter |

### **AUTOMOTIVE PRODUCTS**

Some ADSP-BF561 models are available for automotive applications with controlled manufacturing. Note that these special models may have specifications that differ from the general release models. The automotive grade products shown in Table 42 are available for use in automotive applications. Contact your local ADI account representative or authorized ADI product distributor for specific product ordering information. Note that all automotive products are RoHS compliant.

### Table 42. Automotive Products

|                 |                | Speed Grade<br>(Max) <sup>3</sup> | Package Description | Package<br>Option |

|-----------------|----------------|-----------------------------------|---------------------|-------------------|

| ADBF561WBBZ5xx  | –40°C to +85°C | 533 MHz                           | 297-Ball PBGA       | B-297             |

| ADBF561WBBCZ5xx | –40°C to +85°C | 533 MHz                           | 256-Ball CSP_BGA    | BC-256-4          |

<sup>1</sup> xx denotes silicon revision.

<sup>2</sup> Referenced temperature is ambient temperature.

<sup>3</sup> The internal voltage regulation feature is not available. External voltage regulation is required to ensure correct operation.

### **ORDERING GUIDE**

| Model                           | Temperature<br>Range <sup>1</sup> | Speed Grade (Max) | Package Description | Package<br>Option |

|---------------------------------|-----------------------------------|-------------------|---------------------|-------------------|

| ADSP-BF561SKBCZ-6V <sup>2</sup> | 0°C to +70°C                      | 600 MHz           | 256-Ball CSP_BGA    | BC-256-1          |

| ADSP-BF561SKBCZ-5V <sup>2</sup> | 0°C to +70°C                      | 533 MHz           | 256-Ball CSP_BGA    | BC-256-1          |

| ADSP-BF561SKBCZ500 <sup>2</sup> | 0°C to +70°C                      | 500 MHz           | 256-Ball CSP_BGA    | BC-256-1          |

| ADSP-BF561SKB500                | 0°C to +70°C                      | 500 MHz           | 297-Ball PBGA       | B-297             |

| ADSP-BF561SKB600                | 0°C to +70°C                      | 600 MHz           | 297-Ball PBGA       | B-297             |

| ADSP-BF561SKBZ500 <sup>2</sup>  | 0°C to +70°C                      | 500 MHz           | 297-Ball PBGA       | B-297             |

| ADSP-BF561SKBZ600 <sup>2</sup>  | 0°C to +70°C                      | 600 MHz           | 297-Ball PBGA       | B-297             |

| ADSP-BF561SBB600                | -40°C to +85°C                    | 600 MHz           | 297-Ball PBGA       | B-297             |

| ADSP-BF561SBB500                | -40°C to +85°C                    | 500 MHz           | 297-Ball PBGA       | B-297             |

| ADSP-BF561SBBZ600 <sup>2</sup>  | -40°C to +85°C                    | 600 MHz           | 297-Ball PBGA       | B-297             |

| ADSP-BF561SBBZ500 <sup>2</sup>  | -40°C to +85°C                    | 500 MHz           | 297-Ball PBGA       | B-297             |

| ADSP-BF561SKBCZ-6A <sup>2</sup> | 0°C to +70°C                      | 600 MHz           | 256-Ball CSP_BGA    | BC-256-4          |

| ADSP-BF561SKBCZ-5A <sup>2</sup> | 0°C to +70°C                      | 500 MHz           | 256-Ball CSP_BGA    | BC-256-4          |

| ADSP-BF561SBBCZ-5A <sup>2</sup> | -40°C to +85°C                    | 500 MHz           | 256-Ball CSP_BGA    | BC-256-4          |

<sup>1</sup>Referenced temperature is ambient temperature.

$^{2}$ Z = RoHS compliant part.