Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

EXF

| Product Status                 | Obsolete                                                      |

|--------------------------------|---------------------------------------------------------------|

| Number of LABs/CLBs            | 2320                                                          |

| Number of Logic Elements/Cells | 20880                                                         |

| Total RAM Bits                 | 1622016                                                       |

| Number of I/O                  | 564                                                           |

| Number of Gates                | -                                                             |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 1152-BBGA, FCBGA                                              |

| Supplier Device Package        | 1152-FCBGA (35x35)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2vp20-5ffg1152c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Output Swing and Emphasis**

The output swing and emphasis levels are fully programmable. Each is controlled via attributes at configuration, and can be modified via the PMA attribute programming bus.

The programmable output swing control can adjust the differential peak-to-peak output level between 200 mV and 1600 mV.

With emphasis, the differential voltage swing is boosted to create a stronger rising or falling waveform. This method compensates for high frequency loss in the transmission media that would otherwise limit the magnitude of this waveform. Lossy transmission lines cause the dissipation of electrical energy. This emphasis technique extends the distance that signals can be driven down lossy line media and increases the signal-to-noise ratio at the receiver.

Emphasis can be described from two perspectives, additive to the smaller voltage ( $V_{SM}$ ) (pre-emphasis) or subtractive from the larger voltage ( $V_{LG}$ ) (de-emphasis). The resulting benefits in compensating for channel loss are identical. It is simply a relative way of specifying the effect at the transmitter.

The equations for calculating pre-emphasis as a percentage and dB are as follows:

$\begin{aligned} \text{Pre-Emphasis}_{\&} &= ((V_{LG} - V_{SM}) / V_{SM}) \times 100 \\ \text{Pre-Emphasis}_{dB} &= 20 \log(V_{LG} / V_{SM}) \end{aligned}$

The equations for calculating de-emphasis as a percentage and dB are as follows:

$\label{eq:De-Emphasis} \begin{array}{l} \mbox{De-Emphasis}_{\&} = (V_{LG} - V_{SM}) \ / \ V_{LG}) \ \mbox{x 100} \\ \mbox{De-Emphasis}_{B} = 20 \ \log{(V_{SM}/V_{LG})} \end{array}$

The pre-emphasis amount can be programmed in discrete steps between 0% and 500%. The de-emphasis amount can be programmed in discrete steps between 0% and 83%.

# Serializer

The serializer multiplies the reference frequency provided on REFCLK by 10, 16, 20, 32, or 40, depending on the operation mode. The multiplication of the clock is achieved by using an embedded PLL.

Data is converted from parallel to serial format and transmitted on the TXP and TXN differential outputs. The electrical connection of TXP and TXN can be interchanged through configuration. This option can be controlled by an input (TXPOLARITY) at the FPGA transmitter interface.

# Deserializer

Synchronous serial data reception is facilitated by a clock and data recovery (CDR) circuit. This circuit uses a fully monolithic Phase Lock Loop (PLL), which does not require any external components. The CDR circuit extracts both phase and frequency from the incoming data stream.

The derived clock, RXRECCLK, is generated and locked to as long as it remains within the specified component range.

This clock is presented to the FPGA fabric at 1/10, 1/16, 1/20, 1/32, or 1/40 the incoming data rate depending on the operating mode.

A sufficient number of transitions must be present in the data stream for CDR to work properly. The CDR circuit is guaranteed to work with 8B/10B and 64B/66B encoding. Further, CDR requires approximately 5,000 transitions upon power-up to guarantee locking to the incoming data rate. Once lock is achieved, up to 75 missing transitions can be tolerated before lock to the incoming data stream is lost.

Another feature of CDR is its ability to accept an external precision reference clock, REFCLK, which either acts to clock incoming data or to assist in synchronizing the derived RXRECCLK.

For further clarity, the TXUSRCLK is used to clock data from the FPGA fabric to the TX FIFO. The FIFO depth accounts for the slight phase difference between these two clocks. If the clocks are locked in frequency, then the FIFO acts much like a pass-through buffer.

The receiver can be configured to reverse the RXP and RXN inputs. This can be useful in the event that printed circuit board traces have been reversed.

# **Receiver Lock Control**

The CDR circuits will lock to the reference clock automatically if the data is not present. For proper operation, the frequency of the reference clock must be within  $\pm 100$  ppm of the nominal frequency.

During normal operation, the receiver PLL automatically locks to incoming data (when present) or to the local reference clock (when data is not present). This is the default configuration for all primitives. This function can be overridden via the PMARXLOCKSEL port

When receive PLL lock is forced to the local reference, phase information from the incoming data stream is ignored. Data continues to be sampled, but synchronous to the local reference rather than relative to edges in the data stream.

# **Receive Equalization**

In addition to transmit emphasis, the RocketIO X MGT provides a programmable active receive equalization feature to further compensate the effects of channel attenuation at high frequencies.

By adjusting RXFER, the right amount of equalization can be added to reverse the signal degradation caused by a printed circuit board, a backplane, or a line/switch card. RXFER can be set through software configuration or the PMA Attribute Bus.

# **Receiver Termination**

On-chip termination is provided at the receiver, eliminating the need for external termination. The receiver termination supply ( $V_{TRX}$ ) is the center tap of differential termination to

cation is given at the receiver interface. The realignment indicator is a distinct output.

The transceiver continuously monitors the data for the presence of the 10-bit character(s). Upon each occurrence of a 10-bit character, the data is checked for word alignment. If comma detect is disabled, the data is not aligned to any particular pattern. The programmable option allows a user to align data on comma+, comma-, both, or a unique user-defined and programmed sequence.

Comma detection has been expanded beyond 10-bit symbol detection and alignment to include 8-bit symbol detection and alignment for 16-, 20-, 32-, and 40-bit paths. The ability to detect symbols, and then either align to 1-word, 2-word, or 4-word boundaries is included. The RXSLIDE input allows the user to "slide" or "slip" the alignment by one bit in each 16-, 20-, 32- and 40-bit mode at any time for SONET applications. Comma detection can be bypassed when needed.

#### **Clock Correction**

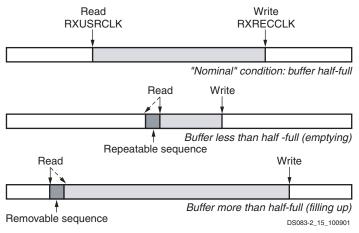

RXRECCLK (the recovered clock) reflects the data rate of the incoming data. RXUSRCLK defines the rate at which the FPGA fabric consumes the data. Ideally, these rates are identical. However, since the clocks typically have different sources, one of the clocks will be faster than the other. The receiver buffer accommodates this difference between the clock rates. See Figure 6.

Figure 6: Clock Correction in Receiver

Nominally, the buffer is always half full. This is shown in the top buffer, Figure 6, where the shaded area represents buffered data not yet read. Received data is inserted via the write pointer under control of RXRECCLK. The FPGA fabric reads data via the read pointer under control of RXUS-RCLK. The half full/half empty condition of the buffer gives a cushion for the differing clock rates. This operation continues indefinitely, regardless of whether or not "meaningful" data is being received. When there is no meaningful data to be received, the incoming data will consist of IDLE characters or other padding.

If RXUSRCLK is faster than RXRECCLK, the buffer becomes more empty over time. The clock correction logic corrects for this by decrementing the read pointer to reread a repeatable byte sequence. This is shown in the middle buffer, Figure 6, where the solid read pointer decrements to the value represented by the dashed pointer. By decrementing the read pointer instead of incrementing it in the usual fashion, the buffer is partially refilled. The transceiver design will repeat a single repeatable byte sequence when necessary to refill a buffer. If the byte sequence length is greater than one, and if attribute CLK\_COR\_REPEAT\_WAIT is 0, then the transceiver may repeat the same sequence multiple times until the buffer is refilled to the desired extent.

Similarly, if RXUSRCLK is slower than RXRECCLK, the buffer will fill up over time. The clock correction logic corrects for this by incrementing the read pointer to skip over a removable byte sequence that need not appear in the final FPGA fabric byte stream. This is shown in the bottom buffer, Figure 6, where the solid read pointer increments to the value represented by the dashed pointer. This accelerates the emptying of the buffer, preventing its overflow. The transceiver design will skip a single byte sequence when necessary to partially empty a buffer. If attribute CLK\_COR\_REPEAT\_WAIT is 0, the transceiver may also skip two consecutive removable byte sequences in one step to further empty the buffer when necessary.

These operations require the clock correction logic to recognize a byte sequence that can be freely repeated or omitted in the incoming data stream. This sequence is generally an IDLE sequence, or other sequence comprised of special values that occur in the gaps separating packets of meaningful data. These gaps are required to occur sufficiently often to facilitate the timely execution of clock correction.

#### **Channel Bonding**

Some gigabit I/O standards such as Infiniband specify the use of multiple transceivers in parallel for even higher data rates. Words of data are split into bytes, with each byte sent over a separate channel (transceiver). See Figure 7.

The top half of the figure shows the transmission of words split across four transceivers (channels or lanes). PPPP, QQQQ, RRRR, SSSS, and TTTT represent words sent over the four channels.

The bottom-left portion of Figure 7 shows the initial situation in the FPGA's receivers at the other end of the four channels. Due to variations in transmission delay—especially if the channels are routed through repeaters—the FPGA fabric might not correctly assemble the bytes into complete words. The bottom-left illustration shows the incorrect assembly of data words PQPP, QRQQ, RSRR, and so forth. To support correction of this misalignment, the data stream includes special byte sequences that define corresponding points in the several channels. In the bottom half of Figure 7, the shaded "P" bytes represent these special characters. Each receiver recognizes the "P" channel bondCRC may adjust certain trailing bytes to generate the required running disparity at the end of the packet.

On the receiver side, the CRC logic verifies the received CRC value, supporting the same standards as above.

The CRC logic also supports a user mode, with a simple data packet stucture beginning and ending with user-defined SOP and EOP characters.

#### Loopback

In order to facilitate testing without having the need to either apply patterns or measure data at GHz rates, two programmable loop-back features are available.

One option, serial loopback, places the gigabit transceiver into a state where transmit data is directly fed back to the receiver. An important point to note is that the feedback path is at the output pads of the transmitter. This tests the entirety of the transmitter and receiver.

The second option, parallel loopback, checks the digital circuitry. When parallel loopback is enabled, the serial loopback path is disabled. However, the transmitter outputs remain active, and data can be transmitted. If TXINHIBIT is asserted, TXP is forced to 0 until TXINHIBIT is de-asserted.

#### Reset

The receiver and transmitter have their own synchronous reset inputs. The transmitter reset recenters the transmission FIFO, and resets all transmitter registers and the 8B/10B decoder. The receiver reset recenters the receiver elastic buffer, and resets all receiver registers and the 8B/10B encoder. Neither reset has any effect on the PLLs.

#### Power

All RocketIO transceivers in the FPGA, whether instantiated in the design or not, must be connected to power and ground. Unused transceivers can be powered by any 2.5V source, and passive filtering is not required.

#### Power Down

The Power Down module is controlled by the transceiver's POWERDOWN input pin. The Power Down pin on the FPGA package has no effect on the transceiver.

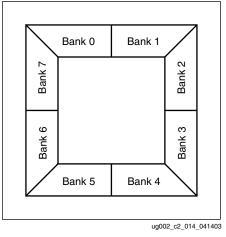

Figure 24: I/O Banks: Wire-Bond Packages (FG) Top View

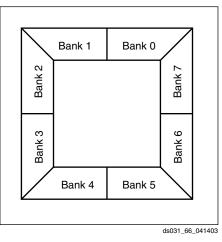

Figure 25: I/O Banks: Flip-Chip Packages (FF) Top View

Some input standards require a user-supplied threshold voltage (V<sub>REF</sub>), and certain user-I/O pins are automatically configured as V<sub>REF</sub> inputs. Approximately one in six of the I/O pins in the bank assume this role.

$V_{REF}$  pins within a bank are interconnected internally, thus only one  $V_{REF}$  voltage can be used within each bank. However, for correct operation, all  $V_{REF}$  pins in the bank must be connected to the external reference voltage source.

The V<sub>CCO</sub> and the V<sub>REF</sub> pins for each bank appear in the device pinout tables. Within a given package, the number of V<sub>REF</sub> and V<sub>CCO</sub> pins can vary depending on the size of device. In larger devices, more I/O pins convert to V<sub>REF</sub> pins. Since these are always a superset of the V<sub>REF</sub> pins used for smaller devices, it is possible to design a PCB that permits migration to a larger device if necessary.

All V<sub>REF</sub> pins for the largest device anticipated must be connected to the V<sub>REF</sub> voltage and not used for I/O. In smaller devices, some V<sub>CCO</sub> pins used in larger devices do not con-

nect within the package. These unconnected pins can be left unconnected externally, or, if necessary, they can be connected to  $V_{CCO}$  to permit migration to a larger device.

# Rules for Combining I/O Standards in the Same Bank

The following rules must be obeyed to combine different input, output, and bi-directional standards in the same bank:

1. Combining output standards only. Output standards with the same output  $V_{CCO}$  requirement can be combined in the same bank.

Compatible example:

SSTL2\_I and LVDS\_25 outputs

- Incompatible example: SSTL2\_I (output  $V_{CCO} = 2.5V$ ) and LVCMOS33 (output  $V_{CCO} = 3.3V$ ) outputs

- 2. Combining input standards only. Input standards with the same input  $V_{\rm CCO}$  and input  $V_{\rm REF}$  requirements can be combined in the same bank.

Compatible example: LVCMOS15 and HSTL\_IV inputs Incompatible example:

LVCMOS15 (input  $V_{CCO} = 1.5V$ ) and LVCMOS18 (input  $V_{CCO} = 1.8V$ ) inputs

Incompatible example: HSTL\_I\_DCI\_18 (V<sub>REF</sub> = 0.9V) and

HSTL\_IV\_DCI\_18 (V<sub>REF</sub> = 1.1V) inputs

3. Combining input standards and output standards. Input standards and output standards with the same input  $V_{CCO}$  and output  $V_{CCO}$  requirement can be combined in the same bank.

Compatible example:

LVDS\_25 output and HSTL\_I input

Incompatible example: LVDS\_25 output (output  $V_{CCO} = 2.5V$ ) and HSTL\_I\_DCI\_18 input (input  $V_{CCO} = 1.8V$ )

- 4. **Combining bi-directional standards with input or output standards.** When combining bi-directional I/O with other standards, make sure the bi-directional standard can meet rules 1 through 3 above.

- 5. Additional rules for combining DCI I/O standards.

- a. No more than one Single Termination type (input or output) is allowed in the same bank. *Incompatible example:*

HSTL\_IV\_DCI input and HSTL\_III\_DCI input

No more than one Split Termination type (input or output) is allowed in the same bank.

Incompatible example:

HSTL\_I\_DCI input and HSTL\_II\_DCI input

The implementation tools will enforce the above design rules.

Table 12, page 30, summarizes all standards and voltage supplies.

### Table 12: Summary of Voltage Supply Requirements for All Input and Output Standards

#### Table 12: Summary of Voltage Supply Requirements for All Input and Output Standards (Continued)

|                         | vc     | v <sub>cco</sub> |       | Terminat | ion Type |

|-------------------------|--------|------------------|-------|----------|----------|

| I/O Standard            | Output | Input            | Input | Output   | Input    |

| LVTTL <sup>(1)</sup>    |        |                  | N/R   | N/R      | N/R      |

| LVCMOS33 <sup>(1)</sup> | -      |                  | N/R   | N/R      | N/R      |

| LVDCI_33 <sup>(1)</sup> | 3.3    | 3.3              | N/R   | Series   | N/R      |

| PCIX <sup>(2)</sup>     | 3.3    | 3.3              | N/R   | N/R      | N/R      |

| PCI33_3 <sup>(2)</sup>  | -      |                  | N/R   | N/R      | N/R      |

| PCI66_3 <sup>(2)</sup>  | -      |                  | N/R   | N/R      | N/R      |

| LVDS_25                 |        |                  | N/R   | N/R      | N/R      |

| LVDSEXT_25              |        |                  | N/R   | N/R      | N/R      |

| LDT_25                  | 1      |                  | N/R   | N/R      | N/R      |

| ULVDS_25                | -      | Note (3)         | N/R   | N/R      | N/R      |

| BLVDS_25                | -      | Note (3)         | N/R   | N/R      | N/R      |

| LVPECL_25               | -      |                  | N/R   | N/R      | N/R      |

| SSTL2_I                 | -      |                  | 1.25  | N/R      | N/R      |

| SSTL2_II                | -      |                  | 1.25  | N/R      | N/R      |

| LVCMOS25                | -      |                  | N/R   | N/R      | N/R      |

| LVDCI_25                | 2.5    |                  | N/R   | Series   | N/R      |

| LVDCI_DV2_25            | -      |                  | N/R   | Series   | N/R      |

| LVDS_25_DCI             |        |                  | N/R   | N/R      | Split    |

| LVDSEXT_25_DCI          | 1      |                  | N/R   | N/R      | Split    |

| SSTL2_I_DCI             | 1      | 2.5              | 1.25  | N/R      | Split    |

| SSTL2_II_DCI            |        |                  | 1.25  | Split    | Split    |

| LVDS_25_DT              | 1      |                  | N/R   | N/R      | N/R      |

| LVDSEXT_25_DT           | 1      |                  | N/R   | N/R      | N/R      |

| LDT_25_DT               |        |                  | N/R   | N/R      | N/R      |

| ULVDS_25_DT             | 1      |                  | N/R   | N/R      | N/R      |

|                 | V <sub>cco</sub> |           | $V_{REF}$ | Termination Ty |        |

|-----------------|------------------|-----------|-----------|----------------|--------|

| I/O Standard    | Output           | Input     | Input     | Output         | Input  |

| HSTL_III_18     |                  |           | 1.1       | N/R            | N/R    |

| HSTL_IV_18      | _                |           | 1.1       | N/R            | N/R    |

| HSTL_I_18       | _                | Nista (O) | 0.9       | N/R            | N/R    |

| HSTL_II_18      |                  | Note (3)  | 0.9       | N/R            | N/R    |

| SSTL18_I        |                  |           | 0.9       | N/R            | N/R    |

| SSTL18_II       |                  |           | 0.9       | N/R            | N/R    |

| LVCMOS18        |                  |           | N/R       | N/R            | N/R    |

| LVDCI_18        | 1.8              |           | N/R       | Series         | N/R    |

| LVDCI_DV2_18    |                  |           | N/R       | Series         | N/R    |

| HSTL_III_DCI_18 |                  |           | 1.1       | N/R            | Single |

| HSTL_IV_DCI_18  |                  | 1.8       | 1.1       | Single         | Single |

| HSTL_I_DCI_18   |                  |           | 0.9       | N/R            | Split  |

| HSTL_II_DCI_18  |                  |           | 0.9       | Split          | Split  |

| SSTL18_I_DCI    |                  |           | 0.9       | N/R            | Split  |

| SSTL18_II_DCI   |                  |           | 0.9       | Split          | Split  |

| HSTL_III        |                  |           | 0.9       | N/R            | N/R    |

| HSTL_IV         |                  | Note (2)  | 0.9       | N/R            | N/R    |

| HSTL_I          |                  | Note (3)  | 0.75      | N/R            | N/R    |

| HSTL_II         |                  |           | 0.75      | N/R            | N/R    |

| LVCMOS15        |                  |           | N/R       | N/R            | N/R    |

| LVDCI_15        | - 1.5            |           | N/R       | Series         | N/R    |

| LVDCI_DV2_15    | 1.5              |           | N/R       | Series         | N/R    |

| GTLP_DCI        |                  | 1.5       | 1         | Single         | Single |

| HSTL_III_DCI    | 1                | 1.5       | 0.9       | N/R            | Single |

| HSTL_IV_DCI     | 1                |           | 0.9       | Single         | Single |

| HSTL_I_DCI      | 1                |           | 0.75      | N/R            | Split  |

| HSTL_II_DCI     | 1                |           |           | Split          | Split  |

| GTL_DCI         | 1.2              | 1.2       | 0.8       | Single         | Single |

| GTLP            | N/R              | Note (3)  | 1         | N/R            | N/R    |

| GTL             | חעיו             | 14018 (3) | 0.8       | N/R            | N/R    |

Notes:

See application note XAPP659 for more detailed information. See application note XAPP653 for more detailed information. 1.

2.

Pin voltage must not exceed V<sub>CCO</sub>. 3. 4.

N/R = no requirement.

#### Table 34: RocketIO TXUSRCLK2 Switching Characteristics

|                                                 |                                                   | S          | Speed Grade |            |         |

|-------------------------------------------------|---------------------------------------------------|------------|-------------|------------|---------|

| Description                                     | Symbol                                            | -7         | -6          | -5         | Units   |

| Setup and Hold Relative to Clock<br>(TXUSRCLK2) |                                                   |            |             |            |         |

| CONFIGENABLE control input                      | T <sub>GCCK</sub> _CFGEN/T <sub>GCKC</sub> _CFGEN | 0.35/ 0.10 | 0.35/ 0.10  | 0.39/ 0.11 | ns, min |

| TXBYPASS8B10B control inputs                    | T <sub>GCCK</sub> TBYP/T <sub>GCKC</sub> TBYP     | 0.02/ 0.00 | 0.02/ 0.00  | 0.02/ 0.00 | ns, min |

| TXFORCECRCERR control input                     | T <sub>GCCK</sub> _TCRCE/T <sub>GCKC</sub> _TCRCE | 0.39/ 0.12 | 0.44/ 0.14  | 0.49/ 0.15 | ns, min |

| TXPOLARITY control input                        | T <sub>GCCK</sub> _TPOL/T <sub>GCKC</sub> _TPOL   | 0.02/ 0.00 | 0.02/ 0.00  | 0.02/0.00  | ns, min |

| TXINHIBIT control inputs                        | T <sub>GCCK</sub> _TINH/T <sub>GCKC</sub> _TINH   | 0.02/ 0.00 | 0.02/ 0.00  | 0.02/0.00  | ns, min |

| LOOPBACK control inputs                         | T <sub>GCCK</sub> _LBK/T <sub>GCKC</sub> _LBK     | 0.02/ 0.00 | 0.02/0.00   | 0.02/ 0.00 | ns, min |

| TXRESET control input                           | T <sub>GCCK</sub> TRST/T <sub>GCKC</sub> TRST     | 0.02/ 0.10 | 0.02/ 0.10  | 0.02/0.11  | ns, min |

| TXCHARISK control inputs                        | T <sub>GCCK</sub> _TKCH/T <sub>GCKC</sub> _TKCH   | 0.02/ 0.00 | 0.02/ 0.00  | 0.02/0.00  | ns, min |

| TXCHARDISPMODE control inputs                   | T <sub>GCCK</sub> _TCDM/T <sub>GCKC</sub> _TCDM   | 0.02/ 0.00 | 0.02/ 0.00  | 0.02/ 0.00 | ns, min |

| TXCHARDISPVAL control inputs                    | T <sub>GCCK</sub> _TCDV/T <sub>GCKC</sub> _TCDV   | 0.02/ 0.00 | 0.02/ 0.00  | 0.02/0.00  | ns, min |

| CONFIGIN data input                             | T <sub>GDCK</sub> _CFGIN/T <sub>GCKD</sub> _CFGIN | 0.35/ 0.10 | 0.35/ 0.10  | 0.39/ 0.11 | ns, mir |

| TXDATA data inputs                              | T <sub>GDCK</sub> _TDAT/T <sub>GCKD</sub> _TDAT   | 0.02/ 0.00 | 0.02/ 0.00  | 0.02/0.00  | ns, min |

| Clock to Out                                    |                                                   |            |             |            |         |

| TXBUFERR status output                          | T <sub>GCKST</sub> _TBERR                         | 0.54       | 0.54        | 0.60       | ns, max |

| TXKERR status outputs                           | T <sub>GCKST</sub> _TKERR                         | 0.41       | 0.41        | 0.46       | ns, max |

| TXRUNDISP status outputs                        | T <sub>GCKST</sub> _TRDIS                         | 0.41       | 0.41        | 0.46       | ns, max |

| CONFIGOUT data output                           | T <sub>GCKDO</sub> _CFGOUT                        | 0.25       | 0.25        | 0.28       | ns, max |

| Clock                                           |                                                   |            |             |            |         |

| TXUSRCLK2 minimum pulse width, High             | T <sub>GPWH</sub> TX2                             | 1.42       | 1.42        | 2.25       | ns, min |

| TXUSRCLK2 minimum pulse width, Low              | T <sub>GPWL</sub> TX2                             | 1.42       | 1.42        | 2.25       | ns, min |

## Table 36: IOB Input Switching Characteristics Standard Adjustments (Continued)

|                                                              | IOSTANDARD      | Timing                        | Speed Grade |      |      |       |

|--------------------------------------------------------------|-----------------|-------------------------------|-------------|------|------|-------|

| Description                                                  | Attribute       | Parameter                     | -7          | -6   | -5   | Units |

| HSLVDCI, 1.8V                                                | HSLVDCI_18      | T <sub>IHSLVDCI_18</sub>      | 0.59        | 0.68 | 0.75 | ns    |

| HSLVDCI, 2.5V                                                | HSLVDCI_25      | T <sub>IHSLVDCI_25</sub>      | 0.59        | 0.68 | 0.75 | ns    |

| HSLVDCI, 3.3V                                                | HSLVDCI_33      | T <sub>IHSLVDCI_33</sub>      | 0.59        | 0.68 | 0.75 | ns    |

| GTL (Gunning Transceiver Logic) with DCI                     | GTL_DCI         | T <sub>IGTL_DCI</sub>         | 0.49        | 0.57 | 0.62 | ns    |

| GTL Plus with DCI                                            | GTLP_DCI        | T <sub>IGTLP_DCI</sub>        | 0.27        | 0.31 | 0.35 | ns    |

| HSTL (High-Speed Transceiver Logic), Class I, with DCI       | HSTL_I_DCI      | T <sub>IHSTL_I_DCI</sub>      | 0.27        | 0.31 | 0.35 | ns    |

| HSTL, Class II, with DCI                                     | HSTL_II_DCI     | T <sub>IHSTL_II_DCI</sub>     | 0.27        | 0.31 | 0.35 | ns    |

| HSTL, Class III, with DCI                                    | HSTL_III_DCI    | T <sub>IHSTL_III_DCI</sub>    | 0.27        | 0.31 | 0.35 | ns    |

| HSTL, Class IV, with DCI                                     | HSTL_IV_DCI     | T <sub>IHSTL_IV_DCI</sub>     | 0.27        | 0.31 | 0.35 | ns    |

| HSTL, Class I, 1.8V, with DCI                                | HSTL_I_DCI_18   | T <sub>IHSTL_I_DCI_18</sub>   | 0.27        | 0.31 | 0.35 | ns    |

| HSTL, Class II, 1.8V, with DCI                               | HSTL_II_DCI_18  | T <sub>IHSTL_II_DCI_18</sub>  | 0.27        | 0.31 | 0.35 | ns    |

| HSTL, Class III, 1.8V, with DCI                              | HSTL_III_DCI_18 | T <sub>IHSTL_III_DCI_18</sub> | 0.27        | 0.31 | 0.35 | ns    |

| HSTL, Class IV, 1.8V, with DCI                               | HSTL_IV_DCI_18  | T <sub>IHSTL_IV_DCI_18</sub>  | 0.27        | 0.31 | 0.35 | ns    |

| SSTL (Stub Series Terminated Logic), Class I, 1.8V, with DCI | SSTL18_I_DCI    | T <sub>ISSTL18_I_DCI</sub>    | 0.62        | 0.72 | 0.79 | ns    |

| SSTL, Class II, 1.8V, with DCI                               | SSTL18_II_DCI   | T <sub>ISSTL18_II_DCI</sub>   | 0.64        | 0.73 | 0.81 | ns    |

| SSTL, Class I, 2.5V, with DCI                                | SSTL2_I_DCI     | T <sub>ISSTL2_I_DCI</sub>     | 0.17        | 0.20 | 0.22 | ns    |

| SSTL, Class II, 2.5V, with DCI                               | SSTL2_II_DCI    | T <sub>ISSTL2_II_DCI</sub>    | 0.17        | 0.20 | 0.22 | ns    |

| LVDS, 2.5V, with DCI                                         | LVDS_25_DCI     | T <sub>ILVDS_25_DCI</sub>     | 0.31        | 0.36 | 0.40 | ns    |

| LVDSEXT, 2.5V, with DCI                                      | LVDSEXT_25_DCI  | T <sub>ILVDSEXT_25_DCI</sub>  | 0.33        | 0.37 | 0.41 | ns    |

| LVDS, 2.5V, with Differential Termination (DT)               | LVDS_25_DT      | T <sub>ILVDS_25_DT</sub>      | 0.31        | 0.36 | 0.40 | ns    |

| LVDSEXT, 2.5V, with DT                                       | LVDSEXT_25_DT   | T <sub>ILVDSEXT_25_DT</sub>   | 0.33        | 0.37 | 0.41 | ns    |

| ULVDS, 2.5V, with DT                                         | ULVDS_25_DT     | T <sub>IULVDS_25_DT</sub>     | 0.31        | 0.36 | 0.40 | ns    |

| LDT, 2.5V, with DT                                           | LDT_25_DT       | T <sub>ILDT_25_DT</sub>       | 0.31        | 0.36 | 0.40 | ns    |

www.xilinx.com

# **Virtex-II Pro Pin Definitions**

This section describes the pinouts for Virtex-II Pro devices in the following packages:

- FG256/FGG256, FG456/FGG456, and FG676/FGG676: wire-bond fine-pitch BGA of 1.00 mm pitch

- FF672, FF896, FF1148, FF1152, FF1517, FF1696, and FF1704: flip-chip fine-pitch BGA of 1.00 mm pitch

All of the devices supported in a particular package are pinout-compatible and are listed in the same table (one table

# **Pin Definitions**

Table 4 provides a description of each pin type listed in Virtex-II Pro pinout tables.

Table 4: Virtex-II Pro Pin Definitions

per package). Pins that are not available for smaller devices are listed in right-hand columns.

Each device is split into eight I/O banks to allow for flexibility in the choice of I/O standards. Global pins, including JTAG, configuration, and power/ground pins, are listed at the end of each table. Table 4 provides definitions for all pin types.

All Virtex-II Pro pinout tables are available on the distribution CD-ROM, or on the web (at http://www.xilinx.com).

| Pin Name                                 | Direction                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| User I/O Pins:                           |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| IO_LXXY_#                                | Input/Output/<br>Bidirectional                                                                         | <ul> <li>All user I/O pins are capable of differential signalling and can implement LVDS, ULVDS, BLVDS, LVPECL, or LDT pairs. Each user I/O is labeled "IO_LXXY_#", where:</li> <li>IO indicates a user I/O pin.</li> <li>LXXY indicates a differential pair, with XX a unique pair in the bank and Y = P/N for the positive and negative sides of the differential pair.</li> <li># indicates the bank number (0 through 7)</li> </ul> |  |  |  |

| <b>Dual-Function Pins:</b>               |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| IO_LXXY_#/ZZZ                            | The <i>dual-function pins</i> are labelled "IO_LXXY_#/ZZZ", where "ZZZ" can be one of the following pi |                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                          |                                                                                                        | · VRP, VRN, or VREF<br>GCLKX(S/P), BUSY/DOUT, INIT_B, D0/DIN – D7, RDWR_B, or CS_B                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                          | These dual functions are defined in the following section:                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| "ZZZ" (Dual Functi                       | on) Definitions                                                                                        | S:                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| D0/DIN, D1, D2,<br>D3, D4, D5, D6,<br>D7 | Input/Output                                                                                           | <ul> <li>In SelectMAP mode, D0 through D7 are configuration data pins. These pins become user I/Os after configuration, unless the SelectMAP port is retained.</li> <li>In bit-serial modes, DIN (D0) is the single-data input. This pin becomes a user I/O after configuration.</li> </ul>                                                                                                                                             |  |  |  |

| CS_B                                     | Input                                                                                                  | In SelectMAP mode, this is the active-low Chip Select signal. The pin becomes a user I/O after configuration, unless the SelectMAP port is retained.                                                                                                                                                                                                                                                                                    |  |  |  |

| RDWR_B                                   | Input                                                                                                  | In SelectMAP mode, this is the active-low Write Enable signal. The pin becomes a user I/O after configuration, unless the SelectMAP port is retained.                                                                                                                                                                                                                                                                                   |  |  |  |

| BUSY/DOUT                                | Output                                                                                                 | <ul> <li>In SelectMAP mode, BUSY controls the rate at which configuration data is loaded.<br/>The pin becomes a user I/O after configuration, unless the SelectMAP port is retained.</li> <li>In bit-serial modes, DOUT provides preamble and configuration data to downstream devices in a daisy-chain. The pin becomes a user I/O after configuration.</li> </ul>                                                                     |  |  |  |

| INIT_B                                   | Bidirectional<br>(open-drain)                                                                          | When Low, this pin indicates that the configuration memory is being cleared. When held Low, the start of configuration is delayed. During configuration, a Low on this output indicates that a configuration data error has occurred. The pin becomes a user I/O after configuration.                                                                                                                                                   |  |  |  |

# Table 5: FG256/FGG256 — XC2VP2 and XC2VP4

| Bank | Pin Description  | Pin Number                            |

|------|------------------|---------------------------------------|

| 7    | IO_L85N_7        | G2                                    |

| 7    | IO_L06P_7        | G3                                    |

| 7    | IO_L06N_7        | G4                                    |

| 7    | IO_L04P_7        | F1                                    |

| 7    | IO_L04N_7/VREF_7 | F2                                    |

| 7    | IO_L03P_7        | F3                                    |

| 7    | IO_L03N_7        | F4                                    |

| 7    | IO_L02P_7        | F5                                    |

| 7    | IO_L02N_7        | E4                                    |

| 7    | IO_L01P_7/VRN_7  | E2                                    |

| 7    | IO_L01N_7/VRP_7  | E3                                    |

|      |                  | · · · · · · · · · · · · · · · · · · · |

| 0    | VCCO_0           | F8                                    |

| 0    | VCCO_0           | F7                                    |

| 0    | VCCO_0           | E8                                    |

| 1    | VCCO_1           | F9                                    |

| 1    | VCCO_1           | F10                                   |

| 1    | VCCO_1           | E9                                    |

| 2    | VCCO_2           | H12                                   |

| 2    | VCCO_2           | H11                                   |

| 2    | VCCO_2           | G11                                   |

| 3    | VCCO_3           | K11                                   |

| 3    | VCCO_3           | J12                                   |

| 3    | VCCO_3           | J11                                   |

| 4    | VCCO_4           | M9                                    |

| 4    | VCCO_4           | L9                                    |

| 4    | VCCO_4           | L10                                   |

| 5    | VCCO_5           | M8                                    |

| 5    | VCCO_5           | L8                                    |

| 5    | VCCO_5           | L7                                    |

| 6    | VCCO_6           | K6                                    |

| 6    | VCCO_6           | J6                                    |

| 6    | VCCO_6           | J5                                    |

| 7    | VCCO_7           | H6                                    |

| 7    | VCCO_7           | H5                                    |

## Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                 | Pin No Connects |        |        |        |

|------|-----------------|-----------------|--------|--------|--------|

| Bank | Pin Description | Number          | XC2VP2 | XC2VP4 | XC2VP7 |

| N/A  | VCCINT          | U16             |        |        |        |

| N/A  | VCCINT          | U18             |        |        |        |

| N/A  | VCCINT          | V10             |        |        |        |

| N/A  | VCCINT          | V17             |        |        |        |

| N/A  | VCCINT          | V18             |        |        |        |

| N/A  | VCCINT          | W19             |        |        |        |

| N/A  | VCCAUX          | B2              |        |        |        |

| N/A  | VCCAUX          | N1              |        |        |        |

| N/A  | VCCAUX          | P1              |        |        |        |

| N/A  | VCCAUX          | A13             |        |        |        |

| N/A  | VCCAUX          | A14             |        |        |        |

| N/A  | VCCAUX          | AE2             |        |        |        |

| N/A  | VCCAUX          | B25             |        |        |        |

| N/A  | VCCAUX          | N26             |        |        |        |

| N/A  | VCCAUX          | P26             |        |        |        |

| N/A  | VCCAUX          | AE25            |        |        |        |

| N/A  | VCCAUX          | AF13            |        |        |        |

| N/A  | VCCAUX          | AF14            |        |        |        |

| N/A  | GND             | C3              |        |        |        |

| N/A  | GND             | D4              |        |        |        |

| N/A  | GND             | E5              |        |        |        |

| N/A  | GND             | F6              |        |        |        |

| N/A  | GND             | G7              |        |        |        |

| N/A  | GND             | Y7              |        |        |        |

| N/A  | GND             | AA6             |        |        |        |

| N/A  | GND             | AB5             |        |        |        |

| N/A  | GND             | AC4             |        |        |        |

| N/A  | GND             | AD3             |        |        |        |

| N/A  | GND             | C24             |        |        |        |

| N/A  | GND             | D23             |        |        |        |

| N/A  | GND             | E22             |        |        |        |

| N/A  | GND             | F21             |        |        |        |

| N/A  | GND             | G20             |        |        |        |

| N/A  | GND             | K10             |        |        |        |

| N/A  | GND             | K12             |        |        |        |

| N/A  | GND             | K13             |        |        |        |

| N/A  | GND             | K14             |        |        |        |

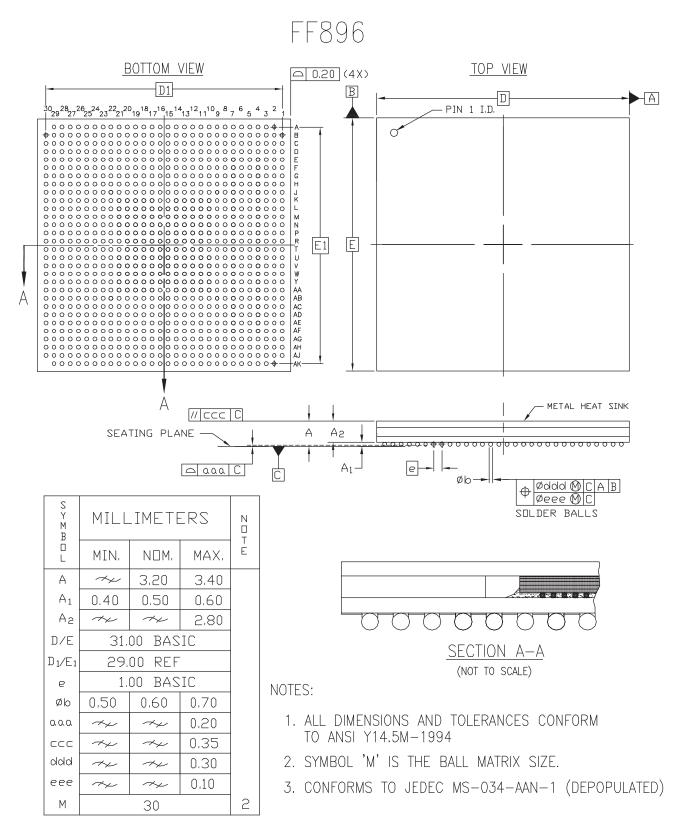

# FF896 Flip-Chip Fine-Pitch BGA Package Specifications (1.00mm pitch)

### Table 10: FF1152 — XC2VP20, XC2VP30, XC2VP40, and XC2VP50

|      |                  | Pin    |         | No Co   | nnects  |         |

|------|------------------|--------|---------|---------|---------|---------|

| Bank | Pin Description  | Number | XC2VP20 | XC2VP30 | XC2VP40 | XC2VP50 |

| 6    | IO_L53P_6        | W25    |         |         |         |         |

| 6    | IO_L53N_6        | W26    |         |         |         |         |

| 6    | IO_L54P_6        | AB33   |         |         |         |         |

| 6    | IO_L54N_6        | AA33   |         |         |         |         |

| 6    | IO_L55P_6        | Y28    |         |         |         |         |

| 6    | IO_L55N_6        | Y29    |         |         |         |         |

| 6    | IO_L56P_6        | W27    |         |         |         |         |

| 6    | IO_L56N_6        | W28    |         |         |         |         |

| 6    | IO_L57P_6        | Y31    |         |         |         |         |

| 6    | IO_L57N_6/VREF_6 | Y32    |         |         |         |         |

| 6    | IO_L58P_6        | W29    |         |         |         |         |

| 6    | IO_L58N_6        | W30    |         |         |         |         |

| 6    | IO_L59P_6        | W24    |         |         |         |         |

| 6    | IO_L59N_6        | V24    |         |         |         |         |

| 6    | IO_L60P_6        | AA34   |         |         |         |         |

| 6    | IO_L60N_6        | Y34    |         |         |         |         |

| 6    | IO_L85P_6        | W31    |         |         |         |         |

| 6    | IO_L85N_6        | W32    |         |         |         |         |

| 6    | IO_L86P_6        | V25    |         |         |         |         |

| 6    | IO_L86N_6        | V26    |         |         |         |         |

| 6    | IO_L87P_6        | Y33    |         |         |         |         |

| 6    | IO_L87N_6/VREF_6 | W33    |         |         |         |         |

| 6    | IO_L88P_6        | V29    |         |         |         |         |

| 6    | IO_L88N_6        | V30    |         |         |         |         |

| 6    | IO_L89P_6        | V27    |         |         |         |         |

| 6    | IO_L89N_6        | V28    |         |         |         |         |

| 6    | IO_L90P_6        | V31    |         |         |         |         |

| 6    | IO_L90N_6        | V32    |         |         |         |         |

|      |                  |        |         |         |         |         |

| 7    | IO_L90P_7        | U32    |         |         |         |         |

| 7    | IO_L90N_7        | U31    |         |         |         |         |

| 7    | IO_L89P_7        | U28    |         |         |         |         |

| 7    | IO_L89N_7        | U27    |         |         |         |         |

| 7    | IO_L88P_7        | V33    |         |         |         |         |

| 7    | IO_L88N_7/VREF_7 | U33    |         |         |         |         |

| 7    | IO_L87P_7        | U30    |         |         |         |         |

| 7    | IO_L87N_7        | U29    |         |         |         |         |

| 7    | IO_L86P_7        | U26    |         |         |         |         |

## Table 11: FF1148 — XC2VP40 and XC2VP50

|      |                  |            | No Connects |         |  |

|------|------------------|------------|-------------|---------|--|

| Bank | Pin Description  | Pin Number | XC2VP40     | XC2VP50 |  |

| 5    | IO_L27P_5        | AL23       |             |         |  |

| 5    | IO_L26N_5        | AD22       |             |         |  |

| 5    | IO_L26P_5        | AE22       |             |         |  |

| 5    | IO_L25N_5        | AJ23       |             |         |  |

| 5    | IO_L25P_5        | AK23       |             |         |  |

| 5    | IO_L21N_5        | AN24       |             |         |  |

| 5    | IO_L21P_5        | AP24       |             |         |  |

| 5    | IO_L20N_5        | AE23       |             |         |  |

| 5    | IO_L20P_5        | AF23       |             |         |  |

| 5    | IO_L19N_5        | AM23       |             |         |  |

| 5    | IO_L19P_5        | AM24       |             |         |  |

| 5    | IO_L09N_5/VREF_5 | AJ24       |             |         |  |

| 5    | IO_L09P_5        | AK24       |             |         |  |

| 5    | IO_L08N_5        | AG22       |             |         |  |

| 5    | IO_L08P_5        | AG23       |             |         |  |

| 5    | IO_L07N_5/VREF_5 | AH23       |             |         |  |

| 5    | IO_L07P_5        | AH24       |             |         |  |

| 5    | IO_L06N_5/VRP_5  | AN25       |             |         |  |

| 5    | IO_L06P_5/VRN_5  | AP25       |             |         |  |

| 5    | IO_L05_5/No_Pair | AH25       |             |         |  |

| 5    | IO_L03N_5/D4     | AL25       |             |         |  |

| 5    | IO_L03P_5/D5     | AM25       |             |         |  |

| 5    | IO_L02N_5/D6     | AE24       |             |         |  |

| 5    | IO_L02P_5/D7     | AF24       |             |         |  |

| 5    | IO_L01N_5/RDWR_B | AJ25       |             |         |  |

| 5    | IO_L01P_5/CS_B   | AK25       |             |         |  |

|      |                  |            |             | 1       |  |

| 6    | IO_L01P_6/VRN_6  | AP32       |             |         |  |

| 6    | IO_L01N_6/VRP_6  | AN32       |             |         |  |

| 6    | IO_L02P_6        | AP28       |             |         |  |

| 6    | IO_L02N_6        | AN28       |             |         |  |

| 6    | IO_L03P_6        | AP31       |             |         |  |

| 6    | IO_L03N_6/VREF_6 | AN31       |             |         |  |

| 6    | IO_L04P_6        | AP29       |             |         |  |

| 6    | IO_L04N_6        | AN29       |             |         |  |

| 6    | IO_L05P_6        | AN26       |             |         |  |

| 6    | IO_L05N_6        | AN27       |             |         |  |

| 6    | IO_L06P_6        | AM33       |             |         |  |

|      |                  | Pin    | No Co   | nnects  |

|------|------------------|--------|---------|---------|

| Bank | Pin Description  | Number | XC2VP50 | XC2VP70 |

| 2    | IO_L11N_2        | L9     |         |         |

| 2    | IO_L11P_2        | M10    |         |         |

| 2    | IO_L12N_2        | H4     |         |         |

| 2    | IO_L12P_2        | J5     |         |         |

| 2    | IO_L13N_2        | J1     |         |         |

| 2    | IO_L13P_2        | J2     |         |         |

| 2    | IO_L14N_2        | M8     |         |         |

| 2    | IO_L14P_2        | N9     |         |         |

| 2    | IO_L15N_2        | K6     |         |         |

| 2    | IO_L15P_2        | K7     |         |         |

| 2    | IO_L16N_2/VREF_2 | K4     |         |         |

| 2    | IO_L16P_2        | K5     |         |         |

| 2    | IO_L17N_2        | P10    |         |         |

| 2    | IO_L17P_2        | N10    |         |         |

| 2    | IO_L18N_2        | K3     |         |         |

| 2    | IO_L18P_2        | J3     |         |         |

| 2    | IO_L19N_2        | K1     |         |         |

| 2    | IO_L19P_2        | K2     |         |         |

| 2    | IO_L20N_2        | M11    |         |         |

| 2    | IO_L20P_2        | N11    |         |         |

| 2    | IO_L21N_2        | L7     |         |         |

| 2    | IO_L21P_2        | L8     |         |         |

| 2    | IO_L22N_2/VREF_2 | L5     |         |         |

| 2    | IO_L22P_2        | L6     |         |         |

| 2    | IO_L23N_2        | P8     |         |         |

| 2    | IO_L23P_2        | P9     |         |         |

| 2    | IO_L24N_2        | L3     |         |         |

| 2    | IO_L24P_2        | L4     |         |         |

| 2    | IO_L25N_2        | L1     |         |         |

| 2    | IO_L25P_2        | L2     |         |         |

| 2    | IO_L26N_2        | P11    |         |         |

| 2    | IO_L26P_2        | P12    |         |         |

| 2    | <br>IO_L27N_2    | M6     |         |         |

| 2    | <br>IO_L27P_2    | M7     |         |         |

| 2    | IO_L28N_2/VREF_2 | M2     |         |         |

| 2    | IO_L28P_2        | М3     |         |         |

| 2    | <br>IO_L29N_2    | R9     |         |         |

| 2    | IO_L29P_2        | R10    |         |         |

|      |                 | Pin    | No Connects |         |  |

|------|-----------------|--------|-------------|---------|--|

| Bank | Pin Description | Number | XC2VP50     | XC2VP70 |  |

| 2    | VCCO_2          | F8     |             |         |  |

| 2    | VCCO_2          | U7     |             |         |  |

| 2    | VCCO_2          | Y5     |             |         |  |

| 2    | VCCO_2          | N4     |             |         |  |

| 2    | VCCO_2          | J4     |             |         |  |

| 2    | VCCO_2          | E4     |             |         |  |

| 2    | VCCO_2          | U3     |             |         |  |

| 2    | VCCO_2          | E1     |             |         |  |

| 1    | VCCO_1          | N14    |             |         |  |

| 1    | VCCO_1          | K13    |             |         |  |

| 1    | VCCO_1          | F13    |             |         |  |

| 1    | VCCO_1          | P19    |             |         |  |

| 1    | VCCO_1          | P18    |             |         |  |

| 1    | VCCO_1          | P17    |             |         |  |

| 1    | VCCO_1          | K17    |             |         |  |

| 1    | VCCO_1          | F17    |             |         |  |

| 1    | VCCO_1          | P16    |             |         |  |

| 1    | VCCO_1          | N16    |             |         |  |

| 1    | VCCO_1          | P15    |             |         |  |

| 1    | VCCO_1          | N15    |             |         |  |

| 0    | VCCO_0          | K27    |             |         |  |

| 0    | VCCO_0          | F27    |             |         |  |

| 0    | VCCO_0          | N26    |             |         |  |

| 0    | VCCO_0          | P25    |             |         |  |

| 0    | VCCO_0          | N25    |             |         |  |

| 0    | VCCO_0          | P24    |             |         |  |

| 0    | VCCO_0          | N24    |             |         |  |

| 0    | VCCO_0          | P23    |             |         |  |

| 0    | VCCO_0          | K23    |             |         |  |

| 0    | VCCO_0          | F23    |             |         |  |

| 0    | VCCO_0          | P22    |             |         |  |

| 0    | VCCO_0          | P21    |             |         |  |

|      |                 |        |             |         |  |

| N/A  | CCLK            | AJ10   |             |         |  |

| N/A  | PROG_B          | D32    |             |         |  |

| N/A  | DONE            | AJ11   |             |         |  |

| N/A  | МО              | AP31   |             |         |  |

| N/A  | M1              | AJ30   |             |         |  |

| Bank | Pin Description | Pin    | No Connects |         |  |

|------|-----------------|--------|-------------|---------|--|

|      |                 | Number | XC2VP50     | XC2VP70 |  |

| N/A  | TXNPAD23        | AW36   |             |         |  |

| N/A  | VTTXPAD23       | AV36   |             |         |  |

| N/A  | AVCCAUXTX23     | AV35   |             |         |  |

|      |                 |        |             |         |  |

| N/A  | VCCINT          | AH28   |             |         |  |

| N/A  | VCCINT          | M28    |             |         |  |

| N/A  | VCCINT          | AG27   |             |         |  |

| N/A  | VCCINT          | N27    |             |         |  |

| N/A  | VCCINT          | AF26   |             |         |  |

| N/A  | VCCINT          | P26    |             |         |  |

| N/A  | VCCINT          | AE25   |             |         |  |

| N/A  | VCCINT          | AD25   |             |         |  |

| N/A  | VCCINT          | AC25   |             |         |  |

| N/A  | VCCINT          | AB25   |             |         |  |

| N/A  | VCCINT          | AA25   |             |         |  |

| N/A  | VCCINT          | Y25    |             |         |  |

| N/A  | VCCINT          | W25    |             |         |  |

| N/A  | VCCINT          | V25    |             |         |  |

| N/A  | VCCINT          | U25    |             |         |  |

| N/A  | VCCINT          | T25    |             |         |  |

| N/A  | VCCINT          | R25    |             |         |  |

| N/A  | VCCINT          | AE24   |             |         |  |

| N/A  | VCCINT          | AD24   |             |         |  |

| N/A  | VCCINT          | T24    |             |         |  |

| N/A  | VCCINT          | R24    |             |         |  |

| N/A  | VCCINT          | AE23   |             |         |  |

| N/A  | VCCINT          | R23    |             |         |  |

| N/A  | VCCINT          | AE22   |             |         |  |

| N/A  | VCCINT          | R22    |             |         |  |

| N/A  | VCCINT          | AE21   |             |         |  |

| N/A  | VCCINT          | R21    |             |         |  |

| N/A  | VCCINT          | AE20   |             |         |  |

| N/A  | VCCINT          | R20    |             |         |  |

| N/A  | VCCINT          | AE19   |             |         |  |

| N/A  | VCCINT          | R19    |             |         |  |

| N/A  | VCCINT          | AE18   |             |         |  |

| N/A  | VCCINT          | R18    |             |         |  |

| N/A  | VCCINT          | AE17   |             |         |  |

| Bank | Pin Description | Pin    | No Connects |         |  |

|------|-----------------|--------|-------------|---------|--|

|      |                 | Number | XC2VP50     | XC2VP70 |  |

| N/A  | GND             | W18    |             |         |  |

| N/A  | GND             | V18    |             |         |  |

| N/A  | GND             | U18    |             |         |  |

| N/A  | GND             | T18    |             |         |  |

| N/A  | GND             | AD17   |             |         |  |

| N/A  | GND             | AC17   |             |         |  |

| N/A  | GND             | AB17   |             |         |  |

| N/A  | GND             | AA17   |             |         |  |

| N/A  | GND             | Y17    |             |         |  |

| N/A  | GND             | W17    |             |         |  |

| N/A  | GND             | V17    |             |         |  |

| N/A  | GND             | U17    |             |         |  |

| N/A  | GND             | P20    |             |         |  |

| N/A  | GND             | L20    |             |         |  |

| N/A  | GND             | G20    |             |         |  |

| N/A  | GND             | C20    |             |         |  |

| N/A  | GND             | AD19   |             |         |  |

| N/A  | GND             | AC19   |             |         |  |

| N/A  | GND             | AB19   |             |         |  |

| N/A  | GND             | AA19   |             |         |  |

| N/A  | GND             | Y19    |             |         |  |

| N/A  | GND             | W19    |             |         |  |

| N/A  | GND             | V19    |             |         |  |

| N/A  | GND             | U19    |             |         |  |

| N/A  | GND             | T19    |             |         |  |

| N/A  | GND             | AD18   |             |         |  |

| N/A  | GND             | AC18   |             |         |  |

| N/A  | GND             | U21    |             |         |  |

| N/A  | GND             | T21    |             |         |  |

| N/A  | GND             | AU20   |             |         |  |

| N/A  | GND             | AN20   |             |         |  |

| N/A  | GND             | AJ20   |             |         |  |

| N/A  | GND             | AF20   |             |         |  |

| N/A  | GND             | AD20   |             |         |  |

| N/A  | GND             | AC20   |             |         |  |

| N/A  | GND             | AB20   |             |         |  |

| N/A  | GND             | AA20   |             |         |  |

| N/A  | GND             | Y20    |             |         |  |

### Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

| Bank | Pin Description       |                            |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

|      | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 3    | IO_L17N_3             |                            | AL9        |                      |          |

| 3    | IO_L17P_3             |                            | AL10       |                      |          |

| 3    | IO_L16N_3             |                            | AM1        |                      |          |

| 3    | IO_L16P_3             |                            | AM2        |                      |          |

| 3    | IO_L15N_3/VREF_3      |                            | AM3        |                      |          |

| 3    | IO_L15P_3             |                            | AN3        |                      |          |

| 3    | IO_L14N_3             |                            | AM8        |                      |          |

| 3    | IO_L14P_3             |                            | AM9        |                      |          |

| 3    | IO_L13N_3             |                            | AM4        |                      |          |

| 3    | IO_L13P_3             |                            | AM5        |                      |          |

| 3    | IO_L12N_3             |                            | AM6        |                      |          |

| 3    | IO_L12P_3             |                            | AM7        |                      |          |

| 3    | IO_L11N_3             |                            | AN9        |                      |          |

| 3    | IO_L11P_3             |                            | AM10       |                      |          |

| 3    | IO_L10N_3             |                            | AN1        |                      |          |

| 3    | IO_L10P_3             |                            | AN2        |                      |          |

| 3    | IO_L09N_3/VREF_3      |                            | AN5        |                      |          |

| 3    | IO_L09P_3             |                            | AN6        |                      |          |

| 3    | IO_L08N_3             |                            | AN7        |                      |          |

| 3    | IO_L08P_3             |                            | AN8        |                      |          |

| 3    | IO_L07N_3             |                            | AP1        |                      |          |

| 3    | IO_L07P_3             |                            | AP2        |                      |          |

| 3    | IO_L84N_3             |                            | AP4        |                      |          |

| 3    | IO_L84P_3             |                            | AP5        |                      |          |

| 3    | IO_L83N_3             |                            | AR7        |                      |          |

| 3    | IO_L83P_3             |                            | AP8        |                      |          |

| 3    | IO_L82N_3             |                            | AP6        |                      |          |

| 3    | IO_L82P_3             |                            | AP7        |                      |          |

| 3    | IO_L81N_3/VREF_3      |                            | AR2        |                      |          |

| 3    | IO_L81P_3             |                            | AR3        |                      |          |

| 3    | IO_L80N_3             |                            | AT5        |                      |          |

| 3    | IO_L80P_3             |                            | AR6        |                      |          |

| 3    | IO_L79N_3             |                            | AR4        |                      |          |

| 3    | IO_L79P_3             |                            | AR5        |                      |          |

| 3    | IO_L78N_3             |                            | AT1        |                      |          |

| 3    | IO_L78P_3             |                            | AT2        |                      |          |

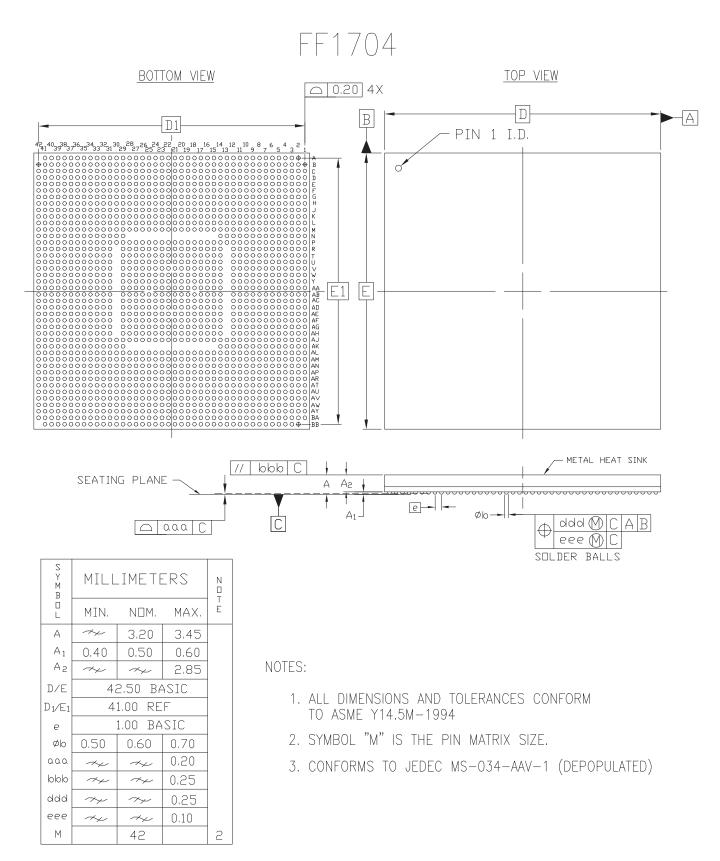

# FF1704 Flip-Chip Fine-Pitch BGA Package Specifications (1.00mm pitch)

Figure 9: FF1704 Flip-Chip Fine-Pitch BGA Package Specifications

www.xilinx.com

# *Table 14:* **FF1696 — XC2VP100**

|      |                 |            | No Connects |

|------|-----------------|------------|-------------|

| Bank | Pin Description | Pin Number | XC2VP100    |

| N/A  | GND             | AF1        |             |

| N/A  | GND             | AC1        |             |

| N/A  | GND             | Y1         |             |

| N/A  | GND             | U1         |             |

| N/A  | GND             | N1         |             |

| N/A  | GND             | J1         |             |

| N/A  | GND             | E1         |             |

Notes:

1. See Table 4 for an explanation of the signals available on this pin.