Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 2320                                                        |

| Number of Logic Elements/Cells | 20880                                                       |

| Total RAM Bits                 | 1622016                                                     |

| Number of I/O                  | 556                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 896-BBGA, FCBGA                                             |

| Supplier Device Package        | 896-FCBGA (31x31)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2vp20-6ff896c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

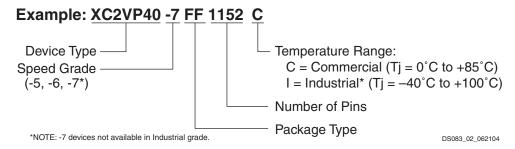

# **Virtex-II Pro Ordering Examples**

Virtex-II Pro ordering examples are shown in Figure 1 (flip-chip package) and Figure 2 (Pb-free wire-bond package).

Figure 1: Virtex-II Pro Ordering Example, Flip-Chip Package

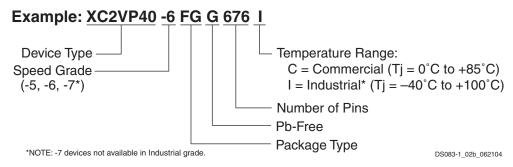

Figure 2: Virtex-II Pro Ordering Example, Pb-Free Wire-Bond Package

# **Virtex-II Pro X Ordering Example**

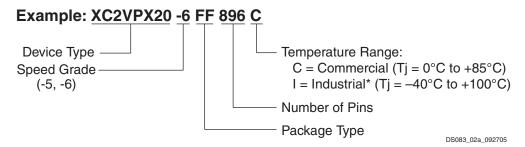

A Virtex-II Pro X ordering example is shown in Figure 3.

Figure 3: Virtex-II Pro X Ordering Example, Flip-Chip Package

# **Product Not Recommended For New Designs**

### Other RocketlO X Features and Notes

#### Loopback

In order to facilitate testing without having the need to either apply patterns or measure data at GHz rates, four programmable loop-back features are available.

The first option, serial loopback, is available in two modes: *pre-driver* and *post-driver*.

- The pre-driver mode loops back to the receiver without going through the output driver. In this mode, TXP and TXN are not driven and therefore need not be terminated.

- The post-driver mode is the same as the RocketIO loopback. In this mode, TXP and TXN are driven and must be properly terminated.

The third option, parallel loopback, checks the digital circuitry. When parallel loopback is enabled, the serial loopback path is disabled. However, the transmitter outputs remain active, and data can be transmitted. If TXINHIBIT is asserted, TXP is forced to 0 until TXINHIBIT is de-asserted.

The fourth option, repeater loopback, allows received data to be transmitted without going through the FPGA fabric.

#### Reset

The receiver and transmitter have their own synchronous reset inputs. The transmitter reset, TXRESET, recenters the transmission FIFO and resets all transmitter registers and the encoder. The receiver reset, RXRESET, recenters the

receiver elastic buffer and resets all receiver registers and the decoder. When the signals TXRESET or RXRESET are asserted High, the PCS is in reset. After TXRESET or RXRESET are deasserted, the PCS takes five clocks to come out of reset for each clock domain.

The PMA configuration vector is not affected during this reset, so the PMA speed, filter settings, and so on, all remain the same. Also, the PMA internal pipeline is not affected and continues to operate in normal fashion.

#### Power

The transceiver voltage regulator circuits must not be shared with any other supplies (including FPGA supplies  $V_{CCINT}$ ,  $V_{CCO}$ ,  $V_{CCAUX}$ , and  $V_{REF}$ ). Voltage regulators can be shared among transceiver power supplies of the same voltage, but each supply pin must still have its own separate passive filtering network.

All RocketIO transceivers in the FPGA, whether instantiated in the design or not, must be connected to power and ground. Unused transceivers can be powered by any 1.5V or 2.5V source, and passive filtering is not required.

The Power Down feature is controlled by the transceiver's POWERDOWN input pin. Any given transceiver that is not instantiated in the design is automatically set to the POWERDOWN state by the Xilinx ISE development software. The Power Down pin on the FPGA package has no effect on the MGT.

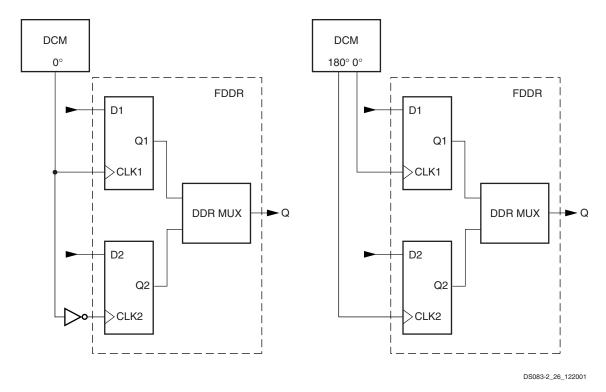

Figure 20: Double Data Rate Registers

This DDR mechanism can be used to mirror a copy of the clock on the output. This is useful for propagating a clock along the data that has an identical delay. It is also useful for multiple clock generation, where there is a unique clock driver for every clock load. Virtex-II Pro devices can produce many copies of a clock with very little skew.

Each group of two registers has a clock enable signal (ICE for the input registers, OCE for the output registers, and TCE for the 3-state registers). The clock enable signals are active High by default. If left unconnected, the clock enable for that storage element defaults to the active state.

Each IOB block has common synchronous or asynchronous set and reset (SR and REV signals). Two neighboring IOBs have a shared routing resource connecting the ICLK and OTCLK pins on pairs of IOBs. If two adjacent IOBs using DDR registers do not share the same clock signals on their clock pins (ICLK1, ICLK2, OTCLK1, and OTCLK2), one of the clock signals will be unroutable.

The IOB pairing is identical to the LVDS IOB pairs. Hence, the package pin-out table can also be used for pin assignment to avoid conflict.

SR forces the storage element into the state specified by the SRHIGH or SRLOW attribute. SRHIGH forces a logic 1. SRLOW forces a logic "0". When SR is used, a second input

(REV) forces the storage element into the opposite state. The reset condition predominates over the set condition. The initial state after configuration or global initialization state is defined by a separate INIT0 and INIT1 attribute. By default, the SRLOW attribute forces INIT0, and the SRHIGH attribute forces INIT1.

For each storage element, the SRHIGH, SRLOW, INITO, and INIT1 attributes are independent. Synchronous or asynchronous set / reset is consistent in an IOB block.

All the control signals have independent polarity. Any inverter placed on a control input is automatically absorbed.

Each register or latch, independent of all other registers or latches, can be configured as follows:

- No set or reset

- Synchronous set

- Synchronous reset

- Synchronous set and reset

- Asynchronous set (preset)

- Asynchronous reset (clear)

- · Asynchronous set and reset (preset and clear)

The synchronous reset overrides a set, and an asynchronous clear overrides a preset.

Refer to Figure 21.

Figure 36, Figure 37, and Figure 38 illustrate various example configurations.

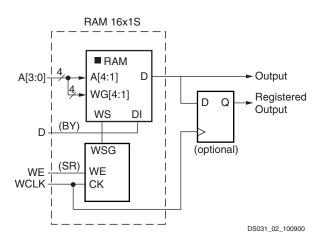

Figure 36: Distributed SelectRAM+ (RAM16x1S)

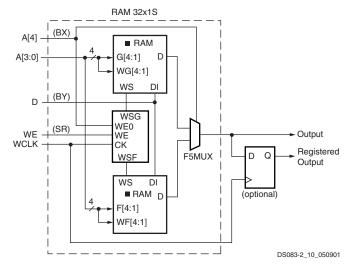

Figure 37: Single-Port Distributed SelectRAM+ (RAM32x1S)

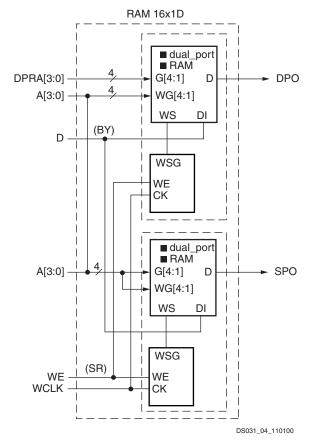

Figure 38: Dual-Port Distributed SelectRAM+ (RAM16x1D)

Similar to the RAM configuration, each function generator (LUT) can implement a 16 x 1-bit ROM. Five configurations are available: ROM16x1, ROM32x1, ROM64x1, ROM128x1, and ROM256x1. The ROM elements are cascadable to implement wider or/and deeper ROM. ROM contents are loaded at configuration. Table 17 shows the number of LUTs occupied by each configuration.

Table 17: ROM Configuration

| ROM     | Number of LUTs |

|---------|----------------|

| 16 x 1  | 1              |

| 32 x 1  | 2              |

| 64 x 1  | 4              |

| 128 x 1 | 8 (1 CLB)      |

| 256 x 1 | 16 (2 CLBs)    |

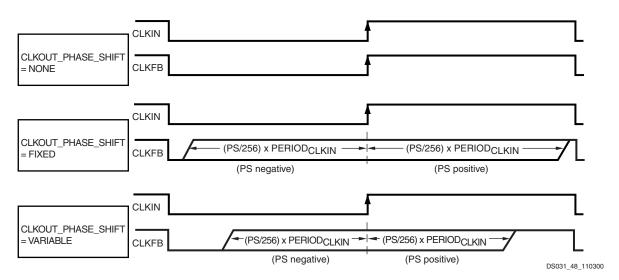

Figure 63: Fine-Phase Shifting Effects

Two separate components of the phase shift range must be understood:

- PHASE\_SHIFT attribute range

- FINE\_SHIFT\_RANGE DCM timing parameter range

The PHASE\_SHIFT attribute is the numerator in the following equation:

Phase Shift (ns) = (PHASE\_SHIFT/256) \* PERIOD<sub>CLKIN</sub>

The full range of this attribute is always -255 to +255, but its practical range varies with CLKIN frequency, as constrained by the FINE\_SHIFT\_RANGE component, which represents the total delay achievable by the phase shift delay line. Total delay is a function of the number of delay taps used in the circuit. Across process, voltage, and temperature, this absolute range is guaranteed to be as specified under **DCM Timing Parameters** in Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics.

Absolute range (fixed mode) = ± FINE\_SHIFT\_RANGE

Absolute range (variable mode) =  $\pm$  FINE\_SHIFT\_RANGE/2

The reason for the difference between fixed and variable modes is as follows. For variable mode to allow symmetric, dynamic sweeps from -255/256 to +255/256, the DCM sets the "zero phase skew" point as the middle of the delay line, thus dividing the total delay line range in half. In fixed mode,

since the PHASE\_SHIFT value never changes after configuration, the entire delay line is available for insertion into either the CLKIN or CLKFB path (to create either positive or negative skew).

Taking both of these components into consideration, the following are some usage examples:

- If PERIOD<sub>CLKIN</sub> = 2 \* FINE\_SHIFT\_RANGE, then PHASE\_SHIFT in fixed mode is limited to ± 128, and in variable mode it is limited to ± 64.

- If PERIOD<sub>CLKIN</sub> = FINE\_SHIFT\_RANGE, then PHASE\_SHIFT in fixed mode is limited to ± 255, and in variable mode it is limited to ± 128.

- If  $PERIOD_{CLKIN} \le 0.5$  \* FINE\_SHIFT\_RANGE, then PHASE\_SHIFT is limited to  $\pm 255$  in either mode.

#### Operating Modes

The frequency ranges of DCM input and output clocks depend on the operating mode specified, either low-frequency mode or high-frequency mode, according to Table 30. For actual values, see Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics. The CLK2X, CLK2X180, CLK90, and CLK270 outputs are not available in high-frequency mode.

High or low-frequency mode is selected by an attribute.

Table 30: DCM Frequency Ranges

|                 | Low-Frequency Mode |                   | Low-Frequency Mode |                   | High-Freq | uency Mode |

|-----------------|--------------------|-------------------|--------------------|-------------------|-----------|------------|

| Output Clock    | CLKIN Input        | CLK Output        | CLKIN Input        | CLK Output        |           |            |

| CLK0, CLK180    | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_1X_LF | CLKIN_FREQ_DLL_HF  | CLKOUT_FREQ_1X_HF |           |            |

| CLK90, CLK270   | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_1X_LF | NA                 | NA                |           |            |

| CLK2X, CLK2X180 | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_2X_LF | NA                 | NA                |           |            |

| CLKDV           | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_DV_LF | CLKIN_FREQ_DLL_HF  | CLKOUT_FREQ_DV_HF |           |            |

| CLKFX, CLKFX180 | CLKIN_FREQ_FX_LF   | CLKOUT_FREQ_FX_LF | CLKIN_FREQ_FX_HF   | CLKOUT_FREQ_FX_HF |           |            |

## Routing

### **DCM and MGT Locations/Organization**

Virtex-II Pro DCMs and serial transceivers (MGTs) are placed on the top and bottom of each block RAM and multiplier column in some combination, as shown in Table 31. The number of DCMs and RocketIO transceivers total twice the number of block RAM columns in the device. Refer to Figure 52, page 47 for an illustration of this in the XC2VP4 device.

Table 31: DCM and MGT Organization

| Device   | Block RAM<br>Columns | DCMs | MGTs |

|----------|----------------------|------|------|

| XC2VP2   | 4                    | 4    | 4    |

| XC2VP4   | 4                    | 4    | 4    |

| XC2VP7   | 6                    | 4    | 8    |

| XC2VP20  | 8                    | 8    | 8    |

| XC2VPX20 | 8                    | 8    | 8    |

| XC2VP30  | 8                    | 8    | 8    |

| XC2VP40  | 10                   | 8    | 12   |

| XC2VP50  | 12                   | 8    | 16   |

| XC2VP70  | 14                   | 8    | 20   |

| XC2VPX70 | 14                   | 8    | 20   |

| XC2VP100 | 16                   | 12   | 20   |

Place-and-route software takes advantage of this regular array to deliver optimum system performance and fast compile times. The segmented routing resources are essential to guarantee IP cores portability and to efficiently handle an incremental design flow that is based on modular implementations. Total design time is reduced due to fewer and shorter design iterations.

### **Hierarchical Routing Resources**

Most Virtex-II Pro signals are routed using the global routing resources, which are located in horizontal and vertical routing channels between each switch matrix.

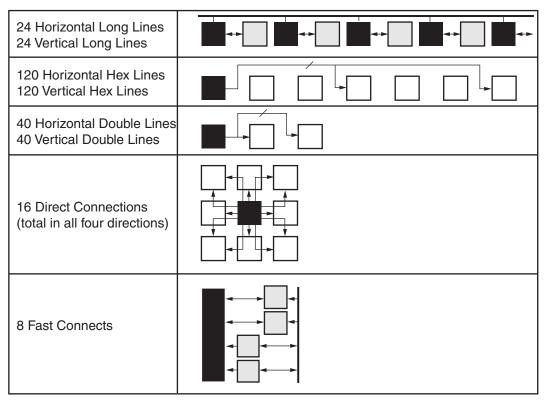

As shown in Figure 64, page 54, Virtex-II Pro has fully buffered programmable interconnections, with a number of resources counted between any two adjacent switch matrix rows or columns. Fanout has minimal impact on the performance of each net.

- The long lines are bidirectional wires that distribute signals across the device. Vertical and horizontal long lines span the full height and width of the device.

- The hex lines route signals to every third or sixth block away in all four directions. Organized in a staggered pattern, hex lines can only be driven from one end. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source).

DS031\_60\_110200

Figure 64: Hierarchical Routing Resources

Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description

### Configuration

Virtex-II Pro devices are configured by loading application specific configuration data into the internal configuration memory. Configuration is carried out using a subset of the device pins, some of which are dedicated, while others can be re-used as general purpose inputs and outputs once configuration is complete.

Depending on the system design, several configuration modes are supported, selectable via mode pins. The mode pins M2, M1, and M0 are dedicated pins. The M2, M1, and M0 mode pins should be set at a constant DC voltage level, either through pull-up or pull-down resistors, or tied directly to ground or  $V_{\text{CCAUX}}$ . The mode pins should not be toggled during and after configuration.

An additional pin, HSWAP\_EN is used in conjunction with the mode pins to select whether user I/O pins have pull-ups during configuration. By default, HSWAP\_EN is tied High (internal pull-up) which shuts off the pull-ups on the user I/O pins during configuration. When HSWAP\_EN is tied Low, user I/Os have pull-ups during configuration. Other dedicated pins are CCLK (the configuration clock pin), DONE, PROG B, and the Boundary-Scan pins: TDI, TDO, TMS, and TCK. (The TDO pin is open-drain and does not have an internal pull-up resistor.) Depending on the configuration mode chosen, CCLK can be an output generated by the FPGA, or an input accepting an externally generated clock. The configuration pins and Boundary-Scan pins are independent of the V<sub>CCO</sub>. The auxiliary power supply (V<sub>CCAUX</sub>) of 2.5V is used for these pins. All configuration pins are LVCMOS25 12mA. See Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics.

A "persist" option is available which can be used to force the configuration pins to retain their configuration function even after device configuration is complete. If the persist option is not selected then the configuration pins with the exception of CCLK, PROG\_B, and DONE can be used as user I/O in normal operation. The persist option does not apply to the Boundary-Scan related pins. The persist feature is valuable in applications which employ partial reconfiguration or reconfiguration on the fly.

### **Configuration Modes**

Virtex-II Pro supports the following five configuration modes:

- Slave-Serial Mode

- Master-Serial Mode

- Slave SelectMAP Mode

- Master SelectMAP Mode

- Boundary-Scan (JTAG, IEEE 1532) Mode

Refer to Table 32, page 57.

A detailed description of configuration modes is provided in the *Virtex-II Pro Platform FPGA User Guide*.

#### Slave-Serial Mode

In slave-serial mode, the FPGA receives configuration data in bit-serial form from a serial PROM or other serial source of configuration data. The CCLK pin on the FPGA is an input in this mode. The serial bitstream must be setup at the DIN input pin a short time before each rising edge of the externally generated CCLK.

Multiple FPGAs can be daisy-chained for configuration from a single source. After a particular FPGA has been configured, the data for the next device is routed internally to the DOUT pin. The data on the DOUT pin changes on the falling edge of CCLK.

Slave-serial mode is selected by applying [111] to the mode pins (M2, M1, M0). A weak pull-up on the mode pins makes slave serial the default mode if the pins are left unconnected.

#### Master-Serial Mode

In master-serial mode, the CCLK pin is an output pin. It is the Virtex-II Pro FPGA device that drives the configuration clock on the CCLK pin to a Xilinx Serial PROM which in turn feeds bit-serial data to the DIN input. The FPGA accepts this data on each rising CCLK edge. After the FPGA has been loaded, the data for the next device in a daisy-chain is presented on the DOUT pin after the falling CCLK edge.

The interface is identical to slave serial except that an internal oscillator is used to generate the configuration clock (CCLK). A wide range of frequencies can be selected for CCLK which always starts at a slow default frequency. Configuration bits then switch CCLK to a higher frequency for the remainder of the configuration.

### Slave SelectMAP Mode

The SelectMAP mode is the fastest configuration option. Byte-wide data is written into the Virtex-II Pro FPGA device with a BUSY flag controlling the flow of data. An external data source provides a byte stream, CCLK, an active Low Chip Select (CS\_B) signal and a Write signal (RDWR\_B). If BUSY is asserted (High) by the FPGA, the data must be held until BUSY goes Low. Data can also be read using the SelectMAP mode. If RDWR\_B is asserted, configuration data is read out of the FPGA as part of a readback operation.

After configuration, the pins of the SelectMAP port can be used as additional user I/O. Alternatively, the port can be retained to permit high-speed 8-bit readback using the persist option.

Multiple Virtex-II Pro FPGAs can be configured using the SelectMAP mode, and be made to start-up simultaneously. To configure multiple devices in this way, wire the individual CCLK, Data, RDWR\_B, and BUSY pins of all the devices in parallel. The individual devices are loaded separately by deasserting the CS\_B pin of each device in turn and writing the appropriate data.

Table 7: FG676/FGG676 — XC2VP20, XC2VP30, and XC2VP40

|      |                 |            | No Connects |          |         |  |

|------|-----------------|------------|-------------|----------|---------|--|

| Bank | Pin Description | Pin Number | XC2VP20     | XC2VP30  | XC2VP40 |  |

| 3    | VCCO_3          | AB24       |             |          |         |  |

| 4    | VCCO_4          | U14        |             |          |         |  |

| 4    | VCCO_4          | U15        |             |          |         |  |

| 4    | VCCO_4          | V16        |             |          |         |  |

| 4    | VCCO_4          | V17        |             |          |         |  |

| 4    | VCCO_4          | AC16       |             |          |         |  |

| 4    | VCCO_4          | AD19       |             |          |         |  |

| 4    | VCCO_4          | AD22       |             |          |         |  |

| 5    | VCCO_5          | U12        |             |          |         |  |

| 5    | VCCO_5          | U13        |             |          |         |  |

| 5    | VCCO_5          | V10        |             |          |         |  |

| 5    | VCCO_5          | V11        |             |          |         |  |

| 5    | VCCO_5          | AC11       |             |          |         |  |

| 5    | VCCO_5          | AD5        |             |          |         |  |

| 5    | VCCO_5          | AD8        |             |          |         |  |

| 6    | VCCO_6          | P10        |             |          |         |  |

| 6    | VCCO_6          | R10        |             |          |         |  |

| 6    | VCCO_6          | T4         |             |          |         |  |

| 6    | VCCO_6          | Т9         |             |          |         |  |

| 6    | VCCO_6          | U9         |             |          |         |  |

| 6    | VCCO_6          | W3         |             |          |         |  |

| 6    | VCCO_6          | AB3        |             |          |         |  |

| 7    | VCCO_7          | E3         |             |          |         |  |

| 7    | VCCO_7          | H3         |             |          |         |  |

| 7    | VCCO_7          | K9         |             |          |         |  |

| 7    | VCCO_7          | L4         |             |          |         |  |

| 7    | VCCO_7          | L9         |             |          |         |  |

| 7    | VCCO_7          | M10        |             |          |         |  |

| 7    | VCCO_7          | N10        |             |          |         |  |

|      |                 |            |             | <u> </u> |         |  |

| N/A  | PROG_B          | B1         |             |          |         |  |

| N/A  | HSWAP_EN        | В3         |             |          |         |  |

| N/A  | DXP             | A3         |             |          |         |  |

| N/A  | DXN             | C4         |             |          |         |  |

| N/A  | AVCCAUXTX4      | B5         |             |          |         |  |

Table 7: FG676/FGG676 — XC2VP20, XC2VP30, and XC2VP40

|      |                 |            | No Connects |         |         |  |

|------|-----------------|------------|-------------|---------|---------|--|

| Bank | Pin Description | Pin Number | XC2VP20     | XC2VP30 | XC2VP40 |  |

| N/A  | GND             | R15        |             |         |         |  |

| N/A  | GND             | R16        |             |         |         |  |

| N/A  | GND             | R24        |             |         |         |  |

| N/A  | GND             | T11        |             |         |         |  |

| N/A  | GND             | T12        |             |         |         |  |

| N/A  | GND             | T13        |             |         |         |  |

| N/A  | GND             | T14        |             |         |         |  |

| N/A  | GND             | T15        |             |         |         |  |

| N/A  | GND             | T16        |             |         |         |  |

| N/A  | GND             | U6         |             |         |         |  |

| N/A  | GND             | U21        |             |         |         |  |

| N/A  | GND             | W4         |             |         |         |  |

| N/A  | GND             | W23        |             |         |         |  |

| N/A  | GND             | AA10       |             |         |         |  |

| N/A  | GND             | AA17       |             |         |         |  |

| N/A  | GND             | AC4        |             |         |         |  |

| N/A  | GND             | AC8        |             |         |         |  |

| N/A  | GND             | AC19       |             |         |         |  |

| N/A  | GND             | AC23       |             |         |         |  |

| N/A  | GND             | AD3        |             |         |         |  |

| N/A  | GND             | AD24       |             |         |         |  |

| N/A  | GND             | AE2        |             |         |         |  |

| N/A  | GND             | AE25       |             |         |         |  |

| N/A  | GND             | AF1        |             |         |         |  |

| N/A  | GND             | AF26       |             |         |         |  |

|      |                 | II         | 1           | 1       | 1       |  |

### Notes:

1. See Table 4 for an explanation of the signals available on this pin.

Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                 | Pin    | No Connects |        |        |  |

|------|-----------------|--------|-------------|--------|--------|--|

| Bank | Pin Description | Number | XC2VP2      | XC2VP4 | XC2VP7 |  |

| 7    | VCCO_7          | L18    |             |        |        |  |

| 7    | VCCO_7          | M18    |             |        |        |  |

| 7    | VCCO_7          | N18    |             |        |        |  |

|      |                 |        |             |        |        |  |

| N/A  | CCLK            | W7     |             |        |        |  |

| N/A  | PROG_B          | D22    |             |        |        |  |

| N/A  | DONE            | AB6    |             |        |        |  |

| N/A  | MO              | AC22   |             |        |        |  |

| N/A  | M1              | W20    |             |        |        |  |

| N/A  | M2              | AB21   |             |        |        |  |

| N/A  | TCK             | G8     |             |        |        |  |

| N/A  | TDI             | H20    |             |        |        |  |

| N/A  | TDO             | H7     |             |        |        |  |

| N/A  | TMS             | F7     |             |        |        |  |

| N/A  | PWRDWN_B        | AC5    |             |        |        |  |

| N/A  | HSWAP_EN        | E21    |             |        |        |  |

| N/A  | RSVD            | D5     |             |        |        |  |

| N/A  | VBATT           | E6     |             |        |        |  |

| N/A  | DXP             | F20    |             |        |        |  |

| N/A  | DXN             | G19    |             |        |        |  |

| N/A  | AVCCAUXTX7      | B11    |             |        |        |  |

| N/A  | VTTXPAD7        | B12    |             |        |        |  |

| N/A  | TXNPAD7         | A12    |             |        |        |  |

| N/A  | TXPPAD7         | A11    |             |        |        |  |

| N/A  | GNDA7           | C11    |             |        |        |  |

| N/A  | RXPPAD7         | A10    |             |        |        |  |

| N/A  | RXNPAD7         | A9     |             |        |        |  |

| N/A  | VTRXPAD7        | B10    |             |        |        |  |

| N/A  | AVCCAUXRX7      | B9     |             |        |        |  |

| N/A  | AVCCAUXTX9      | B6     | NC          | NC     |        |  |

| N/A  | VTTXPAD9        | B7     | NC          | NC     |        |  |

| N/A  | TXNPAD9         | A7     | NC          | NC     |        |  |

| N/A  | TXPPAD9         | A6     | NC          | NC     |        |  |

| N/A  | GNDA9           | C5     | NC          | NC     |        |  |

| N/A  | RXPPAD9         | A5     | NC          | NC     |        |  |

| N/A  | RXNPAD9         | A4     | NC          | NC     |        |  |

| N/A  | VTRXPAD9        | B5     | NC          | NC     |        |  |

Table 9: FF896 — XC2VP7, XC2VP20, XC2VPX20, and XC2VP30

|      | Pin Description       | on                         |               | No Connects |                      |         |

|------|-----------------------|----------------------------|---------------|-------------|----------------------|---------|

| Bank | Virtex-II Pro devices | XC2VPX20<br>(if Different) | Pin<br>Number | XC2VP7      | XC2VP20,<br>XC2VPX20 | XC2VP30 |

| 2    | IO_L59N_2             |                            | P8            |             |                      |         |

| 2    | IO_L59P_2             |                            | P7            |             |                      |         |

| 2    | IO_L60N_2             |                            | N4            |             |                      |         |

| 2    | IO_L60P_2             |                            | N3            |             |                      |         |

| 2    | IO_L85N_2             |                            | P3            |             |                      |         |

| 2    | IO_L85P_2             |                            | P2            |             |                      |         |

| 2    | IO_L86N_2             |                            | R8            |             |                      |         |

| 2    | IO_L86P_2             |                            | R7            |             |                      |         |

| 2    | IO_L87N_2             |                            | P5            |             |                      |         |

| 2    | IO_L87P_2             |                            | P4            |             |                      |         |

| 2    | IO_L88N_2/VREF_2      |                            | R2            |             |                      |         |

| 2    | IO_L88P_2             |                            | T2            |             |                      |         |

| 2    | IO_L89N_2             |                            | R6            |             |                      |         |

| 2    | IO_L89P_2             |                            | R5            |             |                      |         |

| 2    | IO_L90N_2             |                            | R4            |             |                      |         |

| 2    | IO_L90P_2             |                            | R3            |             |                      |         |

|      |                       |                            |               |             |                      |         |

| 3    | IO_L90N_3             |                            | U1            |             |                      |         |

| 3    | IO_L90P_3             |                            | V1            |             |                      |         |

| 3    | IO_L89N_3             |                            | T5            |             |                      |         |

| 3    | IO_L89P_3             |                            | T6            |             |                      |         |

| 3    | IO_L88N_3             |                            | Т3            |             |                      |         |

| 3    | IO_L88P_3             |                            | T4            |             |                      |         |

| 3    | IO_L87N_3/VREF_3      |                            | U2            |             |                      |         |

| 3    | IO_L87P_3             |                            | U3            |             |                      |         |

| 3    | IO_L86N_3             |                            | T7            |             |                      |         |

| 3    | IO_L86P_3             |                            | T8            |             |                      |         |

| 3    | IO_L85N_3             |                            | U4            |             |                      |         |

| 3    | IO_L85P_3             |                            | U5            |             |                      |         |

| 3    | IO_L60N_3             |                            | V2            |             |                      |         |

| 3    | IO_L60P_3             |                            | W2            |             |                      |         |

| 3    | IO_L59N_3             |                            | Т9            |             |                      |         |

| 3    | IO_L59P_3             |                            | U9            |             |                      |         |

| 3    | IO_L58N_3             |                            | V3            |             |                      |         |

| 3    | IO_L58P_3             |                            | V4            |             |                      |         |

| 3    | IO_L57N_3/VREF_3      |                            | W1            |             |                      |         |

Table 10: FF1152 — XC2VP20, XC2VP30, XC2VP40, and XC2VP50

|      |                 | Pin    |         | No Co   | onnects |         |

|------|-----------------|--------|---------|---------|---------|---------|

| Bank | Pin Description | Number | XC2VP20 | XC2VP30 | XC2VP40 | XC2VP50 |

| N/A  | VTTXPAD5        | B25    | NC      | NC      | NC      |         |

| N/A  | TXNPAD5         | A25    | NC      | NC      | NC      |         |

| N/A  | TXPPAD5         | A24    | NC      | NC      | NC      |         |

| N/A  | GNDA5           | C23    | NC      | NC      | NC      |         |

| N/A  | RXPPAD5         | A23    | NC      | NC      | NC      |         |

| N/A  | RXNPAD5         | A22    | NC      | NC      | NC      |         |

| N/A  | VTRXPAD5        | B23    | NC      | NC      | NC      |         |

| N/A  | AVCCAUXRX5      | B22    | NC      | NC      | NC      |         |

| N/A  | AVCCAUXTX6      | B20    |         |         |         |         |

| N/A  | VTTXPAD6        | B21    |         |         |         |         |

| N/A  | TXNPAD6         | A21    |         |         |         |         |

| N/A  | TXPPAD6         | A20    |         |         |         |         |

| N/A  | GNDA6           | C20    |         |         |         |         |

| N/A  | RXPPAD6         | A19    |         |         |         |         |

| N/A  | RXNPAD6         | A18    |         |         |         |         |

| N/A  | VTRXPAD6        | B19    |         |         |         |         |

| N/A  | AVCCAUXRX6      | B18    |         |         |         |         |

| N/A  | AVCCAUXTX7      | B16    |         |         |         |         |

| N/A  | VTTXPAD7        | B17    |         |         |         |         |

| N/A  | TXNPAD7         | A17    |         |         |         |         |

| N/A  | TXPPAD7         | A16    |         |         |         |         |

| N/A  | GNDA7           | C15    |         |         |         |         |

| N/A  | RXPPAD7         | A15    |         |         |         |         |

| N/A  | RXNPAD7         | A14    |         |         |         |         |

| N/A  | VTRXPAD7        | B15    |         |         |         |         |

| N/A  | AVCCAUXRX7      | B14    |         |         |         |         |

| N/A  | AVCCAUXTX8      | B12    | NC      | NC      | NC      |         |

| N/A  | VTTXPAD8        | B13    | NC      | NC      | NC      |         |

| N/A  | TXNPAD8         | A13    | NC      | NC      | NC      |         |

| N/A  | TXPPAD8         | A12    | NC      | NC      | NC      |         |

| N/A  | GNDA8           | C12    | NC      | NC      | NC      |         |

| N/A  | RXPPAD8         | A11    | NC      | NC      | NC      |         |

| N/A  | RXNPAD8         | A10    | NC      | NC      | NC      |         |

| N/A  | VTRXPAD8        | B11    | NC      | NC      | NC      |         |

| N/A  | AVCCAUXRX8      | B10    | NC      | NC      | NC      |         |

| N/A  | AVCCAUXTX9      | B8     |         |         |         |         |

| N/A  | VTTXPAD9        | B9     |         |         |         |         |

| N/A  | TXNPAD9         | A9     |         |         |         |         |

Table 11: FF1148 — XC2VP40 and XC2VP50

|      |                  |            | No Co   | nnects  |

|------|------------------|------------|---------|---------|

| Bank | Pin Description  | Pin Number | XC2VP40 | XC2VP50 |

| 2    | IO_L40P_2        | K3         |         |         |

| 2    | IO_L41N_2        | R9         |         |         |

| 2    | IO_L41P_2        | P9         |         |         |

| 2    | IO_L42N_2        | K1         |         |         |

| 2    | IO_L42P_2        | K2         |         |         |

| 2    | IO_L43N_2        | L5         |         |         |

| 2    | IO_L43P_2        | L6         |         |         |

| 2    | IO_L44N_2        | P7         |         |         |

| 2    | IO_L44P_2        | P8         |         |         |

| 2    | IO_L45N_2        | L1         |         |         |

| 2    | IO_L45P_2        | L2         |         |         |

| 2    | IO_L46N_2/VREF_2 | M5         |         |         |

| 2    | IO_L46P_2        | M6         |         |         |

| 2    | IO_L47N_2        | R10        |         |         |

| 2    | IO_L47P_2        | R11        |         |         |

| 2    | IO_L48N_2        | M3         |         |         |

| 2    | IO_L48P_2        | M4         |         |         |

| 2    | IO_L49N_2        | M1         |         |         |

| 2    | IO_L49P_2        | M2         |         |         |

| 2    | IO_L50N_2        | R7         |         |         |

| 2    | IO_L50P_2        | Т8         |         |         |

| 2    | IO_L51N_2        | P4         |         |         |

| 2    | IO_L51P_2        | N4         |         |         |

| 2    | IO_L52N_2/VREF_2 | N2         |         |         |

| 2    | IO_L52P_2        | N3         |         |         |

| 2    | IO_L53N_2        | T10        |         |         |

| 2    | IO_L53P_2        | T11        |         |         |

| 2    | IO_L54N_2        | P5         |         |         |

| 2    | IO_L54P_2        | P6         |         |         |

| 2    | IO_L55N_2        | R3         |         |         |

| 2    | IO_L55P_2        | P3         |         |         |

| 2    | <br>IO_L56N_2    | T6         |         |         |

| 2    | IO_L56P_2        | T7         |         |         |

| 2    | IO_L57N_2        | P1         |         |         |

| 2    | IO_L57P_2        | P2         |         |         |

| 2    | IO_L58N_2/VREF_2 | R5         |         |         |

| 2    | IO_L58P_2        | R6         |         |         |

| 2    | IO_L59N_2        | U10        |         |         |

Table 11: FF1148 — XC2VP40 and XC2VP50

|      |                  |            | No Connects |         |  |

|------|------------------|------------|-------------|---------|--|

| Bank | Pin Description  | Pin Number | XC2VP40     | XC2VP50 |  |

| 7    | IO_L13P_7        | D28        |             |         |  |

| 7    | IO_L13N_7        | E28        |             |         |  |

| 7    | IO_L12P_7        | C33        |             |         |  |

| 7    | IO_L12N_7        | C34        |             |         |  |

| 7    | IO_L11P_7        | J27        |             |         |  |

| 7    | IO_L11N_7        | K27        |             |         |  |

| 7    | IO_L10P_7        | B30        |             |         |  |

| 7    | IO_L10N_7/VREF_7 | C30        |             |         |  |

| 7    | IO_L09P_7        | C28        |             |         |  |

| 7    | IO_L09N_7        | C29        |             |         |  |

| 7    | IO_L08P_7        | H27        |             |         |  |

| 7    | IO_L08N_7        | H28        |             |         |  |

| 7    | IO_L07P_7        | A32        |             |         |  |

| 7    | IO_L07N_7        | B32        |             |         |  |

| 7    | IO_L06P_7        | A31        |             |         |  |

| 7    | IO_L06N_7        | B31        |             |         |  |

| 7    | IO_L05P_7        | D27        |             |         |  |

| 7    | IO_L05N_7        | E27        |             |         |  |

| 7    | IO_L04P_7        | A29        |             |         |  |

| 7    | IO_L04N_7/VREF_7 | B29        |             |         |  |

| 7    | IO_L03P_7        | A28        |             |         |  |

| 7    | IO_L03N_7        | B28        |             |         |  |

| 7    | IO_L02P_7        | D26        |             |         |  |

| 7    | IO_L02N_7        | C26        |             |         |  |

| 7    | IO_L01P_7/VRN_7  | B26        |             |         |  |

| 7    | IO_L01N_7/VRP_7  | B27        |             |         |  |

|      |                  |            |             |         |  |

| 7    | VCCO_7           | E33        |             |         |  |

| 7    | VCCO_7           | R31        |             |         |  |

| 7    | VCCO_7           | L31        |             |         |  |

| 7    | VCCO_7           | G31        |             |         |  |

| 7    | VCCO_7           | C31        |             |         |  |

| 7    | VCCO_7           | R27        |             |         |  |

| 7    | VCCO_7           | L27        |             |         |  |

| 7    | VCCO_7           | G27        |             |         |  |

| 7    | VCCO_7           | C27        |             |         |  |

| 7    | VCCO_7           | J26        |             |         |  |

| 7    | VCCO_7           | M24        |             |         |  |

Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                  | Pin    |         | nnects  |

|------|------------------|--------|---------|---------|

| Bank | Pin Description  | Number | XC2VP50 | XC2VP70 |

| 0    | IO_L34P_0        | E27    | NC      |         |

| 0    | IO_L35N_0        | L26    | NC      |         |

| 0    | IO_L35P_0        | L25    | NC      |         |

| 0    | IO_L36N_0        | G26    | NC      |         |

| 0    | IO_L36P_0/VREF_0 | H26    | NC      |         |

| 0    | IO_L37N_0        | E26    |         |         |

| 0    | IO_L37P_0        | F26    |         |         |

| 0    | IO_L38N_0        | K25    |         |         |

| 0    | IO_L38P_0        | K24    |         |         |

| 0    | IO_L39N_0        | C26    |         |         |

| 0    | IO_L39P_0        | D26    |         |         |

| 0    | IO_L43N_0        | H25    |         |         |

| 0    | IO_L43P_0        | J25    |         |         |

| 0    | IO_L44N_0        | M25    |         |         |

| 0    | IO_L44P_0        | M24    |         |         |

| 0    | IO_L45N_0        | F25    |         |         |

| 0    | IO_L45P_0/VREF_0 | G25    |         |         |

| 0    | IO_L46N_0        | C25    |         |         |

| 0    | IO_L46P_0        | D25    |         |         |

| 0    | IO_L47N_0        | L23    |         |         |

| 0    | IO_L47P_0        | M22    |         |         |

| 0    | IO_L48N_0        | H24    |         |         |

| 0    | IO_L48P_0        | J24    |         |         |

| 0    | IO_L49N_0        | E25    |         |         |

| 0    | IO_L49P_0        | E24    |         |         |

| 0    | IO_L50_0/No_Pair | N23    |         |         |

| 0    | IO_L53_0/No_Pair | M23    |         |         |

| 0    | IO_L54N_0        | H23    |         |         |

| 0    | IO_L54P_0        | J23    |         |         |

| 0    | IO_L55N_0        | F24    |         |         |

| 0    | IO_L55P_0        | G23    |         |         |

| 0    | IO_L56N_0        | K22    |         |         |

| 0    | IO_L56P_0        | L22    |         |         |

| 0    | <br>IO_L57N_0    | C23    |         |         |

| 0    | IO_L57P_0/VREF_0 | D23    |         |         |

| 0    | IO_L58N_0        | H22    |         |         |

| 0    | <br>IO_L58P_0    | J22    |         |         |

| 0    | IO_L59N_0        | N22    |         |         |

Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       | on                      |            | No Co                | nnects   |

|------|-----------------------|-------------------------|------------|----------------------|----------|

| Bank | Virtex-II Pro Devices | XC2VPX70 (if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 3    | IO_L17N_3             |                         | AL9        |                      |          |

| 3    | IO_L17P_3             |                         | AL10       |                      |          |

| 3    | IO_L16N_3             |                         | AM1        |                      |          |

| 3    | IO_L16P_3             |                         | AM2        |                      |          |

| 3    | IO_L15N_3/VREF_3      |                         | AM3        |                      |          |

| 3    | IO_L15P_3             |                         | AN3        |                      |          |

| 3    | IO_L14N_3             |                         | AM8        |                      |          |

| 3    | IO_L14P_3             |                         | AM9        |                      |          |

| 3    | IO_L13N_3             |                         | AM4        |                      |          |

| 3    | IO_L13P_3             |                         | AM5        |                      |          |

| 3    | IO_L12N_3             |                         | AM6        |                      |          |

| 3    | IO_L12P_3             |                         | AM7        |                      |          |

| 3    | IO_L11N_3             |                         | AN9        |                      |          |

| 3    | IO_L11P_3             |                         | AM10       |                      |          |

| 3    | IO_L10N_3             |                         | AN1        |                      |          |

| 3    | IO_L10P_3             |                         | AN2        |                      |          |

| 3    | IO_L09N_3/VREF_3      |                         | AN5        |                      |          |

| 3    | IO_L09P_3             |                         | AN6        |                      |          |

| 3    | IO_L08N_3             |                         | AN7        |                      |          |

| 3    | IO_L08P_3             |                         | AN8        |                      |          |

| 3    | IO_L07N_3             |                         | AP1        |                      |          |

| 3    | IO_L07P_3             |                         | AP2        |                      |          |

| 3    | IO_L84N_3             |                         | AP4        |                      |          |

| 3    | IO_L84P_3             |                         | AP5        |                      |          |

| 3    | IO_L83N_3             |                         | AR7        |                      |          |

| 3    | IO_L83P_3             |                         | AP8        |                      |          |

| 3    | IO_L82N_3             |                         | AP6        |                      |          |

| 3    | IO_L82P_3             |                         | AP7        |                      |          |

| 3    | IO_L81N_3/VREF_3      |                         | AR2        |                      |          |

| 3    | IO_L81P_3             |                         | AR3        |                      |          |

| 3    | IO_L80N_3             |                         | AT5        |                      |          |

| 3    | IO_L80P_3             |                         | AR6        |                      |          |

| 3    | IO_L79N_3             |                         | AR4        |                      |          |

| 3    | IO_L79P_3             |                         | AR5        |                      |          |

| 3    | IO_L78N_3             |                         | AT1        |                      |          |

| 3    | IO_L78P_3             |                         | AT2        |                      |          |

Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       |                         |            | No Connects          |          |

|------|-----------------------|-------------------------|------------|----------------------|----------|

| Bank | Virtex-II Pro Devices | XC2VPX70 (if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 5    | IO_L19P_5             |                         | AV32       |                      |          |

| 5    | IO_L09N_5/VREF_5      |                         | AP32       |                      |          |

| 5    | IO_L09P_5             |                         | AR32       |                      |          |

| 5    | IO_L08N_5             |                         | AW33       |                      |          |

| 5    | IO_L08P_5             |                         | AV33       |                      |          |

| 5    | IO_L07N_5/VREF_5      |                         | AT33       |                      |          |

| 5    | IO_L07P_5             |                         | AU33       |                      |          |

| 5    | IO_L06N_5/VRP_5       |                         | AP33       |                      |          |

| 5    | IO_L06P_5/VRN_5       |                         | AR33       |                      |          |

| 5    | IO_L05_5/No_Pair      |                         | AN32       |                      |          |

| 5    | IO_L03N_5/D4          |                         | AW34       |                      |          |

| 5    | IO_L03P_5/D5          |                         | AY34       |                      |          |

| 5    | IO_L02N_5/D6          |                         | AV34       |                      |          |

| 5    | IO_L02P_5/D7          |                         | AU34       |                      |          |

| 5    | IO_L01N_5/RDWR_B      |                         | AR34       |                      |          |

| 5    | IO_L01P_5/CS_B        |                         | AT34       |                      |          |

|      |                       |                         |            |                      |          |

| 6    | IO_L01P_6/VRN_6       |                         | AW37       |                      |          |

| 6    | IO_L01N_6/VRP_6       |                         | AV37       |                      |          |

| 6    | IO_L02P_6             |                         | AW36       |                      |          |

| 6    | IO_L02N_6             |                         | AV36       |                      |          |

| 6    | IO_L03P_6             |                         | AY37       |                      |          |

| 6    | IO_L03N_6/VREF_6      |                         | AY38       |                      |          |

| 6    | IO_L04P_6             |                         | AU36       |                      |          |

| 6    | IO_L04N_6             |                         | AT37       |                      |          |

| 6    | IO_L05P_6             |                         | AU35       |                      |          |

| 6    | IO_L05N_6             |                         | AT35       |                      |          |

| 6    | IO_L06P_6             |                         | AW41       |                      |          |

| 6    | IO_L06N_6             |                         | AW42       |                      |          |

| 6    | IO_L73P_6             |                         | AV41       |                      |          |

| 6    | IO_L73N_6             |                         | AV42       |                      |          |

| 6    | IO_L74P_6             |                         | AW40       |                      |          |

| 6    | IO_L74N_6             |                         | AV40       |                      |          |

| 6    | IO_L75P_6             |                         | AU39       |                      |          |

| 6    | IO_L75N_6/VREF_6      |                         | AU40       |                      |          |

| 6    | IO_L76P_6             |                         | AU41       |                      |          |

Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       | Pin Description            |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

| Bank | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| N/A  | GND                   |                            | AE19       |                      |          |

| N/A  | GND                   |                            | AE18       |                      |          |

| N/A  | GND                   |                            | AE17       |                      |          |

| N/A  | GND                   |                            | AE9        |                      |          |

| N/A  | GND                   |                            | AE6        |                      |          |

| N/A  | GND                   |                            | AF25       |                      |          |

| N/A  | GND                   |                            | AF24       |                      |          |

| N/A  | GND                   |                            | AF23       |                      |          |

| N/A  | GND                   |                            | AF22       |                      |          |

| N/A  | GND                   |                            | AF21       |                      |          |

| N/A  | GND                   |                            | AF20       |                      |          |

| N/A  | GND                   |                            | AF19       |                      |          |

| N/A  | GND                   |                            | AF18       |                      |          |

| N/A  | GND                   |                            | AG42       |                      |          |

| N/A  | GND                   |                            | AG1        |                      |          |

| N/A  | GND                   |                            | AH39       |                      |          |

| N/A  | GND                   |                            | AH36       |                      |          |

| N/A  | GND                   |                            | AH7        |                      |          |

| N/A  | GND                   |                            | AH4        |                      |          |

| N/A  | GND                   |                            | AL42       |                      |          |

| N/A  | GND                   |                            | AL1        |                      |          |

| N/A  | GND                   |                            | AM22       |                      |          |

| N/A  | GND                   |                            | AM21       |                      |          |

| N/A  | GND                   |                            | AN39       |                      |          |

| N/A  | GND                   |                            | AN4        |                      |          |

| N/A  | GND                   |                            | AP34       |                      |          |

| N/A  | GND                   |                            | AP9        |                      |          |

| N/A  | GND                   |                            | AR42       |                      |          |

| N/A  | GND                   |                            | AR35       |                      |          |

| N/A  | GND                   |                            | AR22       |                      |          |

| N/A  | GND                   |                            | AR21       |                      |          |

| N/A  | GND                   |                            | AR8        |                      |          |

| N/A  | GND                   |                            | AR1        |                      |          |

| N/A  | GND                   |                            | AT36       |                      |          |

| N/A  | GND                   |                            | AT7        |                      |          |

| N/A  | GND                   |                            | AU37       |                      |          |

*Table 14:* **FF1696** — **XC2VP100**

|      |                  |            | No Connects |  |

|------|------------------|------------|-------------|--|

| Bank | Pin Description  | Pin Number | XC2VP100    |  |

| 2    | IO_L69P_2        | F6         |             |  |

| 2    | IO_L70N_2/VREF_2 | G5         |             |  |

| 2    | IO_L70P_2        | F5         |             |  |

| 2    | IO_L71N_2        | P10        |             |  |

| 2    | IO_L71P_2        | P11        |             |  |

| 2    | IO_L72N_2        | G3         |             |  |

| 2    | IO_L72P_2        | G4         |             |  |

| 2    | IO_L07N_2        | G1         |             |  |

| 2    | IO_L07P_2        | G2         |             |  |

| 2    | IO_L08N_2        | N8         |             |  |

| 2    | IO_L08P_2        | P9         |             |  |

| 2    | IO_L09N_2        | H6         |             |  |

| 2    | IO_L09P_2        | H7         |             |  |

| 2    | IO_L10N_2/VREF_2 | H4         |             |  |

| 2    | IO_L10P_2        | H5         |             |  |

| 2    | IO_L11N_2        | R12        |             |  |

| 2    | IO_L11P_2        | T12        |             |  |

| 2    | IO_L12N_2        | H2         |             |  |

| 2    | IO_L12P_2        | H3         |             |  |

| 2    | IO_L13N_2        | J6         |             |  |

| 2    | IO_L13P_2        | J7         |             |  |

| 2    | IO_L14N_2        | R10        |             |  |

| 2    | IO_L14P_2        | R11        |             |  |

| 2    | IO_L15N_2        | J3         |             |  |

| 2    | IO_L15P_2        | J4         |             |  |

| 2    | IO_L16N_2/VREF_2 | J2         |             |  |

| 2    | IO_L16P_2        | H1         |             |  |

| 2    | IO_L17N_2        | R8         |             |  |

| 2    | IO_L17P_2        | R9         |             |  |

| 2    | IO_L18N_2        | K5         |             |  |

| 2    | IO_L18P_2        | K6         |             |  |

| 2    | IO_L19N_2        | K1         |             |  |

| 2    | IO_L19P_2        | K2         |             |  |

| 2    | IO_L20N_2        | T10        |             |  |

| 2    | IO_L20P_2        | T11        |             |  |

| 2    | IO_L21N_2        | L7         |             |  |

| 2    | IO_L21P_2        | K7         |             |  |

*Table 14:* **FF1696** — **XC2VP100**

|      |                 |            | No Connects |  |

|------|-----------------|------------|-------------|--|

| Bank | Pin Description | Pin Number | XC2VP100    |  |

| N/A  | VCCINT          | AG26       |             |  |

| N/A  | VCCINT          | AF26       |             |  |

| N/A  | VCCINT          | U26        |             |  |

| N/A  | VCCINT          | T26        |             |  |

| N/A  | VCCINT          | R26        |             |  |

| N/A  | VCCINT          | AG25       |             |  |

| N/A  | VCCINT          | T25        |             |  |

| N/A  | VCCINT          | AG24       |             |  |

| N/A  | VCCINT          | T24        |             |  |

| N/A  | VCCINT          | AG23       |             |  |

| N/A  | VCCINT          | T23        |             |  |

| N/A  | VCCINT          | AG22       |             |  |

| N/A  | VCCINT          | T22        |             |  |

| N/A  | VCCINT          | AG21       |             |  |

| N/A  | VCCINT          | T21        |             |  |

| N/A  | VCCINT          | AG20       |             |  |

| N/A  | VCCINT          | T20        |             |  |

| N/A  | VCCINT          | AG19       |             |  |

| N/A  | VCCINT          | T19        |             |  |

| N/A  | VCCINT          | AG18       |             |  |

| N/A  | VCCINT          | T18        |             |  |

| N/A  | VCCINT          | AH17       |             |  |

| N/A  | VCCINT          | AG17       |             |  |

| N/A  | VCCINT          | AF17       |             |  |

| N/A  | VCCINT          | U17        |             |  |

| N/A  | VCCINT          | T17        |             |  |

| N/A  | VCCINT          | R17        |             |  |

| N/A  | VCCINT          | AJ16       |             |  |

| N/A  | VCCINT          | AH16       |             |  |

| N/A  | VCCINT          | AG16       |             |  |

| N/A  | VCCINT          | AF16       |             |  |

| N/A  | VCCINT          | AE16       |             |  |

| N/A  | VCCINT          | AD16       |             |  |

| N/A  | VCCINT          | AC16       |             |  |

| N/A  | VCCINT          | AB16       |             |  |

| N/A  | VCCINT          | AA16       |             |  |

| N/A  | VCCINT          | Y16        |             |  |