Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

EXF

| Product Status                 | Obsolete                                                      |

|--------------------------------|---------------------------------------------------------------|

| Number of LABs/CLBs            | 2320                                                          |

| Number of Logic Elements/Cells | 20880                                                         |

| Total RAM Bits                 | 1622016                                                       |

| Number of I/O                  | 564                                                           |

| Number of Gates                | -                                                             |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 1152-BBGA, FCBGA                                              |

| Supplier Device Package        | 1152-FCBGA (35x35)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2vp20-7ffg1152c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description

DS083 (v5.0) June 21, 2011

### **Product Specification**

# Virtex-II Pro<sup>(1)</sup> Array Functional Description

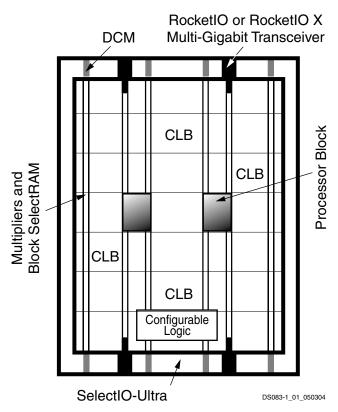

### Figure 1: Virtex-II Pro Generic Architecture Overview

This module describes the following Virtex<sup>™</sup>-II Pro functional components, as shown in Figure 1:

- Embedded RocketIO<sup>™</sup> (up to 3.125 Gb/s) or RocketIO X (up to 6.25 Gb/s) Multi-Gigabit Transceivers (MGTs)

- Processor blocks with embedded IBM PowerPC<sup>™</sup> 405 RISC CPU core (PPC405) and integration circuitry.

- FPGA fabric based on Virtex-II architecture.

# **Virtex-II Pro User Guides**

Virtex-II Pro User Guides cover theory of operation in more detail, and include implementation details, primitives and attributes, command/instruction sets, and many HDL code examples where appropriate. All parameter specifications are given only in Module 3 of this Data Sheet.

These User Guides are available:

- For detailed descriptions of PPC405 embedded core programming models and internal core operations, see <u>PowerPC Processor Reference Guide</u> and <u>PowerPC</u> 405 Processor Block Reference Guide.

- For detailed RocketIO transceiver digital/analog design considerations, see RocketIO Transceiver User Guide.

- For detailed RocketIO X transceiver digital/analog design considerations, see <u>RocketIO X Transceiver</u> <u>User Guide</u>,

- For detailed descriptions of the FPGA fabric (CLB, IOB, DCM, etc.), see <u>Virtex-II Pro Platform FPGA User</u> <u>Guide</u>.

All of the documents above, as well as a complete listing and description of Xilinx-developed Intellectual Property cores for Virtex-II Pro, are available on the Xilinx website.

### **Contents of This Module**

- Functional Description: RocketIO X Multi-Gigabit Transceiver (MGT)

- Functional Description: RocketIO Multi-Gigabit Transceiver (MGT)

- Functional Description: Processor Block

- Functional Description: Embedded PowerPC 405 Core

- Functional Description: FPGA

- Revision History

# Virtex-II Pro Compared to Virtex-II Devices

Virtex-II Pro devices are built on the Virtex-II FPGA architecture. Most FPGA features are identical to Virtex-II devices. Major differences are described below:

- The Virtex-II Pro FPGA family is the first to incorporate embedded PPC405 and RocketIO/RocketIO X cores.

- $V_{CCAUX}$ , the auxiliary supply voltage, is 2.5V instead of 3.3V as for Virtex-II devices. Advanced processing at 0.13  $\mu$ m has resulted in a smaller die, faster speed, and lower power consumption.

- Virtex-II Pro devices are neither bitstream-compatible nor pin-compatible with Virtex-II devices. However, Virtex-II designs can be compiled into Virtex-II Pro devices.

- On-chip input LVDS differential termination is available.

- SSTL3, AGP-2X/AGP, LVPECL\_33, LVDS\_33, and LVDSEXT\_33 standards are not supported.

- The open-drain output pin TDO does not have an internal pull-up resistor.

<sup>1.</sup> Unless otherwise noted, "Virtex-II Pro" refers to members of the Virtex-II Pro and/or Virtex-II Pro X families.

<sup>© 2000–2011</sup> Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM Corp. and is used under license. All other trademarks are the property of their respective owners.

# **Output Swing and Emphasis**

The output swing and emphasis levels are fully programmable. Each is controlled via attributes at configuration, and can be modified via the PMA attribute programming bus.

The programmable output swing control can adjust the differential peak-to-peak output level between 200 mV and 1600 mV.

With emphasis, the differential voltage swing is boosted to create a stronger rising or falling waveform. This method compensates for high frequency loss in the transmission media that would otherwise limit the magnitude of this waveform. Lossy transmission lines cause the dissipation of electrical energy. This emphasis technique extends the distance that signals can be driven down lossy line media and increases the signal-to-noise ratio at the receiver.

Emphasis can be described from two perspectives, additive to the smaller voltage ( $V_{SM}$ ) (pre-emphasis) or subtractive from the larger voltage ( $V_{LG}$ ) (de-emphasis). The resulting benefits in compensating for channel loss are identical. It is simply a relative way of specifying the effect at the transmitter.

The equations for calculating pre-emphasis as a percentage and dB are as follows:

$\begin{aligned} \text{Pre-Emphasis}_{\&} &= ((V_{LG} - V_{SM}) / V_{SM}) \times 100 \\ \text{Pre-Emphasis}_{dB} &= 20 \log(V_{LG} / V_{SM}) \end{aligned}$

The equations for calculating de-emphasis as a percentage and dB are as follows:

$\label{eq:De-Emphasis} \begin{array}{l} \mbox{De-Emphasis}_{\&} = (V_{LG} - V_{SM}) \ / \ V_{LG}) \ x \ 100 \\ \mbox{De-Emphasis}_{B} = 20 \ \log{(V_{SM}/V_{LG})} \end{array}$

The pre-emphasis amount can be programmed in discrete steps between 0% and 500%. The de-emphasis amount can be programmed in discrete steps between 0% and 83%.

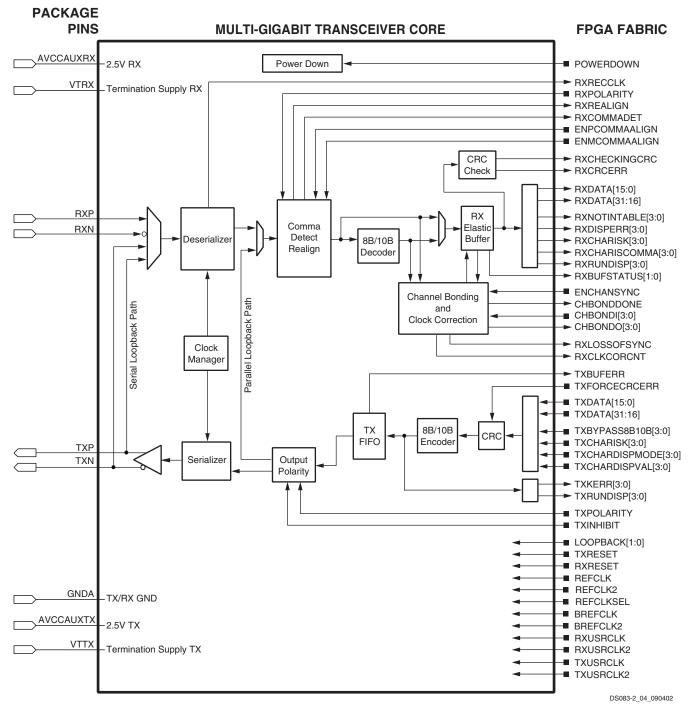

### Serializer

The serializer multiplies the reference frequency provided on REFCLK by 10, 16, 20, 32, or 40, depending on the operation mode. The multiplication of the clock is achieved by using an embedded PLL.

Data is converted from parallel to serial format and transmitted on the TXP and TXN differential outputs. The electrical connection of TXP and TXN can be interchanged through configuration. This option can be controlled by an input (TXPOLARITY) at the FPGA transmitter interface.

### Deserializer

Synchronous serial data reception is facilitated by a clock and data recovery (CDR) circuit. This circuit uses a fully monolithic Phase Lock Loop (PLL), which does not require any external components. The CDR circuit extracts both phase and frequency from the incoming data stream.

The derived clock, RXRECCLK, is generated and locked to as long as it remains within the specified component range.

This clock is presented to the FPGA fabric at 1/10, 1/16, 1/20, 1/32, or 1/40 the incoming data rate depending on the operating mode.

A sufficient number of transitions must be present in the data stream for CDR to work properly. The CDR circuit is guaranteed to work with 8B/10B and 64B/66B encoding. Further, CDR requires approximately 5,000 transitions upon power-up to guarantee locking to the incoming data rate. Once lock is achieved, up to 75 missing transitions can be tolerated before lock to the incoming data stream is lost.

Another feature of CDR is its ability to accept an external precision reference clock, REFCLK, which either acts to clock incoming data or to assist in synchronizing the derived RXRECCLK.

For further clarity, the TXUSRCLK is used to clock data from the FPGA fabric to the TX FIFO. The FIFO depth accounts for the slight phase difference between these two clocks. If the clocks are locked in frequency, then the FIFO acts much like a pass-through buffer.

The receiver can be configured to reverse the RXP and RXN inputs. This can be useful in the event that printed circuit board traces have been reversed.

# **Receiver Lock Control**

The CDR circuits will lock to the reference clock automatically if the data is not present. For proper operation, the frequency of the reference clock must be within  $\pm 100$  ppm of the nominal frequency.

During normal operation, the receiver PLL automatically locks to incoming data (when present) or to the local reference clock (when data is not present). This is the default configuration for all primitives. This function can be overridden via the PMARXLOCKSEL port

When receive PLL lock is forced to the local reference, phase information from the incoming data stream is ignored. Data continues to be sampled, but synchronous to the local reference rather than relative to edges in the data stream.

### **Receive Equalization**

In addition to transmit emphasis, the RocketIO X MGT provides a programmable active receive equalization feature to further compensate the effects of channel attenuation at high frequencies.

By adjusting RXFER, the right amount of equalization can be added to reverse the signal degradation caused by a printed circuit board, a backplane, or a line/switch card. RXFER can be set through software configuration or the PMA Attribute Bus.

### **Receiver Termination**

On-chip termination is provided at the receiver, eliminating the need for external termination. The receiver termination supply ( $V_{TRX}$ ) is the center tap of differential termination to

Figure 10: RocketIO Transceiver Block Diagram

### **Output Swing and Pre-emphasis**

The output swing and pre-emphasis levels of the RocketIO MGTs are fully programmable. Each is controlled via attributes at configuration, but can be modified via partial reconfiguration.

The programmable output swing control can adjust the differential output level between 400 mV and 800 mV in four increments of 100 mV.

With pre-emphasis, the differential voltage swing is boosted to create a stronger rising waveform. This method compensates for high-frequency loss in the transmission media that would otherwise limit the magnitude of this waveform. Lossy transmission lines cause the dissipation of electrical energy. This pre-emphasis technique extends the distance that signals can be driven down lossy line media and increases the signal-to-noise ratio at the receiver.

### Table 5: Clock Ratios for Various Data Widths

| Fabric Data Width | Frequency Ratio of<br>USRCLK:USRCLK2 |

|-------------------|--------------------------------------|

| 1-byte            | 1:2 <sup>(1)</sup>                   |

| 2-byte            | 1:1                                  |

| 4-byte            | 2:1 <sup>(1)</sup>                   |

#### Notes:

1. Each edge of slower clock must align with falling edge of faster clock.

### FPGA Transmit Interface

The FPGA can send either one, two, or four characters of data to the transmitter. Each character can be either 8 bits or 10 bits wide. If 8-bit data is applied, the additional inputs become control signals for the 8B/10B encoder. When the 8B/10B encoder is bypassed, the 10-bit character order is generated as follows:

| TXCHARDISPM | 10DE[0]      | (first bit transmitted) |

|-------------|--------------|-------------------------|

| TXCHARDISPV | 'AL[0]       |                         |

| TXDATA[7:0] | (last bit ti | ansmitted is TXDATA[0]) |

# **Disparity Control**

The 8B/10B encoder is initialized with a negative running disparity. Unique control allows forcing the current running disparity state.

TXRUNDISP signals its current running disparity. This may be useful in those cases where there is a need to manipulate the initial running disparity value.

Bits TXCHARDISPMODE and TXCHARDISPVAL control the generation of running disparity before each byte.

For example, the transceiver can generate the sequence

```

K28.5+ K28.5+ K28.5- K28.5-

Or

K28.5- K28.5- K28.5+ K28.5+

```

by specifying inverted running disparity for the second and fourth bytes.

# Transmit FIFO

Proper operation of the circuit is only possible if the FPGA clock (TXUSRCLK) is frequency-locked to the reference clock (REFCLK). Phase variations up to one clock cycle are allowable. The FIFO has a depth of four. Overflow or underflow conditions are detected and signaled at the interface. Bypassing of this FIFO is programmable.

### 8B/10B Encoder

Note: In the RocketIO transceiver, the most-significant byte is sent first; in the RocketIO X transceiver, the least-significant byte is sent first.

A bypassable 8B/10B encoder is included. The encoder uses the same 256 data characters and 12 control characters used by Gigabit Ethernet, Fibre Channel, and InfiniBand. The encoder accepts 8 bits of data along with a K-character signal for a total of 9 bits per character applied, and generates a 10 bit character for transmission. If the K-character signal is High, the data is encoded into one of the twelve possible K-characters available in the 8B/10B code. If the K-character input is Low, the 8 bits are encoded as standard data. If the K-character input is High, and a user applies other than one of the twelve possible combinations, TXKERR indicates the error.

### 8B/10B Decoder

Note: In the RocketlO transceiver, the most-significant byte is sent first; in the RocketlO X transceiver, the least-significant byte is sent first.

An optional 8B/10B decoder is included. A programmable option allows the decoder to be bypassed. When the 8B/10B decoder is bypassed, the 10-bit character order is, for example,

| RXCHARISK[0] | (first bit received)             |

|--------------|----------------------------------|

| RXRUNDISP[0] |                                  |

| RXDATA[7:0]  | (last bit received is RXDATA[0]) |

The decoder uses the same table that is used for Gigabit Ethernet, Fibre Channel, and InfiniBand. In addition to decoding all data and K-characters, the decoder has several extra features. The decoder separately detects both "disparity errors" and "out-of-band" errors. A disparity error is the reception of 10-bit character that exists within the 8B/10B table but has an incorrect disparity. An out-of-band error is the reception of a 10-bit character that does not exist within the 8B/10B table. It is possible to obtain an out-of-band error without having a disparity error. The proper disparity is always computed for both legal and illegal characters. The current running disparity is available at the RXRUNDISP signal.

The 8B/10B decoder performs a unique operation if out-of-band data is detected. If out-of-band data is detected, the decoder signals the error and passes the illegal 10-bits through and places them on the outputs. This can be used for debugging purposes if desired.

The decoder also signals the reception of one of the 12 valid K-characters. In addition, a programmable comma detect is included. The comma detect signal registers a comma on the receipt of any comma+, comma-, or both. Since the comma is defined as a 7-bit character, this includes several out-of-band characters. Another option allows the decoder to detect only the three defined commas (K28.1, K28.5, and K28.7) as comma+, comma-, or both. In total, there are six possible options, three for valid commas and three for "any comma."

Note that all bytes (1, 2, or 4) at the RX FPGA interface each have their own individual 8B/10B indicators (K-character, disparity error, out-of-band error, current running disparity, and comma detect).

| SelectIO-Ultra | Programmable Current (Worst-Case Guaranteed Minimum) |      |      |      |       |       |       |

|----------------|------------------------------------------------------|------|------|------|-------|-------|-------|

| LVTTL          | 2 mA                                                 | 4 mA | 6 mA | 8 mA | 12 mA | 16 mA | 24 mA |

| LVCMOS33       | 2 mA                                                 | 4 mA | 6 mA | 8 mA | 12 mA | 16 mA | 24 mA |

| LVCMOS25       | 2 mA                                                 | 4 mA | 6 mA | 8 mA | 12 mA | 16 mA | 24 mA |

| LVCMOS18       | 2 mA                                                 | 4 mA | 6 mA | 8 mA | 12 mA | 16 mA | n/a   |

| LVCMOS15       | 2 mA                                                 | 4 mA | 6 mA | 8 mA | 12 mA | 16 mA | n/a   |

#### Table 11: LVCMOS Programmable Currents (Sink and Source)

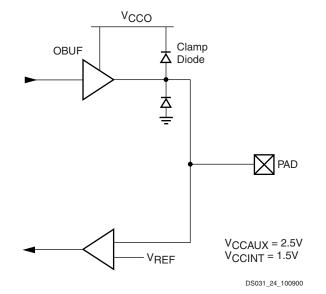

Figure 23 shows the SSTL2, SSTL18, and HSTL configurations. HSTL can sink current up to 48 mA. (HSTL IV)

Figure 23: SSTL or HSTL SelectIO-Ultra Standards

All pads are protected against damage from electrostatic discharge (ESD) and from over-voltage transients. Virtex-II Pro uses two memory cells to control the configuration of an I/O as an input. This is to reduce the probability of an I/O configured as an input from flipping to an output when subjected to a single event upset (SEU) in space applications.

Prior to configuration, all outputs not involved in configuration are forced into their high-impedance state. The pull-down resistors and the weak-keeper circuits are inactive. The dedicated pin HSWAP\_EN controls the pull-up resistors prior to configuration. By default, HSWAP\_EN is set High, which disables the pull-up resistors on user I/O pins. When HSWAP\_EN is set Low, the pull-up resistors are activated on user I/O pins.

All Virtex-II Pro IOBs (except RocketIO transceiver pins) support IEEE 1149.1 and IEEE 1532 compatible Boundary-Scan testing.

# Input Path

The Virtex-II Pro IOB input path routes input signals directly to internal logic and / or through an optional input flip-flop or latch, or through the DDR input registers. An optional delay element at the D-input of the storage element eliminates pad-to-pad hold time. The delay is matched to the internal clock-distribution delay of the Virtex-II Pro device, and when used, assures that the pad-to-pad hold time is zero.

Each input buffer can be configured to conform to any of the low-voltage signaling standards supported. In some of these standards the input buffer utilizes a user-supplied threshold voltage,  $V_{\text{REF}}$ . The need to supply  $V_{\text{REF}}$  imposes constraints on which standards can be used in the same bank. See I/O banking description.

### **Output Path**

The output path includes a 3-state output buffer that drives the output signal onto the pad. The output and / or the 3-state signal can be routed to the buffer directly from the internal logic or through an output / 3-state flip-flop or latch, or through the DDR output / 3-state registers.

Each output driver can be individually programmed for a wide range of low-voltage signaling standards. In most signaling standards, the output High voltage depends on an externally supplied  $V_{CCO}$  voltage. The need to supply  $V_{CCO}$  imposes constraints on which standards can be used in the same bank. See I/O banking description.

### I/O Banking

Some of the I/O standards described above require  $V_{CCO}$  and  $V_{REF}$  voltages. These voltages are externally supplied and connected to device pins that serve groups of IOB blocks, called banks. Consequently, restrictions exist about which I/O standards can be combined within a given bank.

Eight I/O banks result from dividing each edge of the FPGA into two banks, as shown in Figure 24 and Figure 25. Each bank has multiple  $V_{CCO}$  pins, all of which must be connected to the same voltage. This voltage is determined by the output standards in use.

### Table 7: FG676/FGG676 — XC2VP20, XC2VP30, and XC2VP40

|      |                  |            | No Connects |         |         |  |

|------|------------------|------------|-------------|---------|---------|--|

| Bank | Pin Description  | Pin Number | XC2VP20     | XC2VP30 | XC2VP40 |  |

| 6    | IO_L55P_6        | T2         |             |         |         |  |

| 6    | IO_L55N_6        | T1         |             |         |         |  |

| 6    | IO_L57P_6        | R9         |             |         |         |  |

| 6    | IO_L57N_6/VREF_6 | R8         |             |         |         |  |

| 6    | IO_L59P_6        | R6         |             |         |         |  |

| 6    | IO_L59N_6        | P6         |             |         |         |  |

| 6    | IO_L60P_6        | R5         |             |         |         |  |

| 6    | IO_L60N_6        | R4         |             |         |         |  |

| 6    | IO_L85P_6        | R2         |             |         |         |  |

| 6    | IO_L85N_6        | R1         |             |         |         |  |

| 6    | IO_L87P_6        | P9         |             |         |         |  |

| 6    | IO_L87N_6/VREF_6 | P8         |             |         |         |  |

| 6    | IO_L89P_6        | P5         |             |         |         |  |

| 6    | IO_L89N_6        | P4         |             |         |         |  |

| 6    | IO_L90P_6        | P3         |             |         |         |  |

| 6    | IO_L90N_6        | P2         |             |         |         |  |

|      |                  |            |             |         |         |  |

| 7    | IO_L90P_7        | N2         |             |         |         |  |

| 7    | IO_L90N_7        | N3         |             |         |         |  |

| 7    | IO_L88P_7        | N4         |             |         |         |  |

| 7    | IO_L88N_7/VREF_7 | N5         |             |         |         |  |

| 7    | IO_L86P_7        | N8         |             |         |         |  |

| 7    | IO_L86N_7        | N9         |             |         |         |  |

| 7    | IO_L85P_7        | M1         |             |         |         |  |

| 7    | IO_L85N_7        | M2         |             |         |         |  |

| 7    | IO_L60P_7        | M4         |             |         |         |  |

| 7    | IO_L60N_7        | M5         |             |         |         |  |

| 7    | IO_L58P_7        | N6         |             |         |         |  |

| 7    | IO_L58N_7/VREF_7 | M6         |             |         |         |  |

| 7    | IO_L56P_7        | M8         |             |         |         |  |

| 7    | IO_L56N_7        | M9         |             |         |         |  |

| 7    | IO_L55P_7        | L1         |             |         |         |  |

| 7    | IO_L55N_7        | L2         |             |         |         |  |

| 7    | IO_L54P_7        | L5         |             |         |         |  |

| 7    | IO_L54N_7        | L6         |             |         |         |  |

### Table 7: FG676/FGG676 — XC2VP20, XC2VP30, and XC2VP40

|      |                  |            | No Connects |         |         |  |

|------|------------------|------------|-------------|---------|---------|--|

| Bank | Pin Description  | Pin Number | XC2VP20     | XC2VP30 | XC2VP40 |  |

| 7    | IO_L04N_7/VREF_7 | E2         |             |         |         |  |

| 7    | IO_L03P_7        | F5         |             |         |         |  |

| 7    | IO_L03N_7        | E4         |             |         |         |  |

| 7    | IO_L02P_7        | D1         |             |         |         |  |

| 7    | IO_L02N_7        | D2         |             |         |         |  |

| 7    | IO_L01P_7/VRN_7  | C1         |             |         |         |  |

| 7    | IO_L01N_7/VRP_7  | C2         |             |         |         |  |

|      |                  |            |             |         |         |  |

| 0    | VCCO_0           | C5         |             |         |         |  |

| 0    | VCCO_0           | C8         |             |         |         |  |

| 0    | VCCO_0           | D11        |             |         |         |  |

| 0    | VCCO_0           | J10        |             |         |         |  |

| 0    | VCCO_0           | J11        |             |         |         |  |

| 0    | VCCO_0           | K12        |             |         |         |  |

| 0    | VCCO_0           | K13        |             |         |         |  |

| 1    | VCCO_1           | C19        |             |         |         |  |

| 1    | VCCO_1           | C22        |             |         |         |  |

| 1    | VCCO_1           | D16        |             |         |         |  |

| 1    | VCCO_1           | J16        |             |         |         |  |

| 1    | VCCO_1           | J17        |             |         |         |  |

| 1    | VCCO_1           | K14        |             |         |         |  |

| 1    | VCCO_1           | K15        |             |         |         |  |

| 2    | VCCO_2           | E24        |             |         |         |  |

| 2    | VCCO_2           | H24        |             |         |         |  |

| 2    | VCCO_2           | K18        |             |         |         |  |

| 2    | VCCO_2           | L18        |             |         |         |  |

| 2    | VCCO_2           | L23        |             |         |         |  |

| 2    | VCCO_2           | M17        |             |         |         |  |

| 2    | VCCO_2           | N17        |             |         |         |  |

| 3    | VCCO_3           | P17        |             |         |         |  |

| 3    | VCCO_3           | R17        |             |         |         |  |

| 3    | VCCO_3           | T18        |             |         |         |  |

| 3    | VCCO_3           | T23        |             |         |         |  |

| 3    | VCCO_3           | U18        |             |         |         |  |

| 3    | VCCO_3           | W24        |             |         |         |  |

### Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      | Pin Description  | Pin    | No Connects |        |        |  |

|------|------------------|--------|-------------|--------|--------|--|

| Bank |                  | Number | XC2VP2      | XC2VP4 | XC2VP7 |  |

| 7    | IO_L44P_7        | G24    | NC          |        |        |  |

| 7    | IO_L44N_7        | G23    | NC          |        |        |  |

| 7    | IO_L43P_7        | G22    | NC          |        |        |  |

| 7    | IO_L43N_7        | G21    | NC          |        |        |  |

| 7    | IO_L42P_7        | F25    | NC          | NC     | NC     |  |

| 7    | IO_L42N_7        | F24    | NC          | NC     | NC     |  |

| 7    | IO_L40P_7        | F23    | NC          | NC     | NC     |  |

| 7    | IO_L40N_7/VREF_7 | F22    | NC          | NC     | NC     |  |

| 7    | IO_L06P_7        | E26    |             |        |        |  |

| 7    | IO_L06N_7        | E25    |             |        |        |  |

| 7    | IO_L05P_7        | E24    |             |        |        |  |

| 7    | IO_L05N_7        | E23    |             |        |        |  |

| 7    | IO_L04P_7        | D26    |             |        |        |  |

| 7    | IO_L04N_7/VREF_7 | D25    |             |        |        |  |

| 7    | IO_L03P_7        | C26    |             |        |        |  |

| 7    | IO_L03N_7        | C25    |             |        |        |  |

| 7    | IO_L02P_7        | B26    |             |        |        |  |

| 7    | IO_L02N_7        | A25    |             |        |        |  |

| 7    | IO_L01P_7/VRN_7  | D24    |             |        |        |  |

| 7    | IO_L01N_7/VRP_7  | C23    |             |        |        |  |

|      |                  |        |             |        |        |  |

| 0    | VCCO_0           | C17    |             |        |        |  |

| 0    | VCCO_0           | C20    |             |        |        |  |

| 0    | VCCO_0           | H17    |             |        |        |  |

| 0    | VCCO_0           | H18    |             |        |        |  |

| 0    | VCCO_0           | J14    |             |        |        |  |

| 0    | VCCO_0           | J15    |             |        |        |  |

| 0    | VCCO_0           | J16    |             |        |        |  |

| 1    | VCCO_1           | C7     |             |        |        |  |

| 1    | VCCO_1           | H9     |             |        |        |  |

| 1    | VCCO_1           | C10    |             |        |        |  |

| 1    | <br>VCCO_1       | H10    |             |        |        |  |

| 1    | <br>VCCO_1       | J11    |             |        |        |  |

| 1    | VCCO_1           | J12    |             |        |        |  |

| 1    | <br>VCCO_1       | J13    |             |        |        |  |

| 2    | <br>VCCO_2       | G2     |             |        |        |  |

| 2    | VCCO_2           | J8     |             |        |        |  |

# Table 9: FF896 — XC2VP7, XC2VP20, XC2VPX20, and XC2VP30

|      | Pin Description       | on                         |               | No Connects |                      |         |  |

|------|-----------------------|----------------------------|---------------|-------------|----------------------|---------|--|

| Bank | Virtex-II Pro devices | XC2VPX20<br>(if Different) | Pin<br>Number | XC2VP7      | XC2VP20,<br>XC2VPX20 | XC2VP30 |  |

| 0    | IO_L01N_0/VRP_0       |                            | E25           |             |                      |         |  |

| 0    | IO_L01P_0/VRN_0       |                            | E24           |             |                      |         |  |

| 0    | IO_L02N_0             |                            | F24           |             |                      |         |  |

| 0    | IO_L02P_0             |                            | F23           |             |                      |         |  |

| 0    | IO_L03N_0             |                            | E23           |             |                      |         |  |

| 0    | IO_L03P_0/VREF_0      |                            | E22           |             |                      |         |  |

| 0    | IO_L05_0/No_Pair      |                            | G23           |             |                      |         |  |

| 0    | IO_L06N_0             |                            | H22           |             |                      |         |  |

| 0    | IO_L06P_0             |                            | G22           |             |                      |         |  |

| 0    | IO_L07N_0             |                            | F22           |             |                      |         |  |

| 0    | IO_L07P_0             |                            | F21           |             |                      |         |  |

| 0    | IO_L08N_0             |                            | D24           |             |                      |         |  |

| 0    | IO_L08P_0             |                            | C24           |             |                      |         |  |

| 0    | IO_L09N_0             |                            | H21           |             |                      |         |  |

| 0    | IO_L09P_0/VREF_0      |                            | G21           |             |                      |         |  |

| 0    | IO_L37N_0             |                            | E21           |             |                      |         |  |

| 0    | IO_L37P_0             |                            | D21           |             |                      |         |  |

| 0    | IO_L38N_0             |                            | D23           |             |                      |         |  |

| 0    | IO_L38P_0             |                            | C23           |             |                      |         |  |

| 0    | IO_L39N_0             |                            | H20           |             |                      |         |  |

| 0    | IO_L39P_0             |                            | G20           |             |                      |         |  |

| 0    | IO_L43N_0             |                            | E20           |             |                      |         |  |

| 0    | IO_L43P_0             |                            | D20           |             |                      |         |  |

| 0    | IO_L44N_0             |                            | B23           |             |                      |         |  |

| 0    | IO_L44P_0             |                            | A23           |             |                      |         |  |

| 0    | IO_L45N_0             |                            | H19           |             |                      |         |  |

| 0    | IO_L45P_0/VREF_0      |                            | G19           |             |                      |         |  |

| 0    | IO_L46N_0             |                            | E19           | NC          |                      |         |  |

| 0    | IO_L46P_0             |                            | E18           | NC          |                      |         |  |

| 0    | IO_L47N_0             |                            | C22           | NC          |                      |         |  |

| 0    | IO_L47P_0             |                            | B22           | NC          |                      |         |  |

| 0    | IO_L48N_0             |                            | F20           | NC          |                      |         |  |

| 0    | IO_L48P_0             |                            | F19           | NC          |                      |         |  |

| 0    | IO_L49N_0             |                            | G17           | NC          |                      |         |  |

| 0    | IO_L49P_0             |                            | F17           | NC          |                      |         |  |

| 0    | IO_L50_0/No_Pair      |                            | B21           | NC          |                      |         |  |

### Table 10: FF1152 — XC2VP20, XC2VP30, XC2VP40, and XC2VP50

|      | Pin No Connects  |        | nnects  | ts      |         |         |

|------|------------------|--------|---------|---------|---------|---------|

| Bank | Pin Description  | Number | XC2VP20 | XC2VP30 | XC2VP40 | XC2VP50 |

| 6    | IO_L53P_6        | W25    |         |         |         |         |

| 6    | IO_L53N_6        | W26    |         |         |         |         |

| 6    | IO_L54P_6        | AB33   |         |         |         |         |

| 6    | IO_L54N_6        | AA33   |         |         |         |         |

| 6    | IO_L55P_6        | Y28    |         |         |         |         |

| 6    | IO_L55N_6        | Y29    |         |         |         |         |

| 6    | IO_L56P_6        | W27    |         |         |         |         |

| 6    | IO_L56N_6        | W28    |         |         |         |         |

| 6    | IO_L57P_6        | Y31    |         |         |         |         |

| 6    | IO_L57N_6/VREF_6 | Y32    |         |         |         |         |

| 6    | IO_L58P_6        | W29    |         |         |         |         |

| 6    | IO_L58N_6        | W30    |         |         |         |         |

| 6    | IO_L59P_6        | W24    |         |         |         |         |

| 6    | IO_L59N_6        | V24    |         |         |         |         |

| 6    | IO_L60P_6        | AA34   |         |         |         |         |

| 6    | IO_L60N_6        | Y34    |         |         |         |         |

| 6    | IO_L85P_6        | W31    |         |         |         |         |

| 6    | IO_L85N_6        | W32    |         |         |         |         |

| 6    | IO_L86P_6        | V25    |         |         |         |         |

| 6    | IO_L86N_6        | V26    |         |         |         |         |

| 6    | IO_L87P_6        | Y33    |         |         |         |         |

| 6    | IO_L87N_6/VREF_6 | W33    |         |         |         |         |

| 6    | IO_L88P_6        | V29    |         |         |         |         |

| 6    | IO_L88N_6        | V30    |         |         |         |         |

| 6    | IO_L89P_6        | V27    |         |         |         |         |

| 6    | IO_L89N_6        | V28    |         |         |         |         |

| 6    | IO_L90P_6        | V31    |         |         |         |         |

| 6    | IO_L90N_6        | V32    |         |         |         |         |

|      |                  |        |         |         |         |         |

| 7    | IO_L90P_7        | U32    |         |         |         |         |

| 7    | IO_L90N_7        | U31    |         |         |         |         |

| 7    | IO_L89P_7        | U28    |         |         |         |         |

| 7    | IO_L89N_7        | U27    |         |         |         |         |

| 7    | IO_L88P_7        | V33    |         |         |         |         |

| 7    | IO_L88N_7/VREF_7 | U33    |         |         |         |         |

| 7    | IO_L87P_7        | U30    |         |         |         |         |

| 7    | IO_L87N_7        | U29    |         |         |         |         |

| 7    | IO_L86P_7        | U26    |         |         |         |         |

### Table 11: FF1148 — XC2VP40 and XC2VP50

|      | Pin Description  |            | No Connects |         |  |

|------|------------------|------------|-------------|---------|--|

| Bank |                  | Pin Number | XC2VP40     | XC2VP50 |  |

| 3    | IO_L36N_3        | AE4        |             |         |  |

| 3    | IO_L36P_3        | AF4        |             |         |  |

| 3    | IO_L35N_3        | AC10       |             |         |  |

| 3    | IO_L35P_3        | AD10       |             |         |  |

| 3    | IO_L34N_3        | AE1        |             |         |  |

| 3    | IO_L34P_3        | AE2        |             |         |  |

| 3    | IO_L33N_3/VREF_3 | AF6        |             |         |  |

| 3    | IO_L33P_3        | AF7        |             |         |  |

| 3    | IO_L32N_3        | AC8        |             |         |  |

| 3    | IO_L32P_3        | AC9        |             |         |  |

| 3    | IO_L31N_3        | AF2        |             |         |  |

| 3    | IO_L31P_3        | AF3        |             |         |  |

| 3    | IO_L30N_3        | AG5        |             |         |  |

| 3    | IO_L30P_3        | AG6        |             |         |  |

| 3    | IO_L29N_3        | AD9        |             |         |  |

| 3    | IO_L29P_3        | AE9        |             |         |  |

| 3    | IO_L28N_3        | AG4        |             |         |  |

| 3    | IO_L28P_3        | AH3        |             |         |  |

| 3    | IO_L27N_3/VREF_3 | AG2        |             |         |  |

| 3    | IO_L27P_3        | AG3        |             |         |  |

| 3    | IO_L26N_3        | AD7        |             |         |  |

| 3    | IO_L26P_3        | AE7        |             |         |  |

| 3    | IO_L25N_3        | AH6        |             |         |  |

| 3    | IO_L25P_3        | AH7        |             |         |  |

| 3    | IO_L24N_3        | AH5        |             |         |  |

| 3    | IO_L24P_3        | AJ5        |             |         |  |

| 3    | IO_L23N_3        | AE8        |             |         |  |

| 3    | IO_L23P_3        | AF8        |             |         |  |

| 3    | IO_L22N_3        | AH1        |             |         |  |

| 3    | IO_L22P_3        | AH2        |             |         |  |

| 3    | IO_L21N_3/VREF_3 | AJ6        |             |         |  |

| 3    | IO_L21P_3        | AK6        |             |         |  |

| 3    | IO_L20N_3        | AG7        |             |         |  |

| 3    | IO_L20P_3        | AG8        |             |         |  |

| 3    | IO_L19N_3        | AJ3        |             |         |  |

| 3    | IO_L19P_3        | AJ4        |             |         |  |

| 3    | IO_L18N_3        | AJ1        |             |         |  |

| 3    | IO_L18P_3        | AJ2        |             |         |  |

### Table 11: FF1148 — XC2VP40 and XC2VP50

|      |                 |            |         | nnects  |

|------|-----------------|------------|---------|---------|

| Bank | Pin Description | Pin Number | XC2VP40 | XC2VP50 |

| N/A  | VCCINT          | M12        |         |         |

| N/A  | VCCINT          | AD11       |         |         |

| N/A  | VCCINT          | L11        |         |         |

| N/A  | VCCAUX          | AN34       |         |         |

| N/A  | VCCAUX          | AG34       |         |         |

| N/A  | VCCAUX          | U34        |         |         |

| N/A  | VCCAUX          | H34        |         |         |

| N/A  | VCCAUX          | B34        |         |         |

| N/A  | VCCAUX          | AP33       |         |         |

| N/A  | VCCAUX          | A33        |         |         |

| N/A  | VCCAUX          | AP27       |         |         |

| N/A  | VCCAUX          | A27        |         |         |

| N/A  | VCCAUX          | AP17       |         |         |

| N/A  | VCCAUX          | A17        |         |         |

| N/A  | VCCAUX          | AP8        |         |         |

| N/A  | VCCAUX          | A8         |         |         |

| N/A  | VCCAUX          | AP2        |         |         |

| N/A  | VCCAUX          | A2         |         |         |

| N/A  | VCCAUX          | AN1        |         |         |

| N/A  | VCCAUX          | AG1        |         |         |

| N/A  | VCCAUX          | U1         |         |         |

| N/A  | VCCAUX          | H1         |         |         |

| N/A  | VCCAUX          | B1         |         |         |

| N/A  | GND             | AK34       |         |         |

| N/A  | GND             | AF34       |         |         |

| N/A  | GND             | AB34       |         |         |

| N/A  | GND             | W34        |         |         |

| N/A  | GND             | V34        |         |         |

| N/A  | GND             | T34        |         |         |

| N/A  | GND             | N34        |         |         |

| N/A  | GND             | J34        |         |         |

| N/A  | GND             | E34        |         |         |

| N/A  | GND             | AN33       |         |         |

| N/A  | GND             | B33        |         |         |

| N/A  | GND             | AM32       |         |         |

| N/A  | GND             | C32        |         |         |

| N/A  | GND             | AP30       |         |         |

| N/A  | GND             | AK30       |         |         |

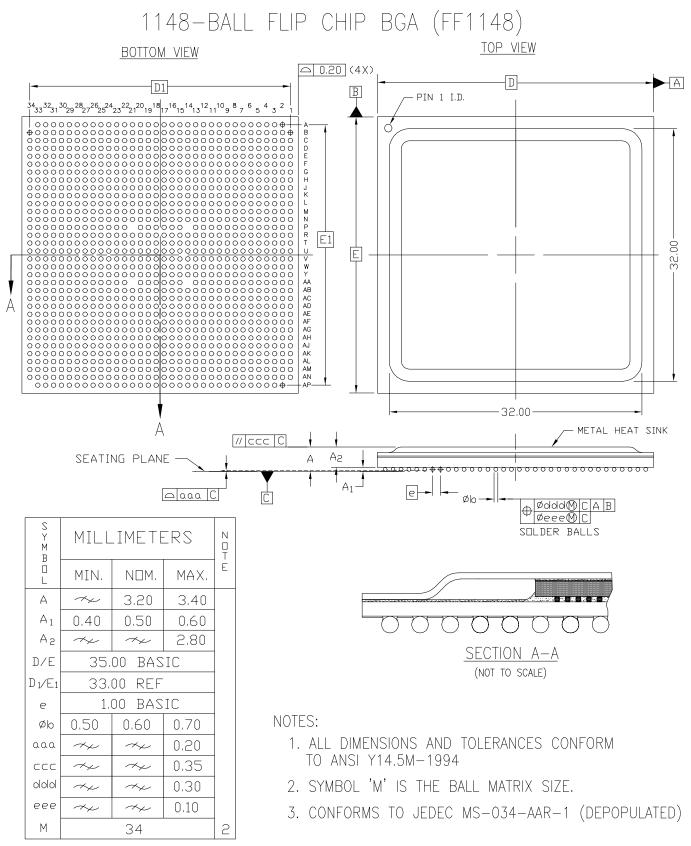

# FF1148 Flip-Chip Fine-Pitch BGA Package Specifications (1.00mm pitch)

### Figure 7: FF1148 Flip-Chip Fine-Pitch BGA Package Specifications

### Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                  | Pin    | No Connects |         |

|------|------------------|--------|-------------|---------|

| Bank | Pin Description  | Number | XC2VP50     | XC2VP70 |

| 1    | IO_L64N_1        | E18    |             |         |

| 1    | IO_L64P_1        | D18    |             |         |

| 1    | IO_L60N_1        | G18    |             |         |

| 1    | IO_L60P_1        | F18    |             |         |

| 1    | IO_L59N_1        | L18    |             |         |

| 1    | IO_L59P_1        | K18    |             |         |

| 1    | IO_L58N_1        | J18    |             |         |

| 1    | IO_L58P_1        | H18    |             |         |

| 1    | IO_L57N_1/VREF_1 | D17    |             |         |

| 1    | IO_L57P_1        | C17    |             |         |

| 1    | IO_L56N_1        | N18    |             |         |

| 1    | IO_L56P_1        | M18    |             |         |

| 1    | IO_L55N_1        | E17    |             |         |

| 1    | IO_L55P_1        | E16    |             |         |

| 1    | IO_L54N_1        | G17    |             |         |

| 1    | IO_L54P_1        | F16    |             |         |

| 1    | IO_L53_1/No_Pair | J17    |             |         |

| 1    | IO_L50_1/No_Pair | H17    |             |         |

| 1    | IO_L49N_1        | J16    |             |         |

| 1    | IO_L49P_1        | H16    |             |         |

| 1    | IO_L48N_1        | D15    |             |         |

| 1    | IO_L48P_1        | C15    |             |         |

| 1    | IO_L47N_1        | L17    |             |         |

| 1    | IO_L47P_1        | K16    |             |         |

| 1    | IO_L46N_1        | F15    |             |         |

| 1    | IO_L46P_1        | E15    |             |         |

| 1    | IO_L45N_1/VREF_1 | H15    |             |         |

| 1    | IO_L45P_1        | G15    |             |         |

| 1    | IO_L44N_1        | N17    |             |         |

| 1    | IO_L44P_1        | M17    |             |         |

| 1    | IO_L43N_1        | D14    |             |         |

| 1    | IO_L43P_1        | C14    |             |         |

| 1    | IO_L39N_1        | F14    |             |         |

| 1    | IO_L39P_1        | E14    |             |         |

| 1    | IO_L38N_1        | M16    |             |         |

| 1    | IO_L38P_1        | M15    |             |         |

| 1    | IO_L37N_1        | H14    |             |         |

| 1    | <br>IO_L37P_1    | G14    |             |         |

### Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                  | Pin    | No Connects |         |

|------|------------------|--------|-------------|---------|

| Bank | Pin Description  | Number | XC2VP50     | XC2VP70 |

| 6    | IO_L53P_6        | AB30   |             |         |

| 6    | IO_L53N_6        | AB31   |             |         |

| 6    | IO_L54P_6        | AC38   |             |         |

| 6    | IO_L54N_6        | AC39   |             |         |

| 6    | IO_L55P_6        | AC34   |             |         |

| 6    | IO_L55N_6        | AC35   |             |         |

| 6    | IO_L56P_6        | AA28   |             |         |

| 6    | IO_L56N_6        | AA29   |             |         |

| 6    | IO_L57P_6        | AB38   |             |         |

| 6    | IO_L57N_6/VREF_6 | AB39   |             |         |

| 6    | IO_L58P_6        | AB36   |             |         |

| 6    | IO_L58N_6        | AB37   |             |         |

| 6    | IO_L59P_6        | AA30   |             |         |

| 6    | IO_L59N_6        | AA31   |             |         |

| 6    | IO_L60P_6        | AB34   |             |         |

| 6    | IO_L60N_6        | AB35   |             |         |

| 6    | IO_L85P_6        | AB32   |             |         |

| 6    | IO_L85N_6        | AB33   |             |         |

| 6    | IO_L86P_6        | AA27   |             |         |

| 6    | IO_L86N_6        | Y27    |             |         |

| 6    | IO_L87P_6        | AA36   |             |         |

| 6    | IO_L87N_6/VREF_6 | AA37   |             |         |

| 6    | IO_L88P_6        | AA34   |             |         |

| 6    | IO_L88N_6        | AA35   |             |         |

| 6    | IO_L89P_6        | Y28    |             |         |

| 6    | IO_L89N_6        | Y29    |             |         |

| 6    | IO_L90P_6        | AA32   |             |         |

| 6    | IO_L90N_6        | AA33   |             |         |

|      |                  |        |             |         |

| 7    | IO_L90P_7        | Y36    |             |         |

| 7    | IO_L90N_7        | Y37    |             |         |

| 7    | IO_L89P_7        | Y31    |             |         |

| 7    | IO_L89N_7        | W31    |             |         |

| 7    | IO_L88P_7        | Y32    |             |         |

| 7    | IO_L88N_7/VREF_7 | Y33    |             |         |

| 7    | IO_L87P_7        | W36    |             |         |

| 7    | IO_L87N_7        | W37    |             |         |

| 7    | IO_L86P_7        | W27    |             |         |

### Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                 | Pin    | No Connects |         |

|------|-----------------|--------|-------------|---------|

| Bank | Pin Description | Number | XC2VP50     | XC2VP70 |

| 2    | VCCO_2          | F8     |             |         |

| 2    | VCCO_2          | U7     |             |         |

| 2    | VCCO_2          | Y5     |             |         |

| 2    | VCCO_2          | N4     |             |         |

| 2    | VCCO_2          | J4     |             |         |

| 2    | VCCO_2          | E4     |             |         |

| 2    | VCCO_2          | U3     |             |         |

| 2    | VCCO_2          | E1     |             |         |

| 1    | VCCO_1          | N14    |             |         |

| 1    | VCCO_1          | K13    |             |         |

| 1    | VCCO_1          | F13    |             |         |

| 1    | VCCO_1          | P19    |             |         |

| 1    | VCCO_1          | P18    |             |         |

| 1    | VCCO_1          | P17    |             |         |

| 1    | VCCO_1          | K17    |             |         |

| 1    | VCCO_1          | F17    |             |         |

| 1    | VCCO_1          | P16    |             |         |

| 1    | VCCO_1          | N16    |             |         |

| 1    | VCCO_1          | P15    |             |         |

| 1    | VCCO_1          | N15    |             |         |

| 0    | VCCO_0          | K27    |             |         |

| 0    | VCCO_0          | F27    |             |         |

| 0    | VCCO_0          | N26    |             |         |

| 0    | VCCO_0          | P25    |             |         |

| 0    | VCCO_0          | N25    |             |         |

| 0    | VCCO_0          | P24    |             |         |

| 0    | VCCO_0          | N24    |             |         |

| 0    | VCCO_0          | P23    |             |         |

| 0    | VCCO_0          | K23    |             |         |

| 0    | VCCO_0          | F23    |             |         |

| 0    | VCCO_0          | P22    |             |         |

| 0    | VCCO_0          | P21    |             |         |

|      |                 |        |             | ·       |

| N/A  | CCLK            | AJ10   |             |         |

| N/A  | PROG_B          | D32    |             |         |

| N/A  | DONE            | AJ11   |             |         |

| N/A  | МО              | AP31   |             |         |

| N/A  | M1              | AJ30   |             |         |

### Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

| Bank | Pin Description       |                            |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

|      | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 3    | IO_L35N_3             |                            | AH11       |                      |          |

| 3    | IO_L35P_3             |                            | AH12       |                      |          |

| 3    | IO_L34N_3             |                            | AH5        |                      |          |

| 3    | IO_L34P_3             |                            | AH6        |                      |          |

| 3    | IO_L33N_3/VREF_3      |                            | AH9        |                      |          |

| 3    | IO_L33P_3             |                            | AH10       |                      |          |

| 3    | IO_L32N_3             |                            | AJ11       |                      |          |

| 3    | IO_L32P_3             |                            | AJ12       |                      |          |

| 3    | IO_L31N_3             |                            | AJ1        |                      |          |

| 3    | IO_L31P_3             |                            | AJ2        |                      |          |

| 3    | IO_L30N_3             |                            | AJ5        |                      |          |

| 3    | IO_L30P_3             |                            | AJ6        |                      |          |

| 3    | IO_L29N_3             |                            | AJ9        |                      |          |

| 3    | IO_L29P_3             |                            | AJ10       |                      |          |

| 3    | IO_L28N_3             |                            | AJ7        |                      |          |

| 3    | IO_L28P_3             |                            | AJ8        |                      |          |

| 3    | IO_L27N_3/VREF_3      |                            | AK1        |                      |          |

| 3    | IO_L27P_3             |                            | AK2        |                      |          |

| 3    | IO_L26N_3             |                            | AK11       |                      |          |

| 3    | IO_L26P_3             |                            | AK12       |                      |          |

| 3    | IO_L25N_3             |                            | AK3        |                      |          |

| 3    | IO_L25P_3             |                            | AK4        |                      |          |

| 3    | IO_L24N_3             |                            | AK5        |                      |          |

| 3    | IO_L24P_3             |                            | AK6        |                      |          |

| 3    | IO_L23N_3             |                            | AK9        |                      |          |

| 3    | IO_L23P_3             |                            | AK10       |                      |          |

| 3    | IO_L22N_3             |                            | AK7        |                      |          |

| 3    | IO_L22P_3             |                            | AK8        |                      |          |

| 3    | IO_L21N_3/VREF_3      |                            | AL2        |                      |          |

| 3    | IO_L21P_3             |                            | AL3        |                      |          |

| 3    | IO_L20N_3             |                            | AL11       |                      |          |

| 3    | IO_L20P_3             |                            | AL12       |                      |          |

| 3    | IO_L19N_3             |                            | AL4        |                      |          |

| 3    | IO_L19P_3             |                            | AL5        |                      |          |

| 3    | IO_L18N_3             |                            | AL7        |                      |          |

| 3    | <br>IO_L18P_3         |                            | AL8        |                      |          |

### Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

| Bank | Pin Description       |                            |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

|      | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| N/A  | VCCINT                |                            | AF16       |                      |          |

| N/A  | VCCINT                |                            | AG27       |                      |          |

| N/A  | VCCINT                |                            | AG26       |                      |          |

| N/A  | VCCINT                |                            | AG25       |                      |          |

| N/A  | VCCINT                |                            | AG24       |                      |          |

| N/A  | VCCINT                |                            | AG23       |                      |          |

| N/A  | VCCINT                |                            | AG22       |                      |          |

| N/A  | VCCINT                |                            | AG21       |                      |          |

| N/A  | VCCINT                |                            | AG20       |                      |          |

| N/A  | VCCINT                |                            | AG19       |                      |          |

| N/A  | VCCINT                |                            | AG18       |                      |          |

| N/A  | VCCINT                |                            | AG17       |                      |          |

| N/A  | VCCINT                |                            | AG16       |                      |          |

| N/A  | VCCINT                |                            | AH28       |                      |          |

| N/A  | VCCINT                |                            | AH27       |                      |          |

| N/A  | VCCINT                |                            | AH26       |                      |          |

| N/A  | VCCINT                |                            | AH17       |                      |          |

| N/A  | VCCINT                |                            | AH16       |                      |          |

| N/A  | VCCINT                |                            | AH15       |                      |          |

| N/A  | VCCINT                |                            | AJ29       |                      |          |

| N/A  | VCCINT                |                            | AJ28       |                      |          |

| N/A  | VCCINT                |                            | AJ27       |                      |          |

| N/A  | VCCINT                |                            | AJ16       |                      |          |

| N/A  | VCCINT                |                            | AJ15       |                      |          |

| N/A  | VCCINT                |                            | AJ14       |                      |          |

| N/A  | VCCINT                |                            | AK30       |                      |          |

| N/A  | VCCINT                |                            | AK13       |                      |          |

| N/A  | VCCINT                |                            | AA27       |                      |          |

| N/A  | VCCINT                |                            | AA16       |                      |          |

| N/A  | VCCINT                |                            | Y27        |                      |          |

| N/A  | VCCINT                |                            | Y16        |                      |          |

| N/A  | VCCINT                |                            | W27        |                      |          |

| N/A  | VCCINT                |                            | W16        |                      |          |

| N/A  | VCCINT                |                            | V27        |                      |          |

| N/A  | VCCINT                |                            | V16        |                      |          |

| N/A  | VCCINT                |                            | U27        |                      |          |

### Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

| Bank | Pin Description       |                            |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

|      | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| N/A  | GND                   |                            | AE19       |                      |          |

| N/A  | GND                   |                            | AE18       |                      |          |

| N/A  | GND                   |                            | AE17       |                      |          |

| N/A  | GND                   |                            | AE9        |                      |          |

| N/A  | GND                   |                            | AE6        |                      |          |

| N/A  | GND                   |                            | AF25       |                      |          |

| N/A  | GND                   |                            | AF24       |                      |          |

| N/A  | GND                   |                            | AF23       |                      |          |

| N/A  | GND                   |                            | AF22       |                      |          |

| N/A  | GND                   |                            | AF21       |                      |          |

| N/A  | GND                   |                            | AF20       |                      |          |

| N/A  | GND                   |                            | AF19       |                      |          |

| N/A  | GND                   |                            | AF18       |                      |          |

| N/A  | GND                   |                            | AG42       |                      |          |

| N/A  | GND                   |                            | AG1        |                      |          |

| N/A  | GND                   |                            | AH39       |                      |          |

| N/A  | GND                   |                            | AH36       |                      |          |

| N/A  | GND                   |                            | AH7        |                      |          |

| N/A  | GND                   |                            | AH4        |                      |          |

| N/A  | GND                   |                            | AL42       |                      |          |

| N/A  | GND                   |                            | AL1        |                      |          |

| N/A  | GND                   |                            | AM22       |                      |          |

| N/A  | GND                   |                            | AM21       |                      |          |

| N/A  | GND                   |                            | AN39       |                      |          |

| N/A  | GND                   |                            | AN4        |                      |          |

| N/A  | GND                   |                            | AP34       |                      |          |

| N/A  | GND                   |                            | AP9        |                      |          |

| N/A  | GND                   |                            | AR42       |                      |          |

| N/A  | GND                   |                            | AR35       |                      |          |

| N/A  | GND                   |                            | AR22       |                      |          |

| N/A  | GND                   |                            | AR21       |                      |          |

| N/A  | GND                   |                            | AR8        |                      |          |

| N/A  | GND                   |                            | AR1        |                      |          |

| N/A  | GND                   |                            | AT36       |                      |          |

| N/A  | GND                   |                            | AT7        |                      |          |

| N/A  | GND                   |                            | AU37       |                      |          |

### Table 14: FF1696 — XC2VP100

|      |                 |            | No Connects |

|------|-----------------|------------|-------------|

| Bank | Pin Description | Pin Number | XC2VP100    |

| N/A  | VCCAUX          | A2         |             |

| N/A  | VCCAUX          | BA1        |             |

| N/A  | VCCAUX          | AY1        |             |

| N/A  | VCCAUX          | AL1        |             |

| N/A  | VCCAUX          | AB1        |             |

| N/A  | VCCAUX          | AA1        |             |

| N/A  | VCCAUX          | M1         |             |

| N/A  | VCCAUX          | C1         |             |

| N/A  | VCCAUX          | B1         |             |

| N/A  | GND             | AV42       |             |

| N/A  | GND             | AP42       |             |

| N/A  | GND             | AK42       |             |

| N/A  | GND             | AF42       |             |

| N/A  | GND             | AC42       |             |

| N/A  | GND             | Y42        |             |

| N/A  | GND             | U42        |             |

| N/A  | GND             | N42        |             |

| N/A  | GND             | J42        |             |

| N/A  | GND             | E42        |             |

| N/A  | GND             | BA41       |             |

| N/A  | GND             | AY41       |             |

| N/A  | GND             | C41        |             |

| N/A  | GND             | B41        |             |

| N/A  | GND             | BA40       |             |

| N/A  | GND             | B40        |             |

| N/A  | GND             | BB38       |             |

| N/A  | GND             | AV38       |             |

| N/A  | GND             | AP38       |             |

| N/A  | GND             | AK38       |             |

| N/A  | GND             | AF38       |             |

| N/A  | GND             | AC38       |             |

| N/A  | GND             | Y38        |             |

| N/A  | GND             | U38        |             |

| N/A  | GND             | N38        |             |

| N/A  | GND             | J38        |             |

| N/A  | GND             | E38        |             |

| N/A  | GND             | A38        |             |