Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 2320                                                        |

| Number of Logic Elements/Cells | 20880                                                       |

| Total RAM Bits                 | 1622016                                                     |

| Number of I/O                  | 404                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 676-BGA                                                     |

| Supplier Device Package        | 676-FBGA (27x27)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2vp20-7fg676c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Product Not Recommended For New Designs**

Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Introduction and Overview

- HyperTransport (LDT) I/O with current driver buffers

- Built-in DDR input and output registers

- Proprietary high-performance SelectLink technology for communications between Xilinx devices

- High-bandwidth data path

- Double Data Rate (DDR) link

- Web-based HDL generation methodology

- SRAM-Based In-System Configuration

- Fast SelectMAP™ configuration

- Triple Data Encryption Standard (DES) security option (bitstream encryption)

- IEEE 1532 support

- Partial reconfiguration

- Unlimited reprogrammability

- Readback capability

- Supported by Xilinx Foundation™ and Alliance Series™ Development Systems

- Integrated VHDL and Verilog design flows

- ChipScope™ Integrated Logic Analyzer

- 0.13 µm Nine-Layer Copper Process with 90 nm **High-Speed Transistors**

- 1.5V (V<sub>CCINT</sub>) core power supply, dedicated 2.5V V<sub>CCAUX</sub> auxiliary and V<sub>CCO</sub> I/O power supplies

- IEEE 1149.1 Compatible Boundary-Scan Logic Support

- Flip-Chip and Wire-Bond Ball Grid Array (BGA) Packages in Standard 1.00 mm Pitch.

- Wire-Bond BGA Devices Available in Pb-Free Packaging (www.xilinx.com/pbfree)

- Each Device 100% Factory Tested

### **General Description**

The Virtex-II Pro and Virtex-II Pro X families contain platform FPGAs for designs that are based on IP cores and customized modules. The family incorporates multi-gigabit transceivers and PowerPC CPU blocks in Virtex-II Pro Series FPGA architecture. It empowers complete solutions for telecommunication, wireless, networking, video, and DSP applications.

The leading-edge 0.13 µm CMOS nine-layer copper process and Virtex-II Pro architecture are optimized for high performance designs in a wide range of densities. Combining a wide variety of flexible features and IP cores, the Virtex-II Pro family enhances programmable logic design capabilities and is a powerful alternative to mask-programmed gate arrays.

### **Architecture**

### **Array Overview**

Virtex-II Pro and Virtex-II Pro X devices are user-programmable gate arrays with various configurable elements and embedded blocks optimized for high-density and high-performance system designs. Virtex-II Pro devices implement the following functionality:

- Embedded high-speed serial transceivers enable data bit rate up to 3.125 Gb/s per channel (RocketlO) or 6.25 Gb/s (RocketIO X).

- Embedded IBM PowerPC 405 RISC processor blocks provide performance up to 400 MHz.

- SelectIO-Ultra blocks provide the interface between package pins and the internal configurable logic. Most popular and leading-edge I/O standards are supported by the programmable IOBs.

- Configurable Logic Blocks (CLBs) provide functional elements for combinatorial and synchronous logic, including basic storage elements. BUFTs (3-state buffers) associated with each CLB element drive dedicated segmentable horizontal routing resources.

- Block SelectRAM+ memory modules provide large 18 Kb storage elements of True Dual-Port RAM.

- Embedded multiplier blocks are 18-bit x 18-bit dedicated multipliers.

- Digital Clock Manager (DCM) blocks provide self-calibrating, fully digital solutions for clock distribution delay compensation, clock multiplication and division, and coarse- and fine-grained clock phase shifting.

A new generation of programmable routing resources called Active Interconnect Technology interconnects all these elements. The general routing matrix (GRM) is an array of routing switches. Each programmable element is tied to a switch matrix, allowing multiple connections to the general routing matrix. The overall programmable interconnection is hierarchical and supports high-speed designs.

programmable elements, including the routing resources, are controlled by values stored in static memory cells. These values are loaded in the memory cells during configuration and can be reloaded to change the functions of the programmable elements.

### **Features**

This section briefly describes Virtex-II Pro / Virtex-II Pro X features. For more details, refer to Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description.

#### RocketIO / RocketIO X MGT Cores

The RocketIO and RocketIO X Multi-Gigabit Transceivers are flexible parallel-to-serial and serial-to-parallel embedded transceiver cores used for high-bandwidth interconnection between buses, backplanes, or other subsystems.

Multiple user instantiations in an FPGA are possible, providing up to 100 Gb/s (RocketIO) or 170 Gb/s (RocketIO X) of full-duplex raw data transfer. Each channel can be operated at a maximum data transfer rate of 3.125 Gb/s (RocketIO) or 6.25 Gb/s (RocketIO X).

cation is given at the receiver interface. The realignment indicator is a distinct output.

The transceiver continuously monitors the data for the presence of the 10-bit character(s). Upon each occurrence of a 10-bit character, the data is checked for word alignment. If comma detect is disabled, the data is not aligned to any particular pattern. The programmable option allows a user to align data on comma+, comma-, both, or a unique user-defined and programmed sequence.

Comma detection has been expanded beyond 10-bit symbol detection and alignment to include 8-bit symbol detection and alignment for 16-, 20-, 32-, and 40-bit paths. The ability to detect symbols, and then either align to 1-word, 2-word, or 4-word boundaries is included. The RXSLIDE input allows the user to "slide" or "slip" the alignment by one bit in each 16-, 20-, 32- and 40-bit mode at any time for SONET applications. Comma detection can be bypassed when needed.

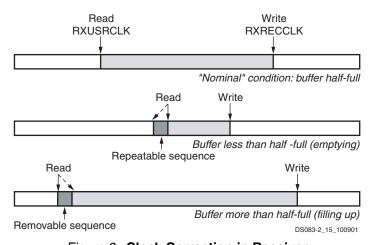

#### **Clock Correction**

RXRECCLK (the recovered clock) reflects the data rate of the incoming data. RXUSRCLK defines the rate at which the FPGA fabric consumes the data. Ideally, these rates are identical. However, since the clocks typically have different sources, one of the clocks will be faster than the other. The receiver buffer accommodates this difference between the clock rates. See Figure 6.

Figure 6: Clock Correction in Receiver

Nominally, the buffer is always half full. This is shown in the top buffer, Figure 6, where the shaded area represents buffered data not vet read. Received data is inserted via the write pointer under control of RXRECCLK. The FPGA fabric reads data via the read pointer under control of RXUS-RCLK. The half full/half empty condition of the buffer gives a cushion for the differing clock rates. This operation continues indefinitely, regardless of whether or not "meaningful" data is being received. When there is no meaningful data to be received, the incoming data will consist of IDLE characters or other padding.

If RXUSRCLK is faster than RXRECCLK, the buffer becomes more empty over time. The clock correction logic corrects for this by decrementing the read pointer to reread a repeatable byte sequence. This is shown in the middle buffer, Figure 6, where the solid read pointer decrements to the value represented by the dashed pointer. By decrementing the read pointer instead of incrementing it in the usual fashion, the buffer is partially refilled. The transceiver design will repeat a single repeatable byte sequence when necessary to refill a buffer. If the byte sequence length is greater than one, and if attribute CLK\_COR\_REPEAT\_WAIT is 0, then the transceiver may repeat the same sequence multiple times until the buffer is refilled to the desired extent.

Similarly, if RXUSRCLK is slower than RXRECCLK, the buffer will fill up over time. The clock correction logic corrects for this by incrementing the read pointer to skip over a removable byte sequence that need not appear in the final FPGA fabric byte stream. This is shown in the bottom buffer, Figure 6, where the solid read pointer increments to the value represented by the dashed pointer. This accelerates the emptying of the buffer, preventing its overflow. The transceiver design will skip a single byte sequence when necessary to partially empty a buffer. If attribute CLK\_COR\_REPEAT\_WAIT is 0, the transceiver may also skip two consecutive removable byte sequences in one step to further empty the buffer when necessary.

These operations require the clock correction logic to recognize a byte sequence that can be freely repeated or omitted in the incoming data stream. This sequence is generally an IDLE sequence, or other sequence comprised of special values that occur in the gaps separating packets of meaningful data. These gaps are required to occur sufficiently often to facilitate the timely execution of clock correction.

### **Channel Bonding**

Some gigabit I/O standards such as Infiniband specify the use of multiple transceivers in parallel for even higher data rates. Words of data are split into bytes, with each byte sent over a separate channel (transceiver). See Figure 7.

The top half of the figure shows the transmission of words split across four transceivers (channels or lanes). PPPP, QQQQ, RRRR, SSSS, and TTTT represent words sent over the four channels.

The bottom-left portion of Figure 7 shows the initial situation in the FPGA's receivers at the other end of the four channels. Due to variations in transmission delay-especially if the channels are routed through repeaters—the FPGA fabric might not correctly assemble the bytes into complete words. The bottom-left illustration shows the incorrect assembly of data words PQPP, QRQQ, RSRR, and so forth.

To support correction of this misalignment, the data stream includes special byte sequences that define corresponding points in the several channels. In the bottom half of Figure 7, the shaded "P" bytes represent these special characters. Each receiver recognizes the "P" channel bondVirtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description

Table 5: Clock Ratios for Various Data Widths

| Fabric Data Width | Frequency Ratio of USRCLK:USRCLK2 |

|-------------------|-----------------------------------|

| 1-byte            | 1:2 <sup>(1)</sup>                |

| 2-byte            | 1:1                               |

| 4-byte            | 2:1 <sup>(1)</sup>                |

#### Notes:

#### FPGA Transmit Interface

The FPGA can send either one, two, or four characters of data to the transmitter. Each character can be either 8 bits or 10 bits wide. If 8-bit data is applied, the additional inputs become control signals for the 8B/10B encoder. When the 8B/10B encoder is bypassed, the 10-bit character order is generated as follows:

TXCHARDISPMODE[0] (first bit transmitted)

TXCHARDISPVAL[0]

TXDATA[7:0] (last bit transmitted is TXDATA[0])

### **Disparity Control**

The 8B/10B encoder is initialized with a negative running disparity. Unique control allows forcing the current running disparity state.

TXRUNDISP signals its current running disparity. This may be useful in those cases where there is a need to manipulate the initial running disparity value.

Bits TXCHARDISPMODE and TXCHARDISPVAL control the generation of running disparity before each byte.

For example, the transceiver can generate the sequence

K28.5+ K28.5+ K28.5- K28.5or K28.5- K28.5- K28.5+ K28.5+

by specifying inverted running disparity for the second and fourth bytes.

#### Transmit FIFO

Proper operation of the circuit is only possible if the FPGA clock (TXUSRCLK) is frequency-locked to the reference clock (REFCLK). Phase variations up to one clock cycle are allowable. The FIFO has a depth of four. Overflow or underflow conditions are detected and signaled at the interface. Bypassing of this FIFO is programmable.

### 8B/10B Encoder

Note: In the RocketIO transceiver, the most-significant byte is sent first; in the RocketIO X transceiver, the least-significant byte is sent first.

A bypassable 8B/10B encoder is included. The encoder uses the same 256 data characters and 12 control characters used by Gigabit Ethernet, Fibre Channel, and InfiniBand.

The encoder accepts 8 bits of data along with a K-character signal for a total of 9 bits per character applied, and generates a 10 bit character for transmission. If the K-character signal is High, the data is encoded into one of the twelve possible K-characters available in the 8B/10B code. If the K-character input is Low, the 8 bits are encoded as standard data. If the K-character input is High, and a user applies other than one of the twelve possible combinations, TXKERR indicates the error.

#### 8B/10B Decoder

Note: In the RocketIO transceiver, the most-significant byte is sent first; in the RocketIO X transceiver, the least-significant byte is sent first.

An optional 8B/10B decoder is included. A programmable option allows the decoder to be bypassed. When the 8B/10B decoder is bypassed, the 10-bit character order is, for example,

RXCHARISK[0] (first bit received)

RXRUNDISP[0]

RXDATA[7:0] (last bit received is RXDATA[0])

The decoder uses the same table that is used for Gigabit Ethernet, Fibre Channel, and InfiniBand. In addition to decoding all data and K-characters, the decoder has several extra features. The decoder separately detects both "disparity errors" and "out-of-band" errors. A disparity error is the reception of 10-bit character that exists within the 8B/10B table but has an incorrect disparity. An out-of-band error is the reception of a 10-bit character that does not exist within the 8B/10B table. It is possible to obtain an out-of-band error without having a disparity error. The proper disparity is always computed for both legal and illegal characters. The current running disparity is available at the RXRUNDISP signal.

The 8B/10B decoder performs a unique operation if out-of-band data is detected. If out-of-band data is detected, the decoder signals the error and passes the illegal 10-bits through and places them on the outputs. This can be used for debugging purposes if desired.

The decoder also signals the reception of one of the 12 valid K-characters. In addition, a programmable comma detect is included. The comma detect signal registers a comma on the receipt of any comma+, comma-, or both. Since the comma is defined as a 7-bit character, this includes several out-of-band characters. Another option allows the decoder to detect only the three defined commas (K28.1, K28.5, and K28.7) as comma+, comma-, or both. In total, there are six possible options, three for valid commas and three for "any comma."

Note that all bytes (1, 2, or 4) at the RX FPGA interface each have their own individual 8B/10B indicators (K-character, disparity error, out-of-band error, current running disparity, and comma detect).

Each edge of slower clock must align with falling edge of faster clock.

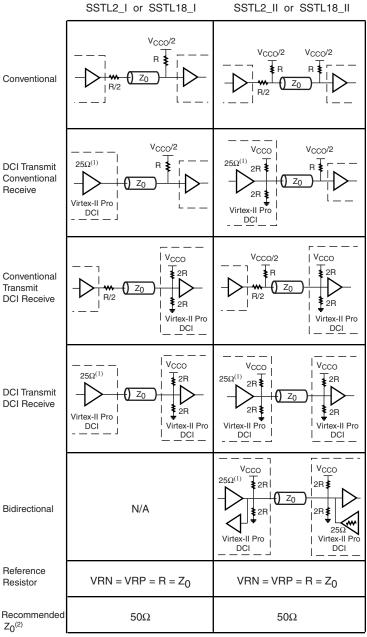

Figure 29 provides examples illustrating the use of the SSTL2\_I\_DCI, SSTL2\_II\_DCI, SSTL18\_I\_DCI, and SSTL18\_II\_DCI I/O standards. For a complete list, see the *Virtex-II Pro Platform FPGA User Guide*.

Notes:

DS083-2\_65b\_011603

Figure 29: SSTL DCI Usage Examples

<sup>1.</sup> The SSTL-compatible  $25\Omega$  series resistor is accounted for in the DCI buffer, and it is not DCI controlled.

<sup>2.</sup>  $Z_0$  is the recommended PCB trace impedance.

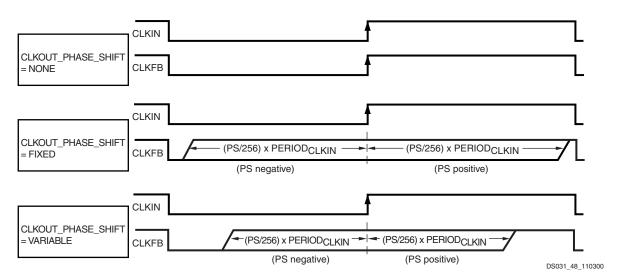

Figure 63: Fine-Phase Shifting Effects

Two separate components of the phase shift range must be understood:

- PHASE\_SHIFT attribute range

- FINE\_SHIFT\_RANGE DCM timing parameter range

The PHASE\_SHIFT attribute is the numerator in the following equation:

Phase Shift (ns) = (PHASE\_SHIFT/256) \* PERIOD<sub>CLKIN</sub>

The full range of this attribute is always -255 to +255, but its practical range varies with CLKIN frequency, as constrained by the FINE\_SHIFT\_RANGE component, which represents the total delay achievable by the phase shift delay line. Total delay is a function of the number of delay taps used in the circuit. Across process, voltage, and temperature, this absolute range is guaranteed to be as specified under **DCM Timing Parameters** in Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics.

Absolute range (fixed mode) = ± FINE\_SHIFT\_RANGE

Absolute range (variable mode) =  $\pm$  FINE\_SHIFT\_RANGE/2

The reason for the difference between fixed and variable modes is as follows. For variable mode to allow symmetric, dynamic sweeps from -255/256 to +255/256, the DCM sets the "zero phase skew" point as the middle of the delay line, thus dividing the total delay line range in half. In fixed mode,

since the PHASE\_SHIFT value never changes after configuration, the entire delay line is available for insertion into either the CLKIN or CLKFB path (to create either positive or negative skew).

Taking both of these components into consideration, the following are some usage examples:

- If PERIOD<sub>CLKIN</sub> = 2 \* FINE\_SHIFT\_RANGE, then PHASE\_SHIFT in fixed mode is limited to ± 128, and in variable mode it is limited to ± 64.

- If PERIOD<sub>CLKIN</sub> = FINE\_SHIFT\_RANGE, then PHASE\_SHIFT in fixed mode is limited to ± 255, and in variable mode it is limited to ± 128.

- If  $PERIOD_{CLKIN} \le 0.5$  \* FINE\_SHIFT\_RANGE, then PHASE\_SHIFT is limited to  $\pm 255$  in either mode.

### Operating Modes

The frequency ranges of DCM input and output clocks depend on the operating mode specified, either low-frequency mode or high-frequency mode, according to Table 30. For actual values, see Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics. The CLK2X, CLK2X180, CLK90, and CLK270 outputs are not available in high-frequency mode.

High or low-frequency mode is selected by an attribute.

Table 30: DCM Frequency Ranges

|                 | Low-Frequency Mode |                   | High-Frequency Mode |                   |  |

|-----------------|--------------------|-------------------|---------------------|-------------------|--|

| Output Clock    | CLKIN Input        | CLK Output        | CLKIN Input         | CLK Output        |  |

| CLK0, CLK180    | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_1X_LF | CLKIN_FREQ_DLL_HF   | CLKOUT_FREQ_1X_HF |  |

| CLK90, CLK270   | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_1X_LF | NA                  | NA                |  |

| CLK2X, CLK2X180 | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_2X_LF | NA                  | NA                |  |

| CLKDV           | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_DV_LF | CLKIN_FREQ_DLL_HF   | CLKOUT_FREQ_DV_HF |  |

| CLKFX, CLKFX180 | CLKIN_FREQ_FX_LF   | CLKOUT_FREQ_FX_LF | CLKIN_FREQ_FX_HF    | CLKOUT_FREQ_FX_HF |  |

### Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics

### **Input Clock Tolerances**

Table 58: Input Clock Tolerances

|                                |                             |                    |       |      | Speed | Grade |       |      |          |

|--------------------------------|-----------------------------|--------------------|-------|------|-------|-------|-------|------|----------|

|                                |                             | Constraints        | _     | 7    | _     | 6     | _     | 5    |          |

| Description                    | Symbol                      | F <sub>CLKIN</sub> | Min   | Max  | Min   | Max   | Min   | Max  | Units    |

| Input Clock Low/High Puls      | e Width                     |                    |       |      |       |       |       |      |          |

| PSCLK                          | PSCLK_PULSE                 | < 1MHz             | 25.00 |      | 25.00 |       | 25.00 |      | ns       |

|                                |                             | 1 – 10 MHz         | 25.00 |      | 25.00 |       | 25.00 |      | ns       |

|                                |                             | 10 – 25 MHz        | 10.00 |      | 10.00 |       | 10.00 |      | ns       |

|                                |                             | 25 – 50 MHz        | 5.00  |      | 5.00  |       | 5.00  |      | ns       |

|                                |                             | 50 – 100 MHz       | 3.00  |      | 3.00  |       | 3.00  |      | ns       |

|                                |                             | 100 – 150 MHz      | 2.40  |      | 2.40  |       | 2.40  |      | ns       |

| PSCLK and CLKIN <sup>(3)</sup> | PSCLK_PULSE and CLKIN_PULSE | 150 – 200 MHz      | 2.00  |      | 2.00  |       | 2.00  |      | ns       |

|                                |                             | 200 – 250 MHz      | 1.80  |      | 1.80  |       | 1.80  |      | ns       |

|                                |                             | 250 – 300 MHz      | 1.50  |      | 1.50  |       | 1.50  |      | ns       |

|                                |                             | 300 – 350 MHz      | 1.30  |      | 1.30  |       | 1.30  |      | ns       |

|                                |                             | 350 – 400 MHz      | 1.15  |      | 1.15  |       | 1.15  |      | ns       |

|                                |                             | > 400 MHz          | 1.05  |      | 1.05  |       | 1.05  |      | ns       |

| Input Clock Cycle-Cycle Jit    | tter (Low Frequency Mode)   |                    |       |      |       |       | 1     |      |          |

| CLKIN (using DLL outputs)(1)   | CLKIN_CYC_JITT_DLL_LF       |                    |       | ±300 |       | ±300  |       | ±300 | ps       |

| CLKIN (using CLKFX outputs)(2) | CLKIN_CYC_JITT_FX_LF        |                    |       | ±300 |       | ±300  |       | ±300 | ps       |

| Input Clock Cycle-Cycle Jit    | ter (High Frequency Mode    | )                  | 1     | I .  | I .   |       | I     | I    |          |

| CLKIN (using DLL outputs)(1)   | CLKIN_CYC_JITT_DLL_HF       |                    |       | ±150 |       | ±150  |       | ±150 | ps       |

| CLKIN (using CLKFX outputs)(2) | CLKIN_CYC_JITT_FX_HF        |                    |       | ±150 |       | ±150  |       | ±150 | ps       |

| Input Clock Period Jitter (L   | ow Frequency Mode)          | 1                  | 1     | I.   | I.    |       | I     | I    |          |

| CLKIN (using DLL outputs)(1)   | CLKIN_PER_JITT_DLL_LF       |                    |       | ±1   |       | ±1    |       | ±1   | ns       |

| CLKIN (using CLKFX outputs)(2) | CLKIN_PER_JITT_FX_LF        |                    |       | ±1   |       | ±1    |       | ±1   | ns       |

| Input Clock Period Jitter (H   | ligh Frequency Mode)        | 1                  | 1     | ı    | ı     |       | ı     | ı    |          |

| CLKIN (using DLL outputs)(1)   | CLKIN_PER_JITT_DLL_HF       |                    |       | ±1   |       | ±1    |       | ±1   | ns       |

| CLKIN (using CLKFX outputs)(2) | CLKIN_PER_JITT_FX_HF        |                    |       | ±1   |       | ±1    |       | ±1   | ns       |

| Feedback Clock Path Delay      | / Variation                 | 1                  | 1     | 1    | 1     |       | ı     | 1    | <u> </u> |

| CLKFB off-chip feedback        | CLKFB_DELAY_VAR_EXT         |                    |       | ±1   |       | ±1    |       | ±1   | ns       |

#### Notes:

- "DLL outputs" is used here to describe the outputs: CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV. If both DLL and CLKFX outputs are used, follow the more restrictive specification.

If DCM phase shift feature is used and CLKIN frequency > 200 Mhz, CLKIN duty cycle must be within ±5% (45/55 to 55/45).

Table 6: FG456/FGG456 — XC2VP2, XC2VP4, and XC2VP7

|      | Pin Description |            | No Connects |        |        |  |

|------|-----------------|------------|-------------|--------|--------|--|

| Bank |                 | Pin Number | XC2VP2      | XC2VP4 | XC2VP7 |  |

| N/A  | VTRXPAD6        | B9         |             |        |        |  |

| N/A  | AVCCAUXRX6      | B10        |             |        |        |  |

| N/A  | AVCCAUXTX7      | B14        |             |        |        |  |

| N/A  | VTTXPAD7        | B13        |             |        |        |  |

| N/A  | TXNPAD7         | A13        |             |        |        |  |

| N/A  | TXPPAD7         | A14        |             |        |        |  |

| N/A  | GNDA7           | C14        |             |        |        |  |

| N/A  | RXPPAD7         | A15        |             |        |        |  |

| N/A  | RXNPAD7         | A16        |             |        |        |  |

| N/A  | VTRXPAD7        | B15        |             |        |        |  |

| N/A  | AVCCAUXRX7      | B16        |             |        |        |  |

| N/A  | AVCCAUXTX9      | B18        | NC          | NC     |        |  |

| N/A  | VTTXPAD9        | B17        | NC          | NC     |        |  |

| N/A  | TXNPAD9         | A17        | NC          | NC     |        |  |

| N/A  | TXPPAD9         | A18        | NC          | NC     |        |  |

| N/A  | GNDA9           | C17        | NC          | NC     |        |  |

| N/A  | RXPPAD9         | A19        | NC          | NC     |        |  |

| N/A  | RXNPAD9         | A20        | NC          | NC     |        |  |

| N/A  | VTRXPAD9        | B19        | NC          | NC     |        |  |

| N/A  | AVCCAUXRX9      | B20        | NC          | NC     |        |  |

| N/A  | AVCCAUXRX16     | AA20       | NC          | NC     |        |  |

| N/A  | VTRXPAD16       | AA19       | NC          | NC     |        |  |

| N/A  | RXNPAD16        | AB20       | NC          | NC     |        |  |

| N/A  | RXPPAD16        | AB19       | NC          | NC     |        |  |

| N/A  | GNDA16          | Y17        | NC          | NC     |        |  |

| N/A  | TXPPAD16        | AB18       | NC          | NC     |        |  |

| N/A  | TXNPAD16        | AB17       | NC          | NC     |        |  |

| N/A  | VTTXPAD16       | AA17       | NC          | NC     |        |  |

| N/A  | AVCCAUXTX16     | AA18       | NC          | NC     |        |  |

| N/A  | AVCCAUXRX18     | AA16       |             |        |        |  |

| N/A  | VTRXPAD18       | AA15       |             |        |        |  |

| N/A  | RXNPAD18        | AB16       |             |        |        |  |

| N/A  | RXPPAD18        | AB15       |             |        |        |  |

| N/A  | GNDA18          | Y14        |             |        |        |  |

| N/A  | TXPPAD18        | AB14       |             |        |        |  |

| N/A  | TXNPAD18        | AB13       |             |        |        |  |

| N/A  | VTTXPAD18       | AA13       |             |        |        |  |

Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                  | Pin    | No Connects |        |        |  |

|------|------------------|--------|-------------|--------|--------|--|

| Bank | Pin Description  | Number | XC2VP2      | XC2VP4 | XC2VP7 |  |

| 7    | IO_L44P_7        | G24    | NC          |        |        |  |

| 7    | IO_L44N_7        | G23    | NC          |        |        |  |

| 7    | IO_L43P_7        | G22    | NC          |        |        |  |

| 7    | IO_L43N_7        | G21    | NC          |        |        |  |

| 7    | IO_L42P_7        | F25    | NC          | NC     | NC     |  |

| 7    | IO_L42N_7        | F24    | NC          | NC     | NC     |  |

| 7    | IO_L40P_7        | F23    | NC          | NC     | NC     |  |

| 7    | IO_L40N_7/VREF_7 | F22    | NC          | NC     | NC     |  |

| 7    | IO_L06P_7        | E26    |             |        |        |  |

| 7    | IO_L06N_7        | E25    |             |        |        |  |

| 7    | IO_L05P_7        | E24    |             |        |        |  |

| 7    | IO_L05N_7        | E23    |             |        |        |  |

| 7    | IO_L04P_7        | D26    |             |        |        |  |

| 7    | IO_L04N_7/VREF_7 | D25    |             |        |        |  |

| 7    | IO_L03P_7        | C26    |             |        |        |  |

| 7    | IO_L03N_7        | C25    |             |        |        |  |

| 7    | IO_L02P_7        | B26    |             |        |        |  |

| 7    | IO_L02N_7        | A25    |             |        |        |  |

| 7    | IO_L01P_7/VRN_7  | D24    |             |        |        |  |

| 7    | IO_L01N_7/VRP_7  | C23    |             |        |        |  |

|      |                  |        |             |        |        |  |

| 0    | VCCO_0           | C17    |             |        |        |  |

| 0    | VCCO_0           | C20    |             |        |        |  |

| 0    | VCCO_0           | H17    |             |        |        |  |

| 0    | VCCO_0           | H18    |             |        |        |  |

| 0    | VCCO_0           | J14    |             |        |        |  |

| 0    | VCCO_0           | J15    |             |        |        |  |

| 0    | VCCO_0           | J16    |             |        |        |  |

| 1    | VCCO_1           | C7     |             |        |        |  |

| 1    | VCCO_1           | H9     |             |        |        |  |

| 1    | VCCO_1           | C10    |             |        |        |  |

| 1    | VCCO_1           | H10    |             |        |        |  |

| 1    | VCCO_1           | J11    |             |        |        |  |

| 1    | VCCO_1           | J12    |             |        |        |  |

| 1    | VCCO_1           | J13    |             |        |        |  |

| 2    | VCCO_2           | G2     |             |        |        |  |

| 2    | VCCO_2           | J8     |             |        |        |  |

Table 9: FF896 — XC2VP7, XC2VP20, XC2VPX20, and XC2VP30

|      | Pin Description       |                            | No Connects   |        |                      |         |

|------|-----------------------|----------------------------|---------------|--------|----------------------|---------|

| Bank | Virtex-II Pro devices | XC2VPX20<br>(if Different) | Pin<br>Number | XC2VP7 | XC2VP20,<br>XC2VPX20 | XC2VP30 |

| N/A  | VCCINT                |                            | Y13           |        |                      |         |

| N/A  | VCCINT                |                            | Y12           |        |                      |         |

| N/A  | VCCINT                |                            | W20           |        |                      |         |

| N/A  | VCCINT                |                            | W11           |        |                      |         |

| N/A  | VCCINT                |                            | V20           |        |                      |         |

| N/A  | VCCINT                |                            | V11           |        |                      |         |

| N/A  | VCCINT                |                            | U20           |        |                      |         |

| N/A  | VCCINT                |                            | U11           |        |                      |         |

| N/A  | VCCINT                |                            | T20           |        |                      |         |

| N/A  | VCCINT                |                            | T11           |        |                      |         |

| N/A  | VCCINT                |                            | R20           |        |                      |         |

| N/A  | VCCINT                |                            | R11           |        |                      |         |

| N/A  | VCCINT                |                            | P20           |        |                      |         |

| N/A  | VCCINT                |                            | P11           |        |                      |         |

| N/A  | VCCINT                |                            | N20           |        |                      |         |

| N/A  | VCCINT                |                            | N11           |        |                      |         |

| N/A  | VCCINT                |                            | M20           |        |                      |         |

| N/A  | VCCINT                |                            | M11           |        |                      |         |

| N/A  | VCCINT                |                            | L19           |        |                      |         |

| N/A  | VCCINT                |                            | L18           |        |                      |         |

| N/A  | VCCINT                |                            | L17           |        |                      |         |

| N/A  | VCCINT                |                            | L16           |        |                      |         |

| N/A  | VCCINT                |                            | L15           |        |                      |         |

| N/A  | VCCINT                |                            | L14           |        |                      |         |

| N/A  | VCCINT                |                            | L13           |        |                      |         |

| N/A  | VCCINT                |                            | L12           |        |                      |         |

| N/A  | GND                   |                            | AK22          |        |                      |         |

| N/A  | GND                   |                            | AK9           |        |                      |         |

| N/A  | GND                   |                            | AJ29          |        |                      |         |

| N/A  | GND                   |                            | AJ2           |        |                      |         |

| N/A  | GND                   |                            | AH28          |        |                      |         |

| N/A  | GND                   |                            | AH17          |        |                      |         |

| N/A  | GND                   |                            | AH14          |        |                      |         |

| N/A  | GND                   |                            | AH3           |        |                      |         |

| N/A  | GND                   |                            | AG27          |        |                      |         |

| N/A  | GND                   |                            | AG22          |        |                      |         |

Table 10: FF1152 — XC2VP20, XC2VP30, XC2VP40, and XC2VP50

|      | Pin Description  | Pin    | No Connects |         |         |         |  |

|------|------------------|--------|-------------|---------|---------|---------|--|

| Bank |                  | Number | XC2VP20     | XC2VP30 | XC2VP40 | XC2VP50 |  |

| 6    | IO_L01P_6/VRN_6  | AJ30   |             |         |         |         |  |

| 6    | IO_L01N_6/VRP_6  | AJ31   |             |         |         |         |  |

| 6    | IO_L02P_6        | AJ27   |             |         |         |         |  |

| 6    | IO_L02N_6        | AJ28   |             |         |         |         |  |

| 6    | IO_L03P_6        | AK31   |             |         |         |         |  |

| 6    | IO_L03N_6/VREF_6 | AK32   |             |         |         |         |  |

| 6    | IO_L04P_6        | AH29   |             |         |         |         |  |

| 6    | IO_L04N_6        | AH30   |             |         |         |         |  |

| 6    | IO_L05P_6        | AH27   |             |         |         |         |  |

| 6    | IO_L05N_6        | AG28   |             |         |         |         |  |

| 6    | IO_L06P_6        | AL33   |             |         |         |         |  |

| 6    | IO_L06N_6        | AL34   |             |         |         |         |  |

| 6    | IO_L15P_6        | AG29   | NC          |         |         |         |  |

| 6    | IO_L15N_6/VREF_6 | AG30   | NC          |         |         |         |  |

| 6    | IO_L16P_6        | AK33   | NC          |         |         |         |  |

| 6    | IO_L16N_6        | AK34   | NC          |         |         |         |  |

| 6    | IO_L17P_6        | AF27   | NC          |         |         |         |  |

| 6    | IO_L17N_6        | AF28   | NC          |         |         |         |  |

| 6    | IO_L18P_6        | AJ33   | NC          |         |         |         |  |

| 6    | IO_L18N_6        | AJ34   | NC          |         |         |         |  |

| 6    | IO_L19P_6        | AH31   | NC          |         |         |         |  |

| 6    | IO_L19N_6        | AH32   | NC          |         |         |         |  |

| 6    | IO_L20P_6        | AD25   | NC          |         |         |         |  |

| 6    | IO_L20N_6        | AD26   | NC          |         |         |         |  |

| 6    | IO_L21P_6        | AG31   | NC          |         |         |         |  |

| 6    | IO_L21N_6/VREF_6 | AG32   | NC          |         |         |         |  |

| 6    | IO_L22P_6        | AF29   | NC          |         |         |         |  |

| 6    | IO_L22N_6        | AF30   | NC          |         |         |         |  |

| 6    | IO_L23P_6        | AE27   | NC          |         |         |         |  |

| 6    | IO_L23N_6        | AE28   | NC          |         |         |         |  |

| 6    | IO_L24P_6        | AH33   | NC          |         |         |         |  |

| 6    | IO_L24N_6        | AH34   | NC          |         |         |         |  |

| 6    | IO_L31P_6        | AF31   |             |         |         |         |  |

| 6    | IO_L31N_6        | AF32   |             |         |         |         |  |

| 6    | IO_L32P_6        | AC25   |             |         |         |         |  |

| 6    | <br>IO_L32N_6    | AC26   |             |         |         |         |  |

| 6    | IO_L33P_6        | AG33   |             |         |         |         |  |

| 6    | IO_L33N_6/VREF_6 | AG34   |             |         |         |         |  |

Table 10: FF1152 — XC2VP20, XC2VP30, XC2VP40, and XC2VP50

|      |                  | Pin    | No Connects |         |         |         |  |

|------|------------------|--------|-------------|---------|---------|---------|--|

| Bank | Pin Description  | Number | XC2VP20     | XC2VP30 | XC2VP40 | XC2VP50 |  |

| 6    | IO_L53P_6        | W25    |             |         |         |         |  |

| 6    | IO_L53N_6        | W26    |             |         |         |         |  |

| 6    | IO_L54P_6        | AB33   |             |         |         |         |  |

| 6    | IO_L54N_6        | AA33   |             |         |         |         |  |

| 6    | IO_L55P_6        | Y28    |             |         |         |         |  |

| 6    | IO_L55N_6        | Y29    |             |         |         |         |  |

| 6    | IO_L56P_6        | W27    |             |         |         |         |  |

| 6    | IO_L56N_6        | W28    |             |         |         |         |  |

| 6    | IO_L57P_6        | Y31    |             |         |         |         |  |

| 6    | IO_L57N_6/VREF_6 | Y32    |             |         |         |         |  |

| 6    | IO_L58P_6        | W29    |             |         |         |         |  |

| 6    | IO_L58N_6        | W30    |             |         |         |         |  |

| 6    | IO_L59P_6        | W24    |             |         |         |         |  |

| 6    | IO_L59N_6        | V24    |             |         |         |         |  |

| 6    | IO_L60P_6        | AA34   |             |         |         |         |  |

| 6    | IO_L60N_6        | Y34    |             |         |         |         |  |

| 6    | IO_L85P_6        | W31    |             |         |         |         |  |

| 6    | IO_L85N_6        | W32    |             |         |         |         |  |

| 6    | IO_L86P_6        | V25    |             |         |         |         |  |

| 6    | IO_L86N_6        | V26    |             |         |         |         |  |

| 6    | IO_L87P_6        | Y33    |             |         |         |         |  |

| 6    | IO_L87N_6/VREF_6 | W33    |             |         |         |         |  |

| 6    | IO_L88P_6        | V29    |             |         |         |         |  |

| 6    | IO_L88N_6        | V30    |             |         |         |         |  |

| 6    | IO_L89P_6        | V27    |             |         |         |         |  |

| 6    | IO_L89N_6        | V28    |             |         |         |         |  |

| 6    | IO_L90P_6        | V31    |             |         |         |         |  |

| 6    | IO_L90N_6        | V32    |             |         |         |         |  |

|      |                  |        |             |         |         |         |  |

| 7    | IO_L90P_7        | U32    |             |         |         |         |  |

| 7    | IO_L90N_7        | U31    |             |         |         |         |  |

| 7    | IO_L89P_7        | U28    |             |         |         |         |  |

| 7    | IO_L89N_7        | U27    |             |         |         |         |  |

| 7    | IO_L88P_7        | V33    |             |         |         |         |  |

| 7    | IO_L88N_7/VREF_7 | U33    |             |         |         |         |  |

| 7    | IO_L87P_7        | U30    |             |         |         |         |  |

| 7    | IO_L87N_7        | U29    |             |         |         |         |  |

| 7    | IO_L86P_7        | U26    |             |         |         |         |  |

Table 10: FF1152 — XC2VP20, XC2VP30, XC2VP40, and XC2VP50

|      |                  | Pin    | No Connects |         |         |         |  |

|------|------------------|--------|-------------|---------|---------|---------|--|

| Bank | Pin Description  | Number | XC2VP20     | XC2VP30 | XC2VP40 | XC2VP50 |  |

| 7    | IO_L86N_7        | U25    |             |         |         |         |  |

| 7    | IO_L85P_7        | T32    |             |         |         |         |  |

| 7    | IO_L85N_7        | T31    |             |         |         |         |  |

| 7    | IO_L60P_7        | T30    |             |         |         |         |  |

| 7    | IO_L60N_7        | T29    |             |         |         |         |  |

| 7    | IO_L59P_7        | T28    |             |         |         |         |  |

| 7    | IO_L59N_7        | T27    |             |         |         |         |  |

| 7    | IO_L58P_7        | T33    |             |         |         |         |  |

| 7    | IO_L58N_7/VREF_7 | R33    |             |         |         |         |  |

| 7    | IO_L57P_7        | R32    |             |         |         |         |  |

| 7    | IO_L57N_7        | R31    |             |         |         |         |  |

| 7    | IO_L56P_7        | T26    |             |         |         |         |  |

| 7    | IO_L56N_7        | T25    |             |         |         |         |  |

| 7    | IO_L55P_7        | R34    |             |         |         |         |  |

| 7    | IO_L55N_7        | P34    |             |         |         |         |  |

| 7    | IO_L54P_7        | R29    |             |         |         |         |  |

| 7    | IO_L54N_7        | R28    |             |         |         |         |  |

| 7    | IO_L53P_7        | U24    |             |         |         |         |  |

| 7    | IO_L53N_7        | T24    |             |         |         |         |  |

| 7    | IO_L52P_7        | P32    |             |         |         |         |  |

| 7    | IO_L52N_7/VREF_7 | P31    |             |         |         |         |  |

| 7    | IO_L51P_7        | P30    |             |         |         |         |  |

| 7    | IO_L51N_7        | P29    |             |         |         |         |  |

| 7    | IO_L50P_7        | R26    |             |         |         |         |  |

| 7    | IO_L50N_7        | R25    |             |         |         |         |  |

| 7    | IO_L49P_7        | P33    |             |         |         |         |  |

| 7    | IO_L49N_7        | N33    |             |         |         |         |  |

| 7    | IO_L48P_7        | N32    |             |         |         |         |  |

| 7    | IO_L48N_7        | N31    |             |         |         |         |  |

| 7    | IO_L47P_7        | P28    |             |         |         |         |  |

| 7    | IO_L47N_7        | P27    |             |         |         |         |  |

| 7    | IO_L46P_7        | N34    |             |         |         |         |  |

| 7    | IO_L46N_7/VREF_7 | M34    |             |         |         |         |  |

| 7    | IO_L45P_7        | N30    |             |         |         |         |  |

| 7    | IO_L45N_7        | N29    |             |         |         |         |  |

| 7    | IO_L44P_7        | P26    |             |         |         |         |  |

| 7    | IO_L44N_7        | P25    |             |         |         |         |  |

| 7    | IO_L43P_7        | M32    |             |         |         |         |  |

Table 11: FF1148 — XC2VP40 and XC2VP50

|      |                  |            | No Co   | nnects  |

|------|------------------|------------|---------|---------|

| Bank | Pin Description  | Pin Number | XC2VP40 | XC2VP50 |

|      |                  |            |         |         |

| 1    | IO_L75N_1/GCLK3P | C17        |         |         |

| 1    | IO_L75P_1/GCLK2S | B17        |         |         |

| 1    | IO_L74N_1/GCLK1P | L17        |         |         |

| 1    | IO_L74P_1/GCLK0S | K17        |         |         |

| 1    | IO_L73N_1        | E17        |         |         |

| 1    | IO_L73P_1        | D17        |         |         |

| 1    | IO_L69N_1/VREF_1 | G17        |         |         |

| 1    | IO_L69P_1        | F17        |         |         |

| 1    | IO_L68N_1        | J17        |         |         |

| 1    | IO_L68P_1        | H17        |         |         |

| 1    | IO_L67N_1        | C16        |         |         |

| 1    | IO_L67P_1        | B16        |         |         |

| 1    | IO_L66N_1/VREF_1 | G16        | NC      |         |

| 1    | IO_L66P_1        | F16        | NC      |         |

| 1    | IO_L57N_1/VREF_1 | B15        |         |         |

| 1    | IO_L57P_1        | A15        |         |         |

| 1    | IO_L56N_1        | L16        |         |         |

| 1    | IO_L56P_1        | K16        |         |         |

| 1    | IO_L55N_1        | D16        |         |         |

| 1    | IO_L55P_1        | C15        |         |         |

| 1    | IO_L54N_1        | F15        |         |         |

| 1    | IO_L54P_1        | E15        |         |         |

| 1    | IO_L53_1/No_Pair | H16        |         |         |

| 1    | IO_L50_1/No_Pair | G15        |         |         |

| 1    | IO_L49N_1        | B14        |         |         |

| 1    | IO_L49P_1        | A14        |         |         |

| 1    | IO_L48N_1        | D14        |         |         |

| 1    | IO_L48P_1        | C14        |         |         |

| 1    | IO_L47N_1        | L15        |         |         |

| 1    | IO_L47P_1        | K15        |         |         |

| 1    | IO_L46N_1        | F14        |         |         |

| 1    | IO_L46P_1        | E14        |         |         |

| 1    | IO_L45N_1/VREF_1 | H14        |         |         |

| 1    | IO_L45P_1        | G14        |         |         |

| 1    | IO_L44N_1        | L14        |         |         |

| 1    | IO_L44P_1        | K14        |         |         |

| 1    | IO_L43N_1        | C13        |         |         |

|      |                  |            |         | 1       |

Table 11: FF1148 — XC2VP40 and XC2VP50

|      | Pin Description  |            | No Connects |         |  |

|------|------------------|------------|-------------|---------|--|

| Bank |                  | Pin Number | XC2VP40     | XC2VP50 |  |

| 6    | IO_L87N_6/VREF_6 | V33        |             |         |  |

| 6    | IO_L88P_6        | V30        |             |         |  |

| 6    | IO_L88N_6        | V31        |             |         |  |

| 6    | IO_L89P_6        | V24        |             |         |  |

| 6    | IO_L89N_6        | V25        |             |         |  |

| 6    | IO_L90P_6        | V28        |             |         |  |

| 6    | IO_L90N_6        | V29        |             |         |  |

|      |                  |            |             |         |  |

| 7    | IO_L90P_7        | U32        |             |         |  |

| 7    | IO_L90N_7        | V32        |             |         |  |

| 7    | IO_L89P_7        | U28        |             |         |  |

| 7    | IO_L89N_7        | U29        |             |         |  |

| 7    | IO_L88P_7        | U30        |             |         |  |

| 7    | IO_L88N_7/VREF_7 | U31        |             |         |  |

| 7    | IO_L87P_7        | T33        |             |         |  |

| 7    | IO_L87N_7        | U33        |             |         |  |

| 7    | IO_L86P_7        | U26        |             |         |  |

| 7    | IO_L86N_7        | U27        |             |         |  |

| 7    | IO_L85P_7        | T31        |             |         |  |

| 7    | IO_L85N_7        | T32        |             |         |  |

| 7    | IO_L60P_7        | R33        |             |         |  |

| 7    | IO_L60N_7        | R34        |             |         |  |

| 7    | IO_L59P_7        | U24        |             |         |  |

| 7    | IO_L59N_7        | U25        |             |         |  |

| 7    | IO_L58P_7        | R29        |             |         |  |

| 7    | IO_L58N_7/VREF_7 | R30        |             |         |  |

| 7    | IO_L57P_7        | P33        |             |         |  |

| 7    | IO_L57N_7        | P34        |             |         |  |

| 7    | IO_L56P_7        | T28        |             |         |  |

| 7    | IO_L56N_7        | T29        |             |         |  |

| 7    | IO_L55P_7        | P32        |             |         |  |

| 7    | IO_L55N_7        | R32        |             |         |  |

| 7    | IO_L54P_7        | P29        |             |         |  |

| 7    | IO_L54N_7        | P30        |             |         |  |

| 7    | IO_L53P_7        | T24        |             |         |  |

| 7    | IO_L53N_7        | T25        |             |         |  |

| 7    | IO_L52P_7        | N32        |             |         |  |

| 7    | IO_L52N_7/VREF_7 | N33        |             |         |  |

Table 11: FF1148 — XC2VP40 and XC2VP50

|      | Pin Description  |            | No Connects |         |  |

|------|------------------|------------|-------------|---------|--|

| Bank |                  | Pin Number | XC2VP40     | XC2VP50 |  |

| 7    | IO_L32P_7        | N24        |             |         |  |

| 7    | IO_L32N_7        | N25        |             |         |  |

| 7    | IO_L31P_7        | G33        |             |         |  |

| 7    | IO_L31N_7        | G34        |             |         |  |

| 7    | IO_L30P_7        | H31        |             |         |  |

| 7    | IO_L30N_7        | G32        |             |         |  |

| 7    | IO_L29P_7        | N27        |             |         |  |

| 7    | IO_L29N_7        | M28        |             |         |  |

| 7    | IO_L28P_7        | G28        |             |         |  |

| 7    | IO_L28N_7/VREF_7 | G29        |             |         |  |

| 7    | IO_L27P_7        | F33        |             |         |  |

| 7    | IO_L27N_7        | F34        |             |         |  |

| 7    | IO_L26P_7        | M26        |             |         |  |

| 7    | IO_L26N_7        | M27        |             |         |  |

| 7    | IO_L25P_7        | F31        |             |         |  |

| 7    | IO_L25N_7        | F32        |             |         |  |

| 7    | IO_L24P_7        | F30        |             |         |  |

| 7    | IO_L24N_7        | G30        |             |         |  |

| 7    | IO_L23P_7        | L25        |             |         |  |

| 7    | IO_L23N_7        | M25        |             |         |  |

| 7    | IO_L22P_7        | F27        |             |         |  |

| 7    | IO_L22N_7/VREF_7 | F28        |             |         |  |

| 7    | IO_L21P_7        | E29        |             |         |  |

| 7    | IO_L21N_7        | F29        |             |         |  |

| 7    | IO_L20P_7        | L28        |             |         |  |

| 7    | IO_L20N_7        | K28        |             |         |  |

| 7    | IO_L19P_7        | D33        |             |         |  |

| 7    | IO_L19N_7        | D34        |             |         |  |

| 7    | IO_L18P_7        | D32        |             |         |  |

| 7    | IO_L18N_7        | E32        |             |         |  |

| 7    | IO_L17P_7        | K26        |             |         |  |

| 7    | IO_L17N_7        | L26        |             |         |  |

| 7    | IO_L16P_7        | D31        |             |         |  |

| 7    | IO_L16N_7/VREF_7 | E31        |             |         |  |

| 7    | IO_L15P_7        | D29        |             |         |  |

| 7    | IO_L15N_7        | D30        |             |         |  |

| 7    | IO_L14P_7        | J28        |             |         |  |

| 7    | <br>IO_L14N_7    | J29        |             |         |  |

# FF1517 Flip-Chip Fine-Pitch BGA Package

As shown in Table 12, XC2VP50 and XC2VP70 Virtex-II Pro devices are available in the FF1517 flip-chip fine-pitch BGA package. Following this table are the FF1517 Flip-Chip Fine-Pitch BGA Package Specifications (1.00mm pitch).

Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                     | Pin    | No Connects |         |  |

|------|---------------------|--------|-------------|---------|--|

| Bank | Pin Description     | Number | XC2VP50     | XC2VP70 |  |

| 0    | IO_L01N_0/VRP_0     | D31    |             |         |  |

| 0    | IO_L01P_0/VRN_0 E31 |        |             |         |  |

| 0    | IO_L02N_0 K30       |        |             |         |  |

| 0    | IO_L02P_0           | J30    |             |         |  |

| 0    | IO_L03N_0           | G30    |             |         |  |

| 0    | IO_L03P_0/VREF_0    | H30    |             |         |  |

| 0    | IO_L05_0/No_Pair    | K28    |             |         |  |

| 0    | IO_L06N_0           | E30    |             |         |  |

| 0    | IO_L06P_0           | F30    |             |         |  |

| 0    | IO_L07N_0           | C30    |             |         |  |

| 0    | IO_L07P_0           | D30    |             |         |  |

| 0    | IO_L08N_0           | J29    |             |         |  |

| 0    | IO_L08P_0           | K29    |             |         |  |

| 0    | IO_L09N_0           | G29    |             |         |  |

| 0    | IO_L09P_0/VREF_0    | H29    |             |         |  |

| 0    | IO_L19N_0           | E29    |             |         |  |

| 0    | IO_L19P_0           | F29    |             |         |  |

| 0    | IO_L20N_0           | L28    |             |         |  |

| 0    | IO_L20P_0           | L27    |             |         |  |

| 0    | IO_L21N_0           | C29    |             |         |  |

| 0    | IO_L21P_0           | D29    |             |         |  |

| 0    | IO_L25N_0           | H28    |             |         |  |

| 0    | IO_L25P_0           | J28    |             |         |  |

| 0    | IO_L26N_0           | M27    |             |         |  |

| 0    | IO_L26P_0           | M26    |             |         |  |

| 0    | IO_L27N_0           | D28    |             |         |  |

| 0    | IO_L27P_0/VREF_0    | E28    |             |         |  |

| 0    | IO_L28N_0           | H27    | NC          |         |  |

| 0    | IO_L28P_0           | J27    | NC          |         |  |

| 0    | IO_L29N_0           | J26    | NC          |         |  |

| 0    | IO_L29P_0           | K26    | NC          |         |  |

| 0    | IO_L30N_0           | F28    | NC          |         |  |

| 0    | IO_L30P_0           | G27    | NC          |         |  |

| 1    |                     |        | D27 NC      |         |  |

Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       |                            |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

| Bank | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 3    | IO_L35N_3             |                            | AH11       |                      |          |

| 3    | IO_L35P_3             |                            | AH12       |                      |          |

| 3    | IO_L34N_3             |                            | AH5        |                      |          |

| 3    | IO_L34P_3             |                            | AH6        |                      |          |

| 3    | IO_L33N_3/VREF_3      |                            | AH9        |                      |          |

| 3    | IO_L33P_3             |                            | AH10       |                      |          |

| 3    | IO_L32N_3             |                            | AJ11       |                      |          |

| 3    | IO_L32P_3             |                            | AJ12       |                      |          |

| 3    | IO_L31N_3             |                            | AJ1        |                      |          |

| 3    | IO_L31P_3             |                            | AJ2        |                      |          |

| 3    | IO_L30N_3             |                            | AJ5        |                      |          |

| 3    | IO_L30P_3             |                            | AJ6        |                      |          |

| 3    | IO_L29N_3             |                            | AJ9        |                      |          |

| 3    | IO_L29P_3             |                            | AJ10       |                      |          |

| 3    | IO_L28N_3             |                            | AJ7        |                      |          |

| 3    | IO_L28P_3             |                            | AJ8        |                      |          |

| 3    | IO_L27N_3/VREF_3      |                            | AK1        |                      |          |

| 3    | IO_L27P_3             |                            | AK2        |                      |          |

| 3    | IO_L26N_3             |                            | AK11       |                      |          |

| 3    | IO_L26P_3             |                            | AK12       |                      |          |

| 3    | IO_L25N_3             |                            | AK3        |                      |          |

| 3    | IO_L25P_3             |                            | AK4        |                      |          |

| 3    | IO_L24N_3             |                            | AK5        |                      |          |

| 3    | IO_L24P_3             |                            | AK6        |                      |          |

| 3    | IO_L23N_3             |                            | AK9        |                      |          |

| 3    | IO_L23P_3             |                            | AK10       |                      |          |

| 3    | IO_L22N_3             |                            | AK7        |                      |          |

| 3    | IO_L22P_3             |                            | AK8        |                      |          |

| 3    | IO_L21N_3/VREF_3      |                            | AL2        |                      |          |

| 3    | IO_L21P_3             |                            | AL3        |                      |          |

| 3    | IO_L20N_3             |                            | AL11       |                      |          |

| 3    | IO_L20P_3             |                            | AL12       |                      |          |

| 3    | IO_L19N_3             |                            | AL4        |                      |          |

| 3    | IO_L19P_3             |                            | AL5        |                      |          |

| 3    | IO_L18N_3             |                            | AL7        |                      |          |

| 3    | IO_L18P_3             |                            | AL8        |                      |          |

*Table 14:* **FF1696** — **XC2VP100**

|      |                 |            | No Connects |  |

|------|-----------------|------------|-------------|--|

| Bank | Pin Description | Pin Number | XC2VP100    |  |

| 2    | VCCO_2          | F4         |             |  |

| 1    | VCCO_1          | R21        |             |  |

| 1    | VCCO_1          | P21        |             |  |

| 1    | VCCO_1          | R20        |             |  |

| 1    | VCCO_1          | P20        |             |  |

| 1    | VCCO_1          | R19        |             |  |

| 1    | VCCO_1          | P19        |             |  |

| 1    | VCCO_1          | R18        |             |  |

| 1    | VCCO_1          | P18        |             |  |

| 1    | VCCO_1          | H18        |             |  |

| 1    | VCCO_1          | D18        |             |  |

| 1    | VCCO_1          | P17        |             |  |

| 1    | VCCO_1          | H14        |             |  |

| 1    | VCCO_1          | D14        |             |  |

| 1    | VCCO_1          | M13        |             |  |

| 1    | VCCO_1          | D10        |             |  |

| 0    | VCCO_0          | D33        |             |  |

| 0    | VCCO_0          | M30        |             |  |

| 0    | VCCO_0          | H29        |             |  |

| 0    | VCCO_0          | D29        |             |  |

| 0    | VCCO_0          | P26        |             |  |

| 0    | VCCO_0          | R25        |             |  |

| 0    | VCCO_0          | P25        |             |  |

| 0    | VCCO_0          | H25        |             |  |

| 0    | VCCO_0          | D25        |             |  |

| 0    | VCCO_0          | R24        |             |  |

| 0    | VCCO_0          | P24        |             |  |

| 0    |                 | R23        |             |  |

| 0    | VCCO_0          | P23        |             |  |

| 0    | VCCO_0          | R22        |             |  |

| 0    | VCCO_0          | P22        |             |  |

|      |                 |            |             |  |

| N/A  | CCLK            | AM10       |             |  |

| N/A  | PROG_B          | J33        |             |  |

| N/A  | DONE            | AN10       |             |  |

| N/A  | M0              | AP33       |             |  |

| N/A  | M1              | AN33       |             |  |

*Table 14:* **FF1696** — **XC2VP100**

|      |                 |            | No Connects |  |

|------|-----------------|------------|-------------|--|

| Bank | Pin Description | Pin Number | XC2VP100    |  |

| N/A  | GND             | AD19       |             |  |

| N/A  | GND             | AC19       |             |  |

| N/A  | GND             | AB19       |             |  |

| N/A  | GND             | AA19       |             |  |

| N/A  | GND             | Y19        |             |  |

| N/A  | GND             | W19        |             |  |

| N/A  | GND             | V19        |             |  |

| N/A  | GND             | U19        |             |  |

| N/A  | GND             | M19        |             |  |

| N/A  | GND             | AF18       |             |  |

| N/A  | GND             | AE18       |             |  |

| N/A  | GND             | AD18       |             |  |

| N/A  | GND             | AC18       |             |  |

| N/A  | GND             | AB18       |             |  |

| N/A  | GND             | AA18       |             |  |

| N/A  | GND             | Y18        |             |  |

| N/A  | GND             | W18        |             |  |

| N/A  | GND             | V18        |             |  |

| N/A  | GND             | U18        |             |  |

| N/A  | GND             | BB17       |             |  |

| N/A  | GND             | AV17       |             |  |

| N/A  | GND             | AP17       |             |  |

| N/A  | GND             | AE17       |             |  |

| N/A  | GND             | AD17       |             |  |

| N/A  | GND             | AC17       |             |  |

| N/A  | GND             | AB17       |             |  |

| N/A  | GND             | AA17       |             |  |

| N/A  | GND             | Y17        |             |  |

| N/A  | GND             | W17        |             |  |

| N/A  | GND             | V17        |             |  |

| N/A  | GND             | J17        |             |  |

| N/A  | GND             | E17        |             |  |

| N/A  | GND             | A17        |             |  |

| N/A  | GND             | BB13       |             |  |

| N/A  | GND             | AV13       |             |  |

| N/A  | GND             | AP13       |             |  |

| N/A  | GND             | J13        |             |  |

# **Revision History**

This section records the change history for this module of the data sheet.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01/31/02 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 08/14/02 | 2.0     | Added package and pinout information for new devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 08/27/02 | 2.1     | <ul> <li>Updated SelectIO-Ultra information in Table 4. (Table deleted in v2.3.)</li> <li>Corrected direction for RXNPAD and TXPPAD in Table 4 (formerly Table 5).</li> </ul>                                                                                                                                                                                                                                                                                                                                          |

| 09/27/02 | 2.2     | Corrected Table 2 and Table 3 entries for XC2VP30, FF1152 package, maximum I/Os from 692 to 644.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11/20/02 | 2.3     | Added Number of Differential Pairs data to Table 3. Removed former Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12/03/02 | 2.4     | <ul> <li>Corrections in Table 4:</li> <li>Reclassified GCLKx (S/P) pins as Input/Output, since these pins can be used as normal I/Os if not used as clocks.</li> <li>Added cautionary note to PWRDWN_B pin, indicating that this function is not supported.</li> </ul>                                                                                                                                                                                                                                                 |

| 01/20/03 | 2.5     | Added and removed package/pinout information for existing devices:  In Table 1, added FG676 package information.  In Table 3, added FG676 package option for XC2VP20, XC2VP30, and XC2VP40.  In Table 12, removed FF1517 package option for XC2VP40.  Added FG676 package pinouts (Table 7) for XC2VP20, XC2VP30, and XC2VP40.  Added package diagram (Figure 3) for FG676 package.                                                                                                                                    |

| 05/19/03 | 2.5.1   | <ul> <li>Added section BREFCLK Pin Definitions, page 5.</li> <li>Added clarification to Table 4 and all device pinout tables regarding the dual-use nature of pins D0/DIN and BUSY/DOUT during configuration.</li> </ul>                                                                                                                                                                                                                                                                                               |

| 06/19/03 | 2.5.3   | <ul> <li>Added notation of "open-drain" to TDO pin in Table 4.</li> <li>The final GND pin in each of six pinout tables was inadvertently deleted in v2.5.1. This revision restores the deleted GND pins as follows: <ul> <li>Pin A1, Table 6, page 16 (FG456)</li> <li>Pin AF26, Table 7, page 30 (FG676)</li> <li>Pin AN34, Table 10, page 98 (FF1152)</li> <li>Pin E1, Table 11, page 130 (FF1148)</li> <li>Pin C38, Table 12, page 162 (FF1517)</li> <li>Pin E1, Table 14, page 253 (FF1696)</li> </ul> </li> </ul> |

| 08/25/03 | 2.5.5   | <ul> <li>Table 4: Deleted Note 2, obsolete. There is only one GNDA pin per MGT.</li> <li>Table 4: Deleted pins ALT_VRP and ALT_VRN. Not used in Virtex-II Pro FPGAs.</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

| 12/10/03 | 3.0     | <ul> <li>XC2VP2 through XC2VP70 speed grades -5, -6, and -7, and XC2VP100 speed grades</li> <li>-5 and -6, are released to <b>Production status</b>.</li> </ul>                                                                                                                                                                                                                                                                                                                                                        |

| 02/19/04 | 3.1     | <ul> <li>Table 4, signal descriptions column:         <ul> <li>For signals TDI, TMS, and TCK, added: Pins are 3.3V-compatible.</li> <li>For signals M2, M1, M0, added: Tie to 3.3V only with 100Ω series resistor. No toggling during or after configuration.</li> <li>For signal TDO, added: No internal pull-up. External pull-up to 3.3V OK with resistor greater than 200Ω.</li> </ul> </li> </ul>                                                                                                                 |

| 03/09/04 | 3.1.1   | Recompiled for backward compatibility with Acrobat 4 and above. No content changes.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 06/30/04 | 4.0     | Merged in DS110-4 (Module 4 of Virtex-II Pro X data sheet). Added data on available Pb-free packages and updated package diagrams for affected devices.                                                                                                                                                                                                                                                                                                                                                                |