Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 3424                                                        |

| Number of Logic Elements/Cells | 30816                                                       |

| Total RAM Bits                 | 2506752                                                     |

| Number of I/O                  | 556                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 896-BBGA, FCBGA                                             |

| Supplier Device Package        | 896-FCBGA (31x31)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2vp30-6ff896c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Introduction and Overview

# Virtex-II Pro / Virtex-II Pro X Device/Package Combinations and Maximum I/Os

Offerings include ball grid array (BGA) packages with 1.0 mm pitch. In addition to traditional wire-bond interconnect (FG/FGG packages), flip-chip interconnect (FF packages) is used in some of the BGA offerings. Flip-chip interconnect construction supports more I/Os than are possible in wire-bond versions of similar packages, providing a high pin count and excellent power dissipation.

The device/package combination table (Table 3) details the maximum number of user I/Os and RocketIO / RocketIO X MGTs for each device and package using wire-bond or flip-chip technology.

The FF1148 and FF1696 packages have no RocketlO transceivers bonded out. Extra SelectIO-Ultra resources occupy available pins in these packages, resulting in a higher user I/O count. These packages are available for the XC2VP40, XC2VP50, and XC2VP100 devices only.

The I/Os per package count includes all user I/Os except the 15 control pins (CCLK, DONE, M0, M1, M2, PROG B, PWRDWN\_B, TCK, TDI, TDO, TMS, HSWAP\_EN, DXN, DXP, and RSVD), VBATT, and the RocketIO / RocketIO X transceiver pins.

Table 3: Virtex-II Pro Device/Package Combinations and Maximum Number of Available I/Os

| Package <sup>(1)</sup> | FG256/<br>FGG256 | FG456/<br>FGG456 | FG676   | FF672   | FF896                | FF1152  | FF1148   | FF1517  | FF1704      | FF1696                 |

|------------------------|------------------|------------------|---------|---------|----------------------|---------|----------|---------|-------------|------------------------|

| Pitch (mm)             | 1.00             | 1.00             | 1.00    | 1.00    | 1.00                 | 1.00    | 1.00     | 1.00    | 1.00        | 1.00                   |

| Size (mm)              | 17 x 17          | 23 x 23          | 26 x 26 | 27 x 27 | 31 x 31              | 35 x 35 | 35 x 35  | 40 x 40 | 42.5 x 42.5 | 42.5 x 42.5            |

| XC2VP2                 | 140/4            | 156/4            |         | 204/4   |                      |         |          |         |             |                        |

| XC2VP4                 | 140/4            | 248/4            |         | 348/4   |                      |         |          |         |             |                        |

| XC2VP7                 |                  | 248/8            |         | 396/8   | 396/8                |         |          |         |             |                        |

| XC2VP20                |                  |                  | 404/8   |         | 556/8                | 564/8   |          |         |             |                        |

| XC2VPX20               |                  |                  |         |         | 552/8 <sup>(2)</sup> |         |          |         |             |                        |

| XC2VP30                |                  |                  | 416/8   |         | 556/8                | 644/8   |          |         |             |                        |

| XC2VP40                |                  |                  | 416/8   |         |                      | 692/12  | 804/0(3) |         |             |                        |

| XC2VP50                |                  |                  |         |         |                      | 692/16  | 812/0(3) | 852/16  |             |                        |

| XC2VP70                |                  |                  |         |         |                      |         |          | 964/16  | 996/20      |                        |

| XC2VPX70               |                  |                  |         |         |                      |         |          |         | 992/20(2)   |                        |

| XC2VP100               |                  |                  |         |         |                      |         |          |         | 1,040/20    | 1,164/0 <sup>(3)</sup> |

#### Notes:

- Wirebond packages FG256, FG456, and FG676 are also available in Pb-free versions FGG256, FGG456, and FGG676. See Virtex-II Pro Ordering Examples for details on how to order.

- Virtex-II Pro X device is equipped with RocketIO X transceiver cores.

- The RocketIO transceivers in devices in the FF1148 and FF1696 packages are not bonded out to the package pins.

### Maximum Performance

Maximum performance of the RocketIO / RocketIO X transceiver and the PowerPC processor block varies, depending on package style and speed grade. See Table 4 for details. Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics contains the rest of the FPGA fabric performance parameters.

Table 4: Maximum RocketlO / RocketlO X Transceiver and Processor Block Performance

| Device                               | <b>-7</b> <sup>(1)</sup> | -6                  | -5                  | Units |

|--------------------------------------|--------------------------|---------------------|---------------------|-------|

| RocketIO X Transceiver FlipChip (FF) | N/A                      | 6.25 <sup>(3)</sup> | 4.25 <sup>(3)</sup> | Gb/s  |

| RocketIO Transceiver FlipChip (FF)   | 3.125                    | 3.125               | 2.0                 | Gb/s  |

| RocketIO Transceiver Wirebond (FG)   | 2.5                      | 2.5                 | 2.0                 | Gb/s  |

| PowerPC Processor Block              | 400 <sup>(2)</sup>       | 350 <sup>(2)</sup>  | 300                 | MHz   |

### Notes:

- -7 speed grade devices are not available in Industrial grade.

- IMPORTANT! When CPMC405CLOCK runs at speeds greater than 350 MHz in -7 Commercial grade dual-processor devices, or greater than 300 MHz in -6 Industrial grade dual-processor devices, users must implement the technology presented in XAPP755, "PowerPC 405 Clock Macro for -7(C) and -6(I) Speed Grade Dual-Processor Devices." Refer to Table 1 to identify dual-processor devices.

- XC2VPX70 is only available at fixed 4.25 Gb/s baud rate.

DS083 (v5.0) June 21, 2011 www.xilinx.com Module 1 of 4

# **Product Not Recommended For New Designs**

Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description

- Single-cycle and multi-cycle mode option for I-side and D-side interfaces

- Single cycle = one CPU clock cycle; multi-cycle = minimum of two and maximum of eight CPU clock cycles

- FPGA configurable DCR addresses within DSOCM and ISOCM.

- Independent 16 MB logical memory space available within PPC405 memory map for each of the DSOCM and ISOCM. The number of block RAMs in the device might limit the maximum amount of OCM supported.

- Maximum of 64K and 128K bytes addressable from DSOCM and ISOCM interfaces, respectively, using address outputs from OCM directly without additional decoding logic.

### **Data-Side OCM (DSOCM)**

- 32-bit Data Read bus and 32-bit Data Write bus

- Byte write access to DSBRAM support

- Second port of dual port DSBRAM is available to read/write from an FPGA interface

- 22-bit address to DSBRAM port

- 8-bit DCR Registers: DSCNTL, DSARC

- Three alternatives to write into DSBRAM: BRAM initialization, CPU, FPGA H/W using second port

### Instruction-Side OCM (ISOCM)

The ISOCM interface contains a 64-bit read only port, for instruction fetches, and a 32-bit write only port, to initialize or test the ISBRAM. When implementing the read only port, the user must deassert the write port inputs. The preferred method of initializing the ISBRAM is through the configuration bitstream.

- 64-bit Data Read Only bus (two instructions per cycle)

- 32-bit Data Write Only bus (through DCR)

- Separate 21-bit address to ISBRAM

- 8-bit DCR Registers: ISCNTL, ISARC

- 32-bit DCR Registers: ISINIT, ISFILL

- Two alternatives to write into ISBRAM: BRAM initialization, DCR and write instruction

## Clock/Control Interface Logic

The clock/control interface logic provides proper initialization and connections for PPC405 clock/power management, resets, PLB cycle control, and OCM interfaces. It also couples user signals between the FPGA fabric and the embedded PPC405 CPU core.

The processor clock connectivity is similar to CLB clock pins. It can connect either to global clock nets or general routing resources. Therefore the processor clock source can come from DCM, CLB, or user package pin.

### **CPU-FPGA Interfaces**

All Processor Block user pins link up with the general FPGA routing resources through the CPU-FPGA interface. Therefore processor signals have the same routability as other non-Processor Block user signals. Longlines and hex lines travel across the Processor Block both vertically and horizontally, allowing signals to route through the Processor Block.

### Processor Local Bus (PLB) Interfaces

The PPC405 core accesses high-speed system resources through PLB interfaces on the instruction and data cache controllers. The PLB interfaces provide separate 32-bit address/64-bit data buses for the instruction and data sides.

The cache controllers are both PLB masters. PLB arbiters are implemented in the FPGA fabric and are available as soft IP cores.

# Device Control Register (DCR) Bus Interface

The device control register (DCR) bus has 10 bits of address space for components external to the PPC405 core. Using the DCR bus to manage status and configuration registers reduces PLB traffic and improves system integrity. System resources on the DCR bus are protected or isolated from wayward code since the DCR bus is not part of the system memory map.

### External Interrupt Controller (EIC) Interface

Two level-sensitive user interrupt pins (critical and non-critical) are available. They can be either driven by user defined logic or Xilinx soft interrupt controller IP core outside the Processor Block.

### Clock/Power Management (CPM) Interface

The CPM interface supports several methods of clock distribution and power management. Three modes of operation that reduce power consumption below the normal operational level are available.

#### Reset Interface

There are three user reset input pins (core, chip, and system) and three user reset output pins for different levels of reset, if required.

### Debug Interface

Debugging interfaces on the embedded PPC405 core, consisting of the JTAG and Trace ports, offer access to resources internal to the core and assist in software development. The JTAG port provides basic JTAG chip testing functionality as well as the ability for external debug tools to gain control of the processor for debug purposes. The Trace port furnishes programmers with a mechanism for acquiring instruction execution traces.

The JTAG port is compatible with IEEE Std 1149.1, which defines a test access port (TAP) and Boundary-Scan architecture. Extensions to the JTAG interface provide debuggers with processor control that includes stopping, starting, and stepping the PPC405 core. These extensions are compliant with the IEEE 1149.1 specifications for vendor-specific extensions.

DS083 (v5.0) June 21, 2011 www.xilinx.com Module 2 of 4

# **Product Not Recommended For New Designs**

Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description

- Execution unit

- Timers

- Debug logic unit

It operates on instructions in a five stage pipeline consisting of a fetch, decode, execute, write-back, and load write-back stage. Most instructions execute in a single cycle, including loads and stores.

### Instruction and Data Cache

The embedded PPC405 core provides an instruction cache unit (ICU) and a data cache unit (DCU) that allow concurrent accesses and minimize pipeline stalls. The instruction and data cache array are 16 KB each. Both cache units are two-way set associative. Each way is organized into 256 lines of 32 bytes (eight words). The instruction set provides a rich assortment of cache control instructions, including instructions to read tag information and data arrays.

The PPC405 core accesses external memory through the instruction (ICU) and data cache units (DCU). The cache units each include a 64-bit PLB master interface, cache arrays, and a cache controller. The ICU and DCU handle cache misses as requests over the PLB to another PLB device such as an external bus interface unit. Cache hits are handled as single cycle memory accesses to the instruction and data caches.

### Instruction Cache Unit (ICU)

The ICU provides one or two instructions per cycle to the instruction queue over a 64-bit bus. A line buffer (built into the output of the array for manufacturing test) enables the ICU to be accessed only once for every four instructions, to reduce power consumption by the array.

The ICU can forward any or all of the four or eight words of a line fill to the EXU to minimize pipeline stalls caused by cache misses. The ICU aborts speculative fetches abandoned by the EXU, eliminating unnecessary line fills and enabling the ICU to handle the next EXU fetch. Aborting abandoned requests also eliminates unnecessary external bus activity, thereby increasing external bus utilization.

### Data Cache Unit (DCU)

The DCU transfers one, two, three, four, or eight bytes per cycle, depending on the number of byte enables presented by the CPU. The DCU contains a single-element command and store data queue to reduce pipeline stalls; this queue enables the DCU to independently process load/store and cache control instructions. Dynamic PLB request prioritization reduces pipeline stalls even further. When the DCU is busy with a low-priority request while a subsequent storage operation requested by the CPU is stalled; the DCU automatically increases the priority of the current request to the PLB

The DCU provides additional features that allow the programmer to tailor its performance for a given application. The DCU can function in write-back or write-through mode,

as controlled by the Data Cache Write-through Register (DCWR) or the Translation Look-aside Buffer (TLB); the cache controller can be tuned for a balance of performance and memory coherency. Write-on-allocate, controlled by the store word on allocate (SWOA) field of the Core Configuration Register 0 (CCR0), can inhibit line fills caused by store misses, to further reduce potential pipeline stalls and unwanted external bus traffic.

### **Fetch and Decode Logic**

The fetch/decode logic maintains a steady flow of instructions to the execution unit by placing up to two instructions in the fetch queue. The fetch queue consists of three buffers: pre-fetch buffer 1 (PFB1), pre-fetch buffer 0 (PFB0), and decode (DCD). The fetch logic ensures that instructions proceed directly to decode when the queue is empty.

Static branch prediction as implemented on the PPC405 core takes advantage of some standard statistical properties of code. Branches with negative address displacement are by default assumed taken. Branches that do not test the condition or count registers are also predicted as taken. The PPC405 core bases branch prediction upon these default conditions when a branch is not resolved and speculatively fetches along the predicted path. The default prediction can be overridden by software at assembly or compile time.

Branches are examined in the decode and pre-fetch buffer 0 fetch queue stages. Two branch instructions can be handled simultaneously. If the branch in decode is not taken, the fetch logic fetches along the predicted path of the branch instruction in pre-fetch buffer 0. If the branch instruction in pre-fetch buffer 0 pre-fetch buffer 0.

### **Execution Unit**

The embedded PPC405 core has a single issue execution unit (EXU) containing the register file, arithmetic logic unit (ALU), and the multiply-accumulate (MAC) unit. The execution unit performs all 32-bit PowerPC integer instructions in hardware.

The register file is comprised of thirty-two 32-bit general purpose registers (GPR), which are accessed with three read ports and two write ports. During the decode stage, data is read out of the GPRs and fed to the execution unit. Likewise, during the write-back stage, results are written to the GPR. The use of the five ports on the register file enables either a load or a store operation to execute in parallel with an ALU operation.

## **Memory Management Unit (MMU)**

The embedded PPC405 core has a 4 GB address space, which is presented as a flat address space.

The MMU provides address translation, protection functions, and storage attribute control for embedded applications. The MMU supports demand-paged virtual memory and other management schemes that require precise control of logical-to-physical address mapping and flexible

# Table 12: Summary of Voltage Supply Requirements for All Input and Output Standards

|                         | v <sub>cco</sub> |          | V <sub>REF</sub> | Terminat | ion Type |

|-------------------------|------------------|----------|------------------|----------|----------|

| I/O Standard            | Output           | Input    | Input            | Output   | Input    |

| LVTTL <sup>(1)</sup>    |                  |          | N/R              | N/R      | N/R      |

| LVCMOS33 <sup>(1)</sup> |                  |          | N/R              | N/R      | N/R      |

| LVDCI_33 <sup>(1)</sup> | 3.3              | 3.3      | N/R              | Series   | N/R      |

| PCIX <sup>(2)</sup>     | 3.3              | 3.3      | N/R              | N/R      | N/R      |

| PCI33_3 <sup>(2)</sup>  |                  |          | N/R              | N/R      | N/R      |

| PCI66_3 <sup>(2)</sup>  |                  |          | N/R              | N/R      | N/R      |

| LVDS_25                 |                  |          | N/R              | N/R      | N/R      |

| LVDSEXT_25              |                  |          | N/R              | N/R      | N/R      |

| LDT_25                  |                  | Note (3) | N/R              | N/R      | N/R      |

| ULVDS_25                |                  |          | N/R              | N/R      | N/R      |

| BLVDS_25                |                  |          | N/R              | N/R      | N/R      |

| LVPECL_25               |                  |          | N/R              | N/R      | N/R      |

| SSTL2_I                 |                  |          | 1.25             | N/R      | N/R      |

| SSTL2_II                |                  |          | 1.25             | N/R      | N/R      |

| LVCMOS25                |                  |          | N/R              | N/R      | N/R      |

| LVDCI_25                | 2.5              |          | N/R              | Series   | N/R      |

| LVDCI_DV2_25            |                  |          | N/R              | Series   | N/R      |

| LVDS_25_DCI             |                  |          | N/R              | N/R      | Split    |

| LVDSEXT_25_DCI          |                  |          | N/R              | N/R      | Split    |

| SSTL2_I_DCI             |                  | 2.5      | 1.25             | N/R      | Split    |

| SSTL2_II_DCI            |                  |          | 1.25             | Split    | Split    |

| LVDS_25_DT              |                  |          | N/R              | N/R      | N/R      |

| LVDSEXT_25_DT           |                  |          | N/R              | N/R      | N/R      |

| LDT_25_DT               |                  |          | N/R              | N/R      | N/R      |

| ULVDS_25_DT             |                  |          | N/R              | N/R      | N/R      |

Table 12: Summary of Voltage Supply Requirements for All Input and Output Standards (Continued)

|                 | V <sub>C</sub> | со        | V <sub>REF</sub> | Terminat | ion Type |

|-----------------|----------------|-----------|------------------|----------|----------|

| I/O Standard    | Output         | Input     | Input            | Output   | Input    |

| HSTL_III_18     |                |           | 1.1              | N/R      | N/R      |

| HSTL_IV_18      |                |           | 1.1              | N/R      | N/R      |

| HSTL_I_18       |                | Note (0)  | 0.9              | N/R      | N/R      |

| HSTL_II_18      |                | Note (3)  | 0.9              | N/R      | N/R      |

| SSTL18_I        |                |           | 0.9              | N/R      | N/R      |

| SSTL18_II       |                |           | 0.9              | N/R      | N/R      |

| LVCMOS18        |                |           | N/R              | N/R      | N/R      |

| LVDCI_18        | 1.8            |           | N/R              | Series   | N/R      |

| LVDCI_DV2_18    |                |           | N/R              | Series   | N/R      |

| HSTL_III_DCI_18 |                |           | 1.1              | N/R      | Single   |

| HSTL_IV_DCI_18  |                | 1.8       | 1.1              | Single   | Single   |

| HSTL_I_DCI_18   |                |           | 0.9              | N/R      | Split    |

| HSTL_II_DCI_18  |                |           | 0.9              | Split    | Split    |

| SSTL18_I_DCI    |                |           | 0.9              | N/R      | Split    |

| SSTL18_II_DCI   |                |           | 0.9              | Split    | Split    |

| HSTL_III        |                | Note (3)  | 0.9              | N/R      | N/R      |

| HSTL_IV         |                |           | 0.9              | N/R      | N/R      |

| HSTL_I          |                | Note (3)  | 0.75             | N/R      | N/R      |

| HSTL_II         |                |           | 0.75             | N/R      | N/R      |

| LVCMOS15        |                |           | N/R              | N/R      | N/R      |

| LVDCI_15        | 1.5            |           | N/R              | Series   | N/R      |

| LVDCI_DV2_15    | 1.5            |           | N/R              | Series   | N/R      |

| GTLP_DCI        |                | 1.5       | 1                | Single   | Single   |

| HSTL_III_DCI    |                | 1.5       | 0.9              | N/R      | Single   |

| HSTL_IV_DCI     |                |           | 0.9              | Single   | Single   |

| HSTL_I_DCI      |                |           | 0.75             | N/R      | Split    |

| HSTL_II_DCI     |                |           | 0.75             | Split    | Split    |

| GTL_DCI         | 1.2            | 1.2       | 0.8              | Single   | Single   |

| GTLP            | N/R            | Note (3)  | 1                | N/R      | N/R      |

| GTL             | IN/□\          | 14018 (3) | 0.8              | N/R      | N/R      |

### Notes:

- See application note XAPP659 for more detailed information. See application note XAPP653 for more detailed information.

- Pin voltage must not exceed V<sub>CCO</sub>.

- N/R = no requirement.

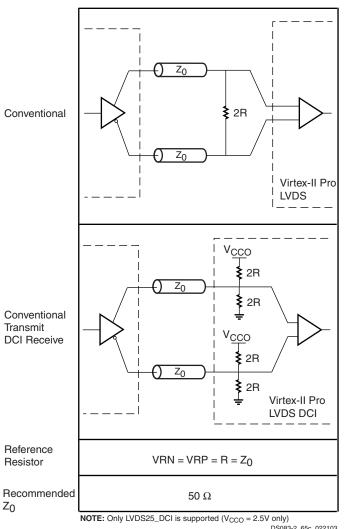

Figure 30 provides examples illustrating the use of the LVDS\_25\_DCI and LVDSEXT\_25\_DCI I/O standards. For a complete list, see the <u>Virtex-II Pro Platform FPGA User Guide</u>.

LVDS\_25\_DCI and LVDSEXT\_25\_DCI Receiver

Figure 30: LVDS DCI Usage Examples

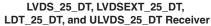

# On-Chip Differential Termination

Virtex-II Pro provides a true  $100\Omega$  differential termination (DT) across the input differential receiver terminals. The LVDS\_25\_DT, LVDSEXT\_25\_DT, LDT\_25\_DT, and ULVDS\_25\_DT standards support on-chip differential termination.

The on-chip input differential termination in Virtex-II Pro provides major advantages over the external resistor or the DCI termination solution:

- Eliminates the stub at the receiver completely and therefore greatly improve signal integrity

- Consumes less power than DCI termination

- Supports LDT (not supported by DCI termination)

- Frees up VRP/VRN pins

Figure 31 provides examples illustrating the use of the LVDS\_25\_DT, LVDSEXT\_25\_DT, LDT\_25\_DT, and ULVDS\_25\_DT I/O standards. For further details, refer to Solution Record 17244. Also see the Virtex-II Pro Platform FPGA User Guide for more design information.

Figure 31: LVDS Differential Termination Usage Examples

Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description

## Master SelectMAP Mode

This mode is a master version of the SelectMAP mode. The device is configured byte-wide on a CCLK supplied by the Virtex-II Pro FPGA device. Timing is similar to the Slave SerialMAP mode except that CCLK is supplied by the Virtex-II Pro FPGA.

### Boundary-Scan (JTAG, IEEE 1532) Mode

In Boundary-Scan mode, dedicated pins are used for configuring the Virtex-II Pro device. The configuration is done entirely through the IEEE 1149.1 Test Access Port (TAP).

Virtex-II Pro device configuration using Boundary-Scan is compatible with with IEEE 1149.1-1993 standard and the new IEEE 1532 standard for In-System Configurable (ISC) devices. The IEEE 1532 standard is backward compliant with the IEEE 1149.1-1993 TAP and state machine. The IEEE Standard 1532 for In-System Configurable (ISC) devices is intended to be programmed, reprogrammed, or tested on the board via a physical and logical protocol. Configuration through the Boundary-Scan port is always available, independent of the mode selection. Selecting the Boundary-Scan mode simply turns off the other modes.

Table 32: Virtex-II Pro Configuration Mode Pin Settings

| Configuration Mode <sup>(1)</sup> | M2 | М1 | МО | CCLK Direction | Data Width | Serial D <sub>OUT</sub> (2) |

|-----------------------------------|----|----|----|----------------|------------|-----------------------------|

| Master Serial                     | 0  | 0  | 0  | Out            | 1          | Yes                         |

| Slave Serial                      | 1  | 1  | 1  | In             | 1          | Yes                         |

| Master SelectMAP                  | 0  | 1  | 1  | Out            | 8          | No                          |

| Slave SelectMAP                   | 1  | 1  | 0  | In             | 8          | No                          |

| Boundary-Scan                     | 1  | 0  | 1  | N/A            | 1          | No                          |

#### Notes:

- 1. The HSWAP\_EN pin controls the pull-ups. Setting M2, M1, and M0 selects the configuration mode, while the HSWAP\_EN pin controls whether or not the pull-ups are used.

- Daisy chaining is possible only in modes where Serial D<sub>OUT</sub> is used. For example, in SelectMAP modes, the first device does NOT support daisy chaining of downstream devices.

Table 33 lists the default total number of bits required to configure each device.

Table 33: Virtex-II Pro Default Bitstream Lengths

| Device   | Number of Configuration<br>Bits |

|----------|---------------------------------|

| XC2VP2   | 1,305,376                       |

| XC2VP4   | 3,006,496                       |

| XC2VP7   | 4,485,408                       |

| XC2VP20  | 8,214,560                       |

| XC2VPX20 | 8,214,560                       |

| XC2VP30  | 11,589,920                      |

| XC2VP40  | 15,868,192                      |

| XC2VP50  | 19,021,344                      |

| XC2VP70  | 26,098,976                      |

| XC2VPX70 | 26,098,976                      |

| XC2VP100 | 34,292,768                      |

# **Configuration Sequence**

The configuration of Virtex-II Pro devices is a three-phase process. First, the configuration memory is cleared. Next, configuration data is loaded into the memory, and finally, the logic is activated by a start-up process.

Configuration is automatically initiated on power-up unless it is delayed by the user. The INIT\_B pin can be held Low using an open-drain driver. An open-drain is required since INIT\_B is a bidirectional open-drain pin that is held Low by a Virtex-II Pro FPGA device while the configuration memory is being cleared. Extending the time that the pin is Low causes the configuration sequencer to wait. Thus, configuration is delayed by preventing entry into the phase where data is loaded.

The configuration process can also be initiated by asserting the PROG\_B pin. The end of the memory-clearing phase is signaled by the INIT\_B pin going High, and the completion of the entire process is signaled by the DONE pin going High. The Global Set/Reset (GSR) signal is pulsed after the last frame of configuration data is written but before the start-up sequence. The GSR signal resets all flip-flops on the device.

The default start-up sequence is that one CCLK cycle after DONE goes High, the global 3-state signal (GTS) is released. This permits device outputs to turn on as necessary. One CCLK cycle later, the Global Write Enable (GWE) signal is released. This permits the internal storage elements to begin changing state in response to the logic and the user clock.

The relative timing of these events can be changed via configuration options in software. In addition, the GTS and GWE events can be made dependent on the DONE pins of multiple devices all going High, forcing the devices to start

Table 24: RocketIO X Receiver Switching Characteristics (1)

| Description                                    | Symbol             | Conditions | Min | Тур  | Max   | Units             |

|------------------------------------------------|--------------------|------------|-----|------|-------|-------------------|

|                                                |                    | 2.488 Gb/s |     | 0.80 | 0.65  | UI <sup>(2)</sup> |

| Receive total jitter tolerance                 | _                  | 3.125 Gb/s |     | 0.80 | 0.65  | UI                |

| using default equalization and PRBS-15 pattern | T <sub>JTOL</sub>  | 4.25 Gb/s  |     | 0.80 | 0.65  | UI                |

| •                                              |                    | 6.25 Gb/s  |     | 0.80 | 0.65  | UI                |

|                                                |                    | 2.488 Gb/s |     | 0.30 |       | UI                |

| Desaive random litter televanes                | _                  | 3.125 Gb/s |     | 0.30 |       | UI                |

| Receive random jitter tolerance                | T <sub>RJTOL</sub> | 4.25 Gb/s  |     | 0.30 |       | UI                |

|                                                |                    | 6.25 Gb/s  |     | 0.30 |       | UI                |

|                                                |                    | 2.488 Gb/s |     | 0.30 | 0.15  | UI                |

| Receive sinusoidal jitter tolerance            | _                  | 3.125 Gb/s |     | 0.30 | 0.15  | UI                |

| measured at 70 MHz                             | T <sub>SJTOL</sub> | 4.25 Gb/s  |     | 0.30 | 0.15  | UI                |

|                                                |                    | 6.25 Gb/s  |     | 0.30 | 0.15  | UI                |

|                                                |                    | 2.488 Gb/s |     | 0.55 | 0.45  | UI                |

| Pagaiva datarministia iittar talaranga         | _                  | 3.125 Gb/s |     | 0.55 | 0.45  | UI                |

| Receive deterministic jitter tolerance         | T <sub>DJTOL</sub> | 4.25 Gb/s  |     | 0.55 | 0.45  | UI                |

|                                                |                    | 6.25 Gb/s  |     | 0.50 | 0.45  | UI                |

| Receive latency <sup>(3)</sup>                 | T <sub>RXLAT</sub> |            |     | 25   | 34(4) | RXUSRCLK cycles   |

| RXUSRCLK duty cycle                            | T <sub>RXDC</sub>  |            | 45  | 50   | 55    | %                 |

| RXUSRCLK2 duty cycle                           | T <sub>RX2DC</sub> |            | 45  | 50   | 55    | %                 |

| Differential receive input sensitivity         | V <sub>EYE</sub>   |            |     | 120  | 250   | mV                |

#### Notes:

- The XC2VPX70 operates at a fixed 4.25 Gb/s baud rate.

- UI = Unit Interval

- Receive latency delay RXP/RXN to RXDATA. Refer to RocketIO X Transceiver User Guide for more information on calculating latency.

- This maximum may occur when certain conditions are present and clock correction and channel bonding are enabled. If these functions are both disabled, the maximum will be near the typical values.

Table 6: FG456/FGG456 — XC2VP2, XC2VP4, and XC2VP7

|      |                      |            |        | No Connects |        |  |  |  |

|------|----------------------|------------|--------|-------------|--------|--|--|--|

| Bank | Pin Description      | Pin Number | XC2VP2 | XC2VP4      | XC2VP7 |  |  |  |

| 7    | IO_L88N_7/VREF_7     | L5         |        |             |        |  |  |  |

| 7    | IO_L86P_7            | L6         |        |             |        |  |  |  |

| 7    | IO_L86N_7            | K6         |        |             |        |  |  |  |

| 7    | IO_L85P_7            | K1         |        |             |        |  |  |  |

| 7    | IO_L85N_7            | K2         |        |             |        |  |  |  |

| 7    | IO_L60P_7            | КЗ         | NC     |             |        |  |  |  |

| 7    | IO_L60N_7            | K4         | NC     |             |        |  |  |  |

| 7    | IO_L58P_7            | K5         | NC     |             |        |  |  |  |

| 7    | IO_L58N_7/VREF_7     | J5         | NC     |             |        |  |  |  |

| 7    | IO_L56P_7            | J1         | NC     |             |        |  |  |  |

| 7    | IO_L56N_7            | J2         | NC     |             |        |  |  |  |

| 7    | IO_L55P_7            | J3         | NC     |             |        |  |  |  |

| 7    | IO_L55N_7            | J4         | NC     |             |        |  |  |  |

| 7    | IO_L54P_7            | J6         | NC     |             |        |  |  |  |

| 7    | IO_L54N_7            | H5         | NC     |             |        |  |  |  |

| 7    | IO_L52P_7            | H1         | NC     |             |        |  |  |  |

| 7    | IO_L52N_7/VREF_7     | H2         | NC     |             |        |  |  |  |

| 7    | IO_L50P_7            | H3         | NC     |             |        |  |  |  |

| 7    | IO_L50N_7            | H4         | NC     |             |        |  |  |  |

| 7    | IO_L49P_7            | G1         | NC     |             |        |  |  |  |

| 7    | IO_L49N_7            | G2         | NC     |             |        |  |  |  |

| 7    | <br>IO_L48P_7        | G3         | NC     |             |        |  |  |  |

| 7    | IO_L48N_7            | G4         | NC     |             |        |  |  |  |

| 7    | IO_L46P_7            | G5         | NC     |             |        |  |  |  |

| 7    | <br>IO_L46N_7/VREF_7 | F5         | NC     |             |        |  |  |  |

| 7    | IO_L43P_7            | F1         | NC     |             |        |  |  |  |

| 7    | IO_L43N_7            | F2         | NC     |             |        |  |  |  |

| 7    | <br>IO_L06P_7        | F3         |        |             |        |  |  |  |

| 7    | <br>IO_L06N_7        | F4         |        |             |        |  |  |  |

| 7    | <br>IO_L04P_7        | E1         |        |             |        |  |  |  |

| 7    | IO_L04N_7/VREF_7     | E2         |        |             |        |  |  |  |

| 7    | IO_L03P_7            | E3         |        |             |        |  |  |  |

| 7    | IO_L03N_7            | E4         |        |             |        |  |  |  |

| 7    | IO_L02P_7            | D1         |        |             |        |  |  |  |

| 7    | IO_L02N_7            | D2         |        |             |        |  |  |  |

| 7    | IO_L01P_7/VRN_7      | C1         |        |             |        |  |  |  |

| 7    | IO_L01N_7/VRP_7      | C2         |        |             |        |  |  |  |

| •    | // _/                | 92         |        |             | 1      |  |  |  |

Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                 | Pin    | No Connects |        |        |  |  |

|------|-----------------|--------|-------------|--------|--------|--|--|

| Bank | Pin Description | Number | XC2VP2      | XC2VP4 | XC2VP7 |  |  |

| N/A  | VCCINT          | U16    |             |        |        |  |  |

| N/A  | VCCINT          | U18    |             |        |        |  |  |

| N/A  | VCCINT          | V10    |             |        |        |  |  |

| N/A  | VCCINT          | V17    |             |        |        |  |  |

| N/A  | VCCINT          | V18    |             |        |        |  |  |

| N/A  | VCCINT          | W19    |             |        |        |  |  |

| N/A  | VCCAUX          | B2     |             |        |        |  |  |

| N/A  | VCCAUX          | N1     |             |        |        |  |  |

| N/A  | VCCAUX          | P1     |             |        |        |  |  |

| N/A  | VCCAUX          | A13    |             |        |        |  |  |

| N/A  | VCCAUX          | A14    |             |        |        |  |  |

| N/A  | VCCAUX          | AE2    |             |        |        |  |  |

| N/A  | VCCAUX          | B25    |             |        |        |  |  |

| N/A  | VCCAUX          | N26    |             |        |        |  |  |

| N/A  | VCCAUX          | P26    |             |        |        |  |  |

| N/A  | VCCAUX          | AE25   |             |        |        |  |  |

| N/A  | VCCAUX          | AF13   |             |        |        |  |  |

| N/A  | VCCAUX          | AF14   |             |        |        |  |  |

| N/A  | GND             | СЗ     |             |        |        |  |  |

| N/A  | GND             | D4     |             |        |        |  |  |

| N/A  | GND             | E5     |             |        |        |  |  |

| N/A  | GND             | F6     |             |        |        |  |  |

| N/A  | GND             | G7     |             |        |        |  |  |

| N/A  | GND             | Y7     |             |        |        |  |  |

| N/A  | GND             | AA6    |             |        |        |  |  |

| N/A  | GND             | AB5    |             |        |        |  |  |

| N/A  | GND             | AC4    |             |        |        |  |  |

| N/A  | GND             | AD3    |             |        |        |  |  |

| N/A  | GND             | C24    |             |        |        |  |  |

| N/A  | GND             | D23    |             |        |        |  |  |

| N/A  | GND             | E22    |             |        |        |  |  |

| N/A  | GND             | F21    |             |        |        |  |  |

| N/A  | GND             | G20    |             |        |        |  |  |

| N/A  | GND             | K10    |             |        |        |  |  |

| N/A  | GND             | K12    |             |        |        |  |  |

| N/A  | GND             | K13    |             |        |        |  |  |

| N/A  | GND             | K14    |             |        |        |  |  |

Table 9: FF896 — XC2VP7, XC2VP20, XC2VPX20, and XC2VP30

|      | Pin Description       | on                         |               | No Connects |                      |         |  |  |

|------|-----------------------|----------------------------|---------------|-------------|----------------------|---------|--|--|

| Bank | Virtex-II Pro devices | XC2VPX20<br>(if Different) | Pin<br>Number | XC2VP7      | XC2VP20,<br>XC2VPX20 | XC2VP30 |  |  |

| 0    | IO_L01N_0/VRP_0       |                            | E25           |             |                      |         |  |  |

| 0    | IO_L01P_0/VRN_0       |                            | E24           |             |                      |         |  |  |

| 0    | IO_L02N_0             |                            | F24           |             |                      |         |  |  |

| 0    | IO_L02P_0             |                            | F23           |             |                      |         |  |  |

| 0    | IO_L03N_0             |                            | E23           |             |                      |         |  |  |

| 0    | IO_L03P_0/VREF_0      |                            | E22           |             |                      |         |  |  |

| 0    | IO_L05_0/No_Pair      |                            | G23           |             |                      |         |  |  |

| 0    | IO_L06N_0             |                            | H22           |             |                      |         |  |  |

| 0    | IO_L06P_0             |                            | G22           |             |                      |         |  |  |

| 0    | IO_L07N_0             |                            | F22           |             |                      |         |  |  |

| 0    | IO_L07P_0             |                            | F21           |             |                      |         |  |  |

| 0    | IO_L08N_0             |                            | D24           |             |                      |         |  |  |

| 0    | IO_L08P_0             |                            | C24           |             |                      |         |  |  |

| 0    | IO_L09N_0             |                            | H21           |             |                      |         |  |  |

| 0    | IO_L09P_0/VREF_0      |                            | G21           |             |                      |         |  |  |

| 0    | IO_L37N_0             |                            | E21           |             |                      |         |  |  |

| 0    | IO_L37P_0             |                            | D21           |             |                      |         |  |  |

| 0    | IO_L38N_0             |                            | D23           |             |                      |         |  |  |

| 0    | IO_L38P_0             |                            | C23           |             |                      |         |  |  |

| 0    | IO_L39N_0             |                            | H20           |             |                      |         |  |  |

| 0    | IO_L39P_0             |                            | G20           |             |                      |         |  |  |

| 0    | IO_L43N_0             |                            | E20           |             |                      |         |  |  |

| 0    | IO_L43P_0             |                            | D20           |             |                      |         |  |  |

| 0    | IO_L44N_0             |                            | B23           |             |                      |         |  |  |

| 0    | IO_L44P_0             |                            | A23           |             |                      |         |  |  |

| 0    | IO_L45N_0             |                            | H19           |             |                      |         |  |  |

| 0    | IO_L45P_0/VREF_0      |                            | G19           |             |                      |         |  |  |

| 0    | IO_L46N_0             |                            | E19           | NC          |                      |         |  |  |

| 0    | IO_L46P_0             |                            | E18           | NC          |                      |         |  |  |

| 0    | IO_L47N_0             |                            | C22           | NC          |                      |         |  |  |

| 0    | IO_L47P_0             |                            | B22           | NC          |                      |         |  |  |

| 0    | IO_L48N_0             |                            | F20           | NC          |                      |         |  |  |

| 0    | IO_L48P_0             |                            | F19           | NC          |                      |         |  |  |

| 0    | IO_L49N_0             |                            | G17           | NC          |                      |         |  |  |

| 0    | IO_L49P_0             |                            | F17           | NC          |                      |         |  |  |

| 0    | IO_L50_0/No_Pair      |                            | B21           | NC          |                      |         |  |  |

Table 9: FF896 — XC2VP7, XC2VP20, XC2VPX20, and XC2VP30

|      | Pin Description       |                            |               |        | No Connects          |         |

|------|-----------------------|----------------------------|---------------|--------|----------------------|---------|

| Bank | Virtex-II Pro devices | XC2VPX20<br>(if Different) | Pin<br>Number | XC2VP7 | XC2VP20,<br>XC2VPX20 | XC2VP30 |

| 7    | IO_L36N_7             |                            | F27           | NC     |                      |         |

| 7    | IO_L35P_7             |                            | K24           | NC     |                      |         |

| 7    | IO_L35N_7             |                            | K23           | NC     |                      |         |

| 7    | IO_L34P_7             |                            | E30           | NC     |                      |         |

| 7    | IO_L34N_7/VREF_7      |                            | E29           | NC     |                      |         |

| 7    | IO_L33P_7             |                            | E28           | NC     |                      |         |

| 7    | IO_L33N_7             |                            | E27           | NC     |                      |         |

| 7    | IO_L32P_7             |                            | H26           | NC     |                      |         |

| 7    | IO_L32N_7             |                            | H25           | NC     |                      |         |

| 7    | IO_L31P_7             |                            | D30           | NC     |                      |         |

| 7    | IO_L31N_7             |                            | D29           | NC     |                      |         |

| 7    | IO_L06P_7             |                            | D28           |        |                      |         |

| 7    | IO_L06N_7             |                            | C27           |        |                      |         |

| 7    | IO_L05P_7             |                            | J24           |        |                      |         |

| 7    | IO_L05N_7             |                            | J23           |        |                      |         |

| 7    | IO_L04P_7             |                            | C30           |        |                      |         |

| 7    | IO_L04N_7/VREF_7      |                            | C29           |        |                      |         |

| 7    | IO_L03P_7             |                            | D26           |        |                      |         |

| 7    | IO_L03N_7             |                            | C26           |        |                      |         |

| 7    | IO_L02P_7             |                            | G26           |        |                      |         |

| 7    | IO_L02N_7             |                            | G25           |        |                      |         |

| 7    | IO_L01P_7/VRN_7       |                            | B28           |        |                      |         |

| 7    | IO_L01N_7/VRP_7       |                            | A28           |        |                      |         |

|      |                       |                            |               |        |                      |         |

| 0    | VCCO_0                |                            | K21           |        |                      |         |

| 0    | VCCO_0                |                            | K20           |        |                      |         |

| 0    | VCCO_0                |                            | K19           |        |                      |         |

| 0    | VCCO_0                |                            | K18           |        |                      |         |

| 0    | VCCO_0                |                            | K17           |        |                      |         |

| 0    | VCCO_0                |                            | K16           |        |                      |         |

| 0    | VCCO_0                |                            | J21           |        |                      |         |

| 0    | VCCO_0                |                            | J20           |        |                      |         |

| 0    | VCCO_0                |                            | J19           |        |                      |         |

| 0    | VCCO_0                |                            | J18           |        |                      |         |

| 1    | VCCO_1                |                            | K15           |        |                      |         |

| 1    | VCCO_1                |                            | K14           |        |                      |         |

Table 11: FF1148 — XC2VP40 and XC2VP50

|      |                 |            | No Connects |         |

|------|-----------------|------------|-------------|---------|

| Bank | Pin Description | Pin Number | XC2VP40     | XC2VP50 |

| N/A  | GND             | AP19       |             |         |

| N/A  | GND             | AK19       |             |         |

| N/A  | GND             | AF19       |             |         |

| N/A  | GND             | AA19       |             |         |

| N/A  | GND             | Y19        |             |         |

| N/A  | GND             | W19        |             |         |

| N/A  | GND             | V19        |             |         |

| N/A  | GND             | U19        |             |         |

| N/A  | GND             | T19        |             |         |

| N/A  | GND             | R19        |             |         |

| N/A  | GND             | P19        |             |         |

| N/A  | GND             | J19        |             |         |

| N/A  | GND             | E19        |             |         |

| N/A  | GND             | A19        |             |         |

| N/A  | GND             | AP18       |             |         |

| N/A  | GND             | AA18       |             |         |

| N/A  | GND             | Y18        |             |         |

| N/A  | GND             | W18        |             |         |

| N/A  | GND             | V18        |             |         |

| N/A  | GND             | U18        |             |         |

| N/A  | GND             | T18        |             |         |

| N/A  | GND             | R18        |             |         |

| N/A  | GND             | P18        |             |         |

| N/A  | GND             | A18        |             |         |

| N/A  | GND             | AA17       |             |         |

| N/A  | GND             | Y17        |             |         |

| N/A  | GND             | W17        |             |         |

| N/A  | GND             | V17        |             |         |

| N/A  | GND             | U17        |             |         |

| N/A  | GND             | T17        |             |         |

| N/A  | GND             | R17        |             |         |

| N/A  | GND             | P17        |             |         |

| N/A  | GND             | AP16       |             |         |

| N/A  | GND             | AK16       |             |         |

| N/A  | GND             | AF16       |             |         |

| N/A  | GND             | AA16       |             |         |

| N/A  | GND             | Y16        |             |         |

| N/A  | GND             | W16        |             |         |

Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                  | Pin    |         | nnects  |

|------|------------------|--------|---------|---------|

| Bank | Pin Description  | Number | XC2VP50 | XC2VP70 |

| 2    | IO_L49N_2        | U5     |         |         |

| 2    | IO_L49P_2        | U6     |         |         |

| 2    | IO_L50N_2        | U13    |         |         |

| 2    | IO_L50P_2        | V13    |         |         |

| 2    | IO_L51N_2        | U4     |         |         |

| 2    | IO_L51P_2        | T4     |         |         |

| 2    | IO_L52N_2/VREF_2 | U1     |         |         |

| 2    | IO_L52P_2        | U2     |         |         |

| 2    | IO_L53N_2        | V9     |         |         |

| 2    | IO_L53P_2        | V10    |         |         |

| 2    | IO_L54N_2        | V7     |         |         |

| 2    | IO_L54P_2        | V8     |         |         |

| 2    | IO_L55N_2        | V5     |         |         |

| 2    | IO_L55P_2        | V6     |         |         |

| 2    | IO_L56N_2        | V11    |         |         |

| 2    | IO_L56P_2        | V12    |         |         |

| 2    | IO_L57N_2        | V3     |         |         |

| 2    | IO_L57P_2        | V4     |         |         |

| 2    | IO_L58N_2/VREF_2 | V1     |         |         |

| 2    | IO_L58P_2        | V2     |         |         |

| 2    | IO_L59N_2        | W10    |         |         |

| 2    | IO_L59P_2        | W11    |         |         |

| 2    | IO_L60N_2        | W7     |         |         |

| 2    | IO_L60P_2        | W8     |         |         |

| 2    | IO_L85N_2        | W5     |         |         |

| 2    | IO_L85P_2        | W6     |         |         |

| 2    | IO_L86N_2        | W12    |         |         |

| 2    | IO_L86P_2        | W13    |         |         |

| 2    | IO_L87N_2        | W3     |         |         |

| 2    | IO_L87P_2        | W4     |         |         |

| 2    | IO_L88N_2/VREF_2 | Y7     |         |         |

| 2    | IO_L88P_2        | Y8     |         |         |

| 2    | IO_L89N_2        | W9     |         |         |

| 2    | IO_L89P_2        | Y9     |         |         |

| 2    | IO_L90N_2        | Y3     |         |         |

| 2    | IO_L90P_2        | Y4     |         |         |

|      |                  |        |         |         |

| 3    | IO_L90N_3        | AA7    |         |         |

|      |                  |        |         | 1       |

Table 12: FF1517 — XC2VP50 and XC2VP70

|      | _               | Pin    | No Connects |         |  |

|------|-----------------|--------|-------------|---------|--|

| Bank | Pin Description | Number | XC2VP50     | XC2VP70 |  |

| 2    | VCCO_2          | F8     |             |         |  |

| 2    | VCCO_2          | U7     |             |         |  |

| 2    | VCCO_2          | Y5     |             |         |  |

| 2    | VCCO_2          | N4     |             |         |  |

| 2    | VCCO_2          | J4     |             |         |  |

| 2    | VCCO_2          | E4     |             |         |  |

| 2    | VCCO_2          | U3     |             |         |  |

| 2    | VCCO_2          | E1     |             |         |  |

| 1    | VCCO_1          | N14    |             |         |  |

| 1    | VCCO_1          | K13    |             |         |  |

| 1    | VCCO_1          | F13    |             |         |  |

| 1    | VCCO_1          | P19    |             |         |  |

| 1    | VCCO_1          | P18    |             |         |  |

| 1    | VCCO_1          | P17    |             |         |  |

| 1    | VCCO_1          | K17    |             |         |  |

| 1    | VCCO_1          | F17    |             |         |  |

| 1    | VCCO_1          | P16    |             |         |  |

| 1    | VCCO_1          | N16    |             |         |  |

| 1    | VCCO_1          | P15    |             |         |  |

| 1    | VCCO_1          | N15    |             |         |  |

| 0    | VCCO_0          | K27    |             |         |  |

| 0    | VCCO_0          | F27    |             |         |  |

| 0    | VCCO_0          | N26    |             |         |  |

| 0    | VCCO_0          | P25    |             |         |  |

| 0    | VCCO_0          | N25    |             |         |  |

| 0    | VCCO_0          | P24    |             |         |  |

| 0    | VCCO_0          | N24    |             |         |  |

| 0    | VCCO_0          | P23    |             |         |  |

| 0    | VCCO_0          | K23    |             |         |  |

| 0    | VCCO_0          | F23    |             |         |  |

| 0    | VCCO_0          | P22    |             |         |  |

| 0    | VCCO_0          | P21    |             |         |  |

|      |                 |        |             |         |  |

| N/A  | CCLK            | AJ10   |             |         |  |

| N/A  | PROG_B          | D32    |             |         |  |

| N/A  | DONE            | AJ11   |             |         |  |

| N/A  | MO              | AP31   |             |         |  |

| N/A  | M1              | AJ30   |             |         |  |

Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                 | Pin    | No Connects |         |

|------|-----------------|--------|-------------|---------|

| Bank | Pin Description | Number | XC2VP50     | XC2VP70 |

| N/A  | GNDA18          | AU16   |             |         |

| N/A  | TXPPAD18        | AW18   |             |         |

| N/A  | TXNPAD18        | AW19   |             |         |

| N/A  | VTTXPAD18       | AV19   |             |         |

| N/A  | AVCCAUXTX18     | AV18   |             |         |

| N/A  | AVCCAUXRX19     | AV21   |             |         |

| N/A  | VTRXPAD19       | AV22   |             |         |

| N/A  | RXNPAD19        | AW21   |             |         |

| N/A  | RXPPAD19        | AW22   |             |         |

| N/A  | GNDA19          | AU24   |             |         |

| N/A  | TXPPAD19        | AW23   |             |         |

| N/A  | TXNPAD19        | AW24   |             |         |

| N/A  | VTTXPAD19       | AV24   |             |         |

| N/A  | AVCCAUXTX19     | AV23   |             |         |

| N/A  | AVCCAUXRX20     | AV25   |             |         |

| N/A  | VTRXPAD20       | AV26   |             |         |

| N/A  | RXNPAD20        | AW25   |             |         |

| N/A  | RXPPAD20        | AW26   |             |         |

| N/A  | GNDA20          | AU27   |             |         |

| N/A  | TXPPAD20        | AW27   |             |         |

| N/A  | TXNPAD20        | AW28   |             |         |

| N/A  | VTTXPAD20       | AV28   |             |         |

| N/A  | AVCCAUXTX20     | AV27   |             |         |

| N/A  | AVCCAUXRX21     | AV29   |             |         |

| N/A  | VTRXPAD21       | AV30   |             |         |

| N/A  | RXNPAD21        | AW29   |             |         |

| N/A  | RXPPAD21        | AW30   |             |         |

| N/A  | GNDA21          | AU31   |             |         |

| N/A  | TXPPAD21        | AW31   |             |         |

| N/A  | TXNPAD21        | AW32   |             |         |

| N/A  | VTTXPAD21       | AV32   |             |         |

| N/A  | AVCCAUXTX21     | AV31   |             |         |

| N/A  | AVCCAUXRX23     | AV33   |             |         |

| N/A  | VTRXPAD23       | AV34   |             |         |

| N/A  | RXNPAD23        | AW33   |             |         |

| N/A  | RXPPAD23        | AW34   |             |         |

| N/A  | GNDA23          | AU34   |             |         |

| N/A  | TXPPAD23        | AW35   |             |         |

Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       | on                         |            | No Co                | nnects   |

|------|-----------------------|----------------------------|------------|----------------------|----------|

| Bank | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| N/A  | GND                   |                            | AB18       |                      |          |

| N/A  | GND                   |                            | AB17       |                      |          |

| N/A  | GND                   |                            | AB11       |                      |          |

| N/A  | GND                   |                            | AB8        |                      |          |

| N/A  | GND                   |                            | AB5        |                      |          |

| N/A  | GND                   |                            | AC41       |                      |          |

| N/A  | GND                   |                            | AC26       |                      |          |

| N/A  | GND                   |                            | AC25       |                      |          |

| N/A  | GND                   |                            | AC24       |                      |          |

| N/A  | GND                   |                            | AC23       |                      |          |

| N/A  | GND                   |                            | AC22       |                      |          |

| N/A  | GND                   |                            | AC21       |                      |          |

| N/A  | GND                   |                            | AC20       |                      |          |

| N/A  | GND                   |                            | AC19       |                      |          |

| N/A  | GND                   |                            | AC18       |                      |          |

| N/A  | GND                   |                            | AC17       |                      |          |

| N/A  | GND                   |                            | AC2        |                      |          |

| N/A  | GND                   |                            | AD26       |                      |          |

| N/A  | GND                   |                            | AD25       |                      |          |

| N/A  | GND                   |                            | AD24       |                      |          |

| N/A  | GND                   |                            | AD23       |                      |          |

| N/A  | GND                   |                            | AD22       |                      |          |

| N/A  | GND                   |                            | AD21       |                      |          |

| N/A  | GND                   |                            | AD20       |                      |          |

| N/A  | GND                   |                            | AD19       |                      |          |

| N/A  | GND                   |                            | AD18       |                      |          |

| N/A  | GND                   |                            | AD17       |                      |          |

| N/A  | GND                   |                            | AE37       |                      |          |

| N/A  | GND                   |                            | AE34       |                      |          |

| N/A  | GND                   |                            | AE26       |                      |          |

| N/A  | GND                   |                            | AE25       |                      |          |

| N/A  | GND                   |                            | AE24       |                      |          |

| N/A  | GND                   |                            | AE23       |                      |          |

| N/A  | GND                   |                            | AE22       |                      |          |

| N/A  | GND                   |                            | AE21       |                      |          |

| N/A  | GND                   |                            | AE20       |                      |          |

*Table 14:* **FF1696** — **XC2VP100**

|      |                  |            | No Connects |  |

|------|------------------|------------|-------------|--|

| Bank | Pin Description  | Pin Number | XC2VP100    |  |

| 3    | IO_L56N_3        | AC11       |             |  |

| 3    | IO_L56P_3        | AC12       |             |  |

| 3    | IO_L55N_3        | AD3        |             |  |

| 3    | IO_L55P_3        | AE3        |             |  |

| 3    | IO_L54N_3        | AE1        |             |  |

| 3    | IO_L54P_3        | AE2        |             |  |

| 3    | IO_L53N_3        | AC6        |             |  |

| 3    | IO_L53P_3        | AC7        |             |  |

| 3    | IO_L52N_3        | AF2        |             |  |

| 3    | IO_L52P_3        | AF3        |             |  |

| 3    | IO_L51N_3/VREF_3 | AF6        |             |  |

| 3    | IO_L51P_3        | AG6        |             |  |

| 3    | IO_L50N_3        | AD10       |             |  |

| 3    | IO_L50P_3        | AD11       |             |  |

| 3    | IO_L49N_3        | AG4        |             |  |

| 3    | IO_L49P_3        | AG5        |             |  |

| 3    | IO_L48N_3        | AF4        |             |  |

| 3    | IO_L48P_3        | AG3        |             |  |

| 3    | IO_L47N_3        | AC10       |             |  |

| 3    | IO_L47P_3        | AD9        |             |  |

| 3    | IO_L46N_3        | AG1        |             |  |

| 3    | IO_L46P_3        | AG2        |             |  |

| 3    | IO_L45N_3/VREF_3 | AG7        |             |  |

| 3    | IO_L45P_3        | AH7        |             |  |

| 3    | IO_L44N_3        | AC8        |             |  |

| 3    | IO_L44P_3        | AD7        |             |  |

| 3    | IO_L43N_3        | AH4        |             |  |

| 3    | IO_L43P_3        | AH5        |             |  |

| 3    | IO_L42N_3        | AH1        |             |  |

| 3    | IO_L42P_3        | AH2        |             |  |

| 3    | <br>IO_L41N_3    | AE10       |             |  |

| 3    | IO_L41P_3        | AE11       |             |  |

| 3    | IO_L40N_3        | AJ6        |             |  |

| 3    | IO_L40P_3        | AJ7        |             |  |

| 3    | IO_L39N_3/VREF_3 | AH6        |             |  |

| 3    | IO_L39P_3        | AJ5        |             |  |

| 3    | IO_L38N_3        | AE8        |             |  |

*Table 14:* **FF1696** — **XC2VP100**

|      |                      |            | No Connects |  |

|------|----------------------|------------|-------------|--|

| Bank | Pin Description      | Pin Number | XC2VP100    |  |

| 5    | IO_L10N_5            | AW27       | NC          |  |

| 5    | IO_L10P_5            | AW26       | NC          |  |

| 5    | IO_L45N_5/VREF_5     | AN27       |             |  |

| 5    | IO_L45P_5            | AP27       |             |  |

| 5    | IO_L44N_5            | AU27       |             |  |

| 5    | IO_L44P_5            | AV27       |             |  |

| 5    | IO_L43N_5            | AR27       |             |  |

| 5    | IO_L43P_5            | AR26       |             |  |

| 5    | IO_L39N_5            | AL27       |             |  |

| 5    | IO_L39P_5            | AM27       |             |  |

| 5    | IO_L38N_5            | BA28       |             |  |

| 5    | IO_L38P_5            | BB28       |             |  |

| 5    | IO_L37N_5            | AY28       |             |  |

| 5    | IO_L37P_5            | AY27       |             |  |

| 5    | IO_L87N_5/VREF_5     | AN28       |             |  |

| 5    | IO_L87P_5            | AP28       |             |  |

| 5    | IO_L86N_5            | AU28       |             |  |

| 5    | IO_L86P_5            | AV28       |             |  |

| 5    | IO_L85N_5            | AT28       |             |  |

| 5    | IO_L85P_5            | AT27       |             |  |

| 5    | IO_L84N_5            | AL28       |             |  |

| 5    | IO_L84P_5            | AM28       |             |  |

| 5    | IO_L83_5/No_Pair     | BA29       |             |  |

| 5    | IO_L80_5/No_Pair     | BB29       |             |  |

| 5    | IO_L79N_5            | AY29       |             |  |

| 5    | IO_L79P_5            | AW28       |             |  |

| 5    | IO_L78N_5            | AN29       |             |  |

| 5    | IO_L78P_5            | AP29       |             |  |

| 5    | IO_L77N_5            | AU29       |             |  |

| 5    | IO_L77P_5            | AV29       |             |  |

| 5    | IO_L76N_5            | AT29       |             |  |

| 5    | <br>IO_L76P_5        | AR28       |             |  |

| 5    | <br>IO_L36N_5/VREF_5 | AL29       |             |  |

| 5    | <br>IO_L36P_5        | AM29       |             |  |

| 5    | IO_L35N_5            | AY30       |             |  |

| 5    | IO_L35P_5            | BA30       |             |  |

| 5    | IO_L34N_5            | AT30       |             |  |

*Table 14:* **FF1696** — **XC2VP100**

|      |                  |            | No Connects |

|------|------------------|------------|-------------|

| Bank | Pin Description  | Pin Number | XC2VP100    |

| 7    | IO_L08N_7        | N35        |             |

| 7    | IO_L07P_7        | G41        |             |

| 7    | IO_L07N_7        | G42        |             |

| 7    | IO_L72P_7        | G39        |             |

| 7    | IO_L72N_7        | G40        |             |

| 7    | IO_L71P_7        | P32        |             |

| 7    | IO_L71N_7        | P33        |             |

| 7    | IO_L70P_7        | F38        |             |

| 7    | IO_L70N_7/VREF_7 | G38        |             |

| 7    | IO_L69P_7        | F37        |             |

| 7    | IO_L69N_7        | G37        |             |

| 7    | IO_L68P_7        | N32        |             |

| 7    | IO_L68N_7        | N33        |             |

| 7    | IO_L67P_7        | G35        |             |

| 7    | IO_L67N_7        | G36        |             |

| 7    | IO_L66P_7        | F41        |             |

| 7    | IO_L66N_7        | F42        |             |

| 7    | IO_L65P_7        | P31        |             |

| 7    | IO_L65N_7        | N31        |             |

| 7    | IO_L64P_7        | E41        |             |

| 7    | IO_L64N_7/VREF_7 | F40        |             |

| 7    | IO_L63P_7        | E36        |             |

| 7    | IO_L63N_7        | F36        |             |

| 7    | IO_L62P_7        | M34        |             |

| 7    | IO_L62N_7        | M35        |             |

| 7    | IO_L61P_7        | E35        |             |

| 7    | IO_L61N_7        | F35        |             |

| 7    | IO_L84P_7        | D40        |             |

| 7    | IO_L84N_7        | E40        |             |

| 7    | <br>IO_L83P_7    | L34        |             |

| 7    | IO_L83N_7        | L35        |             |

| 7    | IO_L82P_7        | D39        |             |

| 7    | IO_L82N_7/VREF_7 | E39        |             |

| 7    | IO_L81P_7        | D38        |             |

| 7    | IO_L81N_7        | E37        |             |

| 7    | IO_L80P_7        | K34        |             |

| 7    | IO_L80N_7        | J35        |             |

*Table 14:* **FF1696** — **XC2VP100**

|      |                 |            | No Connects |

|------|-----------------|------------|-------------|

| Bank | Pin Description | Pin Number | XC2VP100    |

| 2    | VCCO_2          | F4         |             |

| 1    | VCCO_1          | R21        |             |

| 1    | VCCO_1          | P21        |             |

| 1    | VCCO_1          | R20        |             |

| 1    | VCCO_1          | P20        |             |

| 1    | VCCO_1          | R19        |             |

| 1    | VCCO_1          | P19        |             |

| 1    | VCCO_1          | R18        |             |

| 1    | VCCO_1          | P18        |             |

| 1    | VCCO_1          | H18        |             |

| 1    | VCCO_1          | D18        |             |

| 1    | VCCO_1          | P17        |             |

| 1    | VCCO_1          | H14        |             |

| 1    | VCCO_1          | D14        |             |

| 1    | VCCO_1          | M13        |             |

| 1    | VCCO_1          | D10        |             |

| 0    | VCCO_0          | D33        |             |

| 0    | VCCO_0          | M30        |             |

| 0    | VCCO_0          | H29        |             |

| 0    | VCCO_0          | D29        |             |

| 0    | VCCO_0          | P26        |             |

| 0    | VCCO_0          | R25        |             |

| 0    | VCCO_0          | P25        |             |

| 0    | VCCO_0          | H25        |             |

| 0    | VCCO_0          | D25        |             |

| 0    | VCCO_0          | R24        |             |

| 0    | VCCO_0          | P24        |             |

| 0    | VCCO_0          | R23        |             |

| 0    | VCCO_0          | P23        |             |

| 0    | VCCO_0          | R22        |             |

| 0    | VCCO_0          | P22        |             |

|      |                 |            |             |

| N/A  | CCLK            | AM10       |             |

| N/A  | PROG_B          | J33        |             |

| N/A  | DONE            | AN10       |             |

| N/A  | MO              | AP33       |             |

| N/A  | M1              | AN33       |             |