# E·XFL

# AMD Xilinx - XC2VP40-6FF1148I Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                     |

|--------------------------------|--------------------------------------------------------------|

| Number of LABs/CLBs            | 4848                                                         |

| Number of Logic Elements/Cells | 43632                                                        |

| Total RAM Bits                 | 3538944                                                      |

| Number of I/O                  | 804                                                          |

| Number of Gates                | -                                                            |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                           |

| Package / Case                 | 1148-BBGA, FCBGA                                             |

| Supplier Device Package        | 1148-FCPBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2vp40-6ff1148i |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- HSTL (1.5V and 1.8V, Class I, II, III, and IV)

- SSTL (1.8V and 2.5V, Class I and II)

The DCI I/O feature automatically provides on-chip termination for each single-ended I/O standard.

The IOB elements also support the following differential signaling I/O standards:

- LVDS and Extended LVDS (2.5V)

- BLVDS (Bus LVDS)

- ULVDS

- LDT

- LVPECL (2.5V)

Two adjacent pads are used for each differential pair. Two or four IOBs connect to one switch matrix to access the routing resources. On-chip differential termination is available for LVDS, LVDS Extended, ULVDS, and LDT standards.

# Configurable Logic Blocks (CLBs)

CLB resources include four slices and two 3-state buffers. Each slice is equivalent and contains:

- Two function generators (F & G)

- Two storage elements

- Arithmetic logic gates

- Large multiplexers

- Wide function capability

- Fast carry look-ahead chain

- Horizontal cascade chain (OR gate)

The function generators F & G are configurable as 4-input look-up tables (LUTs), as 16-bit shift registers, or as 16-bit distributed SelectRAM+ memory.

In addition, the two storage elements are either edge-triggered D-type flip-flops or level-sensitive latches.

Each CLB has internal fast interconnect and connects to a switch matrix to access general routing resources.

# Block SelectRAM+ Memory

The block SelectRAM+ memory resources are 18 Kb of True Dual-Port RAM, programmable from 16K x 1 bit to 512 x 36 bit, in various depth and width configurations. Each port is totally synchronous and independent, offering three "read-during-write" modes. Block SelectRAM+ memory is cascadable to implement large embedded storage blocks. Supported memory configurations for dual-port and single-port modes are shown in Table 2.

## Table 2: Dual-Port and Single-Port Configurations

| 16K x 1 bit | 4K x 4 bits | 1K x 18 bits  |

|-------------|-------------|---------------|

| 8K x 2 bits | 2K x 9 bits | 512 x 36 bits |

# 18 X 18 Bit Multipliers

A multiplier block is associated with each SelectRAM+ memory block. The multiplier block is a dedicated 18 x 18-bit 2s complement signed multiplier, and is optimized for operations based on the block SelectRAM+ content on one port. The 18 x 18 multiplier can be used independently of the block SelectRAM+ resource. Read/multiply/accumulate operations and DSP filter structures are extremely efficient.

Both the SelectRAM+ memory and the multiplier resource are connected to four switch matrices to access the general routing resources.

# Global Clocking

The DCM and global clock multiplexer buffers provide a complete solution for designing high-speed clock schemes.

Up to twelve DCM blocks are available. To generate deskewed internal or external clocks, each DCM can be used to eliminate clock distribution delay. The DCM also provides 90-, 180-, and 270-degree phase-shifted versions of its output clocks. Fine-grained phase shifting offers high-resolution phase adjustments in increments of  $1/_{256}$  of the clock period. Very flexible frequency synthesis provides a clock output frequency equal to a fractional or integer multiple of the input clock frequency. For exact timing parameters, see Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics.

Virtex-II Pro devices have 16 global clock MUX buffers, with up to eight clock nets per quadrant. Each clock MUX buffer can select one of the two clock inputs and switch glitch-free from one clock to the other. Each DCM can send up to four of its clock outputs to global clock buffers on the same edge. Any global clock pin can drive any DCM on the same edge.

# **Routing Resources**

The IOB, CLB, block SelectRAM+, multiplier, and DCM elements all use the same interconnect scheme and the same access to the global routing matrix. Timing models are shared, greatly improving the predictability of the performance of high-speed designs.

There are a total of 16 global clock lines, with eight available per quadrant. In addition, 24 vertical and horizontal long lines per row or column, as well as massive secondary and local routing resources, provide fast interconnect. Virtex-II Pro buffered interconnects are relatively unaffected by net fanout, and the interconnect layout is designed to minimize crosstalk.

Horizontal and vertical routing resources for each row or column include:

- 24 long lines

- 120 hex lines

- 40 double lines

- 16 direct connect lines (total in all four directions)

## **Boundary Scan**

Boundary-scan instructions and associated data registers support a standard methodology for accessing and configuring Virtex-II Pro devices, complying with IEEE standards 1149.1 and 1532. A system mode and a test mode are

# Virtex-II Pro / Virtex-II Pro X Device/Package Combinations and Maximum I/Os

Offerings include ball grid array (BGA) packages with 1.0 mm pitch. In addition to traditional wire-bond interconnect (FG/FGG packages), flip-chip interconnect (FF packages) is used in some of the BGA offerings. Flip-chip interconnect construction supports more I/Os than are possible in wire-bond versions of similar packages, providing a high pin count and excellent power dissipation.

The device/package combination table (Table 3) details the maximum number of user I/Os and RocketIO / RocketIO X MGTs for each device and package using wire-bond or flip-chip technology.

The FF1148 and FF1696 packages have no RocketIO transceivers bonded out. Extra SelectIO-Ultra resources occupy available pins in these packages, resulting in a higher user I/O count. These packages are available for the XC2VP40, XC2VP50, and XC2VP100 devices only.

The I/Os per package count includes all user I/Os except the 15 control pins (CCLK, DONE, M0, M1, M2, PROG\_B, PWRDWN\_B, TCK, TDI, TDO, TMS, HSWAP\_EN, DXN, DXP, and RSVD), VBATT, and the RocketIO / RocketIO X transceiver pins.

| Package <sup>(1)</sup> | FG256/<br>FGG256 | FG456/<br>FGG456 | FG676   | FF672   | FF896                | FF1152  | FF1148   | FF1517  | FF1704      | FF1696                 |

|------------------------|------------------|------------------|---------|---------|----------------------|---------|----------|---------|-------------|------------------------|

| Pitch (mm)             | 1.00             | 1.00             | 1.00    | 1.00    | 1.00                 | 1.00    | 1.00     | 1.00    | 1.00        | 1.00                   |

| Size (mm)              | 17 x 17          | 23 x 23          | 26 x 26 | 27 x 27 | 31 x 31              | 35 x 35 | 35 x 35  | 40 x 40 | 42.5 x 42.5 | 42.5 x 42.5            |

| XC2VP2                 | 140/4            | 156/4            |         | 204/4   |                      |         |          |         |             |                        |

| XC2VP4                 | 140/4            | 248/4            |         | 348/4   |                      |         |          |         |             |                        |

| XC2VP7                 |                  | 248/8            |         | 396/8   | 396/8                |         |          |         |             |                        |

| XC2VP20                |                  |                  | 404/8   |         | 556/8                | 564/8   |          |         |             |                        |

| XC2VPX20               |                  |                  |         |         | 552/8 <sup>(2)</sup> |         |          |         |             |                        |

| XC2VP30                |                  |                  | 416/8   |         | 556/8                | 644/8   |          |         |             |                        |

| XC2VP40                |                  |                  | 416/8   |         |                      | 692/12  | 804/0(3) |         |             |                        |

| XC2VP50                |                  |                  |         |         |                      | 692/16  | 812/0(3) | 852/16  |             |                        |

| XC2VP70                |                  |                  |         |         |                      |         |          | 964/16  | 996/20      |                        |

| XC2VPX70               |                  |                  |         |         |                      |         |          |         | 992/20(2)   |                        |

| XC2VP100               |                  |                  |         |         |                      |         |          |         | 1,040/20    | 1,164/0 <sup>(3)</sup> |

## Table 3: Virtex-II Pro Device/Package Combinations and Maximum Number of Available I/Os

#### Notes:

1. Wirebond packages FG256, FG456, and FG676 are also available in Pb-free versions FGG256, FGG456, and FGG676. See Virtex-II Pro Ordering Examples for details on how to order.

2. Virtex-II Pro X device is equipped with RocketIO X transceiver cores.

3. The RocketIO transceivers in devices in the FF1148 and FF1696 packages are not bonded out to the package pins.

# Maximum Performance

Maximum performance of the RocketIO / RocketIO X transceiver and the PowerPC processor block varies, depending on package style and speed grade. See Table 4 for details. Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics contains the rest of the FPGA fabric performance parameters.

## Table 4: Maximum RocketIO / RocketIO X Transceiver and Processor Block Performance

|                                      |                          | Speed Grade         |                     |       |  |

|--------------------------------------|--------------------------|---------------------|---------------------|-------|--|

| Device                               | <b>-7</b> <sup>(1)</sup> | -6                  | -5                  | Units |  |

| RocketIO X Transceiver FlipChip (FF) | N/A                      | 6.25 <sup>(3)</sup> | 4.25 <sup>(3)</sup> | Gb/s  |  |

| RocketIO Transceiver FlipChip (FF)   | 3.125                    | 3.125               | 2.0                 | Gb/s  |  |

| RocketIO Transceiver Wirebond (FG)   | 2.5                      | 2.5                 | 2.0                 | Gb/s  |  |

| PowerPC Processor Block              | 400 <sup>(2)</sup>       | 350 <sup>(2)</sup>  | 300                 | MHz   |  |

#### Notes:

1. -7 speed grade devices are not available in Industrial grade.

IMPORTANT! When CPMC405CLOCK runs at speeds greater than 350 MHz in -7 Commercial grade dual-processor devices, or greater than 300 MHz in -6 Industrial grade dual-processor devices, users must implement the technology presented in <u>XAPP755</u>, "PowerPC 405 Clock Macro for -7(C) and -6(I) Speed Grade Dual-Processor Devices." Refer to Table 1 to identify dual-processor devices.

3. XC2VPX70 is only available at fixed 4.25 Gb/s baud rate.

CRC may adjust certain trailing bytes to generate the required running disparity at the end of the packet.

On the receiver side, the CRC logic verifies the received CRC value, supporting the same standards as above.

The CRC logic also supports a user mode, with a simple data packet stucture beginning and ending with user-defined SOP and EOP characters.

## Loopback

In order to facilitate testing without having the need to either apply patterns or measure data at GHz rates, two programmable loop-back features are available.

One option, serial loopback, places the gigabit transceiver into a state where transmit data is directly fed back to the receiver. An important point to note is that the feedback path is at the output pads of the transmitter. This tests the entirety of the transmitter and receiver.

The second option, parallel loopback, checks the digital circuitry. When parallel loopback is enabled, the serial loopback path is disabled. However, the transmitter outputs remain active, and data can be transmitted. If TXINHIBIT is asserted, TXP is forced to 0 until TXINHIBIT is de-asserted.

#### Reset

The receiver and transmitter have their own synchronous reset inputs. The transmitter reset recenters the transmission FIFO, and resets all transmitter registers and the 8B/10B decoder. The receiver reset recenters the receiver elastic buffer, and resets all receiver registers and the 8B/10B encoder. Neither reset has any effect on the PLLs.

#### Power

All RocketIO transceivers in the FPGA, whether instantiated in the design or not, must be connected to power and ground. Unused transceivers can be powered by any 2.5V source, and passive filtering is not required.

## Power Down

The Power Down module is controlled by the transceiver's POWERDOWN input pin. The Power Down pin on the FPGA package has no effect on the transceiver.

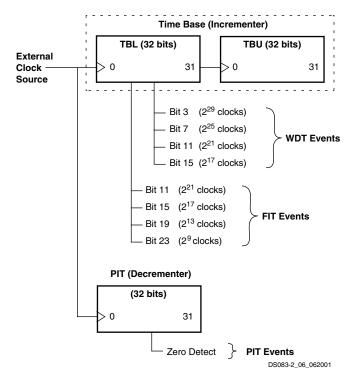

Figure 17: Relationship of Timer Facilities to Base Clock

# Interrupts

The PPC405 provides an interface to an interrupt controller that is logically outside the PPC405 core. This controller combines the asynchronous interrupt inputs and presents them to the embedded core as a single interrupt signal. The sources of asynchronous interrupts are external signals, the JTAG/debug unit, and any implemented peripherals.

# **Debug Logic**

All architected resources on the embedded PPC405 core can be accessed through the debug logic. Upon a debug event, the PPC405 core provides debug information to an external debug tool. Three different types of tools are supported depending on the debug mode: ROM monitors, JTAG debuggers, and instruction trace tools.

In internal debug mode, a debug event enables exception-handling software at a dedicated interrupt vector to take

over the CPU core and communicate with a debug tool. The debug tool has read-write access to all registers and can set hardware or software breakpoints. ROM monitors typically use the internal debug mode.

In external debug mode, the CPU core enters stop state (stops instruction execution) when a debug event occurs. This mode offers a debug tool read-write access to all registers in the PPC405 core. Once the CPU core is in stop state, the debug tool can start the CPU core, step an instruction, freeze the timers, or set hardware or software break points. In addition to CPU core control, the debug logic is capable of writing instructions into the instruction cache, eliminating the need for external memory during initial board bring-up. Communication to a debug tool using external debug mode is through the JTAG port.

Debug wait mode offers the same functionality as external debug mode with one exception. In debug wait mode, the CPU core goes into wait state instead of stop state after a debug event. Wait state is identical to stop state until an interrupt occurs. In wait state, the PPC405 core can vector to an exception handler, service an interrupt and return to wait state. This mode is particularly useful when debugging real time control systems.

Real-time trace debug mode is always enabled. The debug logic continuously broadcasts instruction trace information to the trace port. When a debug event occurs, the debug logic signals an external debug tool to save instruction trace information before and after the event. The number of instructions traced depends on the trace tool.

Debug events signal the debug logic to stop the CPU core, put the CPU core in debug wait state, cause a debug exception or save instruction trace information.

# **Big Endian and Little Endian Support**

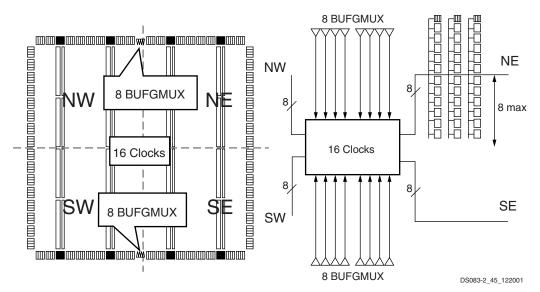

The embedded PPC405 core supports big endian or little endian byte ordering for instructions stored in external memory. Since the PowerPC architecture is big endian internally, the ICU rearranges the instructions stored as little endian into the big endian format. Therefore, the instruction cache always contains instructions in big endian format so that the byte ordering is correct for the execution unit. This feature allows the 405 core to be used in systems designed to function in a little endian environment. Figure 57 shows clock distribution in Virtex-II Pro devices.

In each quadrant, up to eight clocks are organized in clock rows. A clock row supports up to 16 CLB rows (eight up and eight down). To reduce power consumption, any unused clock branches remain static.

Figure 57: Virtex-II Pro Clock Distribution

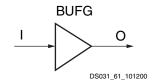

Global clocks are driven by dedicated clock buffers (BUFG), which can also be used to gate the clock (BUFGCE) or to multiplex between two independent clock inputs (BUFGMUX).

The most common configuration option of this element is as a buffer. A BUFG function in this (global buffer) mode, is shown in Figure 58.

Figure 58: Virtex-II Pro BUFG Function

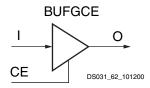

The Virtex-II Pro global clock buffer BUFG can also be configured as a clock enable/disable circuit (Figure 59), as well as a two-input clock multiplexer (Figure 60). A functional description of these two options is provided below. Each of them can be used in either of two modes, selected by configuration: rising clock edge or falling clock edge.

This section describes the rising clock edge option. For the opposite option, falling clock edge, just change all "rising" references to "falling" and all "High" references to "Low", except for the description of the CE and S levels. The rising clock edge option uses the BUFGCE and BUFGMUX primitives. The falling clock edge option uses the BUFGCE\_1 and BUFGMUX\_1 primitives.

# BUFGCE

If the CE input is active (High) prior to the incoming rising clock edge, this Low-to-High-to-Low clock pulse passes through the clock buffer. Any level change of CE during the incoming clock High time has no effect.

Figure 59: Virtex-II Pro BUFGCE Function

If the CE input is inactive (Low) prior to the incoming rising clock edge, the following clock pulse does not pass through the clock buffer, and the output stays Low. Any level change of CE during the incoming clock High time has no effect. CE must not change during a short setup window just prior to the rising clock edge on the BUFGCE input I. Violating this setup time requirement can result in an undefined runt pulse output.

# BUFGMUX

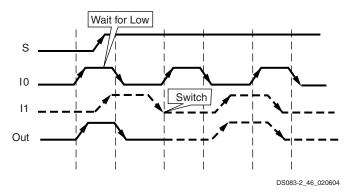

BUFGMUX can switch between two unrelated, even asynchronous clocks. Basically, a Low on S selects the  $I_0$  input, a High on S selects the  $I_1$  input. Switching from one clock to the other is done in such a way that the output High and Low time is never shorter than the shortest High or Low time of either input clock. As long as the presently selected clock is High, any level change of S has no effect.

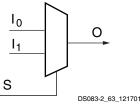

Figure 60: Virtex-II Pro BUFGMUX Function

If the presently selected clock is Low while S changes, or if it goes Low after S has changed, the output is kept Low until the other ("to-be-selected") clock has made a transition from High to Low. At that instant, the new clock starts driving the output.

The two clock inputs can be asynchronous with regard to each other, and the S input can change at any time, except for a short setup time prior to the rising edge of the presently selected clock (I0 or I1). Violating this setup time requirement can result in an undefined runt pulse output.

All Virtex-II Pro devices have 16 global clock multiplexer buffers.

Figure 61 shows a switchover from I0 to I1.

## Figure 61: Clock Multiplexer Waveform Diagram

- The current clock is CLK0.

- S is activated High.

- If CLK0 is currently High, the multiplexer waits for CLK0 to go Low.

- Once CLK0 is Low, the multiplexer output stays Low until CLK1 transitions High to Low.

- When CLK1 transitions from High to Low, the output switches to CLK1.

- No glitches or short pulses can appear on the output.

# Local Clocking

In addition to global clocks, there are local clock resources in the Virtex-II Pro devices. There are more than 72 local clocks in the Virtex-II Pro family. These resources can be used for many different applications, including but not limited to memory interfaces. For example, even using only the left and right I/O banks, Virtex-II Pro FPGAs can support up to 50 local clocks for DDR SDRAM. These interfaces can operate beyond 200 MHz on Virtex-II Pro devices.

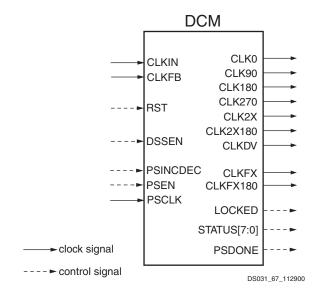

# **Digital Clock Manager (DCM)**

The Virtex-II Pro DCM offers a wide range of powerful clock management features.

- **Clock De-skew**: The DCM generates new system clocks (either internally or externally to the FPGA), which are phase-aligned to the input clock, thus eliminating clock distribution delays.

- Frequency Synthesis: The DCM generates a wide range of output clock frequencies, performing very flexible clock multiplication and division.

- **Phase Shifting**: The DCM provides both coarse phase shifting and fine-grained phase shifting with dynamic phase shift control.

The DCM utilizes fully digital delay lines allowing robust high-precision control of clock phase and frequency. It also utilizes fully digital feedback systems, operating dynamically to compensate for temperature and voltage variations during operation.

Up to four of the nine DCM clock outputs can drive inputs to global clock buffers or global clock multiplexer buffers simultaneously (see Figure 62). All DCM clock outputs can simultaneously drive general routing resources, including routes to output buffers.

Figure 62: Digital Clock Manager

The DCM can be configured to delay the completion of the Virtex-II Pro configuration process until after the DCM has achieved lock. This guarantees that the chip does not begin operating until after the system clocks generated by the DCM have stabilized.

## Table 65: Package Skew

| Description                 | Symbol               | Device/Package | Value                                                  | Units |

|-----------------------------|----------------------|----------------|--------------------------------------------------------|-------|

| Package Skew <sup>(1)</sup> | T <sub>PKGSKEW</sub> | XC2VP2FF672    | 104                                                    | ps    |

|                             |                      | XC2VP4FF672    | 102                                                    | ps    |

|                             |                      | XC2VP7FF672    | 92                                                     | ps    |

|                             |                      | XC2VP7FF896    | 101                                                    | ps    |

|                             |                      | XC2VP20FF896   | 93                                                     | ps    |

|                             |                      | XC2VPX20FF896  | 93                                                     | ps    |

|                             |                      | XC2VP20FF1152  | 106                                                    | ps    |

|                             |                      | XC2VP30FF896   | 86                                                     | ps    |

|                             |                      | XC2VP30FF1152  | 112                                                    | ps    |

|                             |                      | XC2VP40FF1152  | 92                                                     | ps    |

|                             |                      | XC2VP40FF1148  | 102<br>92<br>101<br>93<br>93<br>93<br>106<br>86<br>112 | ps    |

|                             |                      | XC2VP50FF1152  | 88                                                     | ps    |

|                             |                      | XC2VP50FF1148  | 101                                                    | ps    |

|                             |                      | XC2VP50FF1517  | 97                                                     | ps    |

|                             |                      | XC2VP70FF1517  | 95                                                     | ps    |

|                             |                      | XC2VP70FF1704  | 101                                                    | ps    |

|                             |                      | XC2VPX70FF1704 | 101                                                    | ps    |

|                             |                      | XC2VP100FF1704 | 86                                                     | ps    |

|                             |                      | XC2VP100FF1696 | 100                                                    | ps    |

Notes:

1. These values represent the worst-case skew between any two balls of the package: shortest flight time to longest flight time from Pad to Ball (7.1ps per mm).

2. Package trace length information is available for these device/package combinations. This information can be used to deskew the package.

#### Table 66: Sample Window

|                                                |                   |        | Speed Grade   -7 -6 -5   0.50 0.50 0.50 |      | •    |       |

|------------------------------------------------|-------------------|--------|-----------------------------------------|------|------|-------|

| Description                                    | Symbol            | Device | -7                                      | -6   | -5   | Units |

| Sampling Error at Receiver Pins <sup>(1)</sup> | T <sub>SAMP</sub> | All    | 0.50                                    | 0.50 | 0.50 | ns    |

Notes:

1. This parameter indicates the total sampling error of Virtex-II Pro DDR input registers across voltage, temperature, and process. The characterization methodology uses the DCM to capture the DDR input registers' edges of operation.

- 2. These measurements include:

- CLK0 and CLK180 DCM jitter

- Worst-case duty-cycle distortion, T<sub>DCD\_CLK180</sub>

- DCM accuracy (phase offset)

- DCM phase shift resolution

These measurements do not include package or clock tree skew.

# Table 6: FG456/FGG456 — XC2VP2, XC2VP4, and XC2VP7

|      |                                    |            | No Connects |        |        |  |

|------|------------------------------------|------------|-------------|--------|--------|--|

| Bank | Pin Description                    | Pin Number | XC2VP2      | XC2VP4 | XC2VP7 |  |

| 3    | IO_L49N_3                          | T22        | NC          |        |        |  |

| 3    | IO_L49P_3                          | T21        | NC          |        |        |  |

| 3    | IO_L48N_3                          | T20        | NC          |        |        |  |

| 3    | IO_L48P_3                          | T19        | NC          |        |        |  |

| 3    | IO_L47N_3                          | T18        | NC          |        |        |  |

| 3    | IO_L47P_3                          | U18        | NC          |        |        |  |

| 3    | IO_L45N_3/VREF_3                   | U22        | NC          |        |        |  |

| 3    | IO_L45P_3                          | U21        | NC          |        |        |  |

| 3    | IO_L43N_3                          | U20        | NC          |        |        |  |

| 3    | IO_L43P_3                          | U19        | NC          |        |        |  |

| 3    | IO_L06N_3                          | V22        |             |        |        |  |

| 3    | IO_L06P_3                          | V21        |             |        |        |  |

| 3    | IO_L05N_3                          | V20        |             |        |        |  |

| 3    | IO_L05P_3                          | V19        |             |        |        |  |

| 3    | IO_L03N_3/VREF_3                   | W22        |             |        |        |  |

| 3    | IO_L03P_3                          | W21        |             |        |        |  |

| 3    | IO_L02N_3                          | Y22        |             |        |        |  |

| 3    | IO_L02P_3                          | Y21        |             |        |        |  |

| 3    | IO_L01N_3/VRP_3                    | AA22       |             |        |        |  |

| 3    | IO_L01P_3/VRN_3                    | AB21       |             |        |        |  |

|      |                                    |            |             |        |        |  |

| 4    | IO_L01N_4/BUSY/DOUT <sup>(1)</sup> | W18        |             |        |        |  |

| 4    | IO_L01P_4/INIT_B                   | W17        |             |        |        |  |

| 4    | IO_L02N_4/D0/DIN <sup>(1)</sup>    | V17        |             |        |        |  |

| 4    | IO_L02P_4/D1                       | V16        |             |        |        |  |

| 4    | IO_L03N_4/D2                       | W16        |             |        |        |  |

| 4    | IO_L03P_4/D3                       | Y16        |             |        |        |  |

| 4    | IO_L05_4/No_Pair                   | V15        |             |        |        |  |

| 4    | IO_L06N_4/VRP_4                    | W15        |             |        |        |  |

| 4    | IO_L06P_4/VRN_4                    | Y15        |             |        |        |  |

| 4    | IO_L07N_4                          | U14        |             |        |        |  |

| 4    | <br>IO_L07P_4/VREF_4               | V14        |             |        |        |  |

| 4    | IO_L09N_4                          | W14        |             |        |        |  |

| 4    | IO_L09P_4/VREF_4                   | W13        |             |        |        |  |

| 4    | IO_L67N_4                          | U13        |             |        |        |  |

| 4    | IO_L67P_4                          | V13        |             |        |        |  |

| 4    | IO_L69N_4                          | Y13        |             |        |        |  |

# Table 6: FG456/FGG456 — XC2VP2, XC2VP4, and XC2VP7

|      |                  |            |        | No Connects |        |

|------|------------------|------------|--------|-------------|--------|

| Bank | Pin Description  | Pin Number | XC2VP2 | XC2VP4      | XC2VP7 |

| 7    | IO_L88N_7/VREF_7 | L5         |        |             |        |

| 7    | IO_L86P_7        | L6         |        |             |        |

| 7    | IO_L86N_7        | K6         |        |             |        |

| 7    | IO_L85P_7        | K1         |        |             |        |

| 7    | IO_L85N_7        | K2         |        |             |        |

| 7    | IO_L60P_7        | K3         | NC     |             |        |

| 7    | IO_L60N_7        | K4         | NC     |             |        |

| 7    | IO_L58P_7        | K5         | NC     |             |        |

| 7    | IO_L58N_7/VREF_7 | J5         | NC     |             |        |

| 7    | IO_L56P_7        | J1         | NC     |             |        |

| 7    | IO_L56N_7        | J2         | NC     |             |        |

| 7    | IO_L55P_7        | J3         | NC     |             |        |

| 7    | IO_L55N_7        | J4         | NC     |             |        |

| 7    | IO_L54P_7        | J6         | NC     |             |        |

| 7    | IO_L54N_7        | H5         | NC     |             |        |

| 7    | IO_L52P_7        | H1         | NC     |             |        |

| 7    | IO_L52N_7/VREF_7 | H2         | NC     |             |        |

| 7    | IO_L50P_7        | H3         | NC     |             |        |

| 7    | IO_L50N_7        | H4         | NC     |             |        |

| 7    | IO_L49P_7        | G1         | NC     |             |        |

| 7    | IO_L49N_7        | G2         | NC     |             |        |

| 7    | IO_L48P_7        | G3         | NC     |             |        |

| 7    | IO_L48N_7        | G4         | NC     |             |        |

| 7    | IO_L46P_7        | G5         | NC     |             |        |

| 7    | IO_L46N_7/VREF_7 | F5         | NC     |             |        |

| 7    | IO_L43P_7        | F1         | NC     |             |        |

| 7    | IO_L43N_7        | F2         | NC     |             |        |

| 7    | IO_L06P_7        | F3         |        |             |        |

| 7    | IO_L06N_7        | F4         |        |             |        |

| 7    | IO_L04P_7        | E1         |        |             |        |

| 7    | IO_L04N_7/VREF_7 | E2         |        |             |        |

| 7    | IO_L03P_7        | E3         |        |             |        |

| 7    | IO_L03N_7        | E4         |        |             |        |

| 7    | IO_L02P_7        | D1         |        |             |        |

| 7    | IO_L02N_7        | D2         |        |             |        |

| 7    | IO_L01P_7/VRN_7  | C1         |        |             |        |

| 7    | IO_L01N_7/VRP_7  | C2         |        |             |        |

# Table 6: FG456/FGG456 — XC2VP2, XC2VP4, and XC2VP7

|      |                 |            | No Connects |        |        |  |

|------|-----------------|------------|-------------|--------|--------|--|

| Bank | Pin Description | Pin Number | XC2VP2      | XC2VP4 | XC2VP7 |  |

| N/A  | AVCCAUXTX18     | AA14       |             |        |        |  |

| N/A  | AVCCAUXRX19     | AA10       |             |        |        |  |

| N/A  | VTRXPAD19       | AA9        |             |        |        |  |

| N/A  | RXNPAD19        | AB10       |             |        |        |  |

| N/A  | RXPPAD19        | AB9        |             |        |        |  |

| N/A  | GNDA19          | Y9         |             |        |        |  |

| N/A  | TXPPAD19        | AB8        |             |        |        |  |

| N/A  | TXNPAD19        | AB7        |             |        |        |  |

| N/A  | VTTXPAD19       | AA7        |             |        |        |  |

| N/A  | AVCCAUXTX19     | AA8        |             |        |        |  |

| N/A  | AVCCAUXRX21     | AA6        | NC          | NC     |        |  |

| N/A  | VTRXPAD21       | AA5        | NC          | NC     |        |  |

| N/A  | RXNPAD21        | AB6        | NC          | NC     |        |  |

| N/A  | RXPPAD21        | AB5        | NC          | NC     |        |  |

| N/A  | GNDA21          | Y6         | NC          | NC     |        |  |

| N/A  | TXPPAD21        | AB4        | NC          | NC     |        |  |

| N/A  | TXNPAD21        | AB3        | NC          | NC     |        |  |

| N/A  | VTTXPAD21       | AA3        | NC          | NC     |        |  |

| N/A  | AVCCAUXTX21     | AA4        | NC          | NC     |        |  |

|      |                 |            |             |        |        |  |

| N/A  | VCCINT          | U6         |             |        |        |  |

| N/A  | VCCINT          | U17        |             |        |        |  |

| N/A  | VCCINT          | Т8         |             |        |        |  |

| N/A  | VCCINT          | T7         |             |        |        |  |

| N/A  | VCCINT          | T16        |             |        |        |  |

| N/A  | VCCINT          | T15        |             |        |        |  |

| N/A  | VCCINT          | R7         |             |        |        |  |

| N/A  | VCCINT          | R16        |             |        |        |  |

| N/A  | VCCINT          | H7         |             |        |        |  |

| N/A  | VCCINT          | H16        |             |        |        |  |

| N/A  | VCCINT          | G8         |             |        |        |  |

| N/A  | VCCINT          | G7         |             |        |        |  |

| N/A  | VCCINT          | G16        |             |        |        |  |

| N/A  | VCCINT          | G15        |             |        |        |  |

| N/A  | VCCINT          | F6         |             |        |        |  |

| N/A  | VCCINT          | F17        |             |        |        |  |

| N/A  | VCCAUX          | M22        |             |        |        |  |

# Table 7: FG676/FGG676 — XC2VP20, XC2VP30, and XC2VP40

|      |                  |            |         | No Connects | 6       |

|------|------------------|------------|---------|-------------|---------|

| Bank | Pin Description  | Pin Number | XC2VP20 | XC2VP30     | XC2VP40 |

| 4    | IO_L54N_4        | V15        |         |             |         |

| 4    | IO_L54P_4        | W15        |         |             |         |

| 4    | IO_L55N_4        | Y15        |         |             |         |

| 4    | IO_L55P_4        | AA15       |         |             |         |

| 4    | IO_L57N_4        | AB15       |         |             |         |

| 4    | IO_L57P_4/VREF_4 | AA14       |         |             |         |

| 4    | IO_L67N_4        | AC15       |         |             |         |

| 4    | IO_L67P_4        | AD15       |         |             |         |

| 4    | IO_L69N_4        | V14        |         |             |         |

| 4    | IO_L69P_4/VREF_4 | W14        |         |             |         |

| 4    | IO_L74N_4/GCLK3S | AB14       |         |             |         |

| 4    | IO_L74P_4/GCLK2P | AC14       |         |             |         |

| 4    | IO_L75N_4/GCLK1S | AD14       |         |             |         |

| 4    | IO_L75P_4/GCLK0P | AE14       |         |             |         |

|      |                  |            |         | L           |         |

| 5    | IO_L75N_5/GCLK7S | AE13       |         |             |         |

| 5    | IO_L75P_5/GCLK6P | AD13       |         |             |         |

| 5    | IO_L74N_5/GCLK5S | AC13       |         |             |         |

| 5    | IO_L74P_5/GCLK4P | AB13       |         |             |         |

| 5    | IO_L69N_5/VREF_5 | W13        |         |             |         |

| 5    | IO_L69P_5        | V13        |         |             |         |

| 5    | IO_L67N_5        | AD12       |         |             |         |

| 5    | IO_L67P_5        | AC12       |         |             |         |

| 5    | IO_L57N_5/VREF_5 | AA13       |         |             |         |

| 5    | IO_L57P_5        | AB12       |         |             |         |

| 5    | IO_L55N_5        | AA12       |         |             |         |

| 5    | IO_L55P_5        | Y12        |         |             |         |

| 5    | IO_L54N_5        | W12        |         |             |         |

| 5    | IO_L54P_5        | V12        |         |             |         |

| 5    | IO_L53_5/No_Pair | AA11       |         |             |         |

| 5    | IO_L50_5/No_Pair | Y11        |         |             |         |

| 5    | IO_L49N_5        | AD10       |         |             |         |

| 5    | IO_L49P_5        | AC10       |         |             |         |

| 5    | IO_L48N_5        | AB11       |         |             |         |

| 5    | IO_L48P_5        | AB10       |         |             |         |

## Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                 | Pin    |        | No Connects |        |

|------|-----------------|--------|--------|-------------|--------|

| Bank | Pin Description | Number | XC2VP2 | XC2VP4      | XC2VP7 |

| N/A  | GND             | R15    |        |             |        |

| N/A  | GND             | R16    |        |             |        |

| N/A  | GND             | R17    |        |             |        |

| N/A  | GND             | T11    |        |             |        |

| N/A  | GND             | T12    |        |             |        |

| N/A  | GND             | T13    |        |             |        |

| N/A  | GND             | T14    |        |             |        |

| N/A  | GND             | T15    |        |             |        |

| N/A  | GND             | T16    |        |             |        |

| N/A  | GND             | U10    |        |             |        |

| N/A  | GND             | U12    |        |             |        |

| N/A  | GND             | U13    |        |             |        |

| N/A  | GND             | U14    |        |             |        |

| N/A  | GND             | U15    |        |             |        |

| N/A  | GND             | U17    |        |             |        |

| N/A  | GND             | Y20    |        |             |        |

| N/A  | GND             | AA21   |        |             |        |

| N/A  | GND             | AB22   |        |             |        |

| N/A  | GND             | AC23   |        |             |        |

| N/A  | GND             | AD24   |        |             |        |

#### Notes:

1. See Table 4 for an explanation of the signals available on this pin.

# Table 9: FF896 — XC2VP7, XC2VP20, XC2VPX20, and XC2VP30

|      | Pin Description       |                            |               | No Connects |                      |         |

|------|-----------------------|----------------------------|---------------|-------------|----------------------|---------|

| Bank | Virtex-II Pro devices | XC2VPX20<br>(if Different) | Pin<br>Number | XC2VP7      | XC2VP20,<br>XC2VPX20 | XC2VP30 |

| 0    | IO_L53_0/No_Pair      |                            | A21           | NC          |                      |         |

| 0    | IO_L54N_0             |                            | H18           | NC          |                      |         |

| 0    | IO_L54P_0             |                            | G18           | NC          |                      |         |

| 0    | IO_L56N_0             |                            | C21           | NC          |                      |         |

| 0    | IO_L56P_0             |                            | C20           | NC          |                      |         |

| 0    | IO_L57N_0             |                            | J17           | NC          |                      |         |

| 0    | IO_L57P_0/VREF_0      |                            | H17           | NC          |                      |         |

| 0    | IO_L67N_0             |                            | E17           |             |                      |         |

| 0    | IO_L67P_0             |                            | D17           |             |                      |         |

| 0    | IO_L68N_0             |                            | D18           |             |                      |         |

| 0    | IO_L68P_0             |                            | C18           |             |                      |         |

| 0    | IO_L69N_0             |                            | J16           |             |                      |         |

| 0    | IO_L69P_0/VREF_0      |                            | H16           |             |                      |         |

| 0    | IO_L73N_0             |                            | E16           |             |                      |         |

| 0    | IO_L73P_0             |                            | D16           |             |                      |         |

| 0    | IO_L74N_0/GCLK7P      |                            | C16           |             |                      |         |

| 0    | IO_L74P_0/GCLK6S      |                            | B16           |             |                      |         |

| 0    | IO_L75N_0/GCLK5P      | BREFCLKN                   | G16           |             |                      |         |

| 0    | IO_L75P_0/GCLK4S      | BREFCLKP                   | F16           |             |                      |         |

|      |                       |                            |               |             |                      |         |

| 1    | IO_L75N_1/GCLK3P      |                            | F15           |             |                      |         |

| 1    | IO_L75P_1/GCLK2S      |                            | G15           |             |                      |         |

| 1    | IO_L74N_1/GCLK1P      |                            | B15           |             |                      |         |

| 1    | IO_L74P_1/GCLK0S      |                            | C15           |             |                      |         |

| 1    | IO_L73N_1             |                            | D15           |             |                      |         |

| 1    | IO_L73P_1             |                            | E15           |             |                      |         |

| 1    | IO_L69N_1/VREF_1      |                            | H15           |             |                      |         |

| 1    | IO_L69P_1             |                            | J15           |             |                      |         |

| 1    | IO_L68N_1             |                            | C13           |             |                      |         |

| 1    | IO_L68P_1             |                            | D13           |             |                      |         |

| 1    | IO_L67N_1             |                            | D14           |             |                      |         |

| 1    | IO_L67P_1             |                            | E14           |             |                      |         |

| 1    | IO_L57N_1/VREF_1      |                            | H14           | NC          |                      |         |

| 1    | IO_L57P_1             |                            | J14           | NC          |                      |         |

| 1    | <br>IO_L56N_1         |                            | C11           | NC          |                      |         |

| 1    | IO_L56P_1             |                            | C10           | NC          |                      |         |

## Table 9: FF896 — XC2VP7, XC2VP20, XC2VPX20, and XC2VP30

|      | Pin Description       |                            |               | No Connects |                      |         |  |

|------|-----------------------|----------------------------|---------------|-------------|----------------------|---------|--|

| Bank | Virtex-II Pro devices | XC2VPX20<br>(if Different) | Pin<br>Number | XC2VP7      | XC2VP20,<br>XC2VPX20 | XC2VP30 |  |

| 6    | IO_L02P_6             |                            | AH26          |             |                      |         |  |

| 6    | IO_L02N_6             |                            | AG26          |             |                      |         |  |

| 6    | IO_L03P_6             |                            | AH29          |             |                      |         |  |

| 6    | IO_L03N_6/VREF_6      |                            | AH30          |             |                      |         |  |

| 6    | IO_L04P_6             |                            | AH27          |             |                      |         |  |

| 6    | IO_L04N_6             |                            | AG28          |             |                      |         |  |

| 6    | IO_L05P_6             |                            | AD25          |             |                      |         |  |

| 6    | IO_L05N_6             |                            | AD26          |             |                      |         |  |

| 6    | IO_L06P_6             |                            | AG29          |             |                      |         |  |

| 6    | IO_L06N_6             |                            | AG30          |             |                      |         |  |

| 6    | IO_L31P_6             |                            | AF25          | NC          |                      |         |  |

| 6    | IO_L31N_6             |                            | AE26          | NC          |                      |         |  |

| 6    | IO_L32P_6             |                            | AB23          | NC          |                      |         |  |

| 6    | IO_L32N_6             |                            | AB24          | NC          |                      |         |  |

| 6    | IO_L33P_6             |                            | AE27          | NC          |                      |         |  |

| 6    | IO_L33N_6/VREF_6      |                            | AE28          | NC          |                      |         |  |

| 6    | IO_L34P_6             |                            | AF27          | NC          |                      |         |  |

| 6    | IO_L34N_6             |                            | AF28          | NC          |                      |         |  |

| 6    | IO_L35P_6             |                            | AC25          | NC          |                      |         |  |

| 6    | IO_L35N_6             |                            | AC26          | NC          |                      |         |  |

| 6    | IO_L36P_6             |                            | AF29          | NC          |                      |         |  |

| 6    | IO_L36N_6             |                            | AF30          | NC          |                      |         |  |

| 6    | IO_L37P_6             |                            | AD27          | NC          |                      |         |  |

| 6    | IO_L37N_6             |                            | AD28          | NC          |                      |         |  |

| 6    | IO_L38P_6             |                            | AA23          | NC          |                      |         |  |

| 6    | IO_L38N_6             |                            | AA24          | NC          |                      |         |  |

| 6    | IO_L39P_6             |                            | AE29          | NC          |                      |         |  |

| 6    | IO_L39N_6/VREF_6      |                            | AE30          | NC          |                      |         |  |

| 6    | IO_L40P_6             |                            | AB25          | NC          |                      |         |  |

| 6    | IO_L40N_6             |                            | AB26          | NC          |                      |         |  |

| 6    | IO_L41P_6             |                            | Y23           | NC          |                      |         |  |

| 6    | IO_L41N_6             |                            | Y24           | NC          |                      |         |  |

| 6    | IO_L42P_6             |                            | AD29          | NC          |                      |         |  |

| 6    | IO_L42N_6             |                            | AD30          | NC          |                      |         |  |

| 6    | IO_L43P_6             |                            | AC27          |             |                      |         |  |

| 6    | <br>IO_L43N_6         |                            | AC28          |             |                      |         |  |

# Table 10: FF1152 — XC2VP20, XC2VP30, XC2VP40, and XC2VP50

| Bank | Pin Description      | Pin    | No Connects |         |         |          |  |

|------|----------------------|--------|-------------|---------|---------|----------|--|

|      |                      | Number | XC2VP20     | XC2VP30 | XC2VP40 | XC2VP50  |  |

| 0    | IO_L43P_0            | E22    |             |         |         |          |  |

| 0    | IO_L44N_0            | E25    |             |         |         |          |  |

| 0    | IO_L44P_0            | D25    |             |         |         |          |  |

| 0    | IO_L45N_0            | H21    |             |         |         |          |  |

| 0    | IO_L45P_0/VREF_0     | G21    |             |         |         |          |  |

| 0    | IO_L46N_0            | D22    |             |         |         |          |  |

| 0    | IO_L46P_0            | D23    |             |         |         |          |  |

| 0    | IO_L47N_0            | D24    |             |         |         |          |  |

| 0    | IO_L47P_0            | C24    |             |         |         |          |  |

| 0    | IO_L48N_0            | K20    |             |         |         |          |  |

| 0    | IO_L48P_0            | J20    |             |         |         |          |  |

| 0    | IO_L49N_0            | F21    |             |         |         |          |  |

| 0    | IO_L49P_0            | E21    |             |         |         |          |  |

| 0    | IO_L50_0/No_Pair     | C21    |             |         |         |          |  |

| 0    | IO_L53_0/No_Pair     | C22    |             |         |         |          |  |

| 0    | IO_L54N_0            | L19    |             |         |         |          |  |

| 0    | IO_L54P_0            | K19    |             |         |         |          |  |

| 0    | IO_L55N_0            | G20    |             |         |         |          |  |

| 0    | IO_L55P_0            | F20    |             |         |         |          |  |

| 0    | IO_L56N_0            | D21    |             |         |         |          |  |

| 0    | IO_L56P_0            | D20    |             |         |         |          |  |

| 0    | IO_L57N_0            | J19    |             |         |         |          |  |

| 0    | <br>IO_L57P_0/VREF_0 | H19    |             |         |         |          |  |

| 0    | IO_L67N_0            | G19    |             |         |         |          |  |

| 0    | IO_L67P_0            | F19    |             |         |         |          |  |

| 0    | IO_L68N_0            | E19    |             |         |         |          |  |

| 0    | IO_L68P_0            | D19    |             |         |         |          |  |

| 0    | IO_L69N_0            | L18    |             |         |         |          |  |

| 0    | IO_L69P_0/VREF_0     | K18    |             |         |         |          |  |

| 0    | IO_L73N_0            | G18    |             |         |         |          |  |

| 0    | IO_L73P_0            | F18    |             |         |         |          |  |

| 0    | IO_L74N_0/GCLK7P     | E18    |             |         |         |          |  |

| 0    | IO_L74P_0/GCLK6S     | D18    |             |         |         |          |  |

| 0    | IO_L75N_0/GCLK5P     | J18    |             |         |         |          |  |

| 0    | IO_L75P_0/GCLK4S     | H18    |             |         |         |          |  |

| ~    |                      | 1110   |             |         |         | <u> </u> |  |

| 1    | IO_L75N_1/GCLK3P     | H17    |             |         |         |          |  |

| 1    | IO_L75P_1/GCLK2S     | J17    |             |         |         |          |  |

# Table 10: FF1152 — XC2VP20, XC2VP30, XC2VP40, and XC2VP50

| Bank    | Pin Description  | Pin    | No Connects |         |         |         |  |

|---------|------------------|--------|-------------|---------|---------|---------|--|

|         |                  | Number | XC2VP20     | XC2VP30 | XC2VP40 | XC2VP50 |  |

| 1       | IO_L37N_1        | G13    |             |         |         |         |  |

| 1       | IO_L37P_1        | H13    |             |         |         |         |  |

| 1       | IO_L27N_1/VREF_1 | J13    | NC          | NC      |         |         |  |

| 1       | IO_L27P_1        | K13    | NC          | NC      |         |         |  |

| 1       | IO_L26N_1        | D8     | NC          | NC      |         |         |  |

| 1       | IO_L26P_1        | E8     | NC          | NC      |         |         |  |

| 1       | IO_L25N_1        | F12    | NC          | NC      |         |         |  |

| 1       | IO_L25P_1        | G12    | NC          | NC      |         |         |  |

| 1       | IO_L21N_1        | G11    | NC          | NC      |         |         |  |

| 1       | IO_L21P_1        | H11    | NC          | NC      |         |         |  |

| 1       | IO_L20N_1        | C7     | NC          | NC      |         |         |  |

| 1       | IO_L20P_1        | D7     | NC          | NC      |         |         |  |

| 1       | IO_L19N_1        | E11    | NC          | NC      |         |         |  |

| 1       | IO_L19P_1        | F11    | NC          | NC      |         |         |  |

| 1       | IO_L09N_1/VREF_1 | J12    |             |         |         |         |  |

| 1       | IO_L09P_1        | K12    |             |         |         |         |  |

| 1       | IO_L08N_1        | D6     |             |         |         |         |  |

| 1       | IO_L08P_1        | D5     |             |         |         |         |  |

| 1       | IO_L07N_1        | E9     |             |         |         |         |  |

| 1       | IO_L07P_1        | F9     |             |         |         |         |  |

| 1       | IO_L06N_1        | J11    |             |         |         |         |  |

| 1       | IO_L06P_1        | K11    |             |         |         |         |  |

| 1       | IO_L05_1/No_Pair | J10    |             |         |         |         |  |

| 1       | IO_L03N_1/VREF_1 | G10    |             |         |         |         |  |

| 1       | IO_L03P_1        | H10    |             |         |         |         |  |

| 1       | IO_L02N_1        | G9     |             |         |         |         |  |

| 1       | IO_L02P_1        | H9     |             |         |         |         |  |

| 1       | IO_L01N_1/VRP_1  | E7     |             |         |         |         |  |

| 1       | IO_L01P_1/VRN_1  | E6     |             |         |         |         |  |

| · · · · |                  |        |             |         |         |         |  |

| 2       | IO_L01N_2/VRP_2  | D2     |             |         |         |         |  |

| 2       | IO_L01P_2/VRN_2  | D1     |             |         |         |         |  |

| 2       | IO_L02N_2        | F8     |             |         |         |         |  |

| 2       | IO_L02P_2        | F7     |             |         |         |         |  |

| 2       | IO_L03N_2        | E4     |             |         |         |         |  |

| 2       | IO_L03P_2        | E3     |             |         |         |         |  |

| 2       | IO_L04N_2/VREF_2 | E2     |             |         |         |         |  |

| 2       | IO_L04P_2        | E1     |             |         |         |         |  |

# Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                  | Pin    | No Connects |         |  |

|------|------------------|--------|-------------|---------|--|

| Bank | Pin Description  | Number | XC2VP50     | XC2VP70 |  |

| 6    | IO_L04P_6        | AR33   |             |         |  |

| 6    | IO_L04N_6        | AP33   |             |         |  |

| 6    | IO_L05P_6        | AM32   |             |         |  |

| 6    | IO_L05N_6        | AL31   |             |         |  |

| 6    | IO_L06P_6        | AT34   |             |         |  |

| 6    | IO_L06N_6        | AR34   |             |         |  |

| 6    | IO_L73P_6        | AU35   | NC          |         |  |

| 6    | IO_L73N_6        | AT35   | NC          |         |  |

| 6    | IO_L75P_6        | AT38   | NC          |         |  |

| 6    | IO_L75N_6/VREF_6 | AT39   | NC          |         |  |

| 6    | IO_L76P_6        | AR37   | NC          |         |  |

| 6    | IO_L76N_6        | AR38   | NC          |         |  |

| 6    | IO_L78P_6        | AP38   | NC          |         |  |

| 6    | IO_L78N_6        | AP39   | NC          |         |  |

| 6    | IO_L79P_6        | AP36   | NC          |         |  |

| 6    | IO_L79N_6        | AP37   | NC          |         |  |

| 6    | IO_L81P_6        | AP35   | NC          |         |  |

| 6    | IO_L81N_6/VREF_6 | AN35   | NC          |         |  |

| 6    | IO_L82P_6        | AN38   | NC          |         |  |

| 6    | IO_L82N_6        | AN39   | NC          |         |  |

| 6    | IO_L84P_6        | AN36   | NC          |         |  |

| 6    | IO_L84N_6        | AN37   | NC          |         |  |

| 6    | IO_L07P_6        | AN33   |             |         |  |

| 6    | IO_L07N_6        | AN34   |             |         |  |

| 6    | IO_L08P_6        | AK31   |             |         |  |

| 6    | IO_L08N_6        | AK32   |             |         |  |

| 6    | IO_L09P_6        | AM37   |             |         |  |

| 6    | IO_L09N_6/VREF_6 | AM38   |             |         |  |

| 6    | IO_L10P_6        | AM36   |             |         |  |

| 6    | IO_L10N_6        | AL35   |             |         |  |

| 6    | IO_L11P_6        | AJ31   |             |         |  |

| 6    | IO_L11N_6        | AH30   |             |         |  |

| 6    | <br>IO_L12P_6    | AM33   |             |         |  |

| 6    | IO_L12N_6        | AM34   |             |         |  |

| 6    | IO_L13P_6        | AL38   |             |         |  |

| 6    | IO_L13N_6        | AL39   |             |         |  |

| 6    | <br>IO_L14P_6    | AH29   |             |         |  |

| 6    | <br>IO_L14N_6    | AG29   |             |         |  |

# FF1704 Flip-Chip Fine-Pitch BGA Package

As shown in Table 13, XC2VP70 and XC2VP100 Virtex-II Pro devices are available in the FF1704 flip-chip fine-pitch BGA package. Following this table are the FF1704 Flip-Chip Fine-Pitch BGA Package Specifications (1.00mm pitch).

# Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       |                            |            | No Connects          |          |  |

|------|-----------------------|----------------------------|------------|----------------------|----------|--|

| Bank | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |  |

| 0    | IO_L01N_0/VRP_0       |                            | G34        |                      |          |  |

| 0    | IO_L01P_0/VRN_0       |                            | H34        |                      |          |  |

| 0    | IO_L02N_0             |                            | F34        |                      |          |  |

| 0    | IO_L02P_0             |                            | E34        |                      |          |  |

| 0    | IO_L03N_0             |                            | C34        |                      |          |  |

| 0    | IO_L03P_0/VREF_0      |                            | D34        |                      |          |  |

| 0    | IO_L05_0/No_Pair      |                            | K32        |                      |          |  |

| 0    | IO_L06N_0             |                            | H33        |                      |          |  |

| 0    | IO_L06P_0             |                            | J33        |                      |          |  |

| 0    | IO_L07N_0             |                            | F33        |                      |          |  |

| 0    | IO_L07P_0             |                            | G33        |                      |          |  |

| 0    | IO_L08N_0             |                            | E33        |                      |          |  |

| 0    | IO_L08P_0             |                            | D33        |                      |          |  |

| 0    | IO_L09N_0             |                            | H32        |                      |          |  |

| 0    | IO_L09P_0/VREF_0      |                            | J32        |                      |          |  |

| 0    | IO_L19N_0             |                            | E32        |                      |          |  |

| 0    | IO_L19P_0             |                            | F32        |                      |          |  |

| 0    | IO_L20N_0             |                            | C33        |                      |          |  |

| 0    | IO_L20P_0             |                            | C32        |                      |          |  |

| 0    | IO_L21N_0             |                            | K31        |                      |          |  |

| 0    | IO_L21P_0             |                            | L31        |                      |          |  |

| 0    | IO_L25N_0             |                            | H31        |                      |          |  |

| 0    | IO_L25P_0             |                            | J31        |                      |          |  |

| 0    | IO_L26N_0             |                            | G31        |                      |          |  |

| 0    | IO_L26P_0             |                            | F31        |                      |          |  |

| 0    | IO_L27N_0             |                            | D31        |                      |          |  |

| 0    | IO_L27P_0/VREF_0      |                            | E31        |                      |          |  |

| 0    | IO_L28N_0             |                            | L30        |                      |          |  |

| 0    | IO_L28P_0             |                            | M30        |                      |          |  |

| 0    | IO_L29N_0             |                            | J30        |                      |          |  |

| 0    | IO_L29P_0             |                            | K30        |                      |          |  |

| 0    | IO_L30N_0             |                            | G30        |                      |          |  |

| 0    | IO_L30P_0             |                            | H30        |                      |          |  |

# Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       |                            |            | No Connects          |          |  |

|------|-----------------------|----------------------------|------------|----------------------|----------|--|

| Bank | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |  |

| 7    | IO_L27P_7             |                            | P33        |                      |          |  |

| 7    | IO_L27N_7             |                            | P34        |                      |          |  |

| 7    | IO_L26P_7             |                            | N31        |                      |          |  |

| 7    | IO_L26N_7             |                            | N32        |                      |          |  |

| 7    | IO_L25P_7             |                            | N41        |                      |          |  |

| 7    | IO_L25N_7             |                            | N42        |                      |          |  |

| 7    | IO_L24P_7             |                            | N39        |                      |          |  |

| 7    | IO_L24N_7             |                            | N40        |                      |          |  |

| 7    | IO_L23P_7             |                            | N33        |                      |          |  |

| 7    | IO_L23N_7             |                            | N34        |                      |          |  |

| 7    | IO_L22P_7             |                            | N37        |                      |          |  |

| 7    | IO_L22N_7/VREF_7      |                            | N38        |                      |          |  |

| 7    | IO_L21P_7             |                            | N35        |                      |          |  |

| 7    | IO_L21N_7             |                            | N36        |                      |          |  |

| 7    | IO_L20P_7             |                            | M38        |                      |          |  |

| 7    | IO_L20N_7             |                            | M39        |                      |          |  |

| 7    | IO_L19P_7             |                            | M40        |                      |          |  |

| 7    | IO_L19N_7             |                            | M41        |                      |          |  |

| 7    | IO_L18P_7             |                            | M33        |                      |          |  |

| 7    | IO_L18N_7             |                            | M34        |                      |          |  |

| 7    | IO_L17P_7             |                            | M31        |                      |          |  |

| 7    | IO_L17N_7             |                            | M32        |                      |          |  |

| 7    | IO_L16P_7             |                            | M35        |                      |          |  |

| 7    | IO_L16N_7/VREF_7      |                            | M36        |                      |          |  |

| 7    | IO_L15P_7             |                            | L41        |                      |          |  |

| 7    | IO_L15N_7             |                            | L42        |                      |          |  |

| 7    | IO_L14P_7             |                            | L39        |                      |          |  |

| 7    | IO_L14N_7             |                            | L38        |                      |          |  |

| 7    | IO_L13P_7             |                            | L40        |                      |          |  |

| 7    | IO_L13N_7             |                            | K40        |                      |          |  |

| 7    | IO_L12P_7             |                            | L36        |                      |          |  |

| 7    | IO_L12N_7             |                            | L37        |                      |          |  |

| 7    | IO_L11P_7             |                            | L34        |                      |          |  |

| 7    | IO_L11N_7             |                            | L35        |                      |          |  |

| 7    | IO_L10P_7             |                            | K42        |                      |          |  |

| 7    | IO_L10N_7/VREF_7      |                            | K41        |                      |          |  |

# Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

| _    | Pin Description       |                            |            | No Connects          |          |  |

|------|-----------------------|----------------------------|------------|----------------------|----------|--|

| Bank | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |  |

| N/A  | GND                   |                            | AA5        |                      |          |  |

| N/A  | GND                   |                            | Y41        |                      |          |  |

| N/A  | GND                   |                            | Y26        |                      |          |  |

| N/A  | GND                   |                            | Y25        |                      |          |  |

| N/A  | GND                   |                            | Y24        |                      |          |  |

| N/A  | GND                   |                            | Y23        |                      |          |  |

| N/A  | GND                   |                            | Y22        |                      |          |  |

| N/A  | GND                   |                            | Y21        |                      |          |  |

| N/A  | GND                   |                            | Y20        |                      |          |  |

| N/A  | GND                   |                            | Y19        |                      |          |  |

| N/A  | GND                   |                            | Y18        |                      |          |  |

| N/A  | GND                   |                            | Y17        |                      |          |  |

| N/A  | GND                   |                            | Y2         |                      |          |  |

| N/A  | GND                   |                            | W26        |                      |          |  |

| N/A  | GND                   |                            | W25        |                      |          |  |

| N/A  | GND                   |                            | W24        |                      |          |  |

| N/A  | GND                   |                            | W23        |                      |          |  |

| N/A  | GND                   |                            | W22        |                      |          |  |

| N/A  | GND                   |                            | W21        |                      |          |  |

| N/A  | GND                   |                            | W20        |                      |          |  |

| N/A  | GND                   |                            | W19        |                      |          |  |

| N/A  | GND                   |                            | W18        |                      |          |  |

| N/A  | GND                   |                            | W17        |                      |          |  |

| N/A  | GND                   |                            | V37        |                      |          |  |

| N/A  | GND                   |                            | V34        |                      |          |  |

| N/A  | GND                   |                            | V26        |                      |          |  |

| N/A  | GND                   |                            | V25        |                      |          |  |

| N/A  | GND                   |                            | V24        |                      |          |  |

| N/A  | GND                   |                            | V23        |                      |          |  |

| N/A  | GND                   |                            | V22        |                      |          |  |

| N/A  | GND                   |                            | V21        |                      |          |  |

| N/A  | GND                   |                            | V20        |                      |          |  |

| N/A  | GND                   |                            | V19        |                      |          |  |

| N/A  | GND                   |                            | V18        |                      |          |  |

| N/A  | GND                   |                            | V17        |                      |          |  |

| N/A  | GND                   |                            | V9         |                      |          |  |